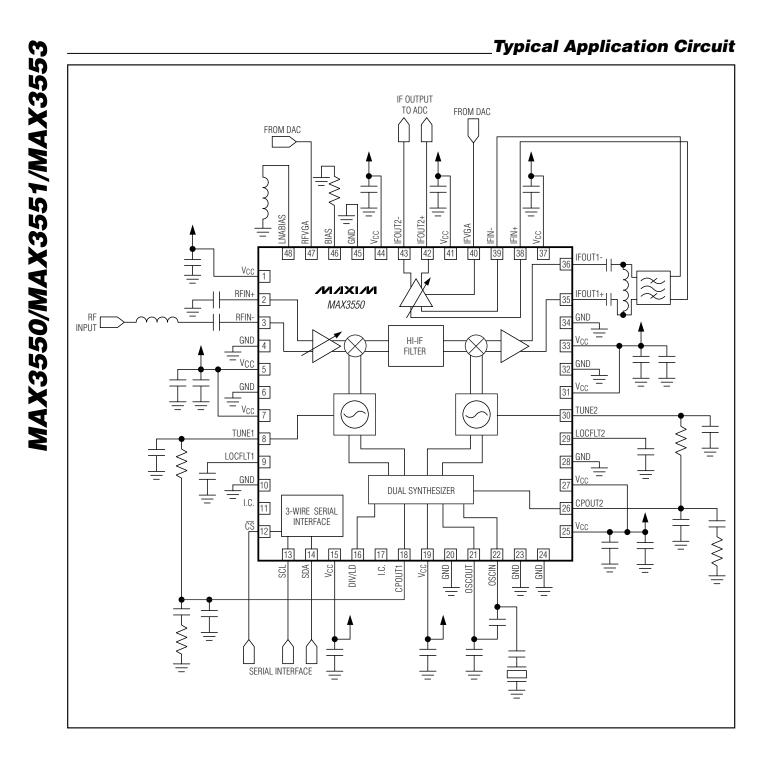

### **General Description**

The MAX3550/MAX3551/MAX3553 low-cost, broadband, dual-conversion tuner ICs are designed for use in analog and digital television receivers. Each IC integrates all necessary RF functions, including an integrated HI-IF filter, fully integrated VCOs, and an integrated IF VGA. The operating frequency range extends from 50MHz to 878MHz while providing over 60dB RF/IF gain-control range. The MAX3550/MAX3551 have an IF frequency centered at 44MHz, while the MAX3553 has an IF output centered at 36MHz.

These devices include a variable-gain front end, achieving an overall 8dB noise figure. A dual synthesizer generates both local oscillator (LO) frequencies, providing superior phase noise performance of -86dBc/Hz at 10kHz. The integrated HI-IF filter achieves 68dBc of image rejection. Only an IF SAW filter, passive loop filters, and a crystal are needed to complete a single-chip tuner. Device programming and configuration are accomplished with a 3-wire serial interface for the MAX3550, and with a 2-wire serial interface for the MAX3551/MAX3553.

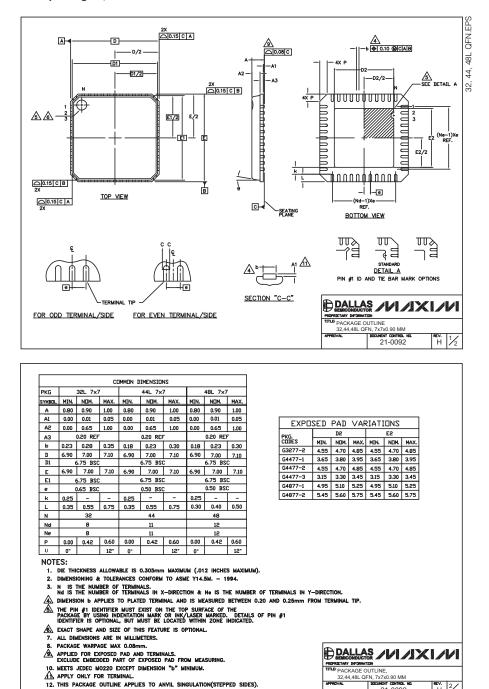

The MAX3550/MAX3551/MAX3553 are available in a 48-pin QFN-EP package and are specified for the commercial (0°C to +70°C) temperature range.

Analog/Digital Cable Set-Top Boxes OpenCable™ Television Receivers DVB-T Digital Terrestrial Receivers ATSC Digital Terrestrial Receivers Cable Modems

#### **Selector Guide**

**Applications**

| PART    | SERIAL INTERFACE | IF CENTER<br>FREQUENCY |

|---------|------------------|------------------------|

| MAX3550 | 3-Wire           | 44MHz                  |

| MAX3551 | 2-Wire           | 44MHz                  |

| MAX3553 | 2-Wire           | 36MHz                  |

OpenCable is a trademark of CableLabs.

####

\_Features

- Fully Integrated HI-IF Filter

- Fully Integrated VCOs, No External Components or Traces

- Low 8dB Noise Figure

- High Linearity—+19dBm IIP3 and +52dBm IIP2

- Industry's Smallest Footprint

- Superior Phase Noise for 256-QAM, 8-VSB, and COFDM

#### **Ordering Information**

| PART               | TEMP RANGE   | PIN-PACKAGE |

|--------------------|--------------|-------------|

| MAX3550CGM         | 0°C to +70°C | 48 QFN-EP*  |

| MAX3551CGM         | 0°C to +70°C | 48 QFN-EP*  |

| MAX3553CGM         | 0°C to +70°C | 48 QFN-EP*  |

| * CD Expand models |              |             |

EP = Exposed paddle.

R 48 47 46 45 44 43 42 41 40 39 38 37 Vcc 1 IFOUT1-36 ////XI/// IFOUT1+ RFIN+ 35 2 MAX3550 34 GND RFIN- 3 33 GND 4 Vcc FILTER Vcc 5 32 GND GND 6 31 Vcc Vcc 7 - 30 TUNE2 29 LOCFLT2 TUNE1 28 LOCFLT1 9 GND GND 10 27 Vcc DUAL SYNTHESIZER 26 11 I.C. 3-WIRE SERIAL CPOUT2 INTERFACE CS 12 25 V<sub>CC</sub> 17 23 24 14 15 18 20 21 <u>.</u> 20 GND 5 SDA 00 POUT1 25 25

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

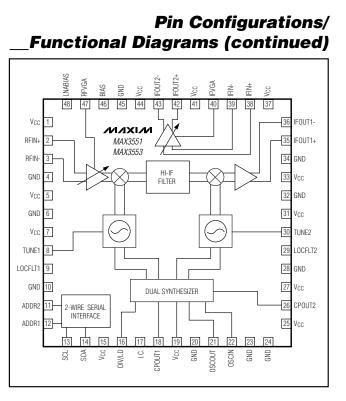

### Pin Configurations/ Functional Diagrams

Pin Configurations/Functional Diagrams continued at end of data sheet.

### ABSOLUTE MAXIMUM RATINGS

V<sub>CC</sub> to GND.....-0.3V to +5.5V IFIN\_, IFOUT1\_, IFOUT2\_, RFIN\_, TUNE\_, LOCFLT\_, CPOUT\_, OSCIN, OSCOUT, IFVGA, REVGA, BIAS, LNABIAS, ADDR\_, CS, SCL, SDA, DIV/LD....-0.3V to (V<sub>CC</sub> + 0.3V)

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |               |

|-------------------------------------------------------|---------------|

| 48-Pin QFN (derate 27mW/°C above +70°C)               | 2162mW        |

| Operating Temperature Range                           | .0°C to +70°C |

| Junction Temperature                                  | +150°C        |

| Storage Temperature Range65                           | 5°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C        |

CAUTION! ESD SENSITIVE DEVICE

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(MAX355\_ EV kit,  $V_{CC} = +4.75V$  to +5.25V,  $R_{BIAS} = 5.9k\Omega \pm 1\%$ , no AC signal applied,  $T_A = 0^{\circ}C$  to +70°C, unless otherwise noted. Typical values are at  $V_{CC} = +5.0V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                         | CONDITIONS                                    | MIN  | TYP | MAX  | UNITS |

|-----------------------------------|-----------------------------------------------|------|-----|------|-------|

| SUPPLY VOLTAGE AND SUPPLY CURRENT |                                               |      |     |      |       |

| Supply Voltage                    |                                               | 4.75 |     | 5.25 | V     |

| Supply Current                    | At $T_A = +25^{\circ}C$ , $V_{RFVGA} = +3.0V$ |      | 320 |      | mA    |

| Supply Current                    | At $T_A = +70^{\circ}C$ , $V_{RFVGA} = +0.5V$ |      |     | 385  | ШA    |

| RF and IF VGA Input Bias Current  | $V_{RFVGA} = V_{IFVGA} = +0.5V$ and +3.0V     | -50  |     | +50  | μΑ    |

| RF and IF VGA Control Voltage     | Maximum gain                                  | 3    |     |      | V     |

| RF and IF VGA Control Voltage     | Minimum gain                                  |      |     | 0.5  | v     |

| LOGIC INTERFACE                   |                                               |      |     |      |       |

| Input-Logic Low (VIL)             |                                               |      |     | 0.9  | V     |

| Input-Logic High (VIH)            |                                               | 2.3  |     |      | V     |

| Input Logic Current               |                                               | -10  |     | +10  | μA    |

| Output-Logic Low                  | Sink current = 3mA                            |      |     | 0.4  | V     |

| Output-Logic High                 | Source current = 3mA                          | 2.8  |     |      | V     |

#### **AC ELECTRICAL CHARACTERISTICS**

(MAX355\_ EV kit, V<sub>CC</sub> = +4.75V to +5.25V, R<sub>BIAS</sub> =  $5.9k\Omega \pm 1\%$ , **inputs terminated to 75** $\Omega$ , f<sub>RFIN</sub> = 50MHz to 878MHz, f<sub>IF</sub> = 45.75MHz (MAX3550/MAX3551), f<sub>IF</sub> = 38.9MHz (MAX3553), f<sub>COMP1</sub> = 1MHz, f<sub>COMP2</sub> = 62.5kHz, T<sub>A</sub> = 0°C to +70°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = +5.0V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                     | CONDITIONS                                                                                        |                                                                                                                | MIN  | ТҮР  | MAX  | UNITS  |

|-------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| OVERALL REQUIREMENTS (RF IN   | NPUT TO 1st IF OUTPUT)                                                                            |                                                                                                                |      |      |      | •      |

| Operating Frequency Range     | Gain specification met across this                                                                | Gain specification met across this frequency band                                                              |      |      |      | MHz    |

| Input Return Loss             | Worst case across band, 75 $\Omega$ , an                                                          | y RFVGA setting                                                                                                |      | 8    |      | dB     |

| Voltage Gain                  | $Z_{\text{SOURCE}} = 75\Omega$ , $Z_{\text{LOAD}} = 200\Omega$ ,                                  | $T_A = +25^{\circ}C$                                                                                           | 31.5 | 38.5 | 45.0 | dB     |

| Voltage Gall                  | $V_{RFVGA} = +3.0V$                                                                               | $T_A = +70^{\circ}C$                                                                                           | 30.0 | 37   | 43.5 | uв     |

| Gain-Reduction Range          | Measured at 50MHz                                                                                 |                                                                                                                | 30   |      |      | dB     |

| Gain Flatness                 | $V_{RFVGA} = +3.0V$ at $f_{RFIN} = 878MH$                                                         | Hz vs. 50MHz                                                                                                   | -1.5 |      | +1.5 | dB     |

| Gain Flatness                 | $V_{RFVGA} = 0.5V$ at $f_{RFIN} = 878MHz$                                                         | z vs. 50MHz                                                                                                    | -2   |      | +2   | uВ     |

| Noise Figure                  | $V_{RFVGA} = +3.0V$                                                                               |                                                                                                                |      | 7.9  |      | dB     |

| IIP2                          | $V_{RFVGA} = +3.0V, T_A = +25^{\circ}C$ to +<br>$V_{CC} = 4.85V$ to 5.15V, f <sub>RF</sub> = 860N |                                                                                                                |      | 34   |      | dDaa   |

|                               | 0                                                                                                 | At 12dB gain reduction, $T_A = +25$ °C to +70°C,<br>V <sub>CC</sub> = 4.85V to 5.15V, f <sub>RF</sub> = 860MHz |      |      |      | - dBm  |

|                               | $V_{RFVGA} = +3.0V, T_A = +25^{\circ}C$ to +<br>$V_{CC} = 4.85V$ to 5.15V                         | $V_{RFVGA} = +3.0V$ , $T_{A} = +25^{\circ}C$ to $+70^{\circ}C$ ,<br>$V_{CC} = 4.85V$ to 5.15V                  |      |      |      |        |

| IIP3                          | At 12dB gain reduction, $T_A = +25$<br>V <sub>CC</sub> = 4.85V to 5.15V                           | At 12dB gain reduction, $T_A = +25^{\circ}C$ to $+70^{\circ}C$ ,<br>V <sub>CC</sub> = 4.85V to 5.15V           |      |      |      | - dBm  |

| Beats Within Output           | 0dBmV PIX carrier level (Note 2)                                                                  |                                                                                                                |      | -68  |      | dBc    |

| Channel Flatness              | From PIX to (PIX + 4) MHz                                                                         |                                                                                                                | -0.5 | 0.3  | +1.0 | dB     |

| Isolation                     | 5MHz to 150MHz, RF input to IF outp                                                               | ut (Note 3)                                                                                                    | -63  | -68  |      | dBc    |

|                               | Measured at 91MHz above desire<br>(MAX3550/MAX3551)                                               | Measured at 91MHz above desired PIX<br>(MAX3550/MAX3551)                                                       |      |      |      | -ID -  |

| Image Rejection               | Measured at 77.75MHz above de (MAX3553)                                                           | Measured at 77.75MHz above desired PIX<br>(MAX3553)                                                            |      |      |      | dBc    |

|                               | 50MHz to 878MHz                                                                                   | 50MHz to 878MHz                                                                                                |      |      | -48  |        |

| Spurious at RF Input (Note 3) | Above 878MHz (LO and LO harm                                                                      |                                                                                                                |      | +3   | dBmV |        |

|                               | foffset = 1kHz                                                                                    | foffset = 1kHz                                                                                                 |      |      |      |        |

| Single Sideband Phase Noise   | fOFFSET = 10kHz, BWLOOP = 2.5k                                                                    | $f_{OFFSET} = 10 \text{kHz}, \text{BW}_{LOOP} = 2.5 \text{kHz}$                                                |      |      |      | dBc/Hz |

|                               | $f_{OFFSET} = 100 \text{kHz}, \text{BW}_{LOOP} = 2.5$                                             | $f_{OFFSET} = 100 \text{kHz}, \text{BW}_{LOOP} = 2.5 \text{kHz}$                                               |      |      |      | 1      |

| Output Return Loss            | Balanced, $50\Omega$                                                                              |                                                                                                                |      | 9    |      | dB     |

### AC ELECTRICAL CHARACTERISTICS

(MAX355\_ EV kit,  $V_{CC} = +4.75V$  to +5.25V,  $R_{BIAS} = 5.9k\Omega \pm 1\%$ , inputs terminated to  $1k\Omega$ ,  $Z_{LOAD} = 300\Omega$ , f<sub>IF</sub> = 40MHz to 48MHz,  $T_A = 0^{\circ}C$  to +70°C, unless otherwise noted. Typical values are at  $V_{CC} = +5.0V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                  | CONDITIONS                                                                                                    | MIN | ТҮР   | MAX | UNITS |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| SECOND IF STAGE                            | · · · ·                                                                                                       |     |       |     |       |

| Input Impedance                            | Balanced                                                                                                      |     | 1.7   |     | kΩ    |

| Output Impedance                           | Balanced (Note 3)                                                                                             |     |       | 100 | Ω     |

| Deschand Valtere Cain                      | $Z_{\text{SOURCE}} = 1.1 \text{k}\Omega$ , $Z_{\text{LOAD}} = 300\Omega$ , $V_{\text{IFVGA}} = +3.0 \text{V}$ | 50  | 53    | 57  | dD    |

| Passband Voltage Gain<br>Passband Flatness | $V_{IFVGA} = +0.5V$                                                                                           |     | 14.5  | 23  | dB    |

| Passband Flatness                          | From PIX to (PIX - 4) MHz for 45.75MHz PIX frequency (Note 3)                                                 |     |       | 0.2 | dB    |

| Maximum Output Voltage                     |                                                                                                               |     | 3.2   |     | VP-P  |

| VGA Gain Slope                             | $V_{IFVGA} = +3.0V \text{ to } +0.5V$                                                                         | 10  |       | 20  | dB/V  |

| -3dB Bandwidth                             | (Note 3)                                                                                                      |     |       | 180 | MHz   |

| Noise Figure                               | $f_{IF} = 44MHz$ , $V_{IFVGA} = +3.0V$                                                                        |     | 5.1   |     | dB    |

| Noise Figure vs. Attenuation               | First 10dB back-off                                                                                           |     | 0.3   |     | dB/dB |

| IIP3                                       | Gain = $45$ dB, V <sub>OUT</sub> = $1.5$ V <sub>P-P</sub>                                                     |     | -27.5 |     | dDaa  |

| IIP3                                       | Gain = $27$ dB, V <sub>OUT</sub> = $1.5$ V <sub>P-P</sub>                                                     |     | -11.3 |     | dBm   |

| OIP3                                       | V <sub>OUT</sub> = 1.5V <sub>P-P</sub> , V <sub>IFVGA</sub> = +3.0V to +0.5V (Note 3)                         |     | 25    |     | dBm   |

| PSRR                                       | 50mV <sub>P-P</sub> at 200kHz                                                                                 |     | -57   |     | dB    |

#### SYNTHESIZER ELECTRICAL CHARACTERISTICS

(MAX355\_EV kit,  $V_{CC} = +4.75V$  to +5.25V,  $R_{BIAS} = 5.9k\Omega \pm 1\%$ ,  $f_{COMP1} = 1$ MHz,  $f_{COMP2} = 62.5$ kHz,  $T_A = 0^{\circ}$ C to +70°C, unless otherwise noted. Typical values are at  $V_{CC} = +5.0V$ ,  $T_A = +25^{\circ}$ C, unless otherwise noted.) (Note 1)

| PARAMETER                          | CONDITIONS                          | MIN T | YP MAX | UNITS |

|------------------------------------|-------------------------------------|-------|--------|-------|

| 1st LOCAL OSCILLATOR (LO1)         |                                     |       |        |       |

| Tuning Range                       |                                     | 1274  | 2111   | MHz   |

| VCO Tuning Gain                    |                                     | 40    | 120    | MHz/V |

| 1st LOCAL OSCILLATOR (LO1) DIVIDER |                                     |       |        |       |

| RF1 N-Divider Ratio                |                                     | 256   | 8191   |       |

| RF1 R-Divider Ratio                |                                     | 1     | 31     |       |

| 1st LOCAL OSCILLATOR (LO1) PHASE I | DETECTOR AND CHARGE PUMP            |       |        |       |

| Phase-Detector Phase Noise         | f <sub>OFFSET</sub> = 2kHz (Note 3) |       | -142   | dBc   |

| Charge-Pump Source/Sink Matching   | Correlate locked vs. unlocked       |       | 6      | %     |

| Charge-Pump Tri-State Current      | RF1                                 | -20   | +20    | nA    |

| 2nd LOCAL OSCILLATOR (LO2)         |                                     |       |        |       |

| Tuning Range                       |                                     | 1175  | 1193   | MHz   |

| VCO Tuning Gain                    |                                     | 25    | 70     | MHz/V |

| 2nd LOCAL OSCILLATOR (LO2) DIVIDER | 3                                   |       |        |       |

| RF2 N-Divider Ratio                |                                     | 512   | 65,535 |       |

| RF2 R-Divider Ratio                |                                     | 2     | 127    |       |

| 2nd LOCAL OSCILLATOR (LO2) PHASE   | DETECTOR AND CHARGE PUMP            |       |        |       |

| Phase-Detector Phase Noise         | f <sub>OFFSET</sub> = 2kHz (Note 3) |       | -142   | dBc   |

| Charge-Pump Source/Sink Matching   | Correlate locked vs. unlocked       |       | 6      | %     |

| Charge-Pump Tri-State Current      | RF2                                 | -7    | +7     | nA    |

### LOGIC INTERFACE

(MAX355\_ EV kit, V<sub>CC</sub> = +4.75V to +5.25V, R<sub>BIAS</sub> =  $5.9k\Omega \pm 1\%$ , T<sub>A</sub> = 0°C to +70°C, unless otherwise noted.) (Note 1)

| PARAMETER               | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|-------------------------|------------|-----|-----|-----|-------|

| Maximum Clock Frequency |            | 400 |     |     | kHz   |

Note 1: These parameters are production tested from  $T_A = +25^{\circ}C$  to  $+70^{\circ}C$ , and are guaranteed by design and characterization at  $T_A = 0^{\circ}C$ .

**Note 2:** When using the tuning table provided in EV kit documentation.

Note 3: These parameters are guaranteed by design and characterization, and are not production tested.

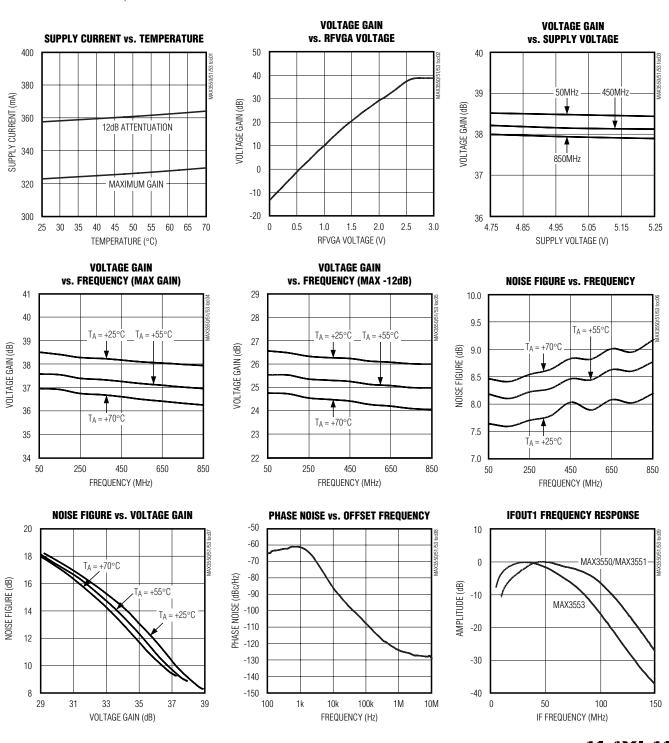

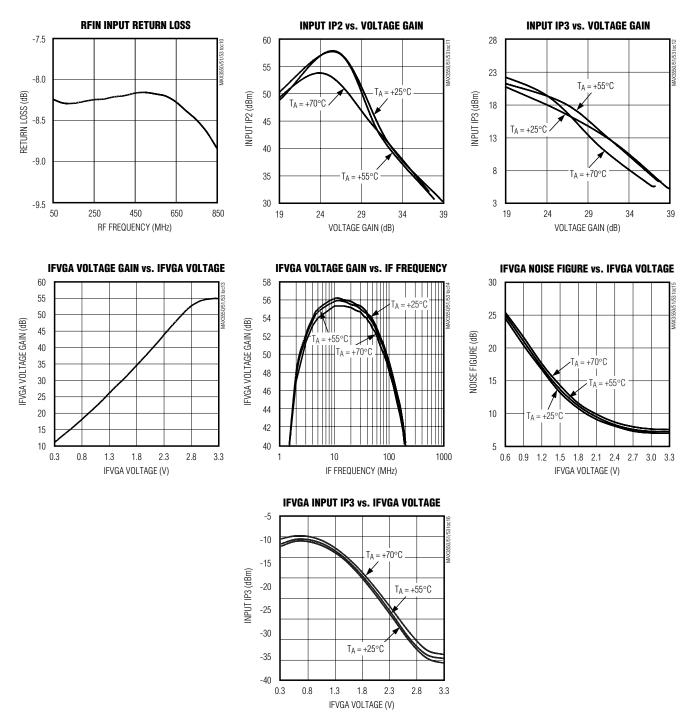

**Typical Operating Characteristics**

#### **Typical Operating Characteristics (continued)**

(MAX355\_EV kit,  $V_{CC} = +5.0V$ ,  $R_{BIAS} = 5.9k\Omega$ ,  $f_{RF} = 860MHz$ ,  $f_{IF} = 44MHz$  (MAX3550/MAX3551), 36MHz (MAX3553),  $T_A = +25^{\circ}C$ , unless otherwise noted.)

### **Pin Description**

| 1         Vcc         RF Variable-Gain Amplifier (VGA) Supply Voltage. Bypass with a capacitor as close to the pin as possible.<br>Do not share the bypass capacitor ground vias with any other branches.           2.3         RFIN-<br>HIN-<br>Along Differential LNA Inputs. Requires AC coupling and can be driven balanced or single ended. Recommend<br>driving pin 3 and AC ground pin 2 for optimum input IP2 performance.           4.6, 10,<br>20, 23,<br>24, 28,<br>32, 34, 45         GND         Ground. Connect to PC board ground plane.           5         Vcc         Ist Mixer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass<br>capacitor ground vias with any other branches.           7         Vcc         Ist VCO Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.           8         TUNE1         1st VCO Tuning Input. Connect the Connection. Connect a capacitor for GND (Refer to the EV kit.)           11         I.CC         Internal Connection. Leave this pin unconnected (MAX3551)           12         CS         3-Wire Serial Interface Enable Input Pin (SPIPUSPIPTMICROWIRET* Compatible) (MAX3550)           13         Sct.         3-Wire Serial Interface Clock Input Pin (SPIPUSPIPTMICROWIRET* Compatible) (MAX3550)           14         SDA         3-Wire Serial Interface Clock Input Pin (MAX3551/MAX3553)           15         Vcc         Digital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do n | PIN                | NAME            | DESCRIPTION                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|------------------------------------------------------------------------------------------------------------|

| 2.3       RFIN-       driving pin 3 and AC ground pin 2 for optimum input IP2 performance.         4. 6. 10, 20, 23, 24, 28, 32, 34, 45       GND       Ground. Connect to PC board ground plane.         5       Vcc       1st Mixer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         7       Vcc       1st VCO Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         8       TUNE1       1st VCO Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         9       LOCFLT1       1st LO Noise-Filtering Capacitor Connection. Connect a capacitor to GND. (Refer to the EV kit.)         11       1.C.       Internal Connection. Leave this pin unconnected (MAX3550).         12       ADDR2       2-Wire Serial Interface 1st Address Pin (MAX3551/MAX3553)         13       SCL       3-Wire Serial Interface 1st Address Pin (MAX3551/MAX3553)         14       SDA       2-Wire Serial Interface Data Input Pin (SPI/OSPI/MICROWIRE Compatible) (MAX3550)         15       Vcc       Digital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         16       DIVLD       Divider or Lock-Detect Logic Output <td< td=""><td>1</td><td>V<sub>CC</sub></td><td></td></td<>                                            | 1                  | V <sub>CC</sub> |                                                                                                            |

| 20, 33,<br>24, 28,<br>32, 34, 45GNDGround. Connect to PC board ground plane.5Vcc1st Mixer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass<br>capacitor ground vias with any other branches.7Vcc1st VCO Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.8TUNE11st VCO Tuning Input. Connect this analog voltage input to a third-order loop-filter output.9LOCFLT11st UCO Tuning Input. Connect this analog voltage input to a third-order loop-filter output.111.C.Internal Connection. Leave this pin unconnected (MAX3550).111.C.Internal Connection. Leave this pin unconnected (MAX3550).12ADDR12-Wire Serial Interface 2nd Address Pin (MAX3551/MAX3553)13SCL3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)13SCL3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)14SDA3-Wire Serial Interface Data Input Pin (MAX3551/MAX3553)15VccbigItal Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.16DIV/LDDivider or Lock-Detect Logic Output17I.C.Interface Output, Connect this high-impedance current output to a third-order loop-filter input.19VccReference Oscillator Buffered Output11Is Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do no                                                                                                                              | 2, 3               |                 |                                                                                                            |

| 5         VCC         capacitor ground vias with any other branches.           7         Vcc         1st VCO Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.           8         TUNE1         1st VCO Tuning Input. Connect this analog voltage input to a third-order loop-filter output.           9         LOCFLT1         1st LO Noise-Filtering Capacitor Connection. Connect a capacitor to GND. (Refer to the EV kit.)           11         1.C.         Internal Connection. Leave this pin unconnected (MAX3550).           11         2.Wire Serial Interface 2nd Address Pin (MAX3551/MAX3553)           12         CS         3-Wire Serial Interface Enable Input Pin (SPI/MQSPI™/MICROWIRE™ Compatible) (MAX3550)           13         SCL         3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)           14         SDA         3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)           14         SDA         3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)           15         Vcc         Digital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.           16         DIV/LD         Divider or Lock-Detect Logic Output           17         I.C.         Internal Connection. Leave th                                                                                                                    | 20, 23,<br>24, 28, | GND             | Ground. Connect to PC board ground plane.                                                                  |

| 7       VCC       bypass capacitor ground vias with any other branches.         8       TUNE1       1st VCO Tuning Input. Connect this analog voltage input to a third-order loop-filter output.         9       LOCFLT1       1st LO Noise-Filtering Capacitor Connection. Connect a capacitor to GND. (Refer to the EV kit.)         11       I.C.       Internal Connection. Leave this pin unconnected (MAX3550).         11       I.C.       Internal Connection. Leave this pin unconnected (MAX3553).         12       CS       3-Wire Serial Interface 2nd Address Pin (MAX3551/MAX3553)         13       SCL       3-Wire Serial Interface Clock Input Pin (SPI/MQSPI™/MICROWIRET™ Compatible) (MAX3550)         13       SCL       3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         14       SDA       3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         15       Vcc       Digital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         16       DIV/LD       Divider or Lock-Detect Logic Output         17       I.C.       Internal Connection. Leave this pin unconnected.         18       CPOUT1       1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         21 <td>5</td> <td>V<sub>CC</sub></td> <td></td>                                                                                                                      | 5                  | V <sub>CC</sub> |                                                                                                            |

| 9       LOCFLT1       1st LO Noise-Filtering Capacitor Connection. Connect a capacitor to GND. (Refer to the EV kit.)         11       I.C.       Internal Connection. Leave this pin unconnected (MAX3550).         11       ADDR2       2-Wire Serial Interface 2nd Address Pin (MAX3551/MAX3553)         12       CS       3-Wire Serial Interface Enable Input Pin (SPI™/QSPI™/MICROWIRE™ Compatible) (MAX3550)         13       SCL       3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         13       SCL       3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         14       SDA       3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         14       SDA       3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         14       SDA       3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         15       Vcc       Digital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         16       DIV/LD       Divider or Lock-Detect Logic Output         17       I.C.       Internal Connection. Leave this pin unconnected.         18       CPOUT1       1st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.         19       V                                                                                                                                                                        | 7                  | V <sub>CC</sub> |                                                                                                            |

| 11       I.C.       Internal Connection. Leave this pin unconnected (MAX3550).         11       ADDR2       2-Wire Serial Interface 2nd Address Pin (MAX3551/MAX3553)         12       CS       3-Wire Serial Interface Enable Input Pin (SPI™/QSPI™/MICROWIRE™ Compatible) (MAX3550)         12       ADDR1       2-Wire Serial Interface 1st Address Pin (MAX3551/MAX3553)         13       SCL       3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         14       SDA       3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         14       SDA       3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         14       SDA       3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         15       Vcc       Digital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         16       DIV/LD       Divider or Lock-Detect Logic Output         17       I.C.       Internal Connection. Leave this pin unconnected.         18       CPOUT1       1st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.         19       Vcc       1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches. <td>8</td> <td>TUNE1</td> <td>1st VCO Tuning Input. Connect this analog voltage input to a third-order loop-filter output.</td>                    | 8                  | TUNE1           | 1st VCO Tuning Input. Connect this analog voltage input to a third-order loop-filter output.               |

| 11       ADDR2       2-Wire Serial Interface 2nd Address Pin (MAX3551/MAX3553)         12       CS       3-Wire Serial Interface Enable Input Pin (SPI™/QSPI™/MICROWIRE™ Compatible) (MAX3550)         13       SCL       3-Wire Serial Interface 1st Address Pin (MAX3551/MAX3553)         13       SCL       3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         14       SDA       3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         14       SDA       3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         15       Vcc       Digital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         16       DIV/LD       Divider or Lock-Detect Logic Output         17       I.C.       Internal Connection. Leave this pin unconnected.         18       CPOUT1       1st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.         19       Vcc       1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         21       OSCUT       Reference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a coupling capacitor.         22       OSCIN       Reference Oscillator                                                                                                                                       | 9                  | LOCFLT1         | 1st LO Noise-Filtering Capacitor Connection. Connect a capacitor to GND. (Refer to the EV kit.)            |

| ADDR22-Wire Serial Interface 2nd Address Pin (MAX3551/MAX3553)12 $\overline{CS}$ 3-Wire Serial Interface Enable Input Pin (SPI'M/QSPI'M/MICROWIRETM Compatible) (MAX3550)13 $ADDR1$ 2-Wire Serial Interface 1st Address Pin (MAX3551/MAX3553)13 $3CL$ $3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)143DA3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)143DA3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)143DA3-Wire Serial Interface Data Input Pin (MAX3551/MAX3553)15V_{CC}Digital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.16DIV/LDDivider or Lock-Detect Logic Output17I.C.Internal Connection. Leave this pin unconnected.18CPOUT11st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.19V_{CC}1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.21OSCOUTReference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a coupling capacitor.22V_{CC}2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor.23V_{CC}2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor.$                                                                                              | 44                 | I.C.            | Internal Connection. Leave this pin unconnected (MAX3550).                                                 |

| 12       ADDR1       2-Wire Serial Interface 1st Address Pin (MAX3551/MAX3553)         13       SCL       3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         14       SDA       3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         14       SDA       3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)         15       Vcc       Digital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         16       DIV/LD       Divider or Lock-Detect Logic Output         17       I.C.       Internal Connection. Leave this pin unconnected.         18       CPOUT1       1st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.         19       Vcc       Ist Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         21       OSCOUT       Reference Oscillator Buffered Output         22       OSCIN       Reference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a coupling capacitor.         25       Vcc       2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.                                                                                                                                 |                    | ADDR2           | 2-Wire Serial Interface 2nd Address Pin (MAX3551/MAX3553)                                                  |

| ADDR12-Wire Serial Interface 1st Address Pin (MAX3551/MAX3553)13SCL3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)14SDA3-Wire Serial Interface Clock Input Pin (MAX3551/MAX3553)14SDA3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)15VccDigital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.16DIV/LDDivider or Lock-Detect Logic Output17I.C.Internal Connection. Leave this pin unconnected.18CPOUT11st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.19Vcc1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.21OSCOUTReference Oscillator Buffered Output22OSCINReference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a<br>coupling capacitor.25Vcc2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                 | CS              | 3-Wire Serial Interface Enable Input Pin (SPI™/QSPI™/MICROWIRE™ Compatible) (MAX3550)                      |

| 13SCL2-Wire Serial Interface Clock Input Pin (MAX3551/MAX3553)14SDA3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)14SDA3-Wire Serial Interface Data Input Pin (MAX3551/MAX3553)15VccDigital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.16DIV/LDDivider or Lock-Detect Logic Output17I.C.Internal Connection. Leave this pin unconnected.18CPOUT11st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.19Vcc1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.21OSCOUTReference Oscillator Buffered Output22OSCINReference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a<br>coupling capacitor.25Vcc2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12                 | ADDR1           | 2-Wire Serial Interface 1st Address Pin (MAX3551/MAX3553)                                                  |

| 2-Wire Serial Interface Clock Input Pin (MAX3551/MAX3553)14SDA3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)15V <sub>CC</sub> Digital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.16DIV/LD17I.C.18CPOUT119V <sub>CC</sub> 11Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.19V <sub>CC</sub> 21OSCOUT22OSCINReference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a<br>coupling capacitor.25V <sub>CC</sub> 202nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.25V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                 | 0.01            | 3-Wire Serial Interface Clock Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)                          |

| 14SDA2-Wire Serial Interface Data Input Pin (MAX3551/MAX3553)15VccDigital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.16DIV/LDDivider or Lock-Detect Logic Output17I.C.Internal Connection. Leave this pin unconnected.18CPOUT11st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.19Vcc1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.21OSCOUTReference Oscillator Buffered Output22OSCINReference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a<br>coupling capacitor.25Vcc2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13                 | SCL             | 2-Wire Serial Interface Clock Input Pin (MAX3551/MAX3553)                                                  |

| 2-Wire Serial Interface Data Input Pin (MAX3551/MAX3553)15VccDigital Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.16DIV/LDDivider or Lock-Detect Logic Output17I.C.Internal Connection. Leave this pin unconnected.18CPOUT11st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.19Vcc1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.21OSCOUTReference Oscillator Buffered Output22OSCINReference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a<br>coupling capacitor.25Vcc2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    | 0.5.4           | 3-Wire Serial Interface Data Input Pin (SPI/QSPI/MICROWIRE Compatible) (MAX3550)                           |

| 15VCCbypass capacitor ground vias with any other branches.16DIV/LDDivider or Lock-Detect Logic Output17I.C.Internal Connection. Leave this pin unconnected.18CPOUT11st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.19Vcc1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.21OSCOUTReference Oscillator Buffered Output22OSCINReference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a<br>coupling capacitor.25Vcc2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14                 | SDA             | 2-Wire Serial Interface Data Input Pin (MAX3551/MAX3553)                                                   |

| 17I.C.Internal Connection. Leave this pin unconnected.18CPOUT11st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.19Vcc1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.21OSCOUTReference Oscillator Buffered Output22OSCINReference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a<br>coupling capacitor.25Vcc2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15                 | V <sub>CC</sub> |                                                                                                            |

| 18CPOUT11st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.19Vcc1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.21OSCOUTReference Oscillator Buffered Output22OSCINReference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a<br>coupling capacitor.25Vcc2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the<br>bypass capacitor ground vias with any other branches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16                 | DIV/LD          | Divider or Lock-Detect Logic Output                                                                        |

| 19       Vcc       1st Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.         21       OSCOUT       Reference Oscillator Buffered Output         22       OSCIN       Reference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a coupling capacitor.         25       Vcc       2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17                 | I.C.            | Internal Connection. Leave this pin unconnected.                                                           |

| 19       VCC       bypass capacitor ground vias with any other branches.         21       OSCOUT       Reference Oscillator Buffered Output         22       OSCIN       Reference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a coupling capacitor.         25       VCC       2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18                 | CPOUT1          | 1st PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input. |

| 22     OSCIN     Reference Oscillator Input. Connect an external reference oscillator or crystal to this analog input through a coupling capacitor.       25     V <sub>CC</sub> 2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19                 | V <sub>CC</sub> |                                                                                                            |

| 22     OSCIN     coupling capacitor.       25     V <sub>CC</sub> 2nd Synthesizer Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21                 | OSCOUT          | Reference Oscillator Buffered Output                                                                       |

| <sup>25</sup> VCC bypass capacitor ground vias with any other branches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                 | OSCIN           |                                                                                                            |

| 26 CPOUT2 2nd PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25                 | V <sub>CC</sub> |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                 | CPOUT2          | 2nd PLL Charge-Pump Output. Connect this high-impedance current output to a third-order loop-filter input. |

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

### \_Pin Description (continued)

| PIN    | NAME                | DESCRIPTION                                                                                                                                                                            |

|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27     | V <sub>CC</sub>     | 2nd Charge-Pump Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.                        |

| 29     | LOCFLT2             | 2nd LO Noise-Filtering Capacitor Connector. Connect a capacitor to GND. (Refer to the EV kit.)                                                                                         |

| 30     | TUNE2               | 2nd VCO Tuning Input. Connect this analog voltage input to a third-order loop-filter output.                                                                                           |

| 31     | V <sub>CC</sub>     | 2nd VCO Circuitry Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.                      |

| 33     | V <sub>CC</sub>     | 2nd LO Generation Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.                      |

| 35, 36 | IFOUT1+,<br>IFOUT1- | 1st Differential IF Outputs. These outputs are AC-coupled to the SAW filter inputs.                                                                                                    |

| 37     | V <sub>CC</sub>     | 2nd Mixer and 1st IF Amplifier Circuit Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches. |

| 38, 39 | IFIN+,<br>IFIN-     | Differential IF Inputs. Connected to the SAW filter outputs.                                                                                                                           |

| 40     | IFVGA               | IF VGA Control. See the Typical Operating Characteristics.                                                                                                                             |

| 41     | V <sub>CC</sub>     | IF VGA Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.                                 |

| 42, 43 | IFOUT2+,<br>IFOUT2- | IF VGA Outputs                                                                                                                                                                         |

| 44     | V <sub>CC</sub>     | HI-IF Filter Circuit Supply Voltage. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with any other branches.                   |

| 46     | BIAS                | Bias Resistor Connection. Connect a 5.9k $\Omega$ precision ±1% resistor to GND.                                                                                                       |

| 47     | RFVGA               | RF VGA Control. See the Typical Operating Characteristics.                                                                                                                             |

| 48     | LNABIAS             | LNA Bias Input. Connect through an inductor to GND. (Refer to the EV kit.)                                                                                                             |

| EP     | GND                 | Exposed Ground Paddle. DC and AC GND return for the IC. Connect to PC board ground plane using multiple vias.                                                                          |

### **Detailed Description**

#### **Programmable Registers**

The MAX3550/MAX3551/MAX3553 include nine programmable registers (registers 1–9) consisting of six divider registers (registers 1–6), one VCO control register (register 7), and one test register (register 8). The final register (register 9) controls the HI-IF filter frequency offset, as well as the DIV/LD output MUX status. Most registers contain some don't care (X) bits. These can be either a "0" or a "1" and do not affect the mode of operation (Table 1). Data is shifted in MSB first. Positive logic is used.

#### **3-Wire Serial Interface**

The MAX3550 uses a 3-wire SPI/QSPI/MICROWIREcompatible serial interface. An active-low chip select ( $\overline{CS}$ ) enables the device to receive data from the serial input (SDA). Register address and data information are clocked in on the rising edge of the serial clock signal (SCL). While shifting in the serial data, the device remains in its original configuration. A rising edge on  $\overline{CS}$  latches the data into the MAX3550's internal register, initiating the device's change of state. Figure 1 shows the details of the 3-wire interface address and data configuration.

#### **2-Wire Serial Interface**

The MAX3551/MAX3553 use a 2-wire I<sup>2</sup>C-compatible serial interface. The serial bus is monitored continuously, waiting for a START condition followed by its address. The address has 5 MSB internally set, while the next two bits are set with external pins, ADDR2 and ADDR1. The LSB determines whether it is a read or write. When the device recognizes its address, it acknowledges by pulling the SDA line low for one clock period; it is then ready to accept the register address for the first byte of data. Another acknowledge (ACK) is sent once the register address is received. The device is then ready to accept the data byte. More data bytes can be sent for sequential registers, and ACK is sent after each byte. After the final ACK is sent, the master issues a STOP condition to free the bus. Figure 2 shows the details of the 2-wire interface structure.

There is only one read-back register in the MAX3551/MAX3553. To access it, send a START condition, and then the read address is set by the external ADDR2 and ADDR1 pins. An ACK is sent, and the master then begins to read from the slave. After the eight bits have been read, the master should issue a no-acknowledge (NACK), and then a STOP condition.

#### Figure 1. 3-Wire Serial Interface Address and Data Configuration

| MSB |                         |    |    |    |    |        |    |    |    |    | LSB |

|-----|-------------------------|----|----|----|----|--------|----|----|----|----|-----|

|     | 4 ADDRESS BITS 8 DATA B |    |    |    |    | A BITS |    |    |    |    |     |

| A3  | A2                      | A1 | A0 | D7 | D6 | D5     | D4 | D3 | D2 | D1 | D0  |

#### Figure 2. 2-Wire Serial Interface Register Write Example

| STADT | DEVICE ADDRESS                          |     | REGISTER ADDRESS |     | DATA  | ACK | DATA  |     | STOP |

|-------|-----------------------------------------|-----|------------------|-----|-------|-----|-------|-----|------|

| START | 8b11000 <addr2><addr1>0</addr1></addr2> | ACK | 8b0000XXXX       | ACK | D7-D0 | ACK | D7-D0 | AUN | 310P |

#### Figure 3. 2-Wire Serial Interface Register Read Example

| START | DEVICE ADDRESS                          | ЛСК | READ BYTE (8 Bits) | NACK | STOP |

|-------|-----------------------------------------|-----|--------------------|------|------|

| SIANI | 8b11000 <addr2><addr1>1</addr1></addr2> | ACK | 8bXXXXXXXX         | NACK | 310P |

# Table 1. 2-Wire Serial Interface AddressConfiguration (Set by ADDR2 andADDR1)

| ADDRESS (WRITE/READ) | ADDR2 | ADDR1 |

|----------------------|-------|-------|

| C0/C1 <sub>hex</sub> | Low   | Low   |

| C2/C3 <sub>hex</sub> | Low   | High  |

| C4/C5 <sub>hex</sub> | High  | Low   |

| C6/C7 <sub>hex</sub> | High  | High  |

I<sup>2</sup>C is a trademark of Philips Corp.

| DEGISTER           |                  |                     | MSB   |       |       |       |        |      |      | LSB  |

|--------------------|------------------|---------------------|-------|-------|-------|-------|--------|------|------|------|

| REGISTER<br>NUMBER | REGISTER<br>NAME | REGISTER<br>ADDRESS |       |       |       | 8 DAT | A BITS |      |      |      |

| NOMBER             |                  | ADDITEOU            | D7    | D6    | D5    | D4    | D3     | D2   | DB1  | D0   |

| 1                  | VCO1_N1          | 00 <sub>hex</sub>   | Х     | Х     | Х     | 1N12  | 1N11   | 1N10 | 1N9  | 1N8  |

| 2                  | VCO1_N2          | 01 <sub>hex</sub>   | 1N7   | 1N6   | 1N5   | 1N4   | 1N3    | 1N2  | 1N1  | 1N0  |

| 3                  | VCO1_R           | 02 <sub>hex</sub>   | Х     | Х     | Х     | 1R4   | 1R3    | 1R2  | 1R1  | 1R0  |

| 4                  | VCO2_N1          | 03 <sub>hex</sub>   | 2N15  | 2N14  | 2N13  | 2N12  | 2N11   | 2N10 | 2N9  | 2N8  |

| 5                  | VCO2_N2          | 04 <sub>hex</sub>   | 2N7   | 2N6   | 2N5   | 2N4   | 2N3    | 2N2  | 2N1  | 2N0  |

| 6                  | VCO2_R           | 05 <sub>hex</sub>   | Х     | 2R6   | 2R5   | 2R4   | 2R3    | 2R2  | 2R1  | 2R0  |

| 7                  | VCO_SET          | 06 <sub>hex</sub>   | 1VCO2 | 1VCO1 | 1VCO0 | Х     | 1CP1   | 1CP0 | 2CP1 | 2CP0 |

| 8                  | TEST             | 07 <sub>hex</sub>   | Х     | 1T4   | 1T3   | 1T2   | 1T1    | 1T0  | ST1  | ST0  |

| 9                  | HI-IF            | 08 <sub>hex</sub>   | Х     | Х     | F1    | FO    | MUX3   | MUX2 | MUX1 | MUX0 |

#### Table 2. Register Configuration

X = Don't care.

### Table 3. Register Description

| REGISTER<br>NUMBER | REGISTER<br>NAME | REGISTER<br>ADDRESS | FUNCTION                                           |

|--------------------|------------------|---------------------|----------------------------------------------------|

| 1                  | VCO1_N1          | 00 <sub>hex</sub>   | VCO1 N divide high                                 |

| 2                  | VCO1_N2          | 01 <sub>hex</sub>   | VCO1 N divide low                                  |

| 3                  | VCO1_R           | 02 <sub>hex</sub>   | VCO1 R divide                                      |

| 4                  | VCO2_N1          | 03 <sub>hex</sub>   | VCO2 N divide high                                 |

| 5                  | VCO2_N2          | 04 <sub>hex</sub>   | VCO2 N divide low                                  |

| 6                  | VCO2_R           | 05 <sub>hex</sub>   | VCO2 R divide                                      |

| 7                  | VCO_SET          | 06 <sub>hex</sub>   | VCO select and charge-pump settings                |

| 8                  | TEST             | 07 <sub>hex</sub>   | Test mode. For test purposes only. Default = 20hex |

| 9                  | HI-IF            | 08 <sub>hex</sub>   | Mode select, MUX output select                     |

### Table 4. 1st VCO N-Divider Higher Register (VCO1\_N1)

| BIT ID | BIT NAME          | BIT LOCATION (0 = LSB) | FUNCTION                   |

|--------|-------------------|------------------------|----------------------------|

| Х      | Х                 | 7–5                    | Reserved                   |

| 1N     | 1st VCO N-Divider | 4–0                    | 1st VCO N-divider MSB bits |

### Table 5. 1st VCO N-Divider Lower Register (VCO1\_N2)

| BIT ID | BIT NAME          | BIT LOCATION (0 = LSB) | FUNCTION                   |

|--------|-------------------|------------------------|----------------------------|

| 1N     | 1st VCO N-Divider | 7–0                    | 1st VCO N-divider LSB bits |

### Table 6. 1st VCO R-Divider Higher Register (VCO1\_R)