# FMS7950 Clock Multiplier

#### **Features**

- · Crystal reference input

- Up to 175 MHz of output frequency

- Nine configurable outputs

- · Output enable pin

- 250 pS of output to output skew

- 300 pS of Cycle to Cycle Jitter

- V<sub>DD</sub> Range of 3.3V ±0.2V

- · Commercial temperature range

- Available in 32 pin LQFP

## **Description**

FMS7950 is a high speed clock synthesizer designed for clock multiplication applications. It uses phase locked loop technology to generate frequencies up to 175 MHz. It has four banks of configurable outputs.

Feedback select (FBsel) pin allows for wider range of input frequencies. When connected low, the lower input frequency range is selected. This provides output frequencies of up to eight times the input (see table 3). The higher input range is allowed when FBsel is connected high.

There are four banks of outputs where each bank has a dedicated divide select (DIV\_SEL). Depending on the divide selection, the outputs are one half, one quarter, or one eighth of the VCO speed (see table 2 for details).

REF\_SEL allows selection between crystal input or a clock driven input. Connecting PLL\_EN LOW and REF\_SEL HIGH will disable the Phase locked loop when the crystal oscillator is not used. In this mode, FMS7950 will be in clock buffer mode where any clock applied to TCLK will be divided down to the four output banks per Table 2. This is ideal for system diagnostic test.

FMS7950 operates at 3.3 Volts and is available in 32 pin LQFP.

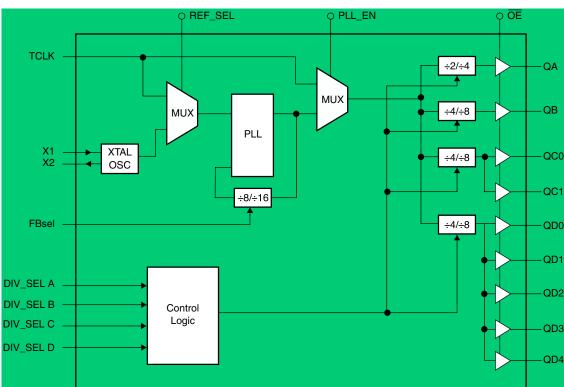

# **Block Diagram**

# **Pin Assignments**

# **Pin Description**

| Pin Name                                                                        | Pin #                                 | Pin Type | Description                                                                                                                                                                                             |

|---------------------------------------------------------------------------------|---------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDCOR                                                                          | 1                                     | PWR      | <b>Power Connection.</b> Power supply for core logic and PLL circuitry. Connect to 3.3 Volts nominal.                                                                                                   |

| FBsel                                                                           | 2                                     | IN       | <b>Feedback Select.</b> When high, the feedback divide is 8, and when low, it is 16. It allows for a wider range of input frequencies.                                                                  |

| DIV_SEL(A:D)                                                                    | 3, 4, 5, 6                            | IN       | <b>Divider Select:</b> It divides the clock to a desirable value. See table 2.                                                                                                                          |

| GNDCOR                                                                          | 7                                     | PWR      | <b>Ground Connection.</b> Ground for core logic and PLL circuitry. Connect to the common system ground plane.                                                                                           |

| X1                                                                              | 8                                     | IN       | <b>Crystal Connection.</b> An input connection for an external crystal or oscillator. 18 pF internal cap. It can be used as an external crystal connection or as an external reference frequency input. |

| X2                                                                              | 9                                     | OUT      | <b>Crystal Connection or External Reference Frequency.</b> This pin has dual functions.                                                                                                                 |

| ŌĒ                                                                              | 10                                    | IN       | Output Enable. When high, all outputs are in high impedance. Normal operation when asserted low.                                                                                                        |

| VDDOUT                                                                          | 11, 15, 19, 23, 27                    | PWR      | <b>Power Connection.</b> Power supply for all the output buffers. Connect to 3.3 Volts nominal.                                                                                                         |

| Q <sub>A</sub> ; Q <sub>B</sub> ; Q <sub>C</sub> (0:1);<br>Q <sub>D</sub> (0:4) | 12, 14, 16, 18, 20,<br>22, 24, 26, 28 | OUT      | Clock Outputs. These outputs are multiple of the input.                                                                                                                                                 |

| GNDOUT                                                                          | 13, 17, 21, 25, 29                    | PWR      | <b>Ground Connection.</b> Ground for all the outputs. Connect to common system ground plane.                                                                                                            |

| TCLK                                                                            | 30                                    | IN       | <b>Test Clock.</b> When REF_SEL is high, all outputs are buffer copy of TCLK. When REF_SEL is low, TCLK is disabled.                                                                                    |

| PLL_EN                                                                          | 31                                    | IN       | PLL Enable. When low, PLL is bypassed.                                                                                                                                                                  |

| REF_SEL                                                                         | 32                                    | IN       | <b>Reference Select.</b> When low, crystal is used for input. When high, TCLK is used for input.                                                                                                        |

FMS7950 PRODUCT SPECIFICATION

**Table 1. Functionality**

| REF_SEL | PLL_EN | ŌĒ | PLL     | All Outputs | Input |

|---------|--------|----|---------|-------------|-------|

| 0       | 0      | 1  | By Pass | Hi-Z        | XTAL  |

| 0       | 0      | 0  | By Pass | Running     | XTAL  |

| 0       | 1      | 0  | Enabled | Running     | XTAL  |

| 1       | 0      | 1  | By Pass | Hi-Z        | TCLK  |

| 1       | 0      | 0  | By Pass | Running     | TCLK  |

| 1       | 1      | 0  | Enabled | Running     | TCLK  |

**Table 2. Input Versus Output Frequency**

|           |           |           |           |       | FBsel = 1 |       |       |       | FBse  | el = 0 |       |

|-----------|-----------|-----------|-----------|-------|-----------|-------|-------|-------|-------|--------|-------|

| DIV_SEL A | DIV_SEL B | DIV_SEL C | DIV_SEL D | QA    | QB        | QC    | QD    | QA    | QB    | QC     | QD    |

| 0         | 0         | 0         | 0         | 4XRef | 2XRef     | 2XRef | 2XRef | 8XRef | 4XRef | 4XRef  | 4XRef |

| 0         | 0         | 0         | 1         | 4XRef | 2XRef     | 2XRef | Ref   | 8XRef | 4XRef | 4XRef  | 2XRef |

| 0         | 0         | 1         | 0         | 4XRef | 2XRef     | Ref   | 2XRef | 8XRef | 4XRef | 2XRef  | 4XRef |

| 0         | 0         | 1         | 1         | 4XRef | 2XRef     | Ref   | Ref   | 8XRef | 4XRef | 2XRef  | 2XRef |

| 0         | 1         | 0         | 0         | 4XRef | Ref       | 2XRef | 2XRef | 8XRef | 2XRef | 4XRef  | 4XRef |

| 0         | 1         | 0         | 1         | 4XRef | Ref       | 2XRef | Ref   | 8XRef | 2XRef | 4XRef  | 2XRef |

| 0         | 1         | 1         | 0         | 4XRef | Ref       | Ref   | 2XRef | 8XRef | 2XRef | 2XRef  | 4XRef |

| 0         | 1         | 1         | 1         | 4XRef | Ref       | Ref   | Ref   | 8XRef | 2XRef | 2XRef  | 2XRef |

| 1         | 0         | 0         | 0         | 2XRef | 2XRef     | 2XRef | 2XRef | 4XRef | 4XRef | 4XRef  | 4XRef |

| 1         | 0         | 0         | 1         | 2XRef | 2XRef     | 2XRef | Ref   | 4XRef | 4XRef | 4XRef  | 2XRef |

| 1         | 0         | 1         | 0         | 2XRef | 2XRef     | Ref   | 2XRef | 4XRef | 4XRef | 2XRef  | 4XRef |

| 1         | 0         | 1         | 1         | 2XRef | 2XRef     | Ref   | Ref   | 4XRef | 4XRef | 2XRef  | 2XRef |

| 1         | 1         | 0         | 0         | 2XRef | Ref       | 2XRef | 2XRef | 4XRef | 2XRef | 4XRef  | 4XRef |

| 1         | 1         | 0         | 1         | 2XRef | Ref       | 2XRef | Ref   | 4XRef | 2XRef | 4XRef  | 2XRef |

| 1         | 1         | 1         | 0         | 2XRef | Ref       | Ref   | 2XRef | 4XRef | 2XRef | 2XRef  | 4XRef |

| 1         | 1         | 1         | 1         | 2XRef | Ref       | Ref   | Ref   | 4XRef | 2XRef | 2XRef  | 2XRef |

#### Note:

**Table 3. Divide Select Functionality**

| DIV_SEL A | DIV_SEL B | DIV_SEL D | DIV_SEL D | QA | QB | QC | QD |

|-----------|-----------|-----------|-----------|----|----|----|----|

| 0         | 0         | 0         | 0         | ÷2 | ÷4 | ÷4 | ÷4 |

| 1         | 1         | 1         | 1         | ÷4 | ÷8 | ÷8 | ÷8 |

<sup>1.</sup> Reference input could be either crystal input or TCLK input.

## **Absolute Maximum Ratings**

| Symbol                            | Parameter                                 | Ratings     | Units |

|-----------------------------------|-------------------------------------------|-------------|-------|

| V <sub>DD</sub> , V <sub>IN</sub> | Voltage on any pin with respect to ground | -0.5 to 7.0 | V     |

| T <sub>STG</sub>                  | Storage Temperature                       | -65 to 150  | °C    |

| T <sub>B</sub>                    | Ambient Temperature                       | -55 to 125  | °C    |

| T <sub>A</sub>                    | Operating Temperature                     | 0 to 70     | °C    |

Stresses greater than those listed in the table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may effect reliability.

### **DC Electrical Characteristics**

$T_A = 0$  to 70°C; Supply Voltage 3.3 V ±0.2V (unless otherwise stated)

| Parameter                          | Symbol          | Conditions                               | Min. | Тур. | Max. | Units |

|------------------------------------|-----------------|------------------------------------------|------|------|------|-------|

| Input Low Voltage                  | V <sub>IL</sub> |                                          |      |      | 0.8  | V     |

| Input High Voltage                 | ViH             |                                          | 2.0  |      |      | V     |

| Input Low Current                  | I <sub>IL</sub> | V <sub>IN</sub> = 0                      | -10  |      | 10   | μΑ    |

| Input High Current                 | Іін             | V <sub>IN</sub> = V <sub>DD</sub>        | -30  |      | 30   | μΑ    |

| Output Low Voltage                 | V <sub>OL</sub> | I <sub>OL</sub> = 40 mA                  |      |      | 0.5  | V     |

| Output High Voltage                | Voн             | I <sub>OH</sub> = -40mA                  | 2.2  |      |      | V     |

| Input Capacitance <sup>(1)</sup>   | C <sub>IN</sub> |                                          |      |      | 7.0  | pF    |

| Supply Current                     | I <sub>DD</sub> | Outputs loaded                           |      |      | 200  | mA    |

| Clock Stabilization <sup>(1)</sup> | TSTAB           | From V <sub>DD</sub> = 3.3V to 1% Target |      |      | 10   | mS    |

#### Note:

### **AC Electrical Characteristics**

$T_A = 0$  to  $70^{\circ}$ C; Supply Voltage  $V_{DD} = 3.3V \pm 0.2V$ ,  $C_L = 10$  pF (unless otherwise stated)

| Parameter                 | Symbol           | Conditions                                                                 | Min. | Тур. | Max. | Units |

|---------------------------|------------------|----------------------------------------------------------------------------|------|------|------|-------|

| Input Frequency Range     | FINPUT           | FBsel = 1                                                                  | 25   |      | 43   | MHz   |

|                           |                  | FBsel = 0                                                                  | 12   |      | 22   | MHz   |

| Output Frequency Range    | Fout             | Q <sub>A</sub> ; DIV_SEL A = 0V                                            |      |      | 175  | MHz   |

|                           |                  | Q <sub>B</sub> , Q <sub>C</sub> & Q <sub>D</sub> ;<br>DIV_SEL B, C, D = 0V |      |      | 88   | MHz   |

| Output to Output Skew     | T <sub>SK1</sub> | V <sub>TH</sub> = V <sub>DD</sub> /2; DIV_SEL A = 0                        |      | 400  | 750  | pS    |

|                           |                  | V <sub>TH</sub> = V <sub>DD</sub> /2; DIV_SEL A = 1                        | -300 | 100  | 300  |       |

| Rise Time <sup>(1)</sup>  | T <sub>R</sub>   | 0.8 to 2.0V                                                                | 0.10 |      | 1.0  | nS    |

| Fall Time <sup>(1)</sup>  | T <sub>F</sub>   | 2.0 to 0.8V                                                                | 0.10 |      | 1.0  | nS    |

| Duty Cycle <sup>(1)</sup> | DT               | $V_{TH} = V_{DD}/2$                                                        | 45   |      | 55   | %     |

| Jitter (Cycle-Cycle)      | TJIT             | QA: DIV_SEL A = 0                                                          |      |      | 450  | pS    |

|                           |                  | QA: DIV_SEL A = 1                                                          |      |      | 200  |       |

|                           |                  | QB Output                                                                  |      |      | 200  |       |

|                           |                  | QC(0:1) Outputs                                                            |      |      | 300  |       |

|                           |                  | QD(0:4) Outputs                                                            |      |      | 375  |       |

#### Note:

<sup>1.</sup> Guaranteed by design, not subject to 100% production testing.

<sup>1.</sup> Guaranteed by design, not subject to 100% production testing.

FMS7950 PRODUCT SPECIFICATION

# **Parameter Measurement Information**

# Duty Cycle (D<sub>T</sub>)

## Rise/Fall Time (T<sub>R</sub>/T<sub>F</sub>)

# Output to Output Skew (T<sub>SK1</sub>)

### **Application**

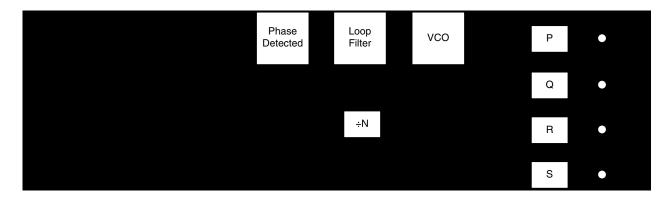

FMS7950 is one of the simplest form of frequency synthesizer. It uses phase locked loop technology with a divide of "N" in its feedback path. Its purpose is to generate a large number of different output frequencies, all related to a single, highly stable reference source. To achieve this, a crystal is connected at X1 and X2. No external components are required since the capacitors and oscillator are integrated.

Figure 1 depicts the block diagram for FMS7950.

Figure 1.

In general, phase locked loops are governed by the equation:

$$F_{OUT} = N \bullet F_{REF}$$

Equation 1

Equation 1 states that any output can be generated if "N" is varied. In FMS7950, the available dividers are eight or sixteen. These values are selected by connecting FBsel to ground or VDD. To determine the allowable range of input frequencies for each different FBsel setting, the following equation must be used:

$$F_{REF} = F_{VCO} \div N$$

Equation 2

If divided by eight is selected, the minimum input range will be:

$$F_{REF\_MIN} = 200 \div 8$$

$$= 25 \text{ MHZ}$$

The maximum input range:

$$F_{REF\_MAX} = 360 \div 8$$

$$= 43.75 \text{ MHZ}$$

If divide by sixteen is selected, a lower range of input frequency is allowed (12.5–22MHZ). This analysis reveals that if lower input frequency is available, FBsel must be connected to GND. On the other hand, higher input frequencies require FBsel to be connected to VDD.

In practical applications, it is always the output frequency that is known and one must work backwards to determine the input and VCO frequencies. The best approach to explain is by an example. Assume an application requires the following output frequencies:

QA = 133.33 MHZ QB = 66.66 MHZ QC & QD = 33.33 MHZ

FMS7950 PRODUCT SPECIFICATION

The following connection is used:

To calculate the VCO frequency, we find the output that requires the highest frequency and used the following equation. In this case, it will be QA output.

$$F_{VCO} = P \cdot QA$$

= 2 \cdot 133.33 MHZ

= 266.66 MHZ

To determine the input frequency, we will use Equation 2, and set "N" to 16:

$$F_{REF} = 266.66 \text{ MHZ} \div 16$$

= 16.66 MHZ

Note, divide by eight could also have been used. The only difference is that it would require an input clock of 33.33MHZ rather than 16.66MHZ.

# **Mechanical Dimensions**

### 32-Pin LQFP

### **Ordering Information**

| Product Number | Package Description | Package Marking |  |  |

|----------------|---------------------|-----------------|--|--|

| FMS7950KWC     | LQFP-32             | 7950KWC         |  |  |

| FMS7950KWCX    | LQFP-32 w/T+R       | 7950KWC         |  |  |

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### Features

- Crystal reference input

- Up to 175 MHz of output frequency

- Nine configurable outputs

- Output enable pin

- 250 pS of output to output skew

- 300 pS of Cycle to Cycle Jitter

- $V_{DD}$  Range of  $3.3V \pm 0.2V$

- Commercial temperature range

- Available in 32 pin LQFP

### back to top

### Product status/pricing/packaging

| Product     | Product status  | Pricing* | Package type | Leads | Package<br>marking | Packing<br>method |

|-------------|-----------------|----------|--------------|-------|--------------------|-------------------|

| FMS7950KWC  | Full Production | \$5.71   | QFP          | 32    | \$G                | TRAY              |

| FMS7950KWCT | Full Production | \$5.71   | QFP          | 32    | \$G                | TAPE REEL         |

<sup>\* 1,000</sup> piece Budgetary Pricing

### back to top

#### Models

| Package & leads | Condition | Temperature range | Vcc range    | Software version | <b>Revision date</b> |

|-----------------|-----------|-------------------|--------------|------------------|----------------------|

| IBIS            |           |                   |              |                  |                      |

| QFP-32          | Typical   | 0°C to 70°C       | 3.1V to 3.5V | 2.1              | Nov 13, 2000         |

### back to top

<u>Home</u> | <u>Find products</u> | <u>Technical information</u> | <u>Buy products</u> | Support | Company | Contact us | Site index | Privacy policy

© Copyright 2002 Fairchild Semiconductor