# TSB82AA2-EP 1394b OHCI-Lynx Controller Data Manual

Literature Number: SCPS167A September 2006

## **Contents**

| Se | ction  | Title                                            | Page |

|----|--------|--------------------------------------------------|------|

| 1  | Introd | uction                                           | 1-1  |

|    | 1.1    | Description                                      | 1-1  |

|    | 1.2    | Features                                         | 1-3  |

|    | 1.3    | Related Documents                                | 1-4  |

|    | 1.4    | Trademarks                                       | 1-4  |

|    | 1.5    | Ordering Information                             | 1-4  |

|    | 1.6    | TSB82AA2-EP Data Manual Document History         | 1-4  |

| 2  | Termi  | nal Descriptions                                 | 2-1  |

| 3  | TSB82  | 2AA2 Controller Programming Model                | 3-1  |

|    | 3.1    | PCI Configuration Registers                      | 3-3  |

|    | 3.2    | Vendor ID Register                               | 3-4  |

|    | 3.3    | Device ID Register                               | 3-4  |

|    | 3.4    | Command Register                                 | 3-5  |

|    | 3.5    | Status Register                                  | 3-6  |

|    | 3.6    | Class Code and Revision ID Register              | 3-7  |

|    | 3.7    | Latency Timer and Class Cache Line Size Register | 3-7  |

|    | 3.8    | Header Type and BIST Register                    | 3-8  |

|    | 3.9    | OHCI Base Address Register                       | 3-8  |

|    | 3.10   | TI Extension Base Address Register               | 3-9  |

|    | 3.11   | CardBus Cis Base Address Register                | 3-10 |

|    | 3.12   | CardBus CIS Pointer Register                     | 3-11 |

|    | 3.13   | Subsystem Identification Register                | 3-12 |

|    | 3.14   | Power Management Capabilities Pointer Register   | 3-12 |

|    | 3.15   | Interrupt Line and Pin Register                  | 3-13 |

|    | 3.16   | MIN_GNT and MAX_LAT Register                     | 3-13 |

|    | 3.17   | OHCI Control Register                            | 3-14 |

|    | 3.18   | Capability ID and Next Item Pointer Register     | 3-14 |

|    | 3.19   | Power Management Capabilities Register           | 3-15 |

|    | 3.20   | Power Management Control and Status Register     | 3-16 |

|    | 3.21   | Power Management Extension Register              | 3-16 |

|    | 3.22   | Multifunction Select Register                    |      |

|    | 3.23   | Miscellaneous Configuration Register             | 3-18 |

|    | 3.24   | Link Enhancement Control Register                | 3-19 |

|    | 3.25   | Subsystem Access Register                        | 3-21 |

|    | 3.26   | GPIO Control Register                            | 3-22 |

| 4  | OHCI   | Registers                                        |      |

|    | 4.1    | OHCI Version Register                            | 4-4  |

| 4.2  | GUID ROM Register                                     | 4-5  |

|------|-------------------------------------------------------|------|

| 4.3  | Asynchronous Transmit Retries Register                | 4-6  |

| 4.4  | CSR Data Register                                     | 4-6  |

| 4.5  | CSR Compare Register                                  | 4-7  |

| 4.6  | CSR Control Register                                  | 4-7  |

| 4.7  | Configuration ROM Header Register                     | 4-8  |

| 4.8  | Bus Identification Register                           | 4-8  |

| 4.9  | Bus Options Register                                  | 4-9  |

| 4.10 | GUID High Register                                    | 4-10 |

| 4.11 | GUID Low Register                                     | 4-10 |

| 4.12 | Configuration ROM Mapping Register                    | 4-11 |

| 4.13 | Posted Write Address Low Register                     | 4-11 |

| 4.14 | Posted Write Address High Register                    | 4-12 |

| 4.15 | Vendor ID Register                                    | 4-13 |

| 4.16 | Host Controller Control Register                      | 4-14 |

| 4.17 | Self-ID Buffer Pointer Register                       | 4-15 |

| 4.18 | Self-ID Count Register                                | 4-16 |

| 4.19 | Isochronous Receive Channel Mask High Register        | 4-17 |

| 4.20 | Isochronous Receive Channel Mask Low Register         | 4-18 |

| 4.21 | Interrupt Event Register                              | 4-19 |

| 4.22 | Interrupt Mask Register                               | 4-21 |

| 4.23 | Isochronous Transmit Interrupt Event Register         | 4-23 |

| 4.24 | Isochronous Transmit Interrupt Mask Register          | 4-24 |

| 4.25 | Isochronous Receive Interrupt Event Register          | 4-25 |

| 4.26 | Isochronous Receive Interrupt Mask Register           | 4-26 |

| 4.27 | Initial Bandwidth Available Register                  | 4-26 |

| 4.28 | Initial Channels Available High Register              | 4-27 |

| 4.29 | Initial Channels Available Low Register               | 4-27 |

| 4.30 | Fairness Control Register                             | 4-28 |

| 4.31 | Link Control Register                                 | 4-29 |

| 4.32 | Node Identification Register                          | 4-30 |

| 4.33 | PHY Layer Control Register                            | 4-31 |

| 4.34 | Isochronous Cycle Timer Register                      | 4-32 |

| 4.35 | Asynchronous Request Filter High Register             | 4-33 |

| 4.36 | Asynchronous Request Filter Low Register              | 4-35 |

| 4.37 | Physical Request Filter High Register                 | 4-36 |

| 4.38 | Physical Request Filter Low Register                  | 4-38 |

| 4.39 | Physical Upper Bound Register (Optional Register)     | 4-38 |

| 4.40 | Asynchronous Context Control Register                 | 4-39 |

| 4.41 | Asynchronous Context Command Pointer Register         | 4-40 |

| 4.42 | Isochronous Transmit Context Control Register         | 4-41 |

| 4.43 | Isochronous Transmit Context Command Pointer Register | 4-42 |

| 4.44 | Isochronous Receive Context Control Register          |      |

| 4.45 | Isochronous Receive Context Command Pointer Register  | 4-44 |

|   | 4.46        | Isochronous Receive Context Match Register                       | 4-45 |

|---|-------------|------------------------------------------------------------------|------|

| 5 | TI Ext      | ension Registers                                                 | 5-1  |

|   | 5.1         | DV Timestamp Enhancements                                        | 5-1  |

|   | 5.2         | MPEG2 Timestamp Procedure                                        | 5-1  |

|   | 5.3         | Isochronous Receive Digital Video Enhancements                   | 5-2  |

|   | 5.4         | Isochronous Receive Digital Video Enhancements Register          | 5-2  |

|   | 5.5         | Link Enhancement Register                                        | 5-4  |

|   | 5.6         | Timestamp Offset Register                                        | 5-6  |

| 6 | <b>GPIO</b> | Interface                                                        | 6-1  |

| 7 | Serial      | EEPROM Interface                                                 | 7-1  |

| 8 | Electr      | ical Characteristics                                             | 8-1  |

|   | 8.1         | Absolute Maximum Ratings Over Operating Temperature Ranges .     | 8-1  |

|   | 8.2         | Recommended Operating Conditions                                 | 8-2  |

|   | 8.3         | Electrical Characteristics Over Recommended Operating Conditions | 8-3  |

|   | 8.4         | Switching Characteristics for PCI Interface                      | 8-3  |

|   | 8.5         | Switching Characteristics for PHY-Link Interface                 | 8-3  |

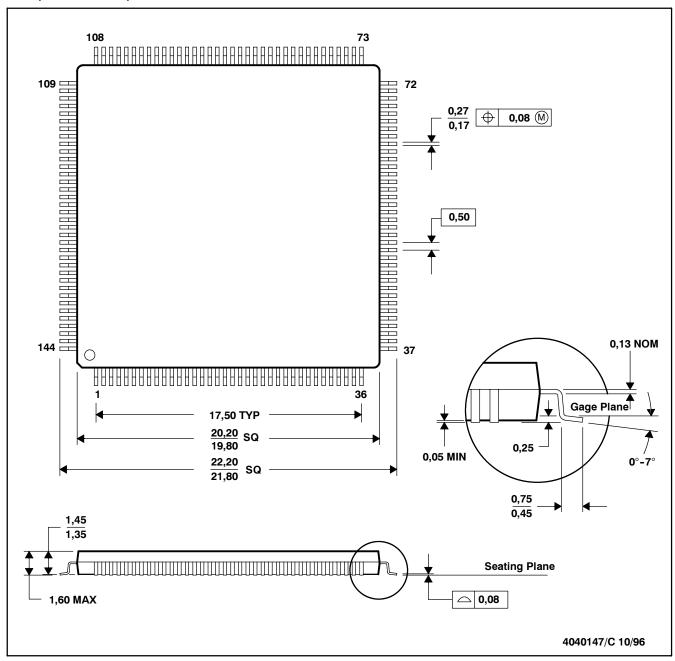

| 9 | Mecha       | anical Information                                               | 9-1  |

## **List of Illustrations**

| Figure | Title                  | Page |

|--------|------------------------|------|

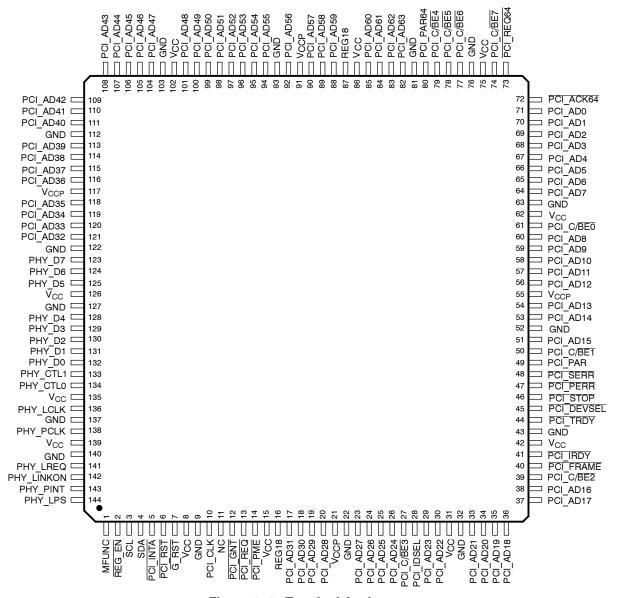

| 2-1    | Terminal Assignments   | 2-1  |

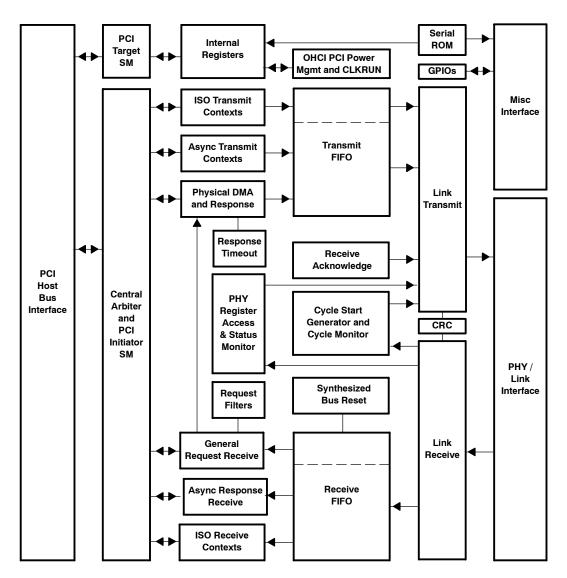

| 3-1    | TSB82AA2 Block Diagram | 3-2  |

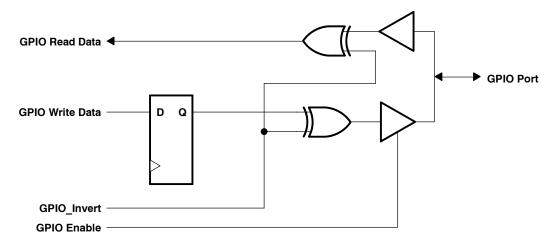

| 6-1    | GPIO Logic Diagram     | 6-1  |

## **List of Tables**

| Table | Title                                                        | Page   |

|-------|--------------------------------------------------------------|--------|

| 2-1   | Signals Sorted by Terminal Number                            | . 2-2  |

| 2-2   | Signal Names Sorted Alphanumerically to Terminal Number      | . 2-3  |

| 2-3   | Power Supply Terminals                                       | . 2-4  |

| 2-4   | Reset and Miscellaneous Terminals                            |        |

| 2-5   | 32-Bit PCI Bus Terminals                                     | . 2-5  |

| 2-6   | PCI 64-Bit Bus Extension Terminals                           |        |

| 2-7   | PHY-Link Interface Terminals                                 | . 2-8  |

| 3-1   | Bit Field Access Tag Descriptions                            | . 3-1  |

| 3-2   | PCI Configuration Register Map                               | . 3-3  |

| 3-3   | Command Register Description                                 | . 3-5  |

| 3-4   | Status Register Description                                  | . 3-6  |

| 3-5   | Class Code and Revision ID Register Description              | . 3-7  |

| 3-6   | Latency Timer and Class Cache Line Size Register Description | . 3-7  |

| 3-7   | Header Type and BIST Register Description                    | . 3-8  |

| 3-8   | OHCI Base Address Register Description                       | . 3-8  |

| 3-9   | TI Base Address Register Description                         | . 3-9  |

| 3-10  | CardBus CIS Base Address Register Description                | . 3-10 |

| 3-11  | CardBus CIS Pointer Register Description                     | . 3-11 |

| 3-12  | Subsystem Identification Register Description                | . 3-12 |

| 3-13  | Interrupt Line and Pin Register Description                  | . 3-13 |

| 3-14  | MIN_GNT and MAX_LAT Register Description                     | . 3-13 |

| 3-15  | OHCI Control Register Description                            | . 3-14 |

| 3-16  | Capability ID and Next Item Pointer Register Description     | . 3-14 |

| 3-17  | Power Management Capabilities Register Description           | . 3-15 |

| 3-18  | Power Management Control and Status Register Description     | . 3-16 |

| 3-19  | Power Management Extension Register Description              | . 3-16 |

| 3-20  | Multifunction Select Register                                | . 3-17 |

| 3-21  | Miscellaneous Configuration Register                         | . 3-18 |

| 3-22  | Link Enhancement Control Register Description                | . 3–19 |

| 3-23  | Subsystem Access Register Description                        | . 3-21 |

| 3-24  | GPIO Control Register Description                            | . 3-22 |

| 4-1   | OHCI Register Map                                            | . 4-1  |

| 4-2   | OHCI Version Register Description                            | . 4-4  |

| 4-3   | GUID ROM Register Description                                |        |

| 4-4   | Asynchronous Transmit Retries Register Description           |        |

| 4-5   | CSR Control Register Description                             |        |

| 4-6   | Configuration ROM Header Register Description                |        |

| 4-7  | Bus Options Register Description                                    | 4-9  |

|------|---------------------------------------------------------------------|------|

| 4-8  | Configuration ROM Mapping Register Description                      | 4-11 |

| 4-9  | Posted Write Address Low Register Description                       | 4-11 |

| 4-10 | Posted Write Address High Register Description                      | 4-12 |

| 4-11 | Vendor ID Register Description                                      | 4-13 |

| 4-12 | Host Controller Control Register Description                        | 4-14 |

| 4-13 | Self-ID Count Register Description                                  | 4-16 |

| 4-14 | Isochronous Receive Channel Mask High Register Description          | 4-17 |

| 4-15 | Isochronous Receive Channel Mask Low Register Description           | 4-18 |

| 4-16 | Interrupt Event Register Description                                | 4-19 |

| 4-17 | Interrupt Mask Register Description                                 | 4-21 |

| 4-18 | Isochronous Transmit Interrupt Event Register Description           | 4-23 |

| 4-19 | Isochronous Receive Interrupt Event Register Description            | 4-25 |

| 4-20 | Initial Bandwith Available Register Description                     | 4-26 |

| 4-21 | Initial Channels Available High Register Description                | 4-27 |

| 4-22 | Initial Channels Available Low Register Description                 | 4-27 |

| 4-23 | Fairness Control Register Description                               | 4-28 |

| 4-24 | Link Control Register Description                                   |      |

| 4-25 | Node Identification Register Description                            | 4-30 |

| 4-26 | PHY Control Register Description                                    | 4-31 |

| 4-27 | Isochronous Cycle Timer Register Description                        | 4-32 |

| 4-28 | Asynchronous Request Filter High Register Description               | 4-33 |

| 4-29 | Asynchronous Request Filter Low Register Description                | 4-35 |

| 4-30 | Physical Request Filter High Register Description                   | 4-36 |

| 4-31 | Physical Request Filter Low Register Description                    | 4-38 |

| 4-32 | Asynchronous Context Control Register Description                   | 4-39 |

| 4-33 | Asynchronous Context Command Pointer Register Description           |      |

| 4-34 | Isochronous Transmit Context Control Register Description           |      |

| 4-35 | Isochronous Receive Context Control Register Description            |      |

| 4-36 | Isochronous Receive Context Match Register Description              |      |

| 5-1  | TI Extension Register Map                                           |      |

| 5-2  | Isochronous Receive Digital Video Enhancements Register Description |      |

| 5-3  | Link Enhancement Register Description                               |      |

| 5-4  | Timestamp Offset Register Description                               | 5-6  |

| 7-1  | Serial EEPROM Map                                                   | 7-2  |

#### 1 Introduction

This chapter provides an overview of the Texas Instruments TSB82AA2 device and its features.

#### 1.1 Description

The TSB82AA2 OHCI-Lynx is a discrete 1394b link-layer device, which has been designed to meet the demanding requirements of today's 1394 bus designs. The TSB82AA2 device is capable of exceptional 800M bits/s performance; thus, providing the throughput and bandwidth to move data efficiently and quickly between the PCI and 1394 buses. The TSB82AA2 device also provides outstanding ultra-low power operation and intelligent power management capabilities. The device provides the IEEE 1394 link function and is compatible with 100M bits/s, 200M bits/s, 400M bits/s, and 800M bits/s serial bus data rates.

The TSB82AA2 improved throughput and increased bandwidth make it ideal for today's high-end PCs and open the door for the development of S800 RAID- and SAN-based peripherals.

The TSB82AA2 OHCI-Lynx operates as the interface between a 33-MHz/64-bit or 33-MHz/32-bit PCI local bus and a compatible 1394b PHY-layer device (such as the TSB81BA3 device) that is capable of supporting serial data rates at 98.304M, 196.608M, 393.216M, or 786.432M bits/s (referred to as S100, S200, S400, or S800 speeds, respectively). When acting as a PCI bus master, the TSB82AA2 device is capable of multiple cacheline bursts of data, which can transfer at 264M bytes/s for 64-bit transfers or 132M bytes/s for 32-bit transfers after connecting to the memory controller.

Due to the high throughput potential of the TSB82AA2 device, it possible to encounter large PCI and legacy 1394 bus latencies, which can cause the 1394 data to be overrun. To overcome this potential problem, the TSB82AA2 implements deep transmit and receive FIFOs (see Section 1.2, *Features*, for FIFO size information) to buffer the 1394 data, thus preventing possible problems due to bus latency. This also ensures that the device can transmit and receive sustained maximum size isochronous or asynchronous data payloads at S800.

The TSB82AA2 device implements other performance enhancements to improve overall performance of the device, such as: a highly tuned physical data path for enhanced SBP-2 performance, physical post writing buffers, multiple isochronous contexts, and advanced internal arbitration.

The TSB82AA2 device also implements hardware enhancements to better support digital video (DV) and MPEG data stream reception and transmission. These enhancements are enabled through the isochronous receive digital video enhancements register at TI extension offset A80h (see Section 5.4, *Isochronous Receive Digital Video Enhancements Register*). These enhancements include automatic time stamp insertion for transmitted DV and MPEG-formatted streams and common isochronous packet (CIP) header stripping for received DV streams.

The CIP format is defined by the IEC 61883-1:1998 specification. The enhancements to the isochronous data contexts are implemented as hardware support for the synchronization timestamp for both DV and audio/video CIP formats. The TSB82AA2 device supports modification of the synchronization timestamp field to ensure that the value inserted via software is not stale—that is, less than the current cycle timer when the packet is transmitted.

The TSB82AA2 performance and enhanced throughput make it an excellent choice for today's 1394 PC market; however, the portable, mobile, and even today's desktop PCs power management schemes continue to require devices to use less and less power, and Texas Instrument's 1394 OHCI-Lynx product line has continued to raise the bar by providing the lowest power 1394 link-layers in the industry. The TSB82AA2 device represents the next evolution of Texas Instruments commitment to meet the challenge of power-sensitive applications. The TSB82AA2 device has ultra-low operational power requirements and intelligent power management capabilities that allow it to autonomously conserve power based on the device usage.

One of the key elements for reducing the TSB82AA2 operational power requirements is Texas Instrument's advanced CMOS process and the implementation of an internal 1.8-V core, which is supplied by an improved integrated 3.3-V to 1.8-V voltage regulator. The TSB82AA2 device implements a next generation voltage regulator which is more

efficient than its predecessors, thus providing an overall reduction in the device's operational power requirements especially when operating in D3<sub>cold</sub> using auxiliary power. In fact, the TSB82AA2 device fully supports D0, D1, D2, and D3<sub>hot/cold</sub> power states as specified in the *PC 2001 Design Guide* requirements and the *PCI Power Management Specification*. PME wake event support is subject to operating system support and implementation.

As required by the 1394 Open Host Controller Interface Specification (OHCI) and IEEE Std 1394a-2000, internal control registers are memory-mapped and nonprefetchable. The PCI configuration header is accessed through configuration cycles as specified by the PCI Local Bus Specification, and provides plug-and-play (PnP) compatibility. Furthermore, the TSB82AA2 device is fully compliant with the latest PCI Local Bus Specification, PCI Bus Power Management Interface Specification, IEEE Draft Std 1394b, IEEE Std 1394a-2000, and 1394 Open Host Controller Interface Specification (see Section 1.3, Related Documents, for a complete list).

#### 1.2 Features

The TSB82AA2-EP device supports the following features:

- Controlled Baseline

- One Assembly/Test Site, One Fabrication Site

- Extended Temperature Performance of -40°C to 85°C

- Enhanced Diminishing Manufacturing Sources (DMS) Support

- Enhanced Product-Change Notification

- Qualification Pedigree<sup>†</sup>

- Single 3.3-V supply (1.8-V internal core voltage with regulator)

- 3.3-V and 5-V PCI signaling environments

- Serial bus data rates of 100M bits/s, 200M bits/s, 400M bits/s, and 800M bits/s

- Physical write posting of up to three outstanding transactions

- Serial ROM or boot ROM interface supports 2-wire serial EEPROM devices

- 33-MHz/64-bit and 33-MHz/32-bit selectable PCI interface

- Multifunction terminal (MFUNC terminal 1):

- PCI CLKRUN protocol per the PCI Mobile Design Guide

- General-purpose I/O

- CYCLEIN/CYCLEOUT for external cycle timer control for customized synchronization

- PCI burst transfers and deep FIFOs to tolerate large host latency:

- Transmit FIFO—5K asynchronous

- Transmit FIFO—2K isochronous

- Receive FIFO—2K asynchronous

- Receive FIFO—2K isochronous

- D0, D1, D2, and D3 power states and PME events per the PCI Bus Power Management Interface Specification

- Programmable asynchronous transmit threshold

- Isochronous receive dual-buffer mode

- Out-of-order pipelining for asynchronous transmit requests

- Register access fail interrupt when the PHY SYSCLK is not active

- · Initial bandwidth available and initial channels available registers

- Digital video and audio performance enhancements

- Fabricated in advanced low-power CMOS process

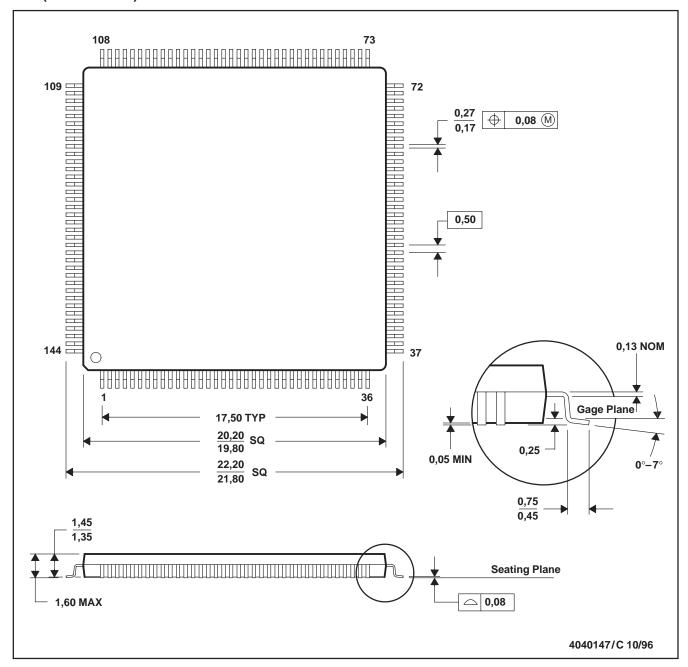

- Packaged in 144-terminal LQFP (PGE)

<sup>&</sup>lt;sup>†</sup> Component qualification in accordance with JEDEC and industry standards to ensure reliable operation over an extended temperature range. This includes, but is not limited to, Highly Accelerated Stress Test (HAST) or biased 85/85, temperature cycle, autoclave or unbiased HAST, electromigration, bond intermetallic life, and mold compound life. Such qualification testing should not be viewed as justifying use of this component beyond specified performance and environmental limits.

#### 1.3 Related Documents

- 1394 Open Host Controller Interface Specification (Revision 1.2)

- IEEE Standard for a High Performance Serial Bus (IEEE Std 1394-1995)

- IEEE Standard for a High Performance Serial Bus—Amendment 1 (IEEE Std 1394a-2000)

- P1394b Draft Standard for High Performance Serial Bus (Supplement)

- PC 2001 Design Guide

- PCI Bus Power Management Interface Specification (Revision 1.1)

- PCI Local Bus Specification (Revision 2.3)

- Serial Bus Protocol 2 (SBP-2)

- Microsoft Windows Logo Program System and Device Requirements (Version 0.5)

- Microsoft Windows Logo Program Desktop and Mobile PC Requirements (Version 1.1)

- Digital Interface for Consumer Electronic Audio/Video Equipment Draft (Version 2.1) (IEC 61883)

#### 1.4 Trademarks

OHCI-Lynx is a trademark of Texas Instruments.

Intel is a trademark of Intel Corporation.

Other trademarks are the property of their respective owners.

#### 1.5 Ordering Information

| ORDERING NUMBER | NAME                                            | VOLTAGE                 | PACKAGE |

|-----------------|-------------------------------------------------|-------------------------|---------|

| TSB82AA2IPGEEP  | OHCI-Lynx™ PCI-Based IEEE 1394 Host Controller, | 3.3V-, 5V-tolerant I/Os | PGE     |

|                 | Enhanced Plastic                                |                         |         |

## 1.6 TSB82AA2-EP Data Manual Document History

| DATE    | REVISION        | PAGE | PARAGRAPH | DESCRIPTION |

|---------|-----------------|------|-----------|-------------|

| 09/2003 | Initial release |      |           |             |

## 2 Terminal Descriptions

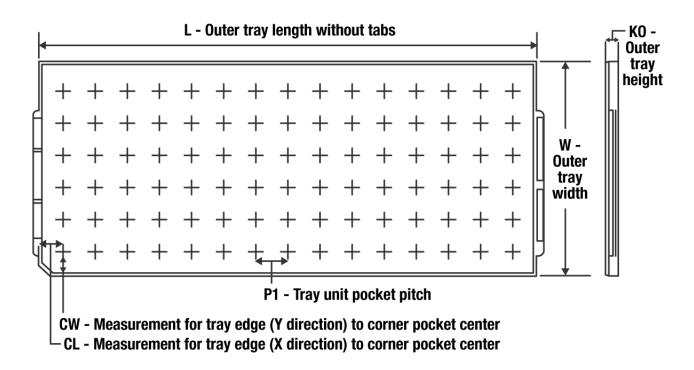

This section provides the terminal descriptions for the TSB82AA2 device. Figure 2-1 shows the signal assigned to each terminal in the package. Table 2-1 and Table 2-2 provide a cross-reference between each terminal number and the name of the signal on that terminal. Table 2-1 is arranged in terminal number order, and Table 2-2 lists the signals in alphanumerical order.

Figure 2-1. Terminal Assignments

Table 2-1. Signals Sorted by Terminal Number

| NO. | TERMINAL NAME    |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|------------------|

| 1   | MFUNC           | 37  | PCI_AD17        | 73  | PCI_REQ64       | 109 | PCI_AD42         |

| 2   | REG_EN          | 38  | PCI_AD16        | 74  | PCI_C/BE7       | 110 | PCI_AD41         |

| 3   | SCL             | 39  | PCI_C/BE2       | 75  | V <sub>CC</sub> | 111 | PCI_AD40         |

| 4   | SDA             | 40  | PCI_FRAME       | 76  | GND             | 112 | GND              |

| 5   | PCI_INTA        | 41  | PCI_IRDY        | 77  | PCI_C/BE6       | 113 | PCI_AD39         |

| 6   | PCI_RST         | 42  | V <sub>CC</sub> | 78  | PCI_C/BE5       | 114 | PCI_AD38         |

| 7   | G_RST           | 43  | GND             | 79  | PCI_C/BE4       | 115 | PCI_AD37         |

| 8   | V <sub>CC</sub> | 44  | PCI_TRDY        | 80  | PCI_PAR64       | 116 | PCI_AD36         |

| 9   | GND             | 45  | PCI_DEVSEL      | 81  | GND             | 117 | V <sub>CCP</sub> |

| 10  | PCI_CLK         | 46  | PCI_STOP        | 82  | PCI_AD63        | 118 | PCI_AD35         |

| 11  | NC              | 47  | PCI_PERR        | 83  | PCI_AD62        | 119 | PCI_AD34         |

| 12  | PCI_GNT         | 48  | PCI_SERR        | 84  | PCI_AD61        | 120 | PCI_AD33         |

| 13  | PCI_REQ         | 49  | PCI_PAR         | 85  | PCI_AD60        | 121 | PCI_AD32         |

| 14  | PCI_PME         | 50  | PCI_C/BE1       | 86  | V <sub>CC</sub> | 122 | GND              |

| 15  | V <sub>CC</sub> | 51  | PCI_AD15        | 87  | REG18           | 123 | PHY_D7           |

| 16  | REG18           | 52  | GND             | 88  | PCI_AD59        | 124 | PHY_D6           |

| 17  | PCI_AD31        | 53  | PCI_AD14        | 89  | PCI_AD58        | 125 | PHY_D5           |

| 18  | PCI_AD30        | 54  | PCI_AD13        | 90  | PCI_AD57        | 126 | V <sub>CC</sub>  |

| 19  | PCI_AD29        | 55  | $V_{CCP}$       | 91  | $V_{CCP}$       | 127 | GND              |

| 20  | PCI_AD28        | 56  | PCI_AD12        | 92  | PCI_AD56        | 128 | PHY_D4           |

| 21  | $V_{CCP}$       | 57  | PCI_AD11        | 93  | GND             | 129 | PHY_D3           |

| 22  | GND             | 58  | PCI_AD10        | 94  | PCI_AD55        | 130 | PHY_D2           |

| 23  | PCI_AD27        | 59  | PCI_AD9         | 95  | PCI_AD54        | 131 | PHY_D1           |

| 24  | PCI_AD26        | 60  | PCI_AD8         | 96  | PCI_AD53        | 132 | PHY_D0           |

| 25  | PCI_AD25        | 61  | PCI_C/BE0       | 97  | PCI_AD52        | 133 | PHY_CTL1         |

| 26  | PCI_AD24        | 62  | V <sub>CC</sub> | 98  | PCI_AD51        | 134 | PHY_CTL0         |

| 27  | PCI_C/BE3       | 63  | GND             | 99  | PCI_AD50        | 135 | V <sub>CC</sub>  |

| 28  | PCI_IDSEL       | 64  | PCI_AD7         | 100 | PCI_AD49        | 136 | PHY_LCLK         |

| 29  | PCI_AD23        | 65  | PCI_AD6         | 101 | PCI_AD48        | 137 | GND              |

| 30  | PCI_AD22        | 66  | PCI_AD5         | 102 | V <sub>CC</sub> | 138 | PHY_PCLK         |

| 31  | V <sub>CC</sub> | 67  | PCI_AD4         | 103 | GND             | 139 | V <sub>CC</sub>  |

| 32  | GND             | 68  | PCI_AD3         | 104 | PCI_AD47        | 140 | GND              |

| 33  | PCI_AD21        | 69  | PCI_AD2         | 105 | PCI_AD46        | 141 | PHY_LREQ         |

| 34  | PCI_AD20        | 70  | PCI_AD1         | 106 | PCI_AD45        | 142 | PHY_LINKON       |

| 35  | PCI_AD19        | 71  | PCI_AD0         | 107 | PCI_AD44        | 143 | PHY_PINT         |

| 36  | PCI_AD18        | 72  | PCI_ACK64       | 108 | PCI_AD43        | 144 | PHY_LPS          |

Table 2-2. Signal Names Sorted Alphanumerically to Terminal Number

| TERMINAL NAME | NO. | TERMINAL NAME | NO. | TERMINAL NAME | NO.  | TERMINAL NAME    | NO. |

|---------------|-----|---------------|-----|---------------|------|------------------|-----|

| GND           | 9   | PCI AD17      | 37  | PCI AD53      | 96   | PHY CTL0         | 134 |

| GND           | 22  | PCI AD18      | 36  | PCI AD54      | 95   | PHY CTL1         | 133 |

| GND           | 32  | PCI AD19      | 35  | PCI AD55      | 94   | PHY D0           | 132 |

| GND           | 43  | PCI AD20      | 34  | PCI AD56      | 92   | PHY D1           | 131 |

| GND           | 52  | PCI AD21      | 33  | PCI AD57      | 90   | PHY D2           | 130 |

| GND           | 63  | PCI AD22      | 30  | PCI AD58      | 89   | PHY D3           | 129 |

| GND           | 76  | PCI_AD23      | 29  | PCI_AD59      | 88   | PHY D4           | 128 |

| GND           | 81  | PCI_AD24      | 26  | PCI_AD60      | 85   | PHY D5           | 125 |

| GND           | 93  | PCI_AD25      | 25  | PCI_AD61      | 84   | PHY D6           | 124 |

| GND           | 103 | PCI_AD26      | 24  | PCI_AD62      | 83   | PHY_D7           | 123 |

| GND           | 112 | PCI AD27      | 23  | PCI_AD63      | 82   | PHY LCLK         | 136 |

| GND           | 122 | PCI_AD28      | 20  | PCI CLK       | 10   | PHY LINKON       | 142 |

| GND           | 127 | PCI AD29      | 19  | PCI_C/BE0     | 61   | PHY_LPS          | 144 |

| GND           | 137 | PCI AD30      | 18  | PCI C/BE1     | 50   | PHY_LREQ         | 141 |

| GND           | 140 | PCI AD31      | 17  | PCI C/BE2     | 39   | PHY PCLK         | 138 |

| G RST         | 7   | PCI AD32      | 121 | PCI C/BE3     | 27   | PHY_PINT         | 143 |

| MFUNC         | 1   | PCI AD33      | 120 | PCI C/BE4     | 79   | REG EN           | 2   |

| NC            | 11  | PCI_AD34      | 119 | PCI C/BE5     | 78   | REG18            | 16  |

| PCI ACK64     | 72  | PCI_AD35      | 118 | PCI C/BE6     | 77   | REG18            | 87  |

| PCI_AD0       | 71  | PCI_AD36      | 116 | PCI_C/BE7     | 74   | SCL              | 3   |

| PCI AD1       | 70  | PCI AD37      | 115 | PCI DEVSEL    | 45   | SDA              | 4   |

| PCI AD2       | 69  | PCI_AD38      | 114 | PCI_FRAME     | 40   | V <sub>CC</sub>  | 8   |

| PCI AD3       | 68  | PCI AD39      | 113 | PCI GNT       | 12   | V <sub>CC</sub>  | 15  |

| PCI AD4       | 67  | PCI AD40      | 111 | PCI IDSEL     | 28   | V <sub>CC</sub>  | 31  |

| PCI AD5       | 66  | PCI AD41      | 110 | PCI INTA      | 5    | V <sub>CC</sub>  | 42  |

| PCI AD6       | 65  | PCI_AD42      | 109 | PCI IRDY      | 41   | V <sub>CC</sub>  | 62  |

| PCI AD7       | 64  | PCI AD43      | 108 | PCI PAR       | 49   | V <sub>CC</sub>  | 75  |

| PCI AD8       | 60  | PCI AD44      | 107 | PCI PAR64     | 80   | V <sub>CC</sub>  | 86  |

| PCI AD9       | 59  | PCI AD45      | 106 | PCI PERR      | 47   | V <sub>CC</sub>  | 102 |

| PCI AD10      | 58  | PCI AD46      | 105 | PCI_PME       | 14   | V <sub>CC</sub>  | 126 |

| PCI AD11      | 57  | PCI AD47      | 104 | PCI REQ       | 13   | V <sub>CC</sub>  | 135 |

| PCI AD12      | 56  | PCI_AD48      | 101 | PCI_REQ64     | 73   | V <sub>CC</sub>  | 139 |

| PCI AD13      | 54  | PCI AD49      | 100 | PCI_RST       | 6    | V <sub>CCP</sub> | 21  |

| PCI AD14      | 53  | PCI AD50      | 99  | PCI_SERR      | 48   | V <sub>CCP</sub> | 55  |

| PCI AD15      | 51  | PCI AD51      | 98  | PCI STOP      | 46   | V <sub>CCP</sub> | 91  |

| PCI AD16      | 38  | PCI AD52      | 97  | PCI_TRDY      | 44   | V <sub>CCP</sub> | 117 |

| 1 01_4010     | 55  | 1 01_7002     | υ,  | I 'S'_111D1   | -1-7 | I ₹CCP           | ''' |

The terminals are grouped in tables by functionality, such as PCI system function and power supply function (see Table 2–3 through Table 2–7). The terminal numbers are also listed for convenient reference.

Table 2-3. Power Supply Terminals

| TE               | RMINAL                                                                      |     |                                                                                                                                                                                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO.                                                                         | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                  |

| GND              | 9, 22, 32, 43,<br>52, 63, 76, 81,<br>93, 103, 112,<br>122, 127, 137,<br>140 | -   | Ground terminals. These terminals must be tied together to the low-impedance circuit board ground plane.                                                                                                                                                                                                     |

| REG18            | 16<br>87                                                                    | -   | The REG18 terminals are connected to the internal 1.8-V core voltage. They provide a mechanism to provide local bypass for the internal core voltage or to externally provide the 1.8 V to the core if the internal regulator is disabled.                                                                   |

| REG_EN           | 2                                                                           | I   | Regulator enable. When this terminal is low, the internal regulator is enabled and generates the 1.8-V internal core voltage from the 3.3-V supply voltage. If it is disabled, then 1.8 V must be provided to the REG18 terminals for normal operation.                                                      |

| V <sub>CC</sub>  | 8, 15, 31, 42,<br>62, 75, 86,<br>102, 126, 135,<br>139                      | -   | 3.3-V power supply terminals. A parallel combination of high frequency decoupling capacitors near each terminal is suggested, such as 0.1 $\mu$ F and 0.001 $\mu$ F. Lower frequency 10- $\mu$ F filtering capacitors are also recommended. They must be tied to a low-impedance point on the circuit board. |

| V <sub>CCP</sub> | 21, 55, 91, 117                                                             | -   | PCI signaling clamp voltage power input. PCI signals are clamped per the $PCI$ Local Bus Specification. In addition, if a 5-V ROM is used, then the $V_{CCP}$ terminal must be connected to 5 V.                                                                                                             |

Table 2-4. Reset and Miscellaneous Terminals

| TERMINAL |     |     | DECORPORTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME     | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| G_RST    | 7   | I   | Global power reset. This reset brings all of the TSB82AA2 internal registers to their default states, including those registers not reset by PCI_RST. When G_RST is asserted, the device is completely nonfunctional. A valid clock input (PCI_CLK) is required before deasserting G_RST to reset some device functionality. Additionally, G_RST must be asserted a minimum of 2 ms after both 3.3 V and 1.8 V are valid at the device.  When implementing wake capabilities from the 1394 host controller, it is necessary to implement two resets to the TSB82AA2 device. G_RST is designed to be a one-time power-on reset, and PCI_RST must be connected to the PCI bus RST. |  |  |  |  |  |

| PCI_RST  | 6   | Ι   | CI reset. When this bus reset is asserted, the TSB82AA2 device places all output buffers in a high-impedance ate and resets all internal registers except device power management context and vendor-specific bits initialized y host power-on software. When PCI_RST is asserted, the device is completely nonfunctional. This terminal ust be connected to PCI bus RST.                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| MFUNC    | 1   | I/O | Multifunction terminal. MFUNC is a multifunction terminal whose function is selected via the multifunction select register:    Bits 2-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| SCL      | 3   | I/O | Serial clock. This terminal provides the SCL serial clock signaling.  ROM is implemented: Connect terminal 3 to the SCL terminal on the ROM; the 2.7-kΩ resistor pulls this signal to the ROM V <sub>CC</sub> . (SDA is implemented as open-drain.)  ROM is not implemented. Connect terminal 3 to ground with a 220-Ω resistor.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| SDA      | 4   | I/O | Serial data. This terminal provides the SDA serial data signaling. This terminal is sampled at $\overline{G_RST}$ to determine f a serial ROM is implemented; thus if no ROM is implemented, then this terminal must be connected to ground. ROM is implemented: Connect terminal 4 to the SDA terminal on the ROM; the 2.7-k $\Omega$ resistor pulls this signal to the ROM V <sub>CC</sub> . (SDA is implemented as open-drain.)  ROM is not implemented. Connect terminal 4 to ground with a 220- $\Omega$ resistor.                                                                                                                                                          |  |  |  |  |  |

Table 2-5. 32-Bit PCI Bus Terminals

| TERMINA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                   |     |                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                         |

| PCI_AD31 PCI_AD30 PCI_AD29 PCI_AD28 PCI_AD26 PCI_AD25 PCI_AD24 PCI_AD23 PCI_AD21 PCI_AD20 PCI_AD21 PCI_AD10 PCI_AD18 PCI_AD15 PCI_AD16 PCI_AD15 PCI_AD14 PCI_AD13 PCI_AD14 PCI_AD13 PCI_AD14 PCI_AD15 PCI_AD10 PCI_AD20 PCI_AD20 PCI_AD3 PCI_AD3 PCI_AD2 PCI_AD1 | NO.  17 18 19 20 23 24 25 26 29 30 33 34 35 36 37 38 51 53 54 56 57 58 59 60 64 65 66 67 68 69 70 | 1/0 | PCI address/data bus for the lower DWORD. These signals make up the multiplexed PCI address and data bus for the lower 32 bits on the PCI interface. During the address phase of a PCI cycle, AD31-AD0 contain a 32-bit address or other destination information. During the data phase, AD31-AD0 contain data.     |

| PCI_AD0  PCI_C/BE0 PCI_C/BE1 PCI_C/BE2 PCI_C/BE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71<br>61<br>50<br>39<br>27                                                                        | I/O | PCI bus commands and byte enables for lower DWORD. The command and byte enable signals are multiplexed on the same PCI terminals. During the address phase of a bus cycle, PCI_C/BE3-PCI_C/BE0 define the bus command. During the data phase, this 4-bit bus is used as byte enables for the lower 32 bits of data. |

| PCI_CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10                                                                                                | I   | PCI bus clock. Provides timing for all transactions on the PCI bus. All PCI signals are sampled at the rising edge of PCI_CLK.                                                                                                                                                                                      |

| PCI_DEVSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45                                                                                                | I/O | PCI device select. The TSB82AA2 device asserts this signal to claim a PCI cycle as the target device. As a PCI initiator, the TSB82AA2 device monitors this signal until a target responds. If no target responds before time-out occurs, then the TSB82AA2 device terminates the cycle with an initiator abort.    |

| PCI_FRAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40                                                                                                | I/O | PCI cycle frame. This signal is driven by the initiator of a PCI bus cycle. PCI_FRAME is asserted to indicate that a bus transaction is beginning, and data transfers continue while this signal is asserted. When PCI_FRAME is deasserted, the PCI bus transaction is in the final data phase.                     |

| PCI_GNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12                                                                                                | I   | PCI bus grant. This signal is driven by the PCI bus arbiter to grant the TSB82AA2 device access to the PCI bus after the current data transaction has completed. This signal may or may not follow a PCI bus request, depending upon the PCI bus parking algorithm.                                                 |

| PCI_IDSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28                                                                                                | I   | Initialization device select. PCI_IDSEL selects the TSB82AA2 device during configuration space accesses. PCI_IDSEL can be connected to 1 of the upper 24 PCI address lines on the PCI bus.                                                                                                                          |

| PCI_INTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                                                                                                 | 0   | Interrupt signal. This output indicates interrupts from the TSB82AA2 device to the host. This terminal is implemented as open-drain.                                                                                                                                                                                |

| PCI_IRDY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41                                                                                                | I/O | PCI initiator ready. PCI_IRDY indicates the ability of the PCI bus initiator to complete the current data phase of the transaction. A data phase is completed upon a rising edge of PCI_CLK where both PCI_IRDY and PCI_TRDY are asserted.                                                                          |

Table 2-5. 32-Bit PCI Bus Terminals (Continued)

| TERMINA  | \L  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PCI_PAR  | 49  | I/O | PCI parity. In all PCI bus read and write cycles, the TSB82AA2 device calculates even parity across the PCI_AD31-PCI_AD0 and PCI_C/BE0-PCI_C/BE3 buses. As an initiator during PCI cycles, the TSB82AA2 device outputs this parity indicator with a one-PCI_CLK delay. As a target during PCI cycles, the calculated parity is compared to the initiator parity indicator; a miscompare can result in a parity error assertion (PCI_PERR).                                                                                                                                  |

| PCI_PERR | 47  | I/O | PCI parity error indicator. This signal is driven by a PCI device to indicate that calculated parity does not match PCI_PAR and/or PCI_PAR64 when PERR_ENB (bit 6) is set to 1 in the command register at offset 04h in the PCI configuration space (see Section 3.4, <i>Command Register</i> ).                                                                                                                                                                                                                                                                            |

| PCI_PME  | 14  | 0   | This terminal indicates wake events to the host. It is an open-drain signal which is asserted when PME_STS is asserted and bit 8 (PME_ENB) in the PCI power management control and status register at offset 48h in the PCI configuration space (see Section 3.20, <i>Power Management Control and Status Register</i> ) has been set. Bit 15 (PME_STS) in the PCI power management control and status register is set due to any unmasked interrupt in the D0 (active) or D1 power state, and on a PHY_LINKON indication in the D2, D3, or D0 (uninitialized) power state. |

| PCI_REQ  | 13  | 0   | PCI bus request. Asserted by the TSB82AA2 device to request access to the bus as an initiator. The host arbiter asserts PCI_GNT when the TSB82AA2 device has been granted access to the bus.                                                                                                                                                                                                                                                                                                                                                                                |

| PCI_SERR | 48  | 0   | PCI system error. When SERR_ENB (bit 8) in the command register at offset 04h in the PCI configuration space (see Section 3.4, <i>Command Register</i> ) is set to 1, the output is pulsed, indicating an address parity error has occurred. The TSB82AA2 device need not be the target of the PCI cycle to assert this signal. This terminal is implemented as open-drain.                                                                                                                                                                                                 |

| PCI_STOP | 46  | I/O | PCI cycle stop signal. This signal is driven by a PCI target to request the initiator to stop the current PCI bus transaction. This signal is used for target disconnects, and is commonly asserted by target devices which do not support burst data transfers.                                                                                                                                                                                                                                                                                                            |

| PCI_TRDY | 44  | I/O | PCI target ready. PCI_TRDY indicates the ability of the PCI bus target to complete the current data phase of the transaction. A data phase is completed upon a rising edge of PCI_CLK where both PCI_IRDY and PCI_TRDY are asserted.                                                                                                                                                                                                                                                                                                                                        |

Table 2-6. PCI 64-Bit Bus Extension Terminals

| TERMINA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | \L                                                                                                                                                                                                             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | NO.                                                                                                                                                                                                            | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PCI_ACK64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72                                                                                                                                                                                                             | I   | PCI bus 64-bit transfer acknowledge. Asserted by a target if it is willing to accept a 64-bit data transfer when it positively decodes its address for a memory transaction and the master has requested a 64-bit data transfer by asserting PCI_REQ64. PCI_REQ64 has identical timing to PCI_DEVSEL. When the TSB82AA2 device is bus master, it monitors PCI_REQ64 when it has requested a 64-bit data transfer for the current transaction. If the target asserts PCI_REQ64 when it claims the cycle, then the TSB82AA2 device transfers data using 64 bits. As a target, the TSB82AA2 does not support 64-bit data transfers and never asserts PCI_REQ64 when another master has requested 64-bit transfer. |

| PCI_AD63 PCI_AD62 PCI_AD61 PCI_AD60 PCI_AD59 PCI_AD58 PCI_AD56 PCI_AD55 PCI_AD55 PCI_AD54 PCI_AD53 PCI_AD52 PCI_AD51 PCI_AD50 PCI_AD49 PCI_AD48 PCI_AD46 PCI_AD45 PCI_AD44 PCI_AD45 PCI_AD44 PCI_AD45 PCI_AD44 PCI_AD45 PCI_AD45 PCI_AD44 PCI_AD45 PCI_AD45 PCI_AD45 PCI_AD46 PCI_AD47 PCI_AD46 PCI_AD47 PCI_AD48 PCI_AD48 PCI_AD48 PCI_AD49 PCI_AD49 PCI_AD40 PCI_AD40 PCI_AD40 PCI_AD40 PCI_AD39 PCI_AD36 PCI_AD36 PCI_AD36 PCI_AD37 PCI_AD37 PCI_AD38 | 82<br>83<br>84<br>85<br>88<br>89<br>90<br>92<br>94<br>95<br>96<br>97<br>98<br>99<br>100<br>101<br>104<br>105<br>106<br>107<br>108<br>109<br>110<br>111<br>113<br>114<br>115<br>116<br>118<br>119<br>120<br>121 | I/O | PCI address/data bus for the upper DWORD. These signals make up the multiplexed PCI address and data bus for the upper 32 bits of the PCI interface. During the address phase of a dual address command with PCI_REQ64 asserted, AD63-AD32 contain the upper 32 bits of a 64-bit address. During the data phase, AD63-AD32 contain data when a 64-bit transfer has been negotiated by the assertion of PCI_REQ64 by the master and PCI_ACK64 by the target. Note, the TSB82AA2 does not support the dual address command.                                                                                                                                                                                      |

| PCI_C/BE7<br>PCI_C/BE6<br>PCI_C/BE5<br>PCI_C/BE4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74<br>77<br>78<br>79                                                                                                                                                                                           | I/O | PCI bus commands and byte enables for the upper DWORD. During the address phase of a bus cycle, PCI_C/BE7-PCI_C/BE4 are reserved and indeterminate since the TSB82AA2 does not support the dual address command. During the data phase, this 4-bit bus is used as byte enables for the upper 32 bits when a 64-bit transfer has been negotiated by the assertion of PCI_REQ64 by the master and PCI_ACK64 by the target.                                                                                                                                                                                                                                                                                       |

| PCI_PAR64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 80                                                                                                                                                                                                             | I   | PCI parity for the upper DWORD. In all PCI bus read and write cycles, the TSB82AA2 device calculates even parity across the PCI_AD63-PCI_AD32 and PCI_C/BE4-PCI_C/BE7 buses. As an initiator during PCI cycles, the TSB82AA2 device outputs this parity indicator with a one-PCI_CLK delay. As a target during PCI cycles, the calculated parity is compared to the initiator parity indicator; a miscompare can result in a parity error assertion (PCI_PERR).                                                                                                                                                                                                                                                |

| PCI_REQ64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73                                                                                                                                                                                                             | ı   | PCI bus request for 64-bit transfer. Asserted by a bus master to request a 64-bit transfer for a memory transaction. The timing of PCI_REQ64 is identical to PCI_FRAME. When the TSB82AA2 device is the bus master, it asserts PCI_REQ64 to request a 64-bit transfer on the current transaction. The TSB82AA2 device only requests a 64-bit transfer for a memory transaction. The target asserts PCI_ACK64 if it is willing to transfer data using 64 bits.                                                                                                                                                                                                                                                  |

Table 2-7. PHY-Link Interface Terminals

| TERMINA                                                                      | L                                                    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------|------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                         | NO.                                                  | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PHY_CTL1<br>PHY_CTL0                                                         | 133<br>134                                           | I/O | PHY-link interface control. These bidirectional control bus signals indicate the phase of operation of the PHY-link interface. Upon a reset of the interface, this bus is driven by the PHY. When driven by the PHY, information on PHY_CTL0 and PHY_CTL1 is synchronous to PHY_PCLK. When driven by the link, information on PHY_CTL0 and PHY_CTL1 is synchronous to PHY_LCLK.                                                                                                                                                                                                                                                                                                  |

| PHY_D7<br>PHY_D6<br>PHY_D5<br>PHY_D4<br>PHY_D3<br>PHY_D2<br>PHY_D1<br>PHY_D0 | 123<br>124<br>125<br>128<br>129<br>130<br>131<br>132 | I/O | PHY-link interface data. These bidirectional data bus signals carry 1394 packet data, packet speed, and grant type information between the PHY and the link. Upon a reset of the interface, this bus is driven by the PHY. When driven by the PHY, information on PHY_D7 through PHY_D0 is synchronous to PHY_PCLK. When driven by the link, information on PHY_D7 through PHY_D0 is synchronous to PHY_LCLK.                                                                                                                                                                                                                                                                    |

| PHY_LINKON                                                                   | 142                                                  | I/O | Link-on notification. PHY_LINKON is an input to the TSB82AA2 device from the PHY that is used to provide notification that a link-on packet has been received, or, if the PHY is configured properly, an event such as a port connection has occurred. This input only has meaning when LPS is disabled. This includes the D0 (uninitialized), D2, and D3 power states. If PHY_LINKON becomes active in the D0 (uninitialized), D2, or D3 power state, then the TSB82AA2 device sets bit 15 (PME_STS) in the power management control and status register in the PCI configuration space at offset 48h (see Section 3.20, <i>Power Management Control and Status Register</i> ). |

| PHY_LPS                                                                      | 144                                                  | I/O | Link power status. PHY_LPS is an output from the TSB82AA2 device that, when active, indicates that the link is powered and capable of maintaining communications over the PHY-link interface. When this signal is inactive, it indicates that the link is not powered or that the link has not been initialized by software. This signal is active when bit 19 (LPS) in the host controller control register at OHCl offset 50h/54h (see Section 4.16, Host Controller Control Register) has been set by software according to the initialization as specified in the 1394 Open Host Controller Interface specification. When active, the signal is nominally a 2-MHz pulse.     |

| PHY_LREQ                                                                     | 141                                                  | 0   | Link request. PHY_LREQ is a serial output from the TSB82AA2 device to the PHY used to request packet transmissions, read and write PHY registers, and to indicate the occurrence of certain link events that are relevant to the PHY. Information encoded on PHY_LREQ is synchronous to PHY_LCLK.                                                                                                                                                                                                                                                                                                                                                                                |

| PHY_LCLK                                                                     | 136                                                  | 0   | Link clock. PHY_LCLK is an output from the TSB82AA2 device that is generated from the incoming PHY_PCLK signal. PHY_LCLK is frequency-locked to PHY_PCLK and synchronizes data and information generated by the link.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |