# SMJ5C1008 128K BY 8-BIT STATIC RANDOM-ACCESS MEMORY SGM5734A - MAY 1996 - REVISED JUNE 1997

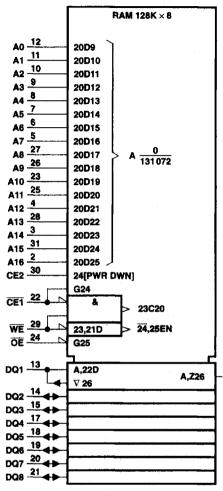

JDC or HM PACKAGE (TOP VIEW)

- Processed to MIL-PRF-38535

- Organization . . . 128K Words × 8 Bits

- Fast Static Operation

- Single 5-V Supply (±10% Tolerance)

- Maximum Access Time From Address or Chip Enable:

'5C1008-20 20 ns '5C1008-25 25 ns

- TTL Compatible Inputs and Outputs

- Low-Power Standby

- 3-State Outputs

- Ceramic Package Options

- 32-Pin Ceramic Dual In-Line Package (CDIP) (400 mil), JDC Suffix

- 32-Pin Leadless Ceramic Chip Carrier (LCCC), HM Suffix

- Military Operating Temperature Range -55°C to 125°C

| NC[               | 1  | 32 V <sub>CC</sub> |

|-------------------|----|--------------------|

| A16[              | 2  | 31 A15             |

| A14[              | 3  | 30 CE2             |

| A12[              | 4  | 29 WE              |

| A7[               | 5  | 28 A13             |

| A6[               | 6  | 27 A8              |

| A5[               | 7  | 26 A9              |

| A4[               | 8  | 25 A11             |

| A3[               | 9  | 24 ] ŌĒ            |

| A2[               | 10 | 23 A10             |

| A1[               | 11 | 22 CE1             |

| A0[               | 12 | 21 DQ8             |

| DQ1[              | 13 | 20 DQ7             |

| DQ2[              | 14 | 19 DQ6             |

| DQ3[              | 15 | 18 🛚 DQ5           |

| V <sub>SS</sub> [ | 16 | 17] DQ4            |

|                   |    |                    |

# description

The SMJ5C1008 is a high-performance 1048576-bit CMOS static random-access memory (SRAM) organized as 128K words  $\times$  8 bits. The device features maximum address or chip-enable access times of 20 ns or 25 ns.

The SMJ5C1008 offers dual chip enables (CE1, CE2) and an output enable (OE) for greater system flexibility. The chip enables place the device in an active or standby-power mode, while

| PIN NOMENCLATURE       |                |  |  |  |  |  |  |

|------------------------|----------------|--|--|--|--|--|--|

| A0 – A16               | Address Inputs |  |  |  |  |  |  |

| CE1, CE2               | Chip Enables   |  |  |  |  |  |  |

| DQ1-DQ8 Data In/Data O |                |  |  |  |  |  |  |

| NC                     | No Connect     |  |  |  |  |  |  |

| ŌĒ                     | Output Enable  |  |  |  |  |  |  |

| · Vcc                  | 5-V Supply     |  |  |  |  |  |  |

| VSS                    | Ground         |  |  |  |  |  |  |

| WE                     | Write Enable   |  |  |  |  |  |  |

OE allows the outputs to be placed in the high-impedance state, eliminating bus contention problems. In the standby-power mode, the device is disabled, resulting in reduced power consumption. This allows designers to meet extremely low standby-power requirements.

To write to the device, the WE and CE1 inputs are held at logic low while CE2 is at logic high. To read from the device, WE and CE2 are held at logic high and CE1 and OE are held at logic low.

All devices operate from a single 5-V ( $\pm 10\%$ ) supply. They are MIL-PRF-38535, Device Class Q qualified and are operational from  $-55^{\circ}$ C to  $125^{\circ}$ C.

# logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for the JDC package.

# truth table

| CE1 | CE2 | ŌĒ | WE | MODE            | VO PIN           | CYCLE | CURRENT |

|-----|-----|----|----|-----------------|------------------|-------|---------|

| Н   | ×   | ×  | Х  | Not selected    | Hi-Z             | _     | ICC1    |

| Х   | L   | Х  | х  | Not selected    | Hi-Z             | -     | ICC1    |

| L   | Н   | Н  | Н  | Output disabled | Hi-Z             |       | Icc     |

| L   | н   | L  | Н  | Read            | TUO <sup>Q</sup> | Read  | lcc     |

| L   | Н   | X  | L  | Write           | DIN              | Write | lcc     |

H = High, L = Low, X = don't care

#### operation

#### address (A0-A16)

Seventeen address lines allow access to each of the 128K 8-bit words in RAM.

#### data inputs/data outputs (DQ1-DQ8)

Data can be written into the device when  $\overline{CE1}$  and  $\overline{WE}$  are low and CE2 is high. DQ1 – DQ8 are TTL compatible. The device is placed in a low-power standby mode with the DQs in the high-impedance state when  $\overline{CE1}$  is at logic high or CE2 is at logic low. The device remains active with high-impedance DQs when  $\overline{OE}$ , CE2, and  $\overline{WE}$  are high, and when  $\overline{CE1}$  is low.

#### chip enable (CE1, CE2)

Two separate chip enables, CE1 and CE2, are provided for greater design flexibility. Whenever CE1 is low and CE2 is high, the device is active. Standby mode is reached when either CE1 is high or CE2 is low. Data is retained during standby.

# write enable (WE)

The read or write mode is selected through the use of WE. WE must be high for the read mode and low for the write mode. WE must be high when address changes occur to prevent erroneously writing data into new memory locations. WE is a don't care function when the device is in standby mode.

# output enable (OE)

When in the read mode,  $\overline{OE}$  controls the state of the DQs. A high on  $\overline{OE}$  places the DQs in the high-impedance state, while a low provides data on the outputs.

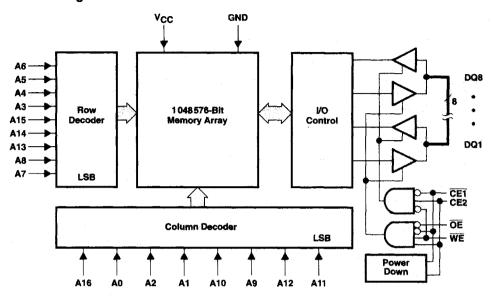

# functional block diagram

# absolute maximum ratings over operating case temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)0.5 V to 7 V               |

|------------------------------------------------------------------------------|

| Input voltage range (see Note 2)                                             |

| Output voltage range in high-impedance state                                 |

| Short-circuit output current (per output)                                    |

| Maximum operating free-air temperature range, T <sub>A</sub> – 55°C to 125°C |

| Storage temperature range, T <sub>St0</sub> – 65°C to 150°C                  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Voltage values are with respect to VSS.

#### recommended operating conditions

|     |                                | MIN   | NOM | MAX                   | UNIT |

|-----|--------------------------------|-------|-----|-----------------------|------|

| Vcc | Supply voltage                 | 4.5   | 5   | 5.5                   | ٧    |

| VIH | High-level input voltage       | 2.2   |     | V <sub>CC</sub> + 0.5 | ٧    |

| VIL | Low-level input voltage        | ~ 0.5 |     | 0.8                   | V    |

| TA  | Operating free-air temperature | 55    |     | 125                   | ŷ    |

Negative undershoots on V<sub>IL</sub> and V<sub>OL</sub> can be tolerated if they are ≥-3.0 V with a maximum pulse duration of 20 ns. Prolonged operation at levels below -1 V results in excessive currents that can damage the device input.

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER      |                                           |                   | '5C1008-20                                                                                                                                                                                                                        |     | '5C1008-25 |     |     |      |

|----------------|-------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|-----|------|

|                | PANAMEICH                                 |                   | TEST CONDITIONS                                                                                                                                                                                                                   | MIN | MAX        | MIN | MAX | UNIT |

| Vон            | High-level output voltage                 |                   | V <sub>CC</sub> = 4.5 V, I <sub>OH</sub> = -4 mA                                                                                                                                                                                  | 2.4 |            | 2.4 |     | ٧    |

| VOL            | Low-level output voltage                  |                   | V <sub>CC</sub> = 4.5 V, I <sub>OL</sub> = 8 mA                                                                                                                                                                                   |     | 0.4        |     | 0.4 | ٧    |

| l <sub>l</sub> | Input current (load)                      |                   | V <sub>CC</sub> = 5.5 V, 0 V ≤ V <sub>I</sub> ≤ V <sub>CC</sub>                                                                                                                                                                   | -5  | 5          | - 5 | 5   | μА   |

| ю              | Output current (leakage)                  |                   | $V_{CC} = 5.5 \text{ V},  0 \text{ V} \le V_{O} \le V_{CC},$<br>Output disabled                                                                                                                                                   | -5  | 5          | - 5 | 5   | μА   |

| lcc            | V <sub>CC</sub> supply current, operating |                   | $\begin{aligned} & \begin{array}{c} V_{CC} = 5.5 \text{ V}, & I_O = 0 \text{ mA}, \\ \hline CE1 = V_{IL} \text{ MAX}, & \\ CE2 = \overline{OE} = \overline{WE} = V_{IH}, & \\ f = \text{MAX} & \\ \end{aligned}$                  |     | 150        |     | 140 | mA   |

|                |                                           | TTL-level         | $V_{CC} = 5.5 \text{ V}$ , $\overrightarrow{CE1} \ge V_{IH} \text{ MIN}$ , $V_{IN} \le V_{IL} \text{ MAX or } \ge V_{IH} \text{ MIN}$ , $f = \text{MAX} = 1/t_{C(R)}$                                                             |     | 40         |     | 35  |      |

| lcc1           | V <sub>CC</sub> supply current, standby   | inputs            | $V_{CC} = 5.5 \text{ V},  \overline{CE1} \ge V_{IH} \text{ MIN}, \\ V_{IN} \le V_{IL} \text{ MAX or } \ge V_{IH} \text{ MIN}, \\ f = 0 \text{ MHz}$                                                                               |     | 38         |     | 38  | mA   |

| 301            | ,                                         | CMOS-level inputs | $\begin{split} & \begin{array}{c} V_{CC} = 5.5 \text{ V,} \\ \hline CE1 \geq V_{CC} - 0.2 \text{ V and} \\ [V_{IN} \geq V_{CC} - 0.2 \text{ V or} \\ \hline V_{IN} \leq V_{SS} + 0.2 \text{ V}] \\ f = 0 \text{ MHz} \end{split}$ |     | 10         |     | 10  | mA   |

<sup>†</sup> For conditions shown as MIN/MAX, use the appropriate value specified under the recommended operating conditions.

# capacitance over recommended ranges of supply voltage, f = 1 MHz, TA = 25°C‡

|    | PARAMETEI                        | 7                | MIN | MAX | UNIT |

|----|----------------------------------|------------------|-----|-----|------|

|    |                                  | OE, A2, A3, A10  |     | 12  |      |

| Ci | C <sub>i</sub> Input capacitance | All other inputs |     | 10  | pF   |

| Co | Output capacitance               | DQ1-DQ8          |     | 14  | pF   |

<sup>‡</sup> Capacitance measurements are made on sample basis only.

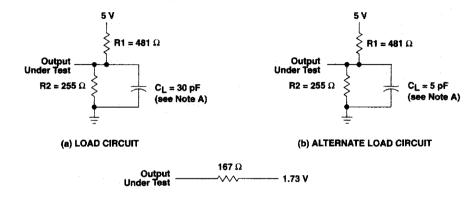

## PARAMETER MEASUREMENT INFORMATION

| PARAMETER                         | VALUE      |

|-----------------------------------|------------|

| Input pulse levels                | 0 V to 3 V |

| Input rise and fall times         | 2 ns       |

| Input and output reference levels | 1.5 V      |

(c) THEVENIN EQUIVALENT OF (a) OR (b)

NOTE A: CL includes probe and fixture capacitances.

Figure 1. Output Load Circuits

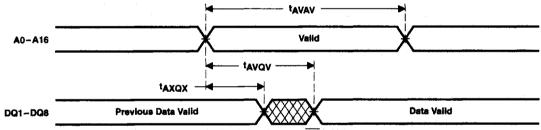

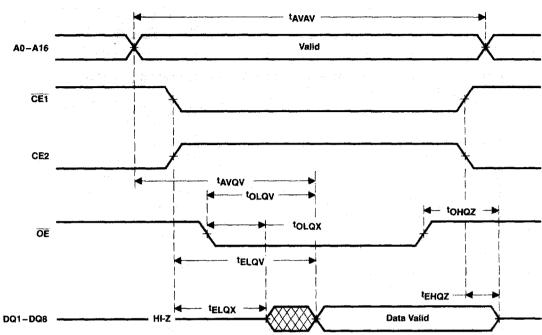

# read-cycle timing requirements over recommended ranges of supply voltage and operating tree-air temperature (unless otherwise noted)

|       |                  | ALT.   | '5C1008-20 | '5C10 | 08-25 | UNIT |

|-------|------------------|--------|------------|-------|-------|------|

|       |                  | SYMBOL | MIN MAX    | MIN   | MAX   | UNIT |

| tc(R) | Cycle time, read | †AVAV  | 20         | 25    |       | ns   |

# read-cycle switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                       | PARAMETER                                      | ALT.              | '5C1008-20<br>MIN MAX |    | '5C10   | 08-25 |      |

|-----------------------|------------------------------------------------|-------------------|-----------------------|----|---------|-------|------|

|                       | PARAME! ER                                     | SYMBOL            |                       |    | MIN MAX |       | UNIT |

| ta(A)                 | Access time from A0-A16                        | tavov             |                       | 20 |         | 25    | ns   |

| ta(E1)                | Access time from CE1 low                       | †ELQV             |                       | 20 |         | 25    | ns   |

| <sup>t</sup> a(E2)    | Access time from CE2 high                      | tELQV             |                       | 20 |         | 25    | ns   |

| <sup>t</sup> a(G)     | Access time from OE low                        | tOLQV             |                       | 7  |         | 10    | ns   |

| <sup>t</sup> v(A)     | Valid time of output data after address change | tAXQX             | 3                     |    | 3       |       | ns   |

| t <sub>en(E)</sub> †‡ | Output enable time from CE1 low or CE2 high    | tel-QX            | 3                     |    | 3       |       | ns   |

| ten(G)†‡              | Output enable time from OE low                 | toLax             | 0                     |    | 0       | min.  | ns   |

| tdis(E)†‡             | Output disable time from CE1 high and CE2 low  | t <sub>EHQZ</sub> | 0                     | 8  |         | 10    | ns   |

| tdis(G)†‡             | Output disable time from OE high               | tohoz             | 0                     | 8  |         | 10    | ns   |

<sup>†</sup> This parameter is specified by design but not tested.

<sup>‡</sup> Transition is measured ± 500 mV from steady-state voltage with the load shown in Figure 1(b).

NOTE A: All chip enables and output enables are held in their active state. WE is high.

Figure 2. Read-Cycle Timing, Device Continously Selected

## PARAMETER MEASUREMENT INFORMATION

NOTE A: Addresses valid prior to or coincident with latest occurring chip enable. WE is high.

Figure 3. Read-Cycle Timing, Enable Controlled

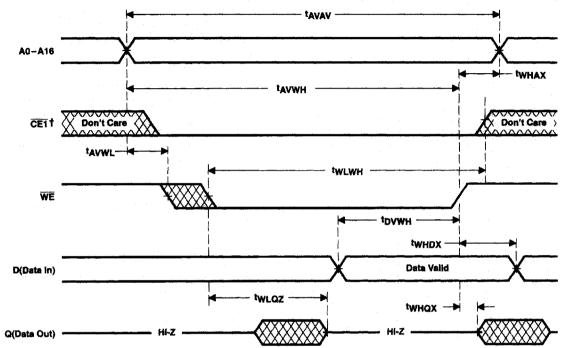

# write-cycle (WE controlled) timing requirements over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                        |                                      | ALT.              | '5C1008-20 |        | '5C1008-25 |     |      |

|------------------------|--------------------------------------|-------------------|------------|--------|------------|-----|------|

|                        |                                      | SYMBOL            | MIN        | MAX    | MIN        | MAX | UNIT |

| t <sub>C</sub> (W)     | Cycle time, write                    | tavav             | 20         |        | 25         |     | ns   |

| <sup>t</sup> w(W)      | Pulse duration, write                | twlwh<br>twleh    | 15         |        | 20         | 1   | ns   |

| t <sub>su(A)</sub> †   | Setup time. address                  | TAVWL             | 0          |        | 0          |     | ns   |

| t <sub>su(D)</sub> ‡   | Setup time, data to end of write     | <sup>t</sup> DVWH | 10         | in Eng | . 15       |     | ns   |

| t <sub>su(AWH)</sub> ‡ | Setup time. address to end of write  | †AVWH             | 15         |        | 20         |     | ns   |

| th(A)‡                 | Hold time, address from end of write | ₩HAX              | 0          |        | 0          |     | ns   |

| th(D) <sup>‡</sup>     | Hold time, data from end of write    | tWHDX             | 0          |        | 0          |     | ns   |

<sup>†</sup> Referenced to latest end of WE, CE1, or CE2

# write-cycle (WE controlled) switching characteristics over recommended ranges of supply voltage and operating free-air temperature (see Notes 3 and 4)

| PARAMETER | ALT.                             | '5C1008-20 |                | '5C1008-25 |     | LIMIT |      |

|-----------|----------------------------------|------------|----------------|------------|-----|-------|------|

|           | FARAMEIER                        | SYMBOL     | SYMBOL MIN MAX | MAX        | MIN | MAX   | UNIT |

| ten(W)§¶  | Enable time, output from WE high | twhqx      | - 5            |            | 5   |       | ns   |

| tdis(W)§¶ | Disable time. output from WE low | twLQZ      | 0              | 9          | 0   | 10    | ns   |

<sup>9</sup> Transition is measured ± 500 mV from steady-state voltage with the load shown in Figure 1(b).

NOTES: 3. If  $\overline{OE}$  goes low coincident with or after  $\overline{W}$  goes low, the output remains in the high-impedance state.

4. If  $\overline{CE1}$  goes low coincident with or after  $\overline{W}$  goes high, the output remains in the high-impedance state.

<sup>‡</sup> Referenced to earliest end of WE, CE1, or CE2

This parameter is specified by design but not tested.

<sup>†</sup>  $\overline{\text{OE}}$  is inactive (high). CE2 timing is the same as  $\overline{\text{CE1}}$  timing except the CE2 waveform is inverted with respect to  $\overline{\text{CE1}}$ .

Figure 4. Write-Cycle Timing, Write-Enable Controlled

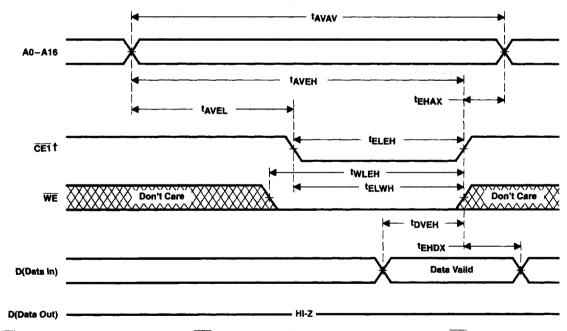

# write-cycle (CE controlled)timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Notes 3 and 4)

|                        |                                         | ALT.<br>SYMBOL    | '5C1008-20 |     | '5C1008-25 |     |      |

|------------------------|-----------------------------------------|-------------------|------------|-----|------------|-----|------|

|                        |                                         |                   | MIN        | MAX | MIN        | MAX | UNIT |

| tc(W)                  | Cycle time, write                       | †AVAV             | 20         | 110 | 25         |     | ns   |

| tw(W)                  | Pulse duration, write                   | WLEH              | 15         |     | 20         |     | ns   |

| <sup>t</sup> su(EW)    | Setup time. chip-enable to end of write | tELWH             | 15         |     | 20         |     | ns   |

| tsu(A) <sup>†</sup>    | Setup time. address                     | †AVEL             | 0          |     | 0          |     | ns   |

| t <sub>su(D)</sub> ‡   | Setup time, data to end of write        | <sup>t</sup> DVEH | 10         |     | 15         |     | ns   |

| t <sub>su(AWH)</sub> ‡ | Setup time, address to end of write     | †AVEH             | 15         |     | 20         |     | ns   |

| th(A)‡                 | Hold time, address from end of write    | <sup>†</sup> EHAX | 0          |     | 0          |     | ns   |

| th(D)#                 | Hold time, data from end of write       | tEHDX             | 0          |     | 0          |     | ns   |

<sup>†</sup> Referenced to latest end of WE, CE1, or C

NOTES: 3. If  $\overline{\text{OE}}$  goes low coincident with or after  $\overline{\text{W}}$  goes low, the output remains in the high-impedance state.

4. If  $\overline{\text{OE}}$  goes low coincident with or after  $\overline{\text{W}}$  goes high, the output remains in the high-impedance state.

TOE is inactive (high). CE2 timing is the same as CE1 timing except the CE2 waveform is inverted with respect to CE1.

Figure 5. Write-Cycle Timing, Chip-Enable Controlled

<sup>‡</sup> Referenced to earliest end of WE, CE1, or CE2

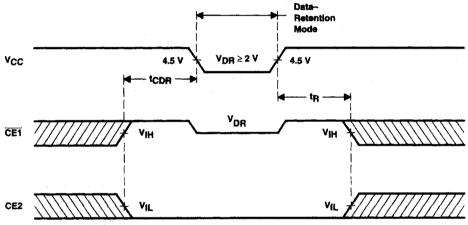

# data-retention characteristics over recommended operating free-air temperature range

|                  | PARAMETER                     |                                                      | '5C10 | '5C1008-20 |      | '5C1008-25 |      |

|------------------|-------------------------------|------------------------------------------------------|-------|------------|------|------------|------|

|                  | PARAME I ER                   | TEST CONDITIONS                                      | MIN   | MAX        | MIN  | MAX        | UNIT |

| VDR              | Data-retention voltage supply | V <sub>CC</sub> = 2 V                                | 2     |            | 2    |            | V    |

| ICC DR           | Data-retention current        | CE1 ≥ V <sub>CC</sub> = 0.2 V or                     |       | 2          |      | 2          | mA   |

| <sup>†</sup> CDR | Retention time †              | CE2 ≤ V <sub>SS</sub> + 0.2 V                        | 0     |            | 0    |            | ns   |

| tH               | Operation recovery time †     | V <sub>IN</sub> ≥ V <sub>CC</sub> - 0.2 V or ≤ 0.2 V | 20    |            | . 25 |            | ns   |

<sup>†</sup> This parameter is tested initially and after any design or process change.

NOTES: A. Either CE1 or CE2 can be used to begin data-retention mode.

B. For try and tCDR:  $\overline{CE1} \ge V_{CC} - 0.2 \text{ V}$  or  $CE2 \le 0.2 \text{ V}$ ,  $V_{IN} \ge V_{CC} - 0.2 \text{ V}$  or  $\le 0.2 \text{ V}$ .

Figure 6. Data-Retention Waveform