## Datasheet

## AS8223

## FlexRay Active Star Device

## 1 General Description

This document is subject to change without notice.

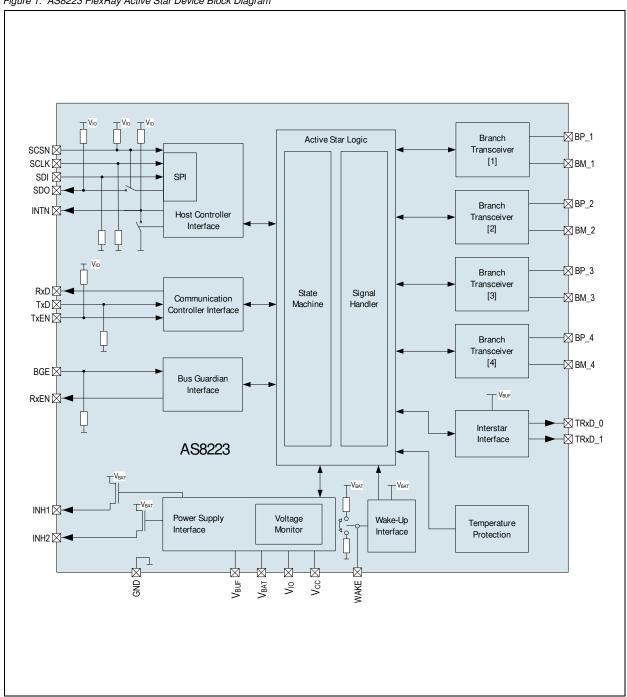

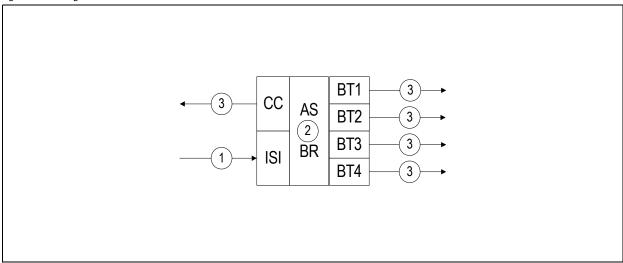

The AS8223 is a monolithic FlexRay compliant Active Star Device that manages communication traffic among four FlexRay branches of the network, expandable to more branches through an Interstar interface.

The four branches of the AS8223 operate as a FlexRay receiver and transmitter; wherein one of the communication paths operates as a receiver while the rest operate as a transmitter.

Additionally, the AS8223 comes with a Host Controller Interface to achieve active control of the power modes and error diagnosis. An autonomous mode is entered automatically, in which the device operates without the need for a host controller. A Communication Controller interface is also built into the AS8223, to provide the standard transceiver functionality on the ECU using the AS8223.

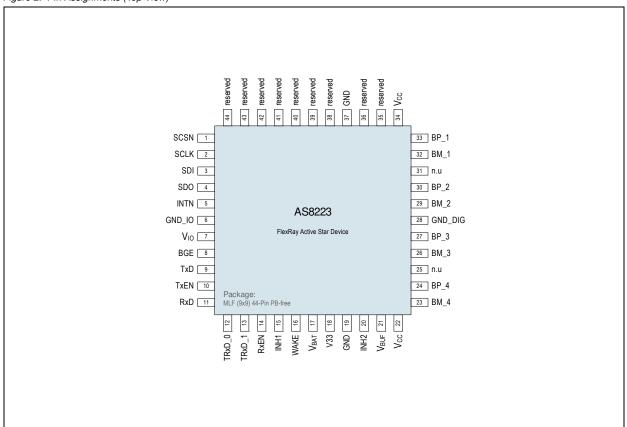

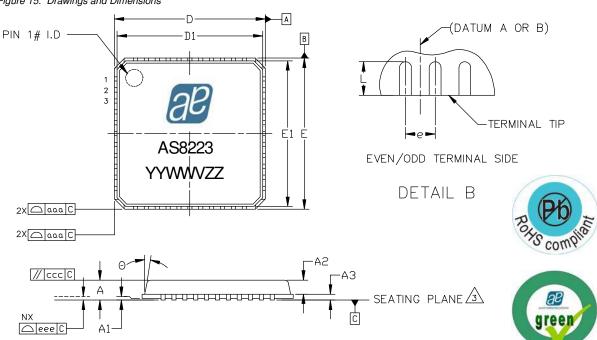

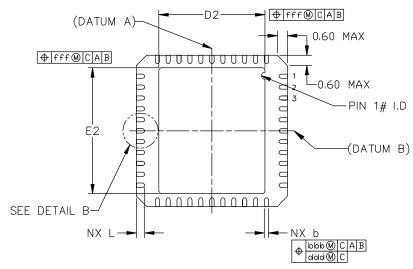

The product is available in 44-pin MLF (9x9) package.

## 2 Key Features

- Active Star Device with four branches

- Message forwarding on six communication paths (Communication Controller Interface, four FlexRay branches, Interstar Interface)

- Data transfer up to 10Mbps

- Compliant with FlexRay Electrical Physical Layer Specification V2.1 Rev B

- Excellent EMC performance

- Low susceptibility to EMI

- Interface with optional bus guardian for bus supervision

- Automatic thermal shutdown protection

- Supports 12V and 24V systems with low sleep current

- Integrated power management system

- Two INH pins for the external voltage regulators control

- Local wake-up input

- Remote wake-up capability via FlexRay bus

- Supports Autonomous Power Mode and Host Controlled Power Mode management

- Supports 2.5V, 3V, 3.3V and 5V microcontrollers; automatically adapts to interface levels

- Vcc supply voltage buffer for fail-safe conditions

- Protection against damage due to short circuit conditions on the FlexRay branches (positive and negative battery voltage)

- Operating ambient temperature range -40°C to +125°C

- RoHs compliant

- 44-pin MLF (9x9) package

## 3 Applications

The AS8223 FlexRay Active Star Device is tailored for automotive gateways with embedded FlexRay Active Star functionality. Several devices can be connected to the chip's Interstar interface, thereby enabling the extension of the FlexRay branches in order to meet specific application requirements.

Figure 1. AS8223 FlexRay Active Star Device Block Diagram

## Contents

| 1 | General Description                                  | 1  |

|---|------------------------------------------------------|----|

| 2 | Key Features                                         | 1  |

| 3 | Applications                                         | 1  |

| 4 | Pin Assignments                                      | 5  |

|   | 4.1 Pin Descriptions                                 |    |

| 5 | Absolute Maximum Ratings                             |    |

|   | Electrical Characteristics                           |    |

| • | 6.1 Supply Voltage                                   |    |

|   | 6.2 State Transitions Active Star                    |    |

|   | 6.3 Branch to Branch Timing                          |    |

|   | 6.4 Communication Controller to Branch Timing        |    |

|   | 6.5 Branch to Communication Controller Timing        |    |

|   | 6.6 Interstar to Branch Timing                       |    |

|   | 6.7 Branch to Interstar Timing                       |    |

|   | 6.8 Communication Controller to Interstar Timing     |    |

|   | 6.9 Interstar to Communication Controller Timing     |    |

|   | 6.10 Active Star General Timing                      |    |

|   | 6.11 Transmitter                                     |    |

|   | 6.12 Receiver                                        |    |

|   | 6.13 Bus Wake-up Detector                            | 15 |

|   | 6.14 Local Wake-up Detector                          | 15 |

|   | 6.15 Supply Voltage Monitor                          | 15 |

|   | 6.16 Bus Error Detection                             | 16 |

|   | 6.17 Over Temperature                                | 16 |

|   | 6.18 Power Supply Interface                          | 16 |

|   | 6.19 Communication Controller Interface              | 16 |

|   | 6.20 Host Controller Interface                       | 17 |

|   | 6.21 Bus Guardian Interface                          | 18 |

|   | 6.22 Interstar Interface                             | 18 |

| 7 | Detailed Description                                 | 19 |

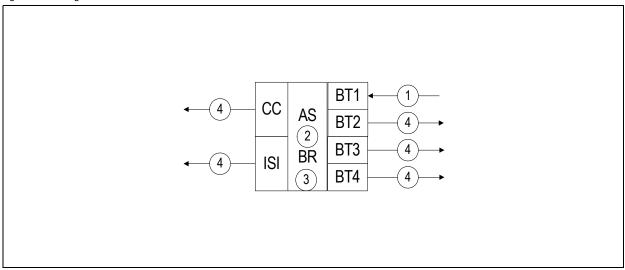

|   | 7.1 Routing Functionality of the Active Star         | 19 |

|   | 7.1.1 Branch Transceivers                            | 19 |

|   | 7.1.2 Communication Controller Interface             | 19 |

|   | 7.1.3 Interstar Interface                            |    |

|   | 7.1.4 Message Forwarding Function of the Active Star |    |

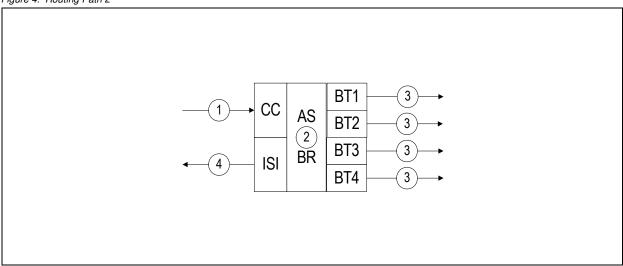

|   | 7.2 Routing Paths                                    | 20 |

|   | 7.2.1 Routing Path 1                                 |    |

|   | 7.2.2 Routing Path 2                                 |    |

|   | 7.2.3 Routing Path 3                                 |    |

|   | 7.3 Collisions                                       |    |

|   | 7.3.1 Extended Active Star (EAS) Collision           |    |

|   | 7.3.2 Active Star Device Collision                   |    |

|   | 7.3. Active star Collision Sequence                  |    |

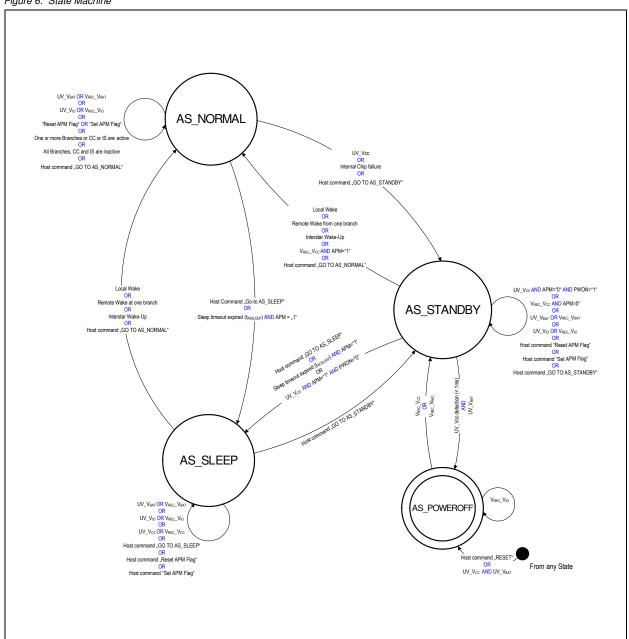

|   | 7.4.1 APM (Autonomous Power Mode)                    |    |

|   | 7.4.2 AS_NORMAL Mode                                 |    |

|   | 7.4.3 AS_STANDBY Mode                                |    |

|   | _                                                    | _• |

| 7.4.4 AS_SLEEP Mode                                 |                |

|-----------------------------------------------------|----------------|

| 7.5 Non Operating Modes of the Active Star          | 23             |

| 7.5.1 AS_POWEROFF                                   |                |

| 7.6 Mode Transitions of the Active Star             | 23             |

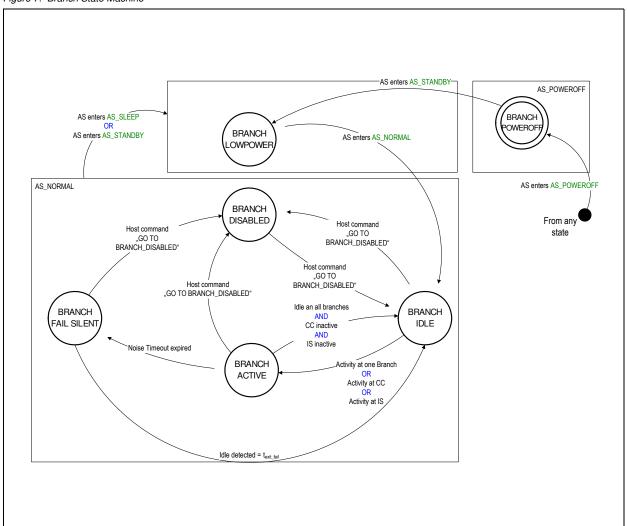

| 7.7 BRANCH Operating Modes                          |                |

| 7.7.1 BRANCH LOWPOWER Mode                          |                |

| 7.7.2 BRANCH_IDLE Mode                              |                |

| 7.7.3 BRANCH_ACTIVE Mode                            |                |

| 7.7.4 BRANCH_DISABLED Mode                          |                |

| 7.7.5 BRANCH_FAILSILENT Mode                        |                |

| 7.8 Non Operating Modes of BRANCH Logic             | 28             |

| 7.8.1 BRANCH_POWEROFF Mode                          |                |

| 7.9 Branch Transitions                              |                |

| 7.10 Undervoltage Events                            |                |

| 7.10.1 Undervoltage VCC Reaction Event              |                |

| 7.10.2 Undervoltage VCC Detection Event             |                |

| 7.10.3 Undervoltage Recovery VCC Event              |                |

| 7.10.4 Undervoltage VBAT Event                      |                |

| 7.10.5 Undervoltage Recovery VBAT Event             |                |

| 7.10.6 Undervoltage VIO Event                       |                |

| 7.10.7 Undervoltage Recovery VIO Event              |                |

| 7.10.8 Power On/Off Events                          |                |

| 7.11 Wake-up Events                                 |                |

| 7.11.1 Remote Wake-up Event                         | 30             |

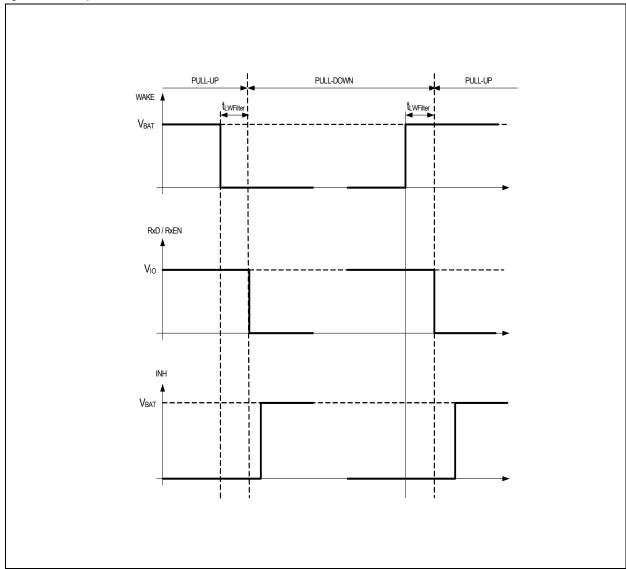

| 7.11.2 Local Wake-up Event                          |                |

| 7.11.3 Interstar Wake-up Event                      |                |

| 7.12 Host Interface Events                          |                |

| 7.13 Sleep Timer Events                             |                |

| 7.13.1 Enable Condition                             |                |

| 7.13.2 Reset Condition                              |                |

| 7.13.3 Timeout Condition                            |                |

| 7.14 Loss of Ground                                 |                |

| 7.15 Error and Status Flags                         |                |

| 7.15.1 General Active Star Error Flags              |                |

| 7.15.2 General Active Status Flags                  |                |

| 7.15.3 Branch Error Flags                           |                |

| 7.15.4 Branch Status Flags                          |                |

| 7.16 INTN                                           |                |

| 7.17 SPI Interface                                  |                |

| 7.17.1 SPI Frame                                    |                |

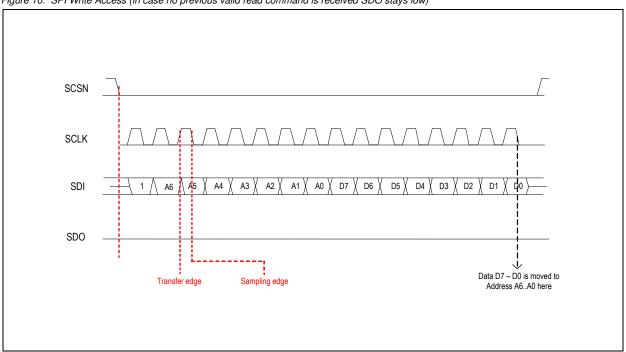

| 7.17.2 Write Access (no previous valid read access) |                |

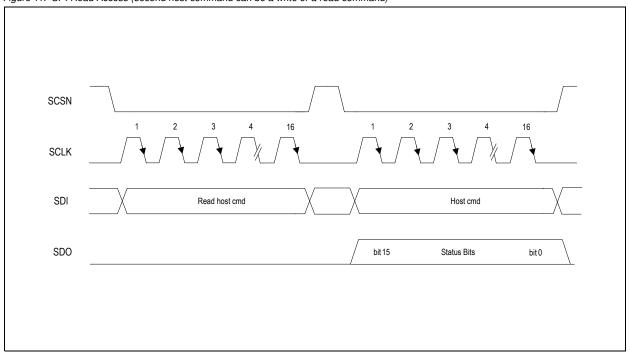

| 7.17.3 Read Access                                  |                |

| 7.17.4 Register Settings                            |                |

| 7.18 Timings                                        | 41             |

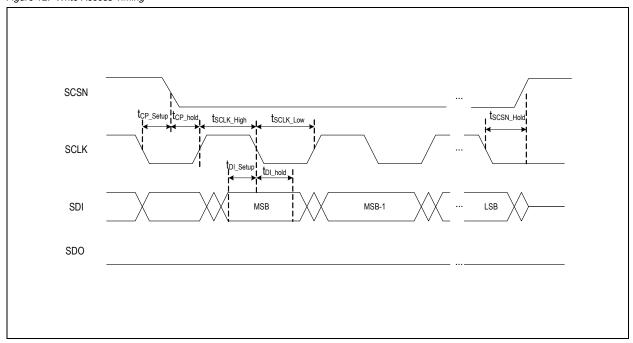

| 7.18.1 Write                                        |                |

| 7.18.2 Read                                         |                |

| 7.19 Inhibit Pins                                   |                |

| 7.20 Damage Tests (Class D)                         |                |

| Package Drawings and Markings                       |                |

| Ordering Information                                |                |

| OTOOTHING HITOTHIAUOH                               | <del>4</del> 0 |

8 9

# 4 Pin Assignments

Figure 2. Pin Assignments (Top View)

## 4.1 Pin Descriptions

Table 1. Pin Descriptions

| Pin Name | Pin Number | Pin Type                     | Description                |

|----------|------------|------------------------------|----------------------------|

| SCSN     | 1          | Digital input with pull-up   | SPI chip select            |

| SCLK     | 2          | Digital input with pull down | SPI clock                  |

| SDI      | 3          | Digital input with pull-down | SPI data in                |

| SDO      | 4          | Digital output / tristate    | SPI data out               |

| INTN     | 5          | Digital output open drain    | Interrupt output           |

| GNDIO    | 6          | Cupply                       | Ground                     |

| VIO      | 7          | Supply                       | I/O supply input voltage   |

| BGE      | 8          | Digital input with pull down | Bus guardian enable input  |

| TxD      | 9          | Digital input with pull-down | Transmit data input        |

| TxEN     | 10         | Digital input with pull-up   | Transmitter enable input   |

| RxD      | 11         | Digital output               | Receive data output        |

| TRxD_0   | 12         | Digital I/O                  | Interstar Bus line 0       |

| TRxD_1   | 13         | Digital I/O                  | Interstar Bus line 1       |

| RxEN     | 14         | Digital output               | Receive data enable output |

Table 1. Pin Descriptions

| Pin Name         | Pin Number | Pin Type      | Description                                             |

|------------------|------------|---------------|---------------------------------------------------------|

| INH1             | 15         | Analog I/O    | Inhibit output for switching external voltage regulator |

| WAKE             | 16         | Analog I/O    | Local Wake input                                        |

| VBAT             | 17         | Supply        | Battery supply input voltage                            |

| V33              | 18         | Analog I/O    | Internal voltage stabilizing output                     |

| GND              | 19         | Supply        | Ground                                                  |

| INH2             | 20         | Analog I/O    | Inhibit output for switching external voltage regulator |

| V <sub>BUF</sub> | 21         | Analog I/O    | TRxD_0, TRxD_1 stabilizing output                       |

| Vcc              | 22         | Supply        | Supply input voltage                                    |

| BM_4             | 23         | Analog I/O    | Bus line minus branch 4                                 |

| BP_4             | 24         | Analog I/O    | Bus line plus branch 4                                  |

| n.u              | 25         | -             | Not used                                                |

| BM_3             | 26         | Analog I/O    | Bus line minus branch 3                                 |

| BP_3             | 27         | Analog I/O    | Bus line plus branch 3                                  |

| GNDD             | 28         | Supply        | Digital ground                                          |

| BM_2             | 29         | A = -1 = -1/O | Bus line minus branch 2                                 |

| BP_2             | 30         | Analog I/O    | Bus line plus branch 2                                  |

| n.u              | 31         | -             | Not used                                                |

| BM_1             | 32         | Analan I/O    | Bus line minus branch 1                                 |

| BP_1             | 33         | Analog I/O    | Bus line plus branch 1                                  |

| Vcc              | 34         | Supply        | Supply voltage                                          |

| Reserved         | 35         | -             | To be connected to GND                                  |

| Reserved         | 36         | -             | To be connected to GND                                  |

| GND              | 37         | Supply        | Ground                                                  |

| Reserved         | 38         | -             | To be left unconnected                                  |

| Reserved         | 39         | -             | To be left unconnected                                  |

| Reserved         | 40         | -             | To be connected to GND or to be left unconnected        |

| Reserved         | 41         | -             | To be connected to GND or to be left unconnected        |

| Reserved         | 42         | -             | To be connected to GND or to be left unconnected        |

| Reserved         | 43         | -             | To be connected to GND or to be left unconnected        |

| Reserved         | 44         | -             | To be connected to GND or to be left unconnected        |

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 9 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: All voltages are referred to pin GND.

Table 2. Absolute Maximum Ratings

| Symbol            | Parameter                                                                               | Min  | Max                    | Units | Note                                                                             |

|-------------------|-----------------------------------------------------------------------------------------|------|------------------------|-------|----------------------------------------------------------------------------------|

| Electrical F      | arameters                                                                               |      |                        |       |                                                                                  |

| VBAT              | Battery Supply Voltage                                                                  | -0.3 | +40                    | V     |                                                                                  |

| Vcc               | Overal Aleltone                                                                         | -0.3 | +7.0                   | V     |                                                                                  |

| Vio               | Supply Voltage                                                                          | -0.3 | +7.0                   | V     | Vio < Vcc                                                                        |

| V <sub>BUF</sub>  | 0.1111.1                                                                                |      |                        | .,    |                                                                                  |

| V33               | Stabilizing voltage output                                                              | -0.3 | +5.0                   | V     |                                                                                  |

|                   | DC Voltage at INTN, TxD, RxD,<br>TxEN, BGE, RxEN, SCSN, SCLK,<br>SDI, SDO               | -0.3 | VIO + 0.3              | V     |                                                                                  |

| VTRxD0,<br>VTRxD1 | DC Voltage at Interstar interface                                                       | -0.3 | V <sub>BUF</sub> + 0.3 | V     |                                                                                  |

|                   | DC Voltage on pin WAKE, INH1, INH2                                                      | -0.3 | VBAT + 0.3             | V     |                                                                                  |

|                   | DC voltage at GNDIO, GNDD                                                               | -0.3 | +0.3                   | V     |                                                                                  |

|                   | DC Voltage at BP <sub>1-4</sub> and BM <sub>1-4</sub>                                   | -40  | +40                    | V     |                                                                                  |

|                   | Input current (latchup immunity)                                                        | -100 | 100                    | mA    | According to AEC-Q100-004                                                        |

| Electrostat       | c Discharge                                                                             |      | 1                      |       |                                                                                  |

|                   | Electrostatic discharge at bus lines VBAT, WAKE                                         | -4   | +4                     | kV    | According to AEC-Q100-002 (HBM)                                                  |

|                   | Electrostatic discharge at bus lines BP <sub>1-4</sub> , BM <sub>1-4</sub>              | -6   | +6                     | kV    | According to AEC-Q100-002 (HBM)                                                  |

| ESD               | Electrostatic discharge at bus lines BP <sub>1-4</sub> , BM <sub>1-4</sub> , VBAT, WAKE | -6   | +6                     | kV    | According to FlexRay Physical Layer EMC<br>Measurement Specification Version 3.0 |

|                   |                                                                                         | -2   | +2                     | kV    | According to AEC-Q100-002 (HBM)                                                  |

|                   | Electrostatic discharge on all pins                                                     | -500 | +500                   | V     | According to AEC-Q100-011<br>(Charge Device Model)                               |

|                   |                                                                                         | -100 | +100                   | V     | According to AEC-Q100-003 (Machine Model)                                        |

| Damage Te         | sts                                                                                     |      |                        |       |                                                                                  |

|                   |                                                                                         |      |                        | V     | ISO7637-2 test pulse 1; class D<br>(see Figure 14)                               |

| 11                | Transient voltage on                                                                    |      | +75                    | V     | ISO7637-2 test pulses 2a; class D<br>(see Figure 14)                             |

| U <sub>s</sub>    | VBAT, BM and BP pins                                                                    | -150 |                        | V     | ISO7637-2 test pulses 3a; class D<br>(see Figure 14)                             |

|                   |                                                                                         |      | +100                   | V     | ISO7637-2 test pulses 3b; class D<br>(see Figure 14)                             |

Table 2. Absolute Maximum Ratings

| Symbol            | Parameter                                          | Min | Max  | Units | Note                                                                                                                                                                                                                                                                               |

|-------------------|----------------------------------------------------|-----|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Dissip      | pation                                             |     |      |       |                                                                                                                                                                                                                                                                                    |

| Pt                | Total power dissipation (all supplies and outputs) |     | 1    | W     |                                                                                                                                                                                                                                                                                    |

| Temperature       | Ranges and Storage Conditions                      |     |      |       |                                                                                                                                                                                                                                                                                    |

| T <sub>strg</sub> | Storage temperature                                | -55 | +150 | °C    |                                                                                                                                                                                                                                                                                    |

| TJ                | Junction temperature                               | -40 | +150 | °C    |                                                                                                                                                                                                                                                                                    |

| TBODY             | Package body temperature                           |     | +260 | °C    | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices".  The lead finish for Pb-free leaded packages is matte tin (100% Sn). |

|                   | Humidity non-condensing                            | 5   | 85   | %     |                                                                                                                                                                                                                                                                                    |

| Фја               | Package thermal resistance                         |     | 25   | °C/W  |                                                                                                                                                                                                                                                                                    |

| MSL               | Moisture Sensitivity Level                         |     | 3    |       | Represents a maximum floor life time of 168h                                                                                                                                                                                                                                       |

## 6 Electrical Characteristics

In this specification, all the defined tolerances for external components are assured over the whole operation conditions range as well as over lifetime.

$T_{\text{J}}\text{=-}40^{\circ}\text{C to +150}^{\circ}\text{C}, \text{VCC}\text{=+}4.75\text{V to +5.25\text{V}}, \text{VBAT}\text{=-}5.5\text{V to +40\text{V}}, \text{VIO}\text{=+}2.2\text{ to VCC}, \text{R}_{\text{L}}\text{=-}45\Omega, \text{CL}\text{=-}100\text{pF}, \text{C}_{\text{RxD}}\text{=-}15\text{pF}, \text{C}_{\text{VBUF}}\text{=-}1\mu\text{F}, \text{C}_{\text{V33}}\text{=-}1\mu\text{F}, \text{C}_{\text{V33}}\text{=-1\mu\text{F}}, \text{C}_{\text{V33}}\text{=-}1\mu\text{F}, \text{C}_{\text{V33}}\text{=-}1\mu\text{$

## 6.1 Supply Voltage

Table 3. Supply Voltage

| Symbol           | Parameter                | Conditions                                                                                            | Min  | Тур | Max   | Units |

|------------------|--------------------------|-------------------------------------------------------------------------------------------------------|------|-----|-------|-------|

| Тамв             | Ambient temperature      |                                                                                                       | -40  |     | +125  | °C    |

| Vcc-Vio          | Difference of supplies   |                                                                                                       | -0.1 |     | +3.05 | V     |

|                  |                          | VBAT=12V; AS_SLEEP and<br>AS_STANDBY mode; TJ<125°C<br>(see footnote 1)                               | 0    |     | 150   | μA    |

| la va            | VBAT current consumption | VBAT=12V; AS_SLEEP and AS_STANDBY; TJ<150°C (see footnote 1)                                          | 0    |     | 150   | μA    |

| I <sub>BAT</sub> | AS_SLEEP a one remote    | VBAT=12V; AS_SLEEP and AS_ STANDBY mode; TJ<125°C, one remote wake-up branch active. (see footnote 1) | 0    |     | 100   | μА    |

|                  |                          | AS_NORMAL mode                                                                                        | 0    |     | 1     | mA    |

|                  |                          | AS_SLEEP and AS_STANDBY mode;<br>VCC = 0V to +5.25V<br>(see footnote 1)                               | -5   |     | 50    | μA    |

| Icc              | Vcc current consumption  | AS_NORMAL, all driver enabled                                                                         | 0    |     | 200   | mA    |

|                  |                          | AS_NORMAL, all driver enabled; $R_{\text{BUS}} = \infty \ \Omega$                                     | 0    |     | 50    | mA    |

| lio              | Vio current consumption  | AS_SLEEP and AS_STANDBY mode;<br>VIO = 0V to +5.25V<br>(see footnote 1)                               | -9   |     | +9    | μA    |

|                  |                          | AS_NORMAL mode                                                                                        | 0    |     | 1     | mA    |

|                  |                          | AS_NORMAL mode; I <sub>33</sub> =10mA                                                                 | 3    |     | 3.6   | ٧     |

| V <sub>33</sub>  | V33 voltage              | AS_SLEEP and AS_STANDBY mode;<br>I <sub>33</sub> =1mA                                                 | 2.5  |     | 3.6   | V     |

| V <sub>BUF</sub> | V <sub>BUF</sub> voltage |                                                                                                       | 1.2  |     | 1.3   | ٧     |

<sup>1.</sup> SCSN, SCLK, SDI, SDO, INTN, TxD, RxD, TxEN, BGE, RxEN, WAKE, INH1, INH2, TRxD\_0, TRxD\_1, Pin 36, Pin 38, Pin 39, Pin 35: Unconnected.

## 6.2 State Transitions Active Star

Table 4. State Transitions Active Star

| Symbol                        | Parameter                                                                   | Conditions                                            | Min | Тур | Max  | Units |

|-------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------|-----|-----|------|-------|

| tas_lp_inhx_h                 | Delay time Host Command to INHx = "high" from AS_SLEEP and AS_STANDBY mode  | INHx "high" = 80% VBAT                                |     |     | 50   | μs    |

| t <sub>AS_Normal_INHx_L</sub> | Delay time Host Command to INHx = "low" from AS_NORMAL mode                 | INHx "low" = 20% Vват,<br>10kΩ external pull-down     |     |     | 10   | μs    |

| tAS_Standby_INHx_L            | Delay time Host Command to INH1 = "low" from AS_STANDBY mode                | INH1 "low" = 20% VBAT 10k $\Omega$ external pull-down |     |     | 50   | μs    |

| tas_lp_inhx_h                 | Delay time wake-up event to INHx = "high" from AS_SLEEP and AS_STANDBY mode | INHx "high" = 80% VBAT                                |     |     | 50   | μs    |

| tas_lp_rxd_h                  | Delay time wake-up event to RxD = "high" from AS_SLEEP and AS_STANDBY mode  | Wake-up flag set                                      |     |     | 100  | μs    |

| tas_lp_rxen_h                 | Delay time wake-up event to RxEN = "high" from AS_SLEEP and AS_STANDBY mode | Wake-up flag set                                      |     |     | 100  | μs    |

| tassleep                      | Go-to-sleep timeout (APM mode)                                              | INH1 low = 20% VBAT<br>10kΩ external pull-down        | 640 |     | 6400 | ms    |

## 6.3 Branch to Branch Timing

Table 5. Branch to Branch Timing

| Symbol                               | Parameter                                             | Conditions                                  | Min  | Тур | Max | Units |

|--------------------------------------|-------------------------------------------------------|---------------------------------------------|------|-----|-----|-------|

| t <sub>BUSxy_TSS_length_change</sub> | Frame TSS length change from BUSx to BUSy             |                                             |      |     | 450 | ns    |

| tBUSxy_FES1_length_change            | Prolongation of last bit of a frame from BUSx to BUSy |                                             |      |     | 450 | ns    |

| $t_{BUSxy\_symbol\_length\_change}$  | Symbol length change                                  |                                             | -300 |     | 450 | ns    |

| t <sub>BUSxy01</sub>                 | Delay time from BUSx to BUSy positive edge            |                                             |      |     | 150 | ns    |

| t <sub>BUSxy10</sub>                 | Delay time from BUSx to BUSy negative edge            |                                             |      |     | 150 | ns    |

| t <sub>BUSxy_</sub> asymmetry        | Delay time from BUSx to<br>BUSy data asymmetry        | t <sub>BUSxy01</sub> – t <sub>BUSxy10</sub> | -8   |     | 8   | ns    |

## 6.4 Communication Controller to Branch Timing

Table 6. Communication Controller to Branch Timing

| Symbol                            | Parameter                                         | Conditions                                                            | Min | Тур | Max | Units |

|-----------------------------------|---------------------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|-------|

| t <sub>TxD_BUS01</sub>            | Delay time from TxD to BUS positive edge          | t <sub>TxD01</sub> = 5ns                                              |     |     | 50  | ns    |

| t <sub>TxD_BUS10</sub>            | Delay time from TxD to<br>BUS negative edge       | t <sub>TxD10</sub> = 5ns                                              |     |     | 50  | ns    |

| t <sub>TxD_BUS_asymmetry</sub>    | Delay time from TxD to BUS asymmetry              | t <sub>TXD_BUS10</sub> - t <sub>TXD_BUS01</sub>                       | -4  |     | 4   | ns    |

| t <sub>TxEN_BUS_Idle</sub> Active | Delay time from TxEN to<br>BUS active             |                                                                       |     |     | 250 | ns    |

| t <sub>TxEN_BUS_ActiveIdle</sub>  | Delay time from TxEN to<br>BUS idle               |                                                                       |     |     | 250 | ns    |

| t <sub>TxEN_BUS_asymmetry</sub>   | Delay time from TxEN to BUS active-idle asymmetry | t <sub>TxEN_BUS_Idle</sub> Active = t <sub>TxEN_BUS_</sub> ActiveIdle | -50 |     | 50  | ns    |

| tBGE_BUS_IdleActive               | Delay time from BGE to<br>BUS active              |                                                                       |     |     | 250 | ns    |

| tBGE_BUS_ActiveIdle               | Delay time from BGE to BUS idle                   |                                                                       |     |     | 250 | ns    |

## 6.5 Branch to Communication Controller Timing

Table 7. Branch to Communication Controller Timing

| Symbol                  | Parameter                                        | Conditions              | Min | Тур | Max | Units |

|-------------------------|--------------------------------------------------|-------------------------|-----|-----|-----|-------|

| tBUS_RxD10              | Delay from BUS to RxD negative edge              |                         |     |     | 80  | ns    |

| t <sub>BUS_RxD01</sub>  | Delay from BUS to RxD positive edge              |                         |     |     | 80  | ns    |

| t <sub>bit</sub>        | Bit time                                         |                         | 54  |     |     | ns    |

| tBUS_RxD_asymmetry      | Delay time from BUS to RxD asymmetry             | tBUS_RxD10 - tBUS_RxD01 | -5  |     | 5   | ns    |

| tBUS_RxEN01             | Delay time from BUS idle to RxEN positive edge   |                         | 50  |     | 400 | ns    |

| t <sub>BUS_RxEN10</sub> | Delay time from BUS active to RxEN negative edge |                         | 100 |     | 450 | ns    |

## 6.6 Interstar to Branch Timing

Table 8. Interstar to Branch Timing

| Symbol                          | Parameter                                | Conditions                                        | Min | Тур | Max | Units |

|---------------------------------|------------------------------------------|---------------------------------------------------|-----|-----|-----|-------|

| t <sub>IS01_BUS01</sub>         | Delay time from ISI to BUS positive edge | t <sub>IS01</sub> = 5ns                           |     |     | 70  | ns    |

| t <sub>IS01_BUS10</sub>         | Delay time from ISI to BUS negative edge | t <sub>IS10</sub> = 5ns                           |     |     | 70  | ns    |

| t <sub>IS_BUS_asymmetry</sub>   | Delay time from ISI to BUS asymmetry     | t <sub>IS10_BUS10</sub> - t <sub>IS01_BUS01</sub> | -5  |     | 5   | ns    |

| t <sub>IS_BUS_Idle</sub> Active | Delay time from ISI to BUS active        |                                                   |     |     | 200 | ns    |

| t <sub>IS_BUS_ActiveIdle</sub>  | Delay time from ISI to BUS idle          |                                                   |     |     | 200 | ns    |

## 6.7 Branch to Interstar Timing

Table 9. Branch to Interstar Timing

| Symbol                          | Parameter                                | Conditions            | Min | Тур | Max | Units |

|---------------------------------|------------------------------------------|-----------------------|-----|-----|-----|-------|

| t <sub>BUS_IS_</sub> ActiveIdle | Delay time from BUS idle to ISI idle     |                       | 50  |     | 400 | ns    |

| t <sub>BUS_IS_Idle</sub> Active | Delay time from BUS active to ISI active |                       | 100 |     | 450 | ns    |

| t <sub>BUS_IS10</sub>           | Delay from BUS to ISI negative edge      |                       |     |     | 100 | ns    |

| t <sub>BUS_IS01</sub>           | Delay from BUS to ISI positive edge      |                       |     |     | 100 | ns    |

| t <sub>bit</sub>                | Bit time                                 |                       | 54  |     |     | ns    |

| tBUS_IS_asymmetry               | Delay time from BUS to ISI asymmetry     | tBUS_IS10 - tBUS_IS01 | -5  |     | 5   | ns    |

## 6.8 Communication Controller to Interstar Timing

Table 10. Communication Controller to Interstar Timing

| Symbol                           | Parameter                                | Conditions                                        | Min | Тур | Max | Units |

|----------------------------------|------------------------------------------|---------------------------------------------------|-----|-----|-----|-------|

| t <sub>TxD01_IS01</sub>          | Delay time from TxD to ISI positive edge | $t_{TxD01} = 5$ ns                                |     |     | 50  | ns    |

| t <sub>TxD10_IS10</sub>          | Delay time from TxD to ISI negative edge | t <sub>TxD01</sub> = 5ns                          |     |     | 50  | ns    |

| t <sub>TxD_IS_</sub> asymmetry   | Delay time from TxD to ISI asymmetry     | t <sub>TxD01_IS01</sub> - t <sub>TxD10_IS10</sub> | -4  |     | 4   | ns    |

| t <sub>TxEN_IS_Idle</sub> Active | Delay time from TxEN to ISI active       |                                                   |     |     | 150 | ns    |

| t <sub>TxEN_IS_</sub> ActiveIdle | Delay time from TxEN to ISI idle         |                                                   |     |     | 150 | ns    |

| tBGE_IS_IdleActive               | Delay time from BGE to ISI active        |                                                   |     |     | 150 | ns    |

| tBGE_IS_ActiveIdle               | Delay time from BGE to ISI idle          |                                                   |     |     | 150 | ns    |

## 6.9 Interstar to Communication Controller Timing

Table 11. Interstar to Communication Controller Timing

| Symbol                        | Parameter                                 | Conditions                                        | Min | Тур | Max | Units |

|-------------------------------|-------------------------------------------|---------------------------------------------------|-----|-----|-----|-------|

| tIS01_RxD01                   | Delay time from ISI to RxD positive edge  | t <sub>IS01</sub> = 5ns                           |     |     | 50  | ns    |

| t <sub>IS01_RxD10</sub>       | Delay time from ISI to RxD negative edge  | t <sub>IS10</sub> = 5ns                           |     |     | 50  | ns    |

| t <sub>IS_RxD_asymmetry</sub> | Delay time from ISI to RxD asymmetry      | t <sub>IS10_RxD10</sub> - t <sub>IS01_RxD01</sub> | -5  |     | 5   | ns    |

| tis_RxEN_01                   | Delay time from ISI to RxEN positive edge |                                                   |     |     | 150 | ns    |

| t <sub>IS_RxEN_10</sub>       | Delay time from ISI to RxEN negative edge |                                                   |     |     | 150 | ns    |

## 6.10 Active Star General Timing

Table 12. Active Star General Timing

| Symbol                            | Parameter                                                                                        | Conditions                   | Min | Тур | Max | Units |

|-----------------------------------|--------------------------------------------------------------------------------------------------|------------------------------|-----|-----|-----|-------|

| tstar_col                         | Active Star collision filter time                                                                | Guaranteed by design         |     |     | 50  | ns    |

| t <sub>exit_fail</sub>            | Idle detection time to exit branch fail silent                                                   | Programmable via SPI command |     | 1.1 | 10  | μs    |

| t <sub>ears_shut</sub>            | Blanking time between two frames                                                                 |                              |     | 1   |     | μs    |

| t <sub>BranchNoiseTimeout</sub>   | Branch noise timeout                                                                             |                              | 1.5 |     | 10  | ms    |

| tCCNoiseTimeout                   | Communication Controller noise timeout                                                           |                              | 1.5 |     | 10  | ms    |

| t <sub>EarsShut_Fault</sub>       | Blanking time between two frames for faulty branches                                             |                              |     | 5   |     | μs    |

| t <sub>TxEN_RxD_</sub> ActiveIdle | Delay time from TxEN rising edge to RxD rising edge; change of bus active to bus idle (loopback) |                              |     |     | 250 | ns    |

## 6.11 Transmitter

The following parameters are applicable to all the branch transmitters.

Table 13. Transmitter

| Symbol                                                 | Parameter                                                                         | Conditions                                                                         | Min       | Тур | Max       | Units |

|--------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------|-----|-----------|-------|

| V <sub>BUS_DIFF_D0</sub>                               | Differential bus voltage low in BRANCH_ACTIVE mode (Data_0)                       | $V_{BPdata0} - V_{BMdata0}$ ;<br>$40\Omega < R_L < 55\Omega$                       | -2        |     | -0.6      | V     |

| V <sub>BUS_DIFF_D1</sub>                               | Differential bus voltage high in BRANCH_ACTIVE mode (Data_1)                      | $V_{BPdata1} - V_{BMdata1};$<br>$40\Omega < R_L < 55\Omega$                        | 0.6       |     | 2         | V     |

| $\Delta V_{BUS\_DIFF}$                                 | Matching between Data_0 and Data_1 differential bus voltage in BRANCH_ACTIVE mode | $V_{BUS\_DIFF\_D0} - V_{BUS\_DIFF\_D1}$<br>$40\Omega < R_L < 55\Omega$             | -200      |     | 200       | mV    |

| V <sub>BUS_COM_D0</sub>                                | Common mode bus voltage in case of Data_0 in Branch non-low-power mode            | $V_{BPdata0}/2+V_{BMdata0}/2$<br>$40\Omega < R_L < 55\Omega$                       | 0.4 * Vcc |     | 0.6 * VCC | V     |

| V <sub>BUS_COM_D1</sub>                                | Common mode bus voltage in case of Data_1 in Branch non-low-power mode            | $V_{\text{BPdata1}}/2 + V_{\text{BMdata1}}/2$ $40\Omega < R_{\text{L}} < 55\Omega$ | 0.4 * Vcc |     | 0.6 * Vcc | V     |

| ΔV BUS_COM                                             | Matching between Data_0 and Data_1 common mode voltage                            | $V_{BUS\_COM\_D0} - V_{BUS\_COM\_D1}$<br>$40\Omega < R_L < 55\Omega$               | -200      |     | 200       | mV    |

| V <sub>BUS_DIFF_Idle</sub>                             | Absolute differential bus voltage in bus idle mode                                |                                                                                    |           |     | 30        | mV    |

| IBP <sub>BMShortMax</sub><br>IBM <sub>BPShortMax</sub> | Absolute maximum current if BP shorted to BM                                      | $V_{BP} = V_{BM}$                                                                  |           |     | +100      | mA    |

| IBP <sub>GNDShortMax</sub>                             | Absolute maximum current if BP is shorted to GND                                  | V <sub>BP</sub> = 0V                                                               |           |     | +100      | mA    |

| IBM <sub>GNDShortMax</sub>                             | Absolute maximum current if BM is shorted to GND                                  | V <sub>BM</sub> = 0V                                                               |           |     | +100      | mA    |

| IBP <sub>-5VShortMax</sub>                             | Absolute maximum current if BP is shorted to -5V                                  | V <sub>BP</sub> = -5V                                                              |           |     | +100      | mA    |

| IBM <sub>-5VShortMax</sub>                             | Absolute maximum current if BM is shorted to -5V                                  | V <sub>BM</sub> = -5V                                                              |           |     | +100      | mA    |

| IBP <sub>27VShortMax</sub>                             | Absolute maximum current if BP is shorted to 27V                                  | V <sub>BP</sub> = 27V                                                              |           |     | +100      | mA    |

Table 13. Transmitter

| Symbol                      | Parameter                                                | Conditions                    | Min  | Тур | Max   | Units |

|-----------------------------|----------------------------------------------------------|-------------------------------|------|-----|-------|-------|

| IBM <sub>27VShortMax</sub>  | Absolute maximum current if BM is shorted to 27V         | V <sub>BM</sub> = 27V         |      |     | +100  | mA    |

| IBP <sub>40</sub> VShortMax | Absolute maximum current if BP is shorted to 40V         | V <sub>BP</sub> = 40V         |      |     | +100  | mA    |

| IBM <sub>40VShortMax</sub>  | Absolute maximum current if BM is shorted to 40V         | V <sub>BM</sub> = 40V         |      |     | +100  | mA    |

| t <sub>BUS_TX10</sub>       | Fall time differential bus voltage                       | 80% – 20% of V <sub>BUS</sub> | 3.75 |     | 18.75 | ns    |

| t <sub>BUS_TX01</sub>       | Rise time differential bus voltage                       | 20% – 80% of V <sub>BUS</sub> | 3.75 |     | 18.75 | ns    |

| tBUS_IdleActive             | Differential bus voltage transition time: idle to active |                               |      |     | 30    | ns    |

| tBUS_ActiveIdle             | Differential bus voltage transition time: active to idle |                               |      |     | 30    | ns    |

## 6.12 Receiver

The following parameters are applicable to all the branch receivers.

Table 14. Receiver

| Symbol                                    | Parameter                                                   | Conditions                                                                                                                                                                                                                | Min       | Тур       | Max       | Units |

|-------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|-------|

| R <sub>BP</sub> , R <sub>BM</sub>         | BP, BM input resistance                                     | Idle mode; R <sub>BUS</sub> =∞                                                                                                                                                                                            | 10        |           | 40        | KΩ    |

| R <sub>DIFF</sub>                         | BP, BM differential input resistance                        | Idle mode; R <sub>BUS</sub> =∞                                                                                                                                                                                            | 20        |           | 80        | KΩ    |

| V <sub>CM</sub>                           | Common mode voltage at receiver                             | $ \begin{array}{c c} 2 \ x \ (   \ V_{Data0} \   \ - \   \ V_{Data1} \   ) \ / \\ (  \ V_{Data0} \   \ + \   \ V_{Data1} \  ) \ x \ 100\%, \ Test \\ with \ (V_{BP} \ + \ V_{BM})/2 \ = \ V_{CM} \ = \ 2.5V \end{array} $ | -10       |           | +15       | V     |

| V <sub>BPidle</sub> , V <sub>BMidle</sub> | Idle voltage in Branch non-low-power modes on pin BP, BM    | Branch non-low-power mode; $V_{TxEN}$ = VIO $40\Omega$    $100$ pF                                                                                                                                                        | 0.4 * Vcc | 0.5 * Vcc | 0.6 * Vcc | V     |

| VBPidle_low,<br>VBMidle_low               | Idle voltage in Branch low-power modes on pin BP, BM        | Branch low-power modes $40\Omega \mid\mid 100 \text{pF}$                                                                                                                                                                  | -0.2      | 0         | +0.2      | V     |

| I <sub>BPidle</sub>                       | Absolute idle output current on pin BP                      | -40V < V <sub>BP</sub> < 40V                                                                                                                                                                                              | 0         |           | 7.5       | mA    |

| I <sub>BMidle</sub>                       | Absolute idle output current on pin BM                      | -40 V < V <sub>BM</sub> < 40V                                                                                                                                                                                             | 0         |           | 7.5       | mA    |

| I <sub>BPleak</sub> , I <sub>BMleak</sub> | Absolute leakage current, when not powered                  | V <sub>BP</sub> =V <sub>BM</sub> =5V, VCC=0V, VBAT=0V;<br>VIO=0V                                                                                                                                                          | 0         |           | 20        | μΑ    |

| V <sub>BUSActiveHigh</sub>                | Activity detection differential input voltage high          | Branch non-low-power modes<br>-10V < (V <sub>BP</sub> , V <sub>BM</sub> ) < 15V                                                                                                                                           | 150       | 225       | 400       | mV    |

| V <sub>BUSActiveLow</sub>                 | Activity detection differential input voltage low           | Branch non-low-power modes<br>-10V < (V <sub>BP</sub> , V <sub>BM</sub> ) < 15V                                                                                                                                           | -400      | -225      | -150      | mV    |

| V <sub>Data1</sub>                        | Data1 detection differential input voltage                  | Pre-condition: Activity already detected. Branch non-low-power modes10V < (V <sub>BP</sub> , V <sub>BM</sub> ) < 15V                                                                                                      | 150       | 225       | 300       | mV    |

| V <sub>Data0</sub>                        | Data0 detection differential input voltage                  | Pre-condition: Activity already detected. Branch non-low-power modes10V < (V <sub>BP</sub> , V <sub>BM</sub> ) < 15V                                                                                                      | -300      | -225      | -150      | mV    |

| V <sub>DataErr</sub>                      | Mismatch between Data0 and Data1 differential input voltage | 2 x (   V <sub>Data0</sub>   -   V <sub>Data1</sub>   ) /<br>(  V <sub>Data0</sub>   +   V <sub>Data1</sub>  ) <sup>2)</sup>                                                                                              |           |           | 10        | %     |

| t <sub>bit</sub>                          | Receiving bit time                                          | C <sub>RxD</sub> =15pF                                                                                                                                                                                                    | 54        | 100       |           | ns    |

Table 14. Receiver

| Symbol                     | Parameter               | Conditions | Min | Тур | Max | Units |

|----------------------------|-------------------------|------------|-----|-----|-----|-------|

| tActivityDetection         | Activity detection time |            | 100 |     | 300 | ns    |

| t <sub>IdleDetection</sub> | Idle detection time     |            | 50  |     | 250 | ns    |

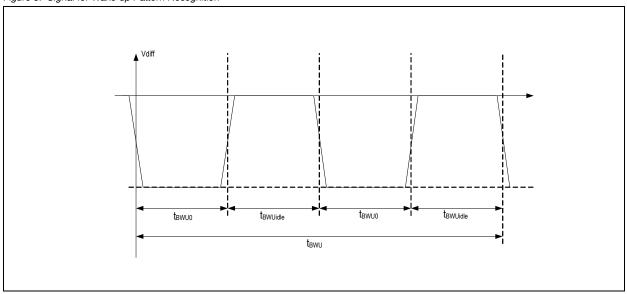

## 6.13 Bus Wake-up Detector

The following parameters are applicable to all the branch wake-up detectors.

Table 15. Bus Wake-up Detector

| Symbol                 | Parameter                                               | Conditions                                             | Min  | Тур | Max  | Units |

|------------------------|---------------------------------------------------------|--------------------------------------------------------|------|-----|------|-------|

| V <sub>BAT_WU</sub>    | VBAT supply to detect wake-up                           |                                                        | 7    |     |      | V     |

| t <sub>BWU0</sub>      | Data_0 detection time in remote wake-up pattern         | -10V<(V <sub>BP</sub> , V <sub>BM</sub> )<15V; VBAT>7V | 1    |     | 4    | μs    |

| t <sub>BWUldle</sub>   | Idle or Data_1 detection time in remote wake-up pattern | -10V<(V <sub>BP</sub> , V <sub>BM</sub> )<15V; VBAT>7V | 1    |     | 4    | μs    |

| t <sub>BWUDetect</sub> | Total remote wake-up detection time                     | -10V<(V <sub>BP</sub> , V <sub>BM</sub> )<15V; VBAT>7V | 48   |     | 140  | us    |

| V <sub>BWUTH</sub>     | Wake-up detector threshold                              | -10V<(V <sub>BP</sub> , V <sub>BM</sub> )<15V; VBAT>7V | -300 |     | -150 | mV    |

## 6.14 Local Wake-up Detector

Table 16. Local Wake-up Detector

| Symbol             | Parameter                                 | Conditions                                                                        | Min | Тур | Max | Units |

|--------------------|-------------------------------------------|-----------------------------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>LWUL</sub>  | Low level input current on WAKE pin       | VBAT=12V;<br>V <sub>WAKE</sub> =2V for t <t<sub>LWUFilter;<br/>VBAT&gt;7V</t<sub> | -20 |     | -5  | μA    |

| I <sub>LWUH</sub>  | High level input current on WAKE pin      | VBAT=12V;<br>V <sub>WAKE</sub> =4V for t <t<sub>LWUFilter;<br/>VBAT&gt;7V</t<sub> | 5   |     | 20  | μΑ    |

| tLWUFilter         | Local wake filter time                    | VBAT>7V                                                                           | 1   |     | 40  | μs    |

| V <sub>LWUTH</sub> | Local Wake-up detection threshold voltage |                                                                                   | 2   |     | 4   | V     |

## 6.15 Supply Voltage Monitor

Table 17. Supply Voltage Monitor

| Symbol              | Parameter                                               | Conditions | Min  | Тур | Max | Units |

|---------------------|---------------------------------------------------------|------------|------|-----|-----|-------|

| VBATTHH             | VBAT undervoltage recovery threshold                    |            | 3.5  |     | 4.5 | V     |

| VBAT <sub>THL</sub> | VBAT undervoltage detection threshold                   |            | 3    |     | 4   | V     |

| VCCTHH              | VCC undervoltage recovery threshold                     |            | 3.5  |     | 4.5 | V     |

| VCCTHL              | VCC undervoltage detection threshold                    |            | 3    |     | 4   | V     |

| VIOTHH              | Vio undervoltage recovery threshold                     |            | 1.25 |     | 2.0 | V     |

| VIOTHL              | Vio undervoltage detection threshold                    |            | 0.75 |     | 1.5 | V     |

| tuv_reaction        | Undervoltage reaction time for VCC                      |            | 30   |     | 700 | μs    |

| tuv_detection       | Undervoltage detection time for VBAT, VCC, VIO          |            | 100  |     | 700 | ms    |

| tuv_recovery        | Undervoltage recovery detection time for VBAT, VCC, VIO |            | 0.7  |     | 5   | ms    |

| tuv_debouncing      | Undervoltage debouncing time for VBAT, VCC, VIO         |            | 8    |     | 64  | μs    |

## 6.16 Bus Error Detection

The following parameters are applicable to all the branch error detectors.

Table 18. Bus Error Detection

| Symbol                 | Parameter                                                                       | Conditions                                 | Min | Тур | Max | Units |

|------------------------|---------------------------------------------------------------------------------|--------------------------------------------|-----|-----|-----|-------|

| I <sub>THL</sub>       | Absolute bus current for low current detection                                  | BRANCH_ACTIVE mode,<br>Transmitter enabled |     | 5   |     | mA    |

| Ітнн                   | Absolute bus current for high current detection                                 | BRANCH_ACTIVE mode,<br>Transmitter enabled |     | 40  |     | mA    |

| V <sub>SHORT</sub>     | Differential voltage on BP and BM for detecting short circuit between bus lines | BRANCH_ACTIVE mode,<br>Transmitter enabled |     | 225 |     | mV    |

| t <sub>BUS_ERROR</sub> | Bus error detection time                                                        | BRANCH_ACTIVE mode,<br>Transmitter enabled |     |     | 500 | ns    |

## 6.17 Over Temperature

Table 19. Over Temperature

| Symbol           | Parameter                   | Conditions | Min | Тур | Max | Units |

|------------------|-----------------------------|------------|-----|-----|-----|-------|

| OT <sub>TH</sub> | Over temperature threshold  |            | 150 |     | 180 | °C    |

| OT <sub>TL</sub> | Over temperature hysteresis |            | 10  |     | 20  | °C    |

## 6.18 Power Supply Interface

Table 20. Power Supply Interface

| Symbol            | Parameter                             | Conditions                         | Min | Тур | Max | Units |

|-------------------|---------------------------------------|------------------------------------|-----|-----|-----|-------|

| $\Delta V_{OINH}$ | High level voltage drop on INH1, INH2 | I <sub>INH</sub> =0.2mA; VBAT=5.5V | 0   |     | 0.8 | V     |

|                   | Leakage current                       | Sleep mode, V <sub>INH</sub> =0V   |     |     | 5   | μA    |

## 6.19 Communication Controller Interface

Table 21. Communication Controller Interface

| Symbol                    | Parameter                                                           | Conditions                                              | Min       | Тур | Max       | Units |

|---------------------------|---------------------------------------------------------------------|---------------------------------------------------------|-----------|-----|-----------|-------|

| $V_{TxDIH}$               | Threshold for detecting TxD as on logical high                      |                                                         |           |     | 0.7 * VIO | V     |

| V <sub>TxDIL</sub>        | Threshold for detecting TxD as on logical low                       |                                                         | 0.3 * VIO |     |           | V     |

| I <sub>TxDIH</sub>        | TxD high level input current                                        |                                                         | 30        |     | 100       | μΑ    |

| I <sub>TxDIL</sub>        | TxD low level input current                                         |                                                         | -5        |     | 5         | μΑ    |

| V <sub>TxENIH</sub>       | V <sub>TxENIH</sub> Threshold for detecting TxEN as on logical high |                                                         |           |     | 0.7 * VIO | V     |

| V <sub>TxENIL</sub>       | Threshold for detecting TxEN as on logical low                      |                                                         | 0.3 * VIO |     |           | V     |

| I <sub>TxENIH</sub>       | TxEN high level input current                                       |                                                         | -5        |     | 5         | μΑ    |

| I <sub>TxENIL</sub>       | TxEN low level input current                                        |                                                         | -100      |     | -30       | μΑ    |

| V <sub>RxDOH</sub>        | RxD high level output voltage                                       | I <sub>RxD</sub> =-4mA, Vio=5V                          | 0.8 * VIO |     | 1.0 * VIO | V     |

| V <sub>RxDOL</sub>        | RxD low level output voltage                                        | I <sub>RxD</sub> =4mA, V <sub>IO</sub> =5V              | 0         |     | 0.2 * VIO | V     |

| t <sub>RxDfall</sub>      | Fall time RxD voltage                                               | 80% – 20% of V <sub>RxDL</sub> ; C <sub>RxD</sub> =15pF |           |     | 5         | ns    |

| t <sub>RxDrise</sub>      | Rise time RxD voltage                                               | 20% – 80% of V <sub>RxDL</sub> ; C <sub>RxD</sub> =15pF |           |     | 5         | ns    |

| t <sub>RxD_mismatch</sub> | Mismatch of rise and fall time of RxD                               | t <sub>RxDrise</sub>   -   t <sub>RxDfall</sub>         | -2        |     | +2        | ns    |

## 6.20 Host Controller Interface

Table 22. Host Controller Interface

| Symbol                 | Parameter                                       | Conditions                                                             | Min       | Тур | Max       | Units |

|------------------------|-------------------------------------------------|------------------------------------------------------------------------|-----------|-----|-----------|-------|

| V <sub>SDI_IH</sub>    | Threshold for detecting SDI as on logical high  |                                                                        |           |     | 0.7 * VIO | V     |

| $V_{SDI\_IL}$          | Threshold for detecting SDI as on logical low   |                                                                        | 0.3 * VIO |     |           | V     |

| I <sub>SDI_IH</sub>    | SDI high level input current                    |                                                                        | 30        |     | 100       | μΑ    |

| I <sub>SDI_IL</sub>    | SDI low level input current                     |                                                                        | -5        |     | 5         | μΑ    |

| V <sub>SDO_OH</sub>    | SDO high level output voltage                   | I <sub>SDO</sub> =-4mA, VIO=5V                                         | 0.8 * VIO |     | 1.0 * Vio | V     |

| V <sub>SDO_OL</sub>    | SDO low level output voltage                    | I <sub>SDO</sub> =4mA, V <sub>IO</sub> =5V                             | 0         |     | 0.2 * VIO | V     |

| V <sub>SCLK_IH</sub>   | Threshold for detecting SCLK as on logical high |                                                                        |           |     | 0.7 * VIO | V     |

| V <sub>SCLK_IL</sub>   | Threshold for detecting SCLK as on logical low  |                                                                        | 0.3 * VIO |     |           | V     |

| I <sub>SCLK_IH</sub>   | SCLK high level input current                   |                                                                        | 30        |     | 100       | μΑ    |

| I <sub>SCLK_IL</sub>   | SCLK low level input current                    |                                                                        | -5        |     | 5         | μΑ    |

| V <sub>SCSN_IH</sub>   | Threshold for detecting SCSN as on logical high |                                                                        |           |     | 0.7 * VIO | V     |

| V <sub>SCSN_IL</sub>   | Threshold for detecting SCSN as on logical low  |                                                                        | 0.3 * VIO |     |           | V     |

| I <sub>SCSN_IH</sub>   | SCSN high level input current                   |                                                                        | 30        |     | 100       | μΑ    |

| I <sub>SCSN_IL</sub>   | SCSN low level input current                    |                                                                        | -5        |     | 5         | μΑ    |

| V <sub>INTN_OH</sub>   | INTN high level output voltage                  | I <sub>NTN</sub> =-4mA, VIO=5V                                         | 0.8 * VIO |     | 1.0 * VIO | ٧     |

| V <sub>INTN_OL</sub>   | INTN low level output voltage                   | I <sub>INTN</sub> =4mA, VIO=5V                                         | 0         |     | 0.2 * VIO | V     |

| BR <sub>SPI</sub>      | Bit rate                                        |                                                                        | 10 kbps   |     | 1 Mbps    |       |

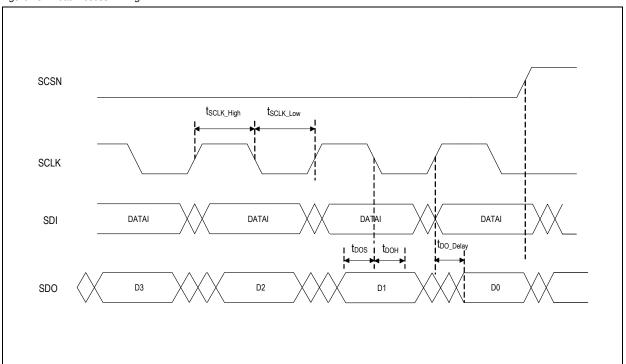

| tsclK_High             | Clock high time                                 |                                                                        | 500       |     |           | ns    |

| t <sub>SCLK_High</sub> | Clock low time                                  |                                                                        | 500       |     |           | ns    |

| t <sub>DI_Setup</sub>  | Data in setup time                              |                                                                        | 20        |     |           | ns    |

| t <sub>DI_Setup</sub>  | Data in hold time                               |                                                                        | 10        |     |           | ns    |

| tscsn_Hold             | SCSN in hold time                               |                                                                        | 100       |     |           | ns    |

| t <sub>DO_Delay</sub>  | Data out delay                                  |                                                                        |           |     | 150       | ns    |

| t <sub>DOS</sub>       | Data out setup time                             |                                                                        | 130       |     |           | ns    |

| t <sub>DOH</sub>       | Data out hold time                              |                                                                        | 130       |     |           | ns    |

| t <sub>DO_HZ</sub>     | Data out to high impedance delay                | Time for the SPI to release the SDO bus with respect to CS rising edge |           |     | 150       | ns    |

| t <sub>CP_Setup</sub>  | Clock setup time                                | Setup time of SCLK with respect to CS falling edge                     | 100       |     |           | ns    |

| t <sub>CP_Hold</sub>   | Clock hold time                                 | Hold time of SCLK with respect to CS falling edge                      | 100       |     |           | ns    |

| I <sub>SDO_PU</sub>    | SDO pull-up current                             |                                                                        | 30        |     | 100       | μA    |

| I <sub>INTN_PU</sub>   | INTN pull-up current                            |                                                                        | 30        |     | 100       | μA    |

## 6.21 Bus Guardian Interface

Table 23. Bus Guardian Interface

| Symbol              | Parameter                                      | Conditions                                   | Min       | Тур | Max       | Units |

|---------------------|------------------------------------------------|----------------------------------------------|-----------|-----|-----------|-------|

| $V_{BGEIH}$         | Threshold for detecting BGE as on logical high |                                              |           |     | 0.7 * VIO | V     |

| V <sub>BGEIL</sub>  | Threshold for detecting BGE as on logical low  |                                              | 0.3 * VIO |     |           | V     |

| I <sub>BGEIH</sub>  | BGE high level input current                   |                                              | 30        |     | 100       | μΑ    |

| I <sub>BGEIL</sub>  | BGE low level input current                    |                                              | -5        |     | 5         | μΑ    |

| V <sub>RxENOH</sub> | RxEN high level output voltage                 | I <sub>RxEN</sub> =-4mA, V <sub>IO</sub> =5V | 0.8 * VIO |     | 1.0 * Vio | V     |

| V <sub>RxENOL</sub> | RxEN low level output voltage                  | I <sub>RxEN</sub> =4mA, VIO=5V               | 0         |     | 0.2 * VIO | V     |

## 6.22 Interstar Interface

Table 24. Interstar Interface

| Symbol                         | Parameter                                    | Conditions                                              | Min                    | Тур  | Max                    | Units |

|--------------------------------|----------------------------------------------|---------------------------------------------------------|------------------------|------|------------------------|-------|

| V <sub>TRxDOH</sub>            | TRxD high level output voltage               |                                                         | 1                      | 1.25 | 1.5                    | V     |

| $V_{TRxDOL}$                   | TRxD low level output voltage                |                                                         | 0                      | 0    | 0.3                    | V     |

| V <sub>TRxD_IH</sub>           | Threshold for detecting TRxD as logical high |                                                         |                        |      | 0.7 * V <sub>BUF</sub> | V     |

| V <sub>TRxD_IL</sub>           | Threshold for detecting TRxD as logical low  |                                                         | 0.3 * V <sub>BUF</sub> |      |                        | V     |

| R <sub>TRxD_PU</sub>           | TRxD Internal pull-up resistance             |                                                         | 60                     | 100  | 180                    | ΚΩ    |

| t <sub>TRxD01</sub>            | TRxD rise time                               | 20% – 80% of V <sub>BUF</sub> ; C <sub>TRXD</sub> =60pF |                        | 5    |                        | ns    |

| t <sub>TRxD10</sub>            | TRxD fall time                               | 80% – 20% of V <sub>BUF</sub> ; C <sub>TRXD</sub> =60pF |                        | 5    |                        | ns    |

| t <sub>ISActiveDetection</sub> | Activity detection time                      |                                                         |                        | 10   |                        | ns    |

| tISIdleDetection               | Idle detection time                          |                                                         |                        | 10   |                        | ns    |

| tisCollision                   | Collision detection time                     |                                                         |                        | 10   |                        | ns    |

## 7 Detailed Description

The AS8223 FlexRay Active Star Device consists of six communication paths. During normal operation one of the communication paths is switched as receiver and the other paths as transmitter. Each of the four Branch Transceivers can be connected to different FlexRay bus lines to provide bi-directional communication of the extended FlexRay network.

Every message stream received at one communication path is converted into a digital signal and then forwarded to the transmitting communication paths.

The device supports different low power states which can be controlled by the host controller. Every Branch Transceiver supports several states for controlling the communication on the respective path.

### 7.1 Routing Functionality of the Active Star

#### 7.1.1 Branch Transceivers

The basic function of the Branch Transceiver (BT) is to convert the FlexRay bus signal into a digital signal and vice-versa according to the FlexRay Specification. Each BT includes a transmitter, a receiver, a wake-up detector and a failure detector. The receiver of each branch transceiver has got a digital interface to the central logic consisting of an RxD and a RxEN signal. Activity is detected on the FlexRay bus when the differential voltage between the lines BP and BM is lower than V<sub>BUSActiveLow</sub> or higher than V<sub>BUSActiveHigh</sub> for a time longer than t<sub>ActivityDetection</sub>. Idle is detected on the bus when the differential signal between BP and BM is higher than V<sub>BUSActiveLow</sub> or lower than V<sub>BUSActiveHigh</sub> for a time longer than t<sub>IdleDetection</sub>. The RxEN signal of the corresponding BT is active low and it gets active when activity on the FlexRay bus is detected. The RxEN signal of the corresponding BT is at logic high when Idle is detected on the bus (Idle, Idle\_LP, Idle\_HZ). The RxD signal is the translated frame from the incoming FlexRay signal to be received by the Active Star. RxD is logical low when the differential signal between BP and BM is lower than V<sub>Data0</sub>. RxD is logical high when the differential signal is higher than V<sub>Data1</sub>. The transmitter of the branch transceiver has got a digital interface to the central logic consisting of a TxD and a TxEN signal. The TxEN signal is an active low signal used by the Active Star Device to activate the transmitter. The TxD signal is the frame signal coming from the Active Star Device to be transmitted by the BT into the FlexRay bus. If the TxEN signal is driven low, the transmitter outputs V<sub>BUSX\_DIFF\_D0</sub> in case TxD is in logical low, and outputs V<sub>BUSX\_DIFF\_D1</sub> in case TxD signal is in logical high. The transmitter signals V<sub>BUSX\_DIFF\_Idle</sub> in case TxD signal is high.

### 7.1.2 Communication Controller Interface

The AS8223 has a Communication Controller Interface (CC) to connect a FlexRay Communication Controller directly with the central logic of the Active Star Device (ASD). The CC interface includes one receive data signal RxD, one transmit data signal TxD and one transmit enable signal TxEN. When sending a data stream, the central logic outputs the digital frame at the RxD signal of the CC interface. The ASD detects idle at the CC when the voltage level at the TxEN pin is higher than VTxENIH. The ASD detects activity at the CC when the voltage level at the TxEN pin is lower than VTxENIL. The TxD signal is the frame signal coming from the CC to be transmitted to the central logic. When the TxEN signal is driven low, the central logic receives Data0 when TxD voltage is lower than VTxDIL; the central logic receives Data1 when TxD voltage is higher than VTxDIH.