## GS1535 HD-LINX II™ Multi-Rate SDI Automatic Reclocker

#### GS1535 Data Sheet

#### **Key Features**

- SMPTE 292M, 259M and 344M compliant

- Supports data rates of 143, 177, 270, 360, 540, 1483.5, 1485 Mb/s

- · Supports DVB-ASI at 270Mb/s

- Auto and Manual Modes for rate selection

- Standards indication in Auto Mode

- 4:1 input multiplexor

- Lock Detect Output

- On-chip Input and Output Termination

- · Differential inputs and outputs

- Configuarble automatic Mute or Bypass when not locked

- Manual Bypass function

- SD/HD indication output to control GS1528 Dual Slew-Rate Cable Driver

- · Pb-free and Green

- Single 3.3V power supply

- Operating temperature range: 0°C to 70°C

#### Applications

SMPTE 292M, SMPTE 259M and SMPTE 344M

Serial Digital Interfaces

#### Description

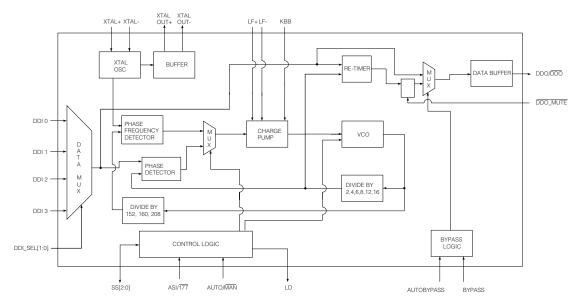

The GS1535 Multi-Rate Serial Digital Reclocker is designed to automatically recover the embedded clock signal and re-time the data from a SMPTE 292M, SMPTE 259M or SMPTE 344M compliant digital video signal.

The device removes the high frequency jitter components from the bit-serial stream. Input termination is on-chip for seamless matching to  $50\Omega$  transmission lines. An LVPECL compliant output interfaces seamlessly to the GS1528 Cable Driver

The GS1535 can operate in either auto or manual rate selection mode. In Auto mode the GS1535 automatically detects and locks onto an incoming SMPTE SDI data signal from 143 Mb/s to 1.485 Gb/s. For single rate data systems, the GS1535 can be configured to operate in manual mode. In both modes, the GS1535 requires only one external crystal to set the VCO frequency when not locked and provides adjustment free operation. In systems which require passing non-SMPTE data rates, the GS1535 will automatically or manually enter a bypass mode in order to pass the signal without reclocking.

The ASI/177 input pin allows for manual selection of support of either 177Mb/s or DVB-ASI inputs.

#### **GS1535 Functional Block Diagram**

## Contents

| Key Features                                                                                                                                                                                                                                                                                                                                                                               | 1                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Applications                                                                                                                                                                                                                                                                                                                                                                               | 1                                |

| Description                                                                                                                                                                                                                                                                                                                                                                                | 1                                |

| 1. Pin Out                                                                                                                                                                                                                                                                                                                                                                                 | 3                                |

| 1.1 Pin Assignment                                                                                                                                                                                                                                                                                                                                                                         | 3                                |

| 1.2 Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                       | 4                                |

| 2. Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                              | 7                                |

| 2.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                               | 7                                |

| 2.2 DC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                          | 7                                |

| 2.3 AC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                          | 8                                |

| 2.4 Input/Output Circuits                                                                                                                                                                                                                                                                                                                                                                  | 10                               |

| 3. Detailed Description                                                                                                                                                                                                                                                                                                                                                                    | 13                               |

| 3.1 Slew Rate Phase Lock Loop (S-PLL)                                                                                                                                                                                                                                                                                                                                                      | 13                               |

| 3.2 VCO                                                                                                                                                                                                                                                                                                                                                                                    | 14                               |

| 3.3 Charge Pump                                                                                                                                                                                                                                                                                                                                                                            | 14                               |

| 3.4 Frequency Acquisition Loop — The Phase-Frequency Detector                                                                                                                                                                                                                                                                                                                              | 14                               |

| 3.5 Phase Acquisition Loop — The Phase Detector                                                                                                                                                                                                                                                                                                                                            | 15                               |

|                                                                                                                                                                                                                                                                                                                                                                                            |                                  |

| 3.6 4:1 Input Mux                                                                                                                                                                                                                                                                                                                                                                          |                                  |

| 3.6 4:1 Input Mux<br>3.7 Automatic And Manual Data Rate Selection                                                                                                                                                                                                                                                                                                                          | 15                               |

|                                                                                                                                                                                                                                                                                                                                                                                            | 15<br>16                         |

| 3.7 Automatic And Manual Data Rate Selection                                                                                                                                                                                                                                                                                                                                               | 15<br>16<br>17                   |

| 3.7 Automatic And Manual Data Rate Selection<br>3.8 Bypass Mode                                                                                                                                                                                                                                                                                                                            | 15<br>16<br>17<br>17             |

| <ul><li>3.7 Automatic And Manual Data Rate Selection</li><li>3.8 Bypass Mode</li><li>3.9 DVB/ASI Operation</li></ul>                                                                                                                                                                                                                                                                       | 15<br>16<br>17<br>17<br>17       |

| <ul> <li>3.7 Automatic And Manual Data Rate Selection</li> <li>3.8 Bypass Mode</li> <li>3.9 DVB/ASI Operation</li></ul>                                                                                                                                                                                                                                                                    | 15<br>16<br>17<br>17<br>17<br>18 |

| <ul> <li>3.7 Automatic And Manual Data Rate Selection</li> <li>3.8 Bypass Mode</li> <li>3.9 DVB/ASI Operation</li></ul>                                                                                                                                                                                                                                                                    |                                  |

| <ul> <li>3.7 Automatic And Manual Data Rate Selection</li></ul>                                                                                                                                                                                                                                                                                                                            |                                  |

| <ul> <li>3.7 Automatic And Manual Data Rate Selection</li> <li>3.8 Bypass Mode</li> <li>3.9 DVB/ASI Operation</li> <li>3.10 LOCK</li> <li>3.11 Output Drivers</li> <li>3.12 Output Mute</li> <li>4. Application Reference Design</li> <li>4.1 Typical Application Circuit</li> <li>5. References</li> </ul>                                                                                |                                  |

| <ul> <li>3.7 Automatic And Manual Data Rate Selection</li> <li>3.8 Bypass Mode</li> <li>3.9 DVB/ASI Operation</li> <li>3.10 LOCK</li> <li>3.11 Output Drivers</li> <li>3.12 Output Mute</li> <li>4. Application Reference Design</li> <li>4.1 Typical Application Circuit</li> </ul>                                                                                                       |                                  |

| <ul> <li>3.7 Automatic And Manual Data Rate Selection</li> <li>3.8 Bypass Mode</li> <li>3.9 DVB/ASI Operation</li> <li>3.10 LOCK</li> <li>3.11 Output Drivers</li> <li>3.12 Output Mute</li> <li>4. Application Reference Design</li> <li>4.1 Typical Application Circuit</li> <li>5. References</li> </ul>                                                                                |                                  |

| <ul> <li>3.7 Automatic And Manual Data Rate Selection</li> <li>3.8 Bypass Mode</li> <li>3.9 DVB/ASI Operation</li> <li>3.10 LOCK</li> <li>3.10 Upt Drivers</li> <li>3.12 Output Drivers</li> <li>3.12 Output Mute</li> <li>4. Application Reference Design</li> <li>4.1 Typical Application Circuit</li> <li>5. References</li> <li>6. Package &amp; Ordering Information</li> </ul>       |                                  |

| <ul> <li>3.7 Automatic And Manual Data Rate Selection</li> <li>3.8 Bypass Mode</li> <li>3.9 DVB/ASI Operation</li> <li>3.10 LOCK</li> <li>3.11 Output Drivers</li> <li>3.12 Output Mute</li> <li>4. Application Reference Design</li> <li>4.1 Typical Application Circuit</li> <li>5. References</li> <li>6. Package &amp; Ordering Information</li> <li>6.1 Package Dimensions</li> </ul> |                                  |

## 1. Pin Out

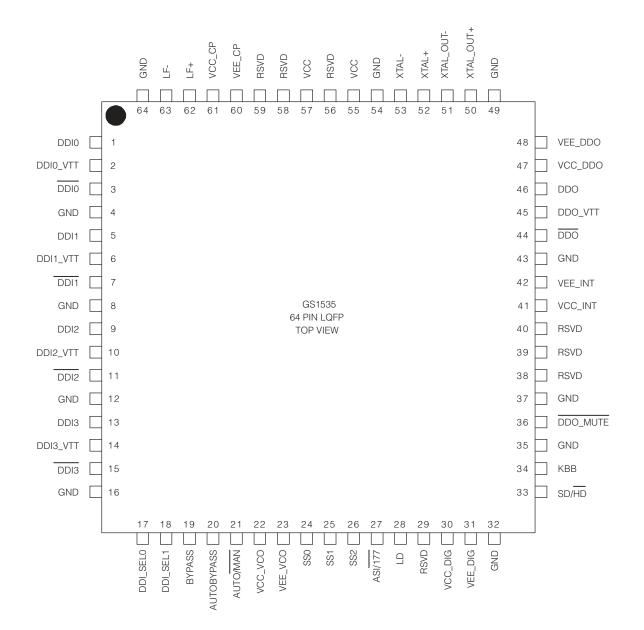

### **1.1 Pin Assignment**

## **1.2 Pin Descriptions**

#### **Table 1-1: Pin Descriptions**

| Pin<br>Number | Name         | Туре        | Description                                                                                            |                                                                                      |                      |                                             |  |

|---------------|--------------|-------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------|---------------------------------------------|--|

| 1, 3          | DDI0, DDI0   | INPUT       | Serial digital dif                                                                                     | ferential input 0.                                                                   |                      |                                             |  |

| 2             | DDI0_VTT     | PASSIVE     | Center tap of tv                                                                                       | vo 50 $\Omega$ on-chip t                                                             | ermination resistors | between DDI0 and $\overline{\text{DDI0}}$ . |  |

| 5, 7          | DDI1,DDI1    | INPUT       | Serial digital dif                                                                                     | ferential input 1.                                                                   |                      |                                             |  |

| 6             | DDI1_VTT     | PASSIVE     | Center tap of tv                                                                                       | vo 50 $\Omega$ on-chip t                                                             | ermination resistors | between DDI1 and DDI1.                      |  |

| 9, 11         | DDI2, DDI2   | INPUT       | Serial digital dif                                                                                     | ferential input 2.                                                                   |                      |                                             |  |

| 10            | DDI2_VTT     | PASSIVE     | Center tap of tv                                                                                       | vo 50 $\Omega$ on-chip t                                                             | ermination resistors | between DDI2 and $\overline{\text{DDI2}}$ . |  |

| 13, 15        | DDI3, DDI3   | INPUT       | Serial digital dif                                                                                     | ferential input 3                                                                    |                      |                                             |  |

| 14            | DDI3_VTT     | PASSIVE     | Center tap of tv                                                                                       | Center tap of two 50 $\Omega$ on-chip termination resistors between DDI3 and DDI3.   |                      |                                             |  |

| 17, 18        | DDI_SEL[1:0] | LOGIC INPUT | Serial digital inp                                                                                     | out select.                                                                          |                      |                                             |  |

|               |              |             | DDI_SEL1                                                                                               | DDI_SEL0                                                                             | INPUT<br>SELECTED    |                                             |  |

|               |              |             | 0                                                                                                      | 0                                                                                    | DDI0                 |                                             |  |

|               |              |             | 0                                                                                                      | 1                                                                                    | DDI1                 |                                             |  |

|               |              |             | 1                                                                                                      | 0                                                                                    | DDI2                 |                                             |  |

|               |              |             | 1                                                                                                      | 1                                                                                    | DDI3                 |                                             |  |

| 19            | BYPASS       | LOGIC INPUT | Bypasses the reclocker stage (Active HIGH). When BYPASS is HIGH, it overwrites the AUTOBYPASS setting. |                                                                                      |                      |                                             |  |

| 20            | AUTOBYPASS   | LOGIC INPUT | Automatically b (Active HIGH).                                                                         | Automatically bypasses the reclocker stage when the PLL is not locked (Active HIGH). |                      |                                             |  |

| 21            | AUTO/MAN     | LOGIC INPUT | When active, th                                                                                        | When active, the standard is automatically detected from the input data rate.        |                      |                                             |  |

#### Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number                                 | Name                    | Туре          | Description                                                                                                                                                                                     |              |              |                                                               |  |  |

|-----------------------------------------------|-------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|---------------------------------------------------------------|--|--|

| 24, 25, 26                                    | SS[2:0]                 | BIDIRECTIONAL | When AUTO/MAN is HIGH, SS[0:2] are outputs, displaying the data rate to which the PLL has locked.<br>When AUTO/MAN is LOW, SS[0:2] are inputs, forcing the PLL to lock only selected data rate. |              |              |                                                               |  |  |

|                                               |                         |               | SS2                                                                                                                                                                                             | SS1          | SS0          | DATA RATE<br>SELECTED/FORCED (Mb/s)                           |  |  |

|                                               |                         |               | 0                                                                                                                                                                                               | 0            | 0            | 143                                                           |  |  |

|                                               |                         |               | 0                                                                                                                                                                                               | 0            | 1            | 177                                                           |  |  |

|                                               |                         |               | 0                                                                                                                                                                                               | 1            | 0            | 270                                                           |  |  |

|                                               |                         |               | 0                                                                                                                                                                                               | 1            | 1            | 360                                                           |  |  |

|                                               |                         |               | 1                                                                                                                                                                                               | 0            | 0            | 540                                                           |  |  |

|                                               |                         |               | 1                                                                                                                                                                                               | 0            | 1            | 1483.5/1485                                                   |  |  |

| 27                                            | ASI/177                 | LOGIC INPUT   | Disables 177Mbps data rate in the AUTO data rate detection circuit. This prevents a FALSE LOCK to 177Mbps when using DVB/ASI.                                                                   |              |              |                                                               |  |  |

| 28                                            | LD                      | OUTPUT        | LOCK DETE                                                                                                                                                                                       | ECT. HIGH    | I when the   | PLL is locked.                                                |  |  |

| 29                                            | RSVD                    | RESERVED      | DO NOT CO                                                                                                                                                                                       | NNECT.       |              |                                                               |  |  |

| 33                                            | SD/HD                   | OUTPUT        | This signal is LOW when the reclocker has locked to 1.485Gbps or 1.485/1.001Gbps, and HIGH when the reclocker has locked to 143Mbps, 177Mbps, 270Mbps, 360Mbps, or 540Mbps.                     |              |              |                                                               |  |  |

| 34                                            | KBB                     | ANALOG INPUT  | Controls the<br>reclocking a                                                                                                                                                                    |              |              | e PLL. Leave this pin floating for serial                     |  |  |

| 36                                            | DDO_MUTE                | LOGIC INPUT   | Mutes the D                                                                                                                                                                                     | DO/DDO d     | outputs, wł  | nen not in bypass mode.                                       |  |  |

| 44, 46                                        | DDO, DDO                | OUTPUT        | Differential S                                                                                                                                                                                  | Serial Digit | al Outputs   |                                                               |  |  |

| 45                                            | DDO_VTT                 | PASSIVE       | Center tap o                                                                                                                                                                                    | f two 50Ω    | on-chip te   | rmination resistors between DDO and $\overline{\text{DDO}}$ . |  |  |

| 50, 51                                        | XTAL_OUT+,<br>XTAL_OUT- | OUTPUT        | Differential b                                                                                                                                                                                  | ouffered ou  | itputs of th | e reference oscillator.                                       |  |  |

| 52, 53                                        | XTAL+, XTAL-            | INPUT         | Reference c                                                                                                                                                                                     | rystal inpu  | t. Connec    | t to the GO1535.                                              |  |  |

| 62, 63                                        | LF+, LF-                | PASSIVE       | Loop filter ca                                                                                                                                                                                  | apacitor co  | nnection.    | (C <sub>LF</sub> = 47nF).                                     |  |  |

| 4, 8, 12,16,<br>32, 35, 37,<br>43, 49, 54, 64 | GND                     | PASSIVE       | Recommended connect to GND.                                                                                                                                                                     |              |              |                                                               |  |  |

| 43                                            | GND_DRV                 | PASSIVE       | Recommended connect to GND.                                                                                                                                                                     |              |              |                                                               |  |  |

#### Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number             | Name    | Туре     | Description                                                                               |

|---------------------------|---------|----------|-------------------------------------------------------------------------------------------|

| 55, 57                    | VCC     | PASSIVE  | Recommend connect to 3.3V.                                                                |

| 22                        | VCC_VCO | POWER    | Most positive power supply connection for the internal VCO section.<br>Connect to 3.3V.   |

| 30                        | VCC_DIG | POWER    | Most positive power supply connection for the internal glue logic.<br>Connect to 3.3V.    |

| 41                        | VCC_INT | POWER    | Most positive power supply connection. Connect to 3.3V.                                   |

| 47                        | VCC_DDO | POWER    | Most positive power supply connection for the DDO/DDO output driver.<br>Connect to 3.3V.  |

| 61                        | VCC_CP  | POWER    | Most positive power supply connection for the internal charge pump.<br>Connect to 3.3V.   |

| 23                        | VEE_VCO | POWER    | Most negative power supply connection for the internal VCO section. Connect to ground.    |

| 31                        | VEE_DIG | POWER    | Most negative power supply connection for the internal glue logic.<br>Connect to ground.  |

| 42                        | VEE_INT | POWER    | Most negative power supply connection. Connect to ground.                                 |

| 48                        | VEE_DDO | POWER    | Most negative power supply connection for the DDO/DDO output driver. Connect to ground.   |

| 60                        | VEE_CP  | POWER    | Most negative power supply connection for the internal charge pump.<br>Connect to ground. |

| 38, 39, 40,<br>56, 58, 59 | RSVD    | RESERVED | Do not Connect.                                                                           |

# **2. Electrical Characteristics**

## 2.1 Absolute Maximum Ratings

| Parameter                 | Value                         |

|---------------------------|-------------------------------|

| Supply Voltage            | +3.6 V <sub>DC</sub>          |

| Input ESD Voltage         | 500V                          |

| Storage Temperature Range | -50°C< T <sub>s</sub> < 125°C |

| Inputs                    | V <sub>CC</sub> + 0.5V        |

#### Table 2-1: Absolute Maximum Ratings

## **2.2 DC Electrical Characteristics**

#### Table 2-2: DC Electrical Characteristics

$V_{cc}$  = 3.3V,  $T_A$  = 0°C to 70°C, unless otherwise shown

| Parameter                                                                    | Conditions           | Symbol          | Min   | Тур | Max   | Units | Test<br>Levels |

|------------------------------------------------------------------------------|----------------------|-----------------|-------|-----|-------|-------|----------------|

| Supply Voltage                                                               | Operating<br>Range   | V <sub>CC</sub> | 3.135 | 3.3 | 3.465 | V     | 3              |

| Power<br>Consumption                                                         | T <sub>A</sub> =25°C |                 | 408   | 600 | 849   | mW    | 5              |

| Supply Current                                                               | T <sub>A</sub> =25°C | I <sub>CC</sub> | 130   | 182 | 245   | mA    | 1              |

| Logic Inputs                                                                 | High                 | V <sub>IH</sub> | 2.0   | -   | -     | V     | 3              |

| DDI_SEL[1:0],<br>BYPASS,<br>AUTOBYPASS,<br>AUTO/MAN,<br>ASI/177,<br>SDO_MUTE | Low                  | V <sub>IL</sub> | -     | -   | 0.8   | V     | 3              |

| Logic Outputs                                                                | 250µA Load           | V <sub>OH</sub> | 3.2   | -   | -     | V     | 3              |

| SD/HD and LD                                                                 |                      | V <sub>OL</sub> | -     | -   | 0.6   | V     | 3              |

| <b>Bi-Directional Pins</b>                                                   | High                 | V <sub>IH</sub> | 2.0   | -   | -     | V     | 3              |

| SS[2:0 <u>],</u><br>AUTO/MAN = 0<br>(Manual Mode)                            | Low                  | V <sub>IL</sub> | -     | -   | 0.8   | V     | 3              |

| Bi-Directional Pins<br>SS[2:0] <u>,</u><br>AUTO/MAN = 1<br>(AUTO Mode)       | High                 | V <sub>OH</sub> | 2.6   | -   |       | V     | 1              |

|                                                                              | Low                  | V <sub>OL</sub> | -     | -   | 0.6   | V     | 1              |

#### Table 2-2: DC Electrical Characteristics

$V_{cc}$  = 3.3V,  $T_A$  = 0°C to 70°C, unless otherwise shown

| Parameter                  | Conditions     | Symbol          | Min                             | Тур                                  | Max                                     | Units | Test<br>Levels |

|----------------------------|----------------|-----------------|---------------------------------|--------------------------------------|-----------------------------------------|-------|----------------|

| XTAL_OUT+,<br>XTAL_OUT-    | High           | V <sub>OH</sub> | -                               | V <sub>CC</sub>                      | -                                       | V     | 7              |

| XIAL_001-                  | Low            | V <sub>OL</sub> | -                               | V <sub>CC</sub> - 0.285              | -                                       | V     | 7              |

| Serial Input<br>Voltage    | Common<br>mode |                 | 1.65 +<br>(V <sub>SID</sub> /2) | -                                    | V <sub>CC</sub> - (V <sub>SID</sub> /2) | V     | 1              |

| Output Voltage<br>SDO, SDO | Common<br>mode |                 | -                               | V <sub>CC</sub> - V <sub>OD</sub> /2 | -                                       | V     | 1              |

**Test Levels**

1. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges.

2. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges using correlated test.

3. Production test at room temperature and nominal supply voltage.

4. QA sample test.

5. Calculated result based on Level 1, 2, or 3.

6. Not tested. Guaranteed by design simulations.

7. Not tested. Based on characterization of nominal parts.

8. Not tested. Based on existing design/characterization data of similar product.

9. Indirect test.

## **2.3 AC Electrical Characteristics**

#### **Table 2-3: AC Electrical Characteristics**

$V_{cc}$  = 3.3V,  $T_A$  = 0°C to 70°C, unless otherwise shown

| Parameter                                   | Symbol             | Conditions                                                                      |              | Min  | Тур | Max  | Units             | Test<br>Levels |

|---------------------------------------------|--------------------|---------------------------------------------------------------------------------|--------------|------|-----|------|-------------------|----------------|

| Serial Input Data Rate                      |                    |                                                                                 |              | 143  | -   | 1485 | Mb/s              | 3              |

| Serial Input Jitter Tolerance               |                    | Worst case modulation<br>Eg. Square wave modulation<br>143, 270, 360, 1485 Mb/s |              | 0.8  | -   | -    | UI                | 1              |

| PLL Lock Time -<br>Asynchronous             | t <sub>ALOCK</sub> |                                                                                 |              | -    | 5   | 10   | ms                | 6,7            |

| PLL Lock Time - Synchronous                 | t <sub>SLOCK</sub> | C <sub>LF</sub> =47nF                                                           | SD/HD=0      | 0.29 | -   | -    | μS                | 6,7            |

|                                             |                    |                                                                                 | SD/HD=1      | 0.16 | -   | -    | μs                | 6,7            |

| Serial Output Rise/Fall Time<br>(20% - 80%) | t <sub>rSDO</sub>  | 50 $\Omega$ load (on (                                                          | chip)        | -    | 114 | -    | ps                | 6,7            |

|                                             | t <sub>fSDO</sub>  | _                                                                               |              | -    | 106 | -    | ps                | -              |

| Serial Input - Signal Swing                 | V <sub>SID</sub>   | 50 $\Omega$ load (on chip)                                                      |              | 100  | -   | 800  | mV <sub>p-p</sub> | 6,7            |

| Serial Output - Signal Swing                | V <sub>OD</sub>    | Differential (ac                                                                | cross 100Ω). | 1400 | -   | 2000 | mV <sub>p-p</sub> | -              |

#### Table 2-3: AC Electrical Characteristics

$V_{cc}$  = 3.3V,  $T_A$  = 0°C to 70°C, unless otherwise shown

| Parameter            | Symbol          | Conditions                |                   | Min | Тур  | Max  | Units | Test<br>Levels |

|----------------------|-----------------|---------------------------|-------------------|-----|------|------|-------|----------------|

| Serial Output Jitter | t <sub>IJ</sub> | KBB=Float,                | 143Mb/s           | -   | 0.02 | -    | UI    | 1              |

| (additive)           |                 | PRN, 2 <sup>23</sup> -1   | 177Mbs            | -   | 0.02 | -    | UI    | 1              |

|                      |                 |                           | 270Mb/s           | -   | 0.02 | 0.09 | UI    | 1              |

|                      |                 |                           | 360Mbs            | -   | 0.03 | -    | UI    | 1              |

|                      |                 |                           | 540Mbs            | -   | 0.03 | 0.09 | UI    | 1              |

|                      |                 |                           | 1485Mb/s          | -   | 0.06 | 0.13 | UI    | 1              |

|                      |                 |                           | BYPASS            | -   | 0.06 | 0.13 | UI    | 1              |

| Loop Bandwidth       | BWLOOP          | 1.485 Gb/s<br>KBB = FLOAT |                   | -   | 1.5  | -    | MHz   | 6,7            |

|                      |                 | 1.485 Gb/s<br>KBB = GND   | <0.1dB<br>Peaking | -   | 3.5  | -    | MHz   | 6,7            |

|                      |                 | 270 Mb/s<br>KBB = FLOAT   |                   | -   | 520  | -    | KHz   | 6,7            |

|                      |                 | 270 Mb/s<br>KBB = GND     |                   | -   | 1000 | -    | KHz   | 6,7            |

Test Levels

1. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges.

2. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges using correlated test.

3. Production test at room temperature and nominal supply voltage.

4. QA sample test.

5. Calculated result based on Level 1, 2, or 3.

6. Not tested. Guaranteed by design simulations.

7. Not tested. Based on characterization of nominal parts.

8. Not tested. Based on existing design/characterization data of similar product.

9. Indirect test.

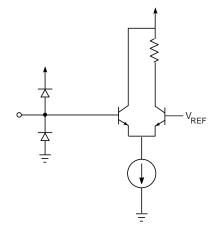

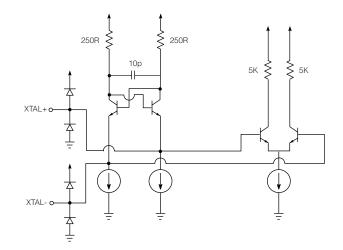

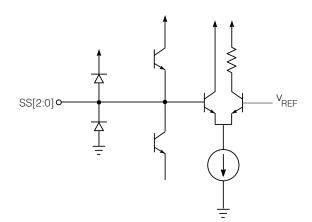

## 2.4 Input/Output Circuits

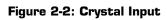

Figure 2-1: TTL Inputs

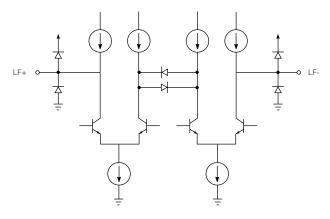

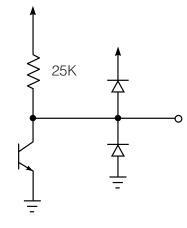

Figure 2-3: Serial Data Outputs

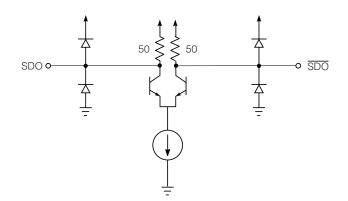

Figure 2-4: Loop Filter

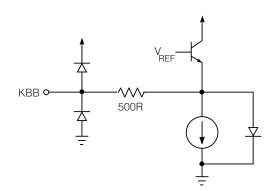

Figure 2-6: KBB

GS1535 Data Sheet

GENNUM

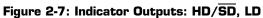

Figure 2-8: Serial Data Inputs

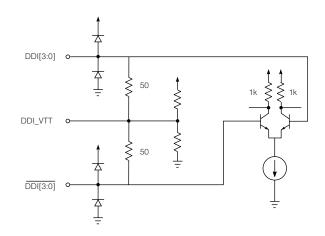

Figure 2-9: Standard Select/Indication Bi-directional pins

## **3. Detailed Description**

The GS1535 is a multi-standard retimer for serial digital SDTV signals at 143, 177, 270, 360 and 540 Mb/s, and HDTV signals at 1.485 Gb/s and 1.485/1.001 Gb/s.

### 3.1 Slew Rate Phase Lock Loop (S-PLL)

The term "slew" refers to the output phase of the PLL in response to a step change at the input. Linear PLLs have an output phase response characterized by an exponential response whereas an S-PLL's output is a ramp response (See Figure 3-1). Because of this non-linear response characteristic, traditional small signal analysis is not possible with an S-PLL.

Figure 3-1: PLL Characteristics

The S-PLL offers several advantages over the linear PLL. The Loop Bandwidth of an S-PLL is independant of the transition density of the input data. Pseudo-random data has a transition density of 0.5 verses a pathological signal which has a transition density of 0.05. The loop bandwidth of a linear PLL will change proportionally with this change in transition density. With an S-PLL, the loop bandwidth is defined by the jitter at the data input. This translates to infinite loop bandwidth with a zero jitter input signal. This allows the loop to correct for small variations in the input jitter quickly, resulting in very low output jitter. The loop bandwidth of the GS1535's PLL is defined at 0.2UI of input jitter.

The GS1535's PLL consists of two acquisition loops. First is the Frequency Acquisiton (FA) loop. This loop is active when the device is not locked and is used to achieve lock to the supported data rates. Second is the phase acquisition (PA) loop. Once locked, the PA loop tracks the incomming data and makes phased corrections to produce a re-clocked output.

### 3.2 VCO

The internal VCO of the GS1535 is a ring oscillator. It is trimmed at the time of manufacture to capture all SD and HD data rates over temperature, and operation voltage ranges.

Integrated into the VCO is a series of programmable dividers, to achieve all serial data rates, as well as additional dividers for the frequency acquisition loop.

### **3.3 Charge Pump**

A common charge pump is used for the GS1535's PLL.

During frequency acquisition, the charge pump has two states, "pump-up" and "pump-down" which is produced by a leading or lagging phase difference between the input and the VCO frequency.

During phase acquisition, there are two levels of "pump-up" and two levels of "pump down" produced for leading and lagging phase difference between the input and VCO frequency. This is to allow for greater precision of VCO control.

The charge pump produces these signals by holding the integrated frequency information on the external loop-filter capacitor,  $C_{LF}$ . The instantaneous frequency information is the result of the current flowing through an internal resistor connected to the loop-filter capacitor.

### 3.4 Frequency Acquisition Loop — The Phase-Frequency Detector

An external crystal of 14.140 MHz is used as a reference to keep the VCO centered at the last known data rate. This allows the GS1535 to achieve a fast synchronous lock, especially in cases where a known data rate is interrupted. The crystal reference is also used to clock internal timers and counters. To keep the optimal performance of the reclocker over all operating conditions, the crystal frequency must be 14.140 MHz, +/-50ppm. The GO1535 meets this specification and is available from GENNUM.

The VCO is divided by a selected ratio which is dependent on the input data rate. The resultant is then compared to the crystal frequency. If the divided VCO frequency and the crystal frequency are within 1% of each other, the PLL is considered to be locked to the input data rate.

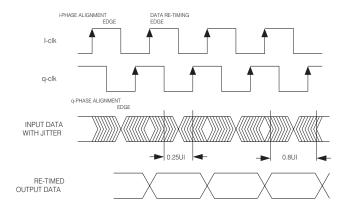

### 3.5 Phase Acquisition Loop — The Phase Detector

The phase detector is a digital quadrature phase detector. It indicates whether the input data is leading or lagging with respect to a clock that is in phase with the VCO (I-clk) and a quadrature clock (Q-clk). When the phase acquisition loop (PA loop) is locked, the input data transition is aligned to the falling edge of I-clk and the output data is re-timed on the rising edge of I-clk. During high input jitter conditions (>0.25UI), Q-clk will sample a different value than I-clk. In this condition, two extra phase correction signals will be generated which instructs the charge pump to create larger frequency corrections for the VCO.

Figure 3-2: Phase Detector Characteristics.

When the PA loop is active, the crystal frequency and the incomming data rate are compared. If the resultant is more that 2%, the PLL is considered to be unlocked and the system jumps to the FA loop.

### 3.6 4:1 Input Mux

The 4:1 input mux allows the connection of four independent streams of video/data. These are differential inputs (DDI[3:0] and DDI[3:0]). The active channel can be selected via the DDI\_SEL[1:0] pins. Table 3-1 shows the input selected for a given state at DDI\_SEL[1:0].

| Table 3 | -1: Bi | t Pattern | for | Input | Select |

|---------|--------|-----------|-----|-------|--------|

|---------|--------|-----------|-----|-------|--------|

| DDI_SEL1:0] | Selected Input |

|-------------|----------------|

| 00          | DDI0           |

| 01          | DDI1           |

| 10          | DDI2           |

| 11          | DDI3           |

The DDI inputs are designed to be DC interfaced with the output of the GS1524 Cable Equalizer. There are on chip  $50\Omega$  termination resistors which come to a common point at the DDI\_VT pins. Connect a 10nF capacitor to this pin and connect the other end of the capacitor to ground. This end-terminates the transmission line at the inputs for optimum performance.

If only one input pair is used, connect the unused positive inputs to +3.3V and leave the unused negative inputs floating. This helps to eliminate crosstalk from potential noise that would couple to the unused input pair.

### **3.7 Automatic And Manual Data Rate Selection**

The GS1535 can be configured to manually lock to a specific data rate or automatically search for and lock to the incoming data rate. The AUTO\_MAN pin selects Automatic data rate detection mode (AUTO mode) when HIGH and manual data rate selection mode (MANUAL mode) when LOW.

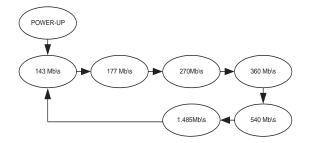

In AUTO mode, the SS[2:0] bi-directional pins become outputs and the bit pattern indicates the data rate that the PLL is locked to (or previously locked to). The "search algorithm" cycles through the data rates (see Figure 3-3) and starts over if that data rate is not found.

Figure 3-3: Data Rate Search Pattern

NOTE: When the device is in AUTO mode, the SD/ $\overline{HD}$  output will toggle when the reclocker is not locked, (LD=LOW). The logic level of SD/ $\overline{HD}$  will depend on the current state of the search algorithm. If the device is also in bypass mode, and the SD/ $\overline{HD}$  signal is used to set the slew rate of the GS1528 Cable Driver, that slew rate will change dynamically when the reclocker is not locked.

In MANUAL mode, the SS[2:0] pins become inputs and the data rate can be programmed. In this mode, the search algorithm is disabled and the GS1535's PLL will only lock to this data rate.

Table 3-2 shows the bit pattern at SS[2:0] for the data rate selected (in MANUAL mode) or the data rate that the PLL has locked to (in AUTO mode).

| <b>SS</b> [2:0] | Data Rate (Mb/s) |

|-----------------|------------------|

| 000             | 143              |

| 001             | 177              |

| 010             | 270              |

| 011             | 360              |

| 100             | 540              |

| 101             | 1485/1483.5      |

Table 3-2: Data Rate Indication/Selection Bit Pattern

### **3.8 Bypass Mode**

In bypass mode, the GS1535 passes the data at the inputs, directly to the outputs. There are two pins that control the bypass function: BYPASS and AUTOBYPASS.

The BYPASS pin is an active high signal which forces the GS1535 into bypass mode for as long as a HIGH is asserted at this pin.

The AUTOBYPASS pin is an active high signal which places the GS1535 into bypass mode only when the PLL has not locked to a data rate. Note that if BYPASS is HIGH, this will overwrite the AUTOBYPASS functionallity.

When the GS1535's PLL is not locked and BYPASS = LOW and AUTOBYPASS = LOW, the serial digital output DDO/DDO will produce invalid data.

### 3.9 DVB/ASI Operation

The GS1535 is designed to re-clock DVB/ASI at 270 Mb/s. There is a harmonic present in idle patterns (K28.5) which is very close the 177 Mb/s data rate (EIC 1179). The ASI/177 pin, when HIGH will disable the 177 Mb/s search in AUTO mode. In this mode, the GS1535 will not lock to 177 Mb/s.

### 3.10 LOCK

The LOCK DETECT signal, LD, is an active high output which indicates when the PLL is locked.

The lock logic with the GS1535 includes a system which monitors the Frequency Acquisition Loop and the Phase Acquisition Loop as well as a monitor to detect harmonic lock.

### 3.11 Output Drivers

The GS1535's serial digital data outputs (DDO/DDO) have a nominal voltage of 800mv single ended or 1600mV differential when terminated into  $50\Omega$ .

The DDO\_VTT pin is the common point of two  $50\Omega$  termination resistors from the DDO and DDO. This pin can be left open if the termination exists on the receiving device.

### 3.12 Output Mute

The DDO\_MUTE pin is provided to allow muting of the retimed output.

When the GS1535's PLL is locked and the device is reclocking, setting  $\overline{DDO}_MUTE = LOW$  will force the serial digital outputs  $\overline{DDO}_\overline{DDO}$  to mute. However, if the GS1535 is in bypass mode, (AUTOBYPASS = HIGH and/or BYPASS = HIGH),  $\overline{DDO}_MUTE$  will have no effect on the output.

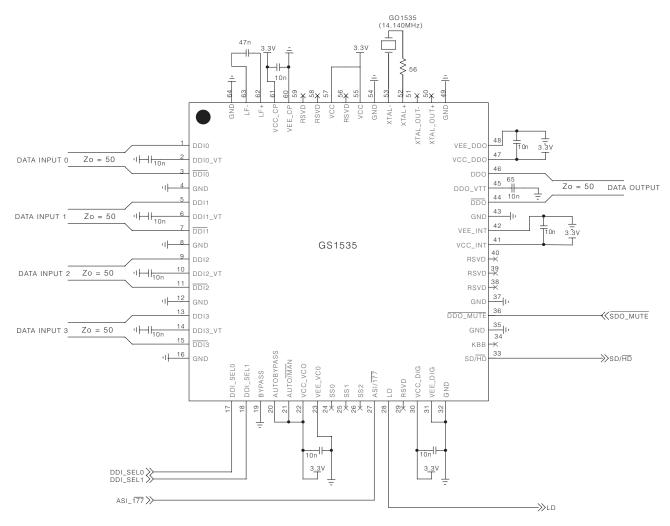

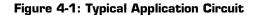

# 4. Application Reference Design

## **4.1 Typical Application Circuit**

Note: All resistors in ohms and all capacitors in Farads.

## **5. References**

Compliant with SMPTE 292M, SMPTE 259M and SMPTE344M.

# 6. Package & Ordering Information

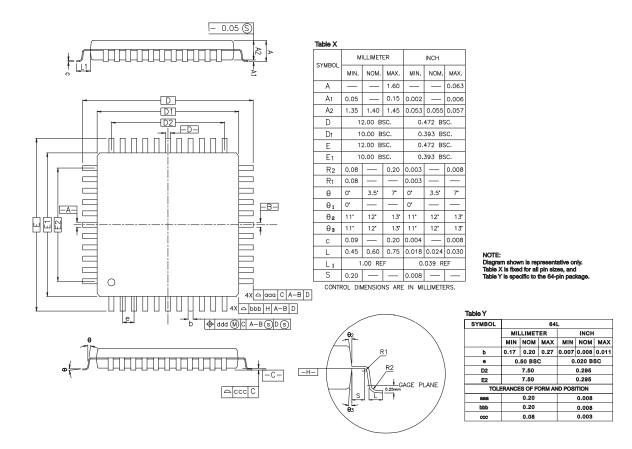

### **6.1 Package Dimensions**

## 6.2 Packaging Data

| Parameter                                                                   | Value                   |

|-----------------------------------------------------------------------------|-------------------------|

| Package Type                                                                | 10mm x 10mm 64-pin LQFP |

| Package Drawing Reference                                                   | JEDEC MS026             |

| Moisture Saturation Level                                                   | 3                       |

| Junction to Case Thermal Resistance, $\theta_{j\text{-c}}$                  | 14.9°C/W                |

| Junction to Air Thermal Resistance, $\theta_{j\text{-}a}$ (at zero airflow) | 45.4°C/W                |

| Psi                                                                         | 0.9°C/W                 |

| Pb-free and Green                                                           | Yes                     |

## **6.3 Ordering Information**

| Part Number  | Package     | Temperature Range | Pb-Free And Green |

|--------------|-------------|-------------------|-------------------|

| GS1535-CFU   | 64 pin LQFP | 0°C to 70°C       | No                |

| GS1535-CFUE3 | 64 pin LQFP | 0°C to 70°C       | Yes               |

# 7. Revision History

| Version | ECR    | Date          | Changes and / or Modifications                                                                                                                                              |

|---------|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | 134667 | November 2004 | Corrected TAC pinout for pins 50, 51. Added<br>packaging data section. Updated pins 62 and 63 on<br>the typical application circuit. Converted to new<br>document template. |

| 8       | 135363 | January 2005  | Corrected block diagram and pin description table to reflect mute functionality of the device.                                                                              |

ELECTROSTATIC SENSITIVE DEVICES DO NOT OPEN PACKAGES OR HANDLE EXCEPT AT A STATIC-FREE WORKSTATION

DOCUMENT IDENTIFICATION

#### DATA SHEET

The product is in production. Gennum reserves the right to make changes to the product at any time without notice to improve reliability, function or design, in order to provide the best product possible.

#### **GENNUM CORPORATION**

Mailing Address: P.O. Box 489, Stn. A, Burlington, Ontario, Canada L7R 3Y3 Shipping Address: 970 Fraser Drive, Burlington, Ontario, Canada L7L 5P5 Tel. +1 (905) 632-2996 Fax. +1 (905) 632-5946

#### **GENNUM JAPAN CORPORATION**

Shinjuku Green Tower Building 27F, 6-14-1, Nishi Shinjuku, Shinjuku-ku, Tokyo, 160-0023 Japan Tel. +81 (03) 3349-5501, Fax. +81 (03) 3349-5505

#### **GENNUM UK LIMITED**

25 Long Garden Walk, Farnham, Surrey, England GU9 7HX Tel. +44 (0)1252 747 000 Fax +44 (0)1252 726 523

Gennum Corporation assumes no liability for any errors or omissions in this document, or for the use of the circuits or devices described herein. The sale of the circuit or device described herein does not imply any patent license, and Gennum makes no representation that the circuit or device is free from patent infringement.

GENNUM and the G logo are registered trademarks of Gennum Corporation.

© Copyright 2002 Gennum Corporation. All rights reserved. Printed in Canada.

www.gennum.com