Ph. 480-503-4295 | NOPP@FocusLCD.com

# TFT | CHARACTER | UWVD | FSC | SEGMENT | CUSTOM | REPLACEMENT

# Graphic Display Module

Part Number

G128ALGSGSW6WTC3XAM

#### Overview

128x128(71.3x75.41), STN, Gray background, White Edge lit, Bottom view, Wide temp, Transflective (positive), 3.0V LCD, 3.3V LED, Controller=ST7528, RoHS Compliant

# 1.Features

- 1. 128X128 dots

2. Built-in controller (ST7528)

- +3.0V power supply

1/128 duty cycle;1/12bias

BKL to be driven by A, K.

| LCD type          | □FSTN positiv | е       |        | □FSTN Negative   |               |

|-------------------|---------------|---------|--------|------------------|---------------|

|                   | □STN Yellow ( | Green   | ⊠STN   | Gray             | □STN-Blue     |

| View direction    | ☑6 O'clock    |         | □12 C  | o'clock          |               |

| Rear Polarizer    | □Reflective   |         | ⊠Tran  | sflective        | □Transmissive |

| Backlight Type    | □LED Array    | ᆸ       |        | □Internal Power  | □4.2V input   |

|                   | ☑LED Edge     |         | _      |                  | ☑3.0 input    |

| Backlight Color   | ☑White        | □Ambe   | er     | □Blue-Green      | □Yellow-Green |

| Temperature Range | □Normal       |         | □Wide  | 9                | ☑Super Wide   |

| DC to DC circuit  | ☑Build-in     |         |        | □Not Build-in    |               |

| El Driver IC      | □Build-in     |         |        | ☑Not Build-in    |               |

| Touch screen      | □With         |         |        | □Without         |               |

| Font type         | □English-Jap  | □Englis | sh-Eur | □English-Russian | ☑other        |

|                   | anese         | open    |        |                  |               |

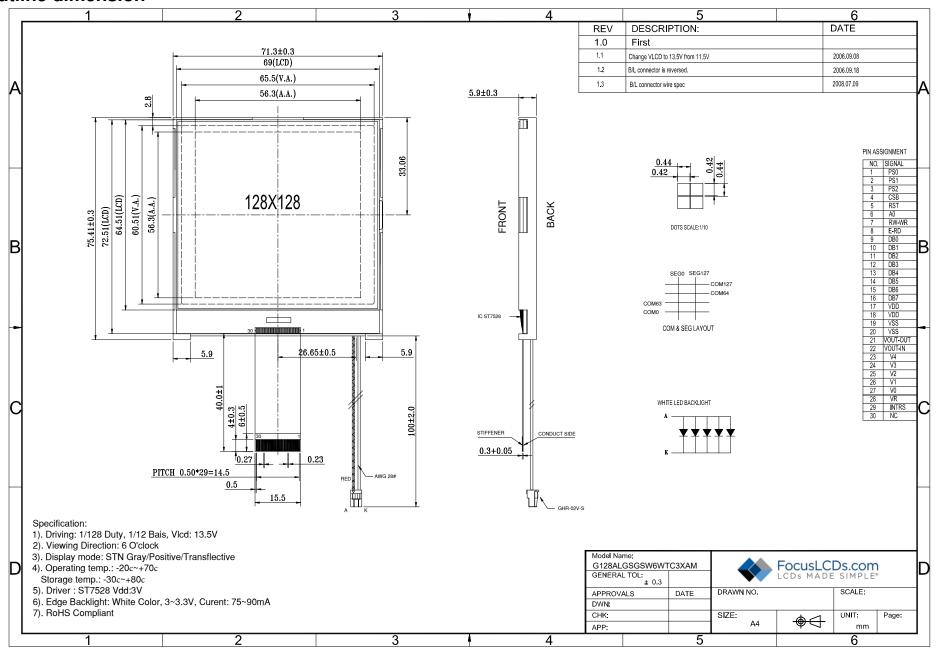

# 2. MECHANICAL SPECIFICATIONS

| Module size  | 71.3 mm(L) * 75.41mm(W) * 5.9(H)mm |

|--------------|------------------------------------|

| Viewing area | 65.5 mm(L) * 60.51 mm(W)           |

| Dots size    | 0.42 mm(L) * 0.42 mm(W)            |

| Dots pitch   | 0.44 mm(L) * 0.44 mm(W)            |

| Weight       | Approx.                            |

### 3. Outline dimension

3

www.FocusLCDs.com

4. Absolute maximum ratings

| Item                        | Symbol                           |     | Standard |     | Unit |

|-----------------------------|----------------------------------|-----|----------|-----|------|

| Power voltage               | V <sub>DD</sub> -V <sub>SS</sub> | 0.3 | -        | 3.6 | V    |

| Input voltage               | V <sub>IN</sub>                  | VSS | -        | VDD | V    |

| Operating temperature range | T <sub>OP</sub>                  | -20 | -        | +70 | °C   |

| Storage temperature range   | T <sub>ST</sub>                  | -30 | -        | +80 | C    |

**5.Interface pin description**Recommended Connector: FH19C-30S-0.5SH(99)

|       |            | Fishering -  |                                                                                                                                                                                                                                                                     |

|-------|------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin   | Symbol     | External     | Function                                                                                                                                                                                                                                                            |

| no.   | - <b>,</b> | connection   |                                                                                                                                                                                                                                                                     |

| 1~3   | PS0~PS2    | 1            | Microprocessor interface select input pin - PS[2:0]=001: 8080-series parallel MPU interface - PS[2:0]=011: 68000-series parallel MPU interface - PS[2:0]=000: 3-Line-SPI MPU interface - PS[2:0]=010: 4-Line-SPI MPU interface - PS[2:0]=100: IIC-SPI MPU interface |

| 4     | CSB        | 1            | Chip select input pins                                                                                                                                                                                                                                              |

| 5     | RST        | 1            | Reset input pin                                                                                                                                                                                                                                                     |

| 6     | A0         | I            | Register select input pin                                                                                                                                                                                                                                           |

| 7     | RW-WR      | I            | Read / Write execution control pin                                                                                                                                                                                                                                  |

| 8     | E-RD       | l            | Read / Write execution control pin                                                                                                                                                                                                                                  |

| 9~16  | DB0~DB7    | I/O          | 8-bit bi-directional data bus that is connected to the standard 8-bit microprocessor data bus.                                                                                                                                                                      |

| 17    | VDD        | Power supply | Power supply for LCM (+3.0V)                                                                                                                                                                                                                                        |

| 18    | VDD        | Power supply | Power supply for LCM (+3.0V)                                                                                                                                                                                                                                        |

| 19    | VSS        | Power supply |                                                                                                                                                                                                                                                                     |

| 20    | VSS        | Power supply |                                                                                                                                                                                                                                                                     |

| 21    | VOUT-OUT   | supply       | If the internal Vout voltage generator is used, the VOUT_IN & VOUT_OUT must be connected together. If an external supply is used, this pin must be left open.                                                                                                       |

| 22    | VOUT-IN    | supply       | An external Vout supply voltage can be supplied using the VOUT_IN pad. In this case, VOUT_OUT has to be left open, and the internal voltage generator has to be programmed to zero.                                                                                 |

| 23~27 | V4~V0      | I/O          | LCD driver supply voltages                                                                                                                                                                                                                                          |

| 28    | VR         | 1            | V0 voltage adjustment pin                                                                                                                                                                                                                                           |

| 29    | INTRS      | I            | Internal resistor select pin                                                                                                                                                                                                                                        |

| 30    | NC         |              |                                                                                                                                                                                                                                                                     |

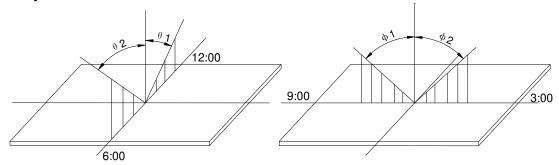

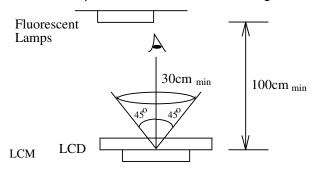

# 6.Optical characteristics

STN type display module (Ta=25°C, VDD=3.0V)

| Item           |           | Symbol         | Condition | Min. | Тур. | Max. | Unit |

|----------------|-----------|----------------|-----------|------|------|------|------|

| Viewing angle  | LeftRight | θ              | Ta=25℃    | -    | 60   | -    | dog  |

| (6 0'clock)    | TopBottom | θ              | 1a=25 C   | -    | 70   | -    | deg  |

| Contrast ratio |           | CR             |           | 3    | 5    | -    | -    |

| Doopongo timo  | Rise      | t <sub>r</sub> | Ta=25°C   | -    | 150  | 250  | mo   |

| Response time  | Tall      | <b>t</b> f     |           | -    | 200  | 300  | ms   |

# 7. Electrical characteristics

# DC characteristics

| Parameter                | Symbol           | Conditions                    | Min. | Тур. | Max.            | Unit |

|--------------------------|------------------|-------------------------------|------|------|-----------------|------|

| Supply voltage for LCD   | $V_{DD}$ - $V_0$ | Ta =25°C                      | -    | 3.0  | -               | V    |

| Input voltage            | $V_{DD}$         |                               | -    | 3.0  | -               |      |

| Supply current           | I <sub>DD</sub>  | Ta=25℃, V <sub>DD</sub> =3.0V | -    | 0.25 | 0.45            | mA   |

| Input leakage current    | ILKG             |                               | -    | -    | 1.0             | uA   |

| "H" level input voltage  | VIH              |                               | 2.2  | -    | V <sub>DD</sub> |      |

| "L" level input voltage  | VIL              | Twice initial value or less   | 0    | -    | 0.6             | V    |

| "H" level output voltage | Vон              | LOH=-0.25mA                   | 2.4  | -    | -               | V    |

| "L" level output voltage | Vol              | LOH=1.6mA                     | -    | -    | 0.4             |      |

# Backlight information

| Parameter          | Symbol | Conditions             | Min. | Тур. | Max. | Unit  |

|--------------------|--------|------------------------|------|------|------|-------|

| Supply Current     | ILED   | Ta =25℃, V=3.0V        | 75   | -    | 90   | mA    |

| Supply voltage     | Vf     |                        | 3.0  | -    | 3.3  | V     |

| Reverse voltage    | VR     | Ta=25℃,                | -    | 5.0  | -    | V     |

| Luminous Intensity | IV     | I <sub>LED</sub> =80mA | -    | -    | -    | Cd/m2 |

| Peak wavelength    | VIH    |                        | -    | -    | -    | nm    |

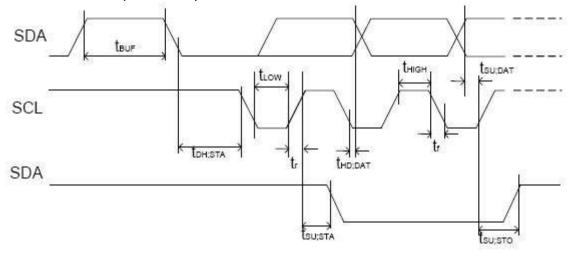

#### 8. TIMING CHARACTERISTICS

SERIAL INTERFACE(IIC Interface)

(VDD=3.3V,Ta=-30~85°C)

| 14                                               | C:     | Complex  | Candition | Ra       | ting            | Herita |

|--------------------------------------------------|--------|----------|-----------|----------|-----------------|--------|

| Item                                             | Signal | Symbol   | Condition | Min.     | Max.            | Units  |

| SCL clock frequency                              | SCL    | FSCLK    |           | j=1      | 400             | kHZ    |

| SCL clock low period                             | SCL    | TLOW     |           | 1.3      | -               | us     |

| SCL clock high period                            | SCL    | THIGH    |           | 0.6      | <del>-</del> -1 | us     |

| Data set-up time                                 | SI     | TSU;Data |           | 100      | #1              | ns     |

| Data hold time                                   | SI     | THD;Data |           | 0        | 0.9             | us     |

| SCL,SDA rise time                                | SCL    | TR       |           | 20+0.1Cb | 300             | ns     |

| SCL,SDA fall time                                | SCL    | TF       |           | 20+0.1Cb | 300             | ns     |

| Capacitive load represented by each bus line     |        | Cb       |           | 324      | 400             | pF     |

| Setup time for a repeated START condition        | SI     | TSU;SUA  |           | 0.6      | -               | us     |

| Start condition hold time                        | SI     | THD;STA  |           | 0.6      | -<br>-          | us     |

| Setup time for STOP ondition                     |        | TSU;STO  |           | 0.6      | -               | us     |

| Tolerable spike width on bus                     |        | TSW      |           | -        | 50              | ns     |

| BUS free time between a STOP and StART condition | SCL    | TBUF     |           | 1.3      |                 | us     |

#### 9. DESCRIPTION OF FUNCTIONS

#### > IIC Interface

The IIC interface receives and executes the commands sent via the IIC Interface. It also receives RAM data and sends it to the RAM.

The IIC Interface is for bi-directional, two-line communication between different ICs or modules. The two lines are a Serial Data line (SDA) and a Serial Clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor. Data transfer may be initiated only when the bus is not busy.

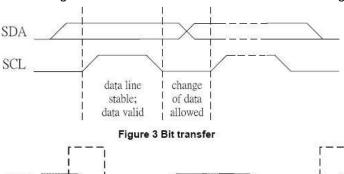

#### **BIT TRANSFER**

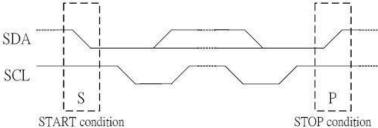

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse because changes in the data line at this time will be interpreted as a control signal. Bit transfer is illustrated in Figure 3.

#### START AND STOP CONDITIONS

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P). The START and STOP conditions are illustrated in

#### Figure 4.

#### SYSTEM CONFIGURATION

The system configuration is illustrated in Figure 5.

- · Transmitter: the device, which sends the data to the bus.

- · Receiver: the device, which receives the data from the bus.

- · Master: the device, which initiates a transfer, generates clock signals and terminates a transfer.

- · Slave: the device addressed by a master.

- · Multi-Master: more than one master can attempt to control the bus at the same time without corrupting the message.

- · Arbitration: procedure to ensure that, if more than one master simultaneously tries to control the bus, only one is allowed to do so and the message is not corrupted.

- · Synchronization: procedure to synchronize the clock signals of two or more devices.

#### **ACKNOWLEDGE**

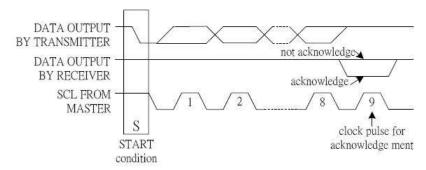

Each byte of eight bits is followed by an acknowledge bit. The acknowledge bit is a HIGH signal put on the bus by the transmitter during which time the master generates an extra acknowledge related clock pulse. A slave receiver which is addressed must generate an acknowledge after the reception of each byte. A master receiver must also generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges must pull-down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse (set-up and hold times must be taken into consideration). A master receiver must signal an end-of-data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.

Acknowledgement on the IIC Interface is illustrated in Figure 5.

Figure 4 Definition of START and STOP conditions

Figure 5 Acknowledgement on the 2-line Interface

#### **IIC Interface protocol**

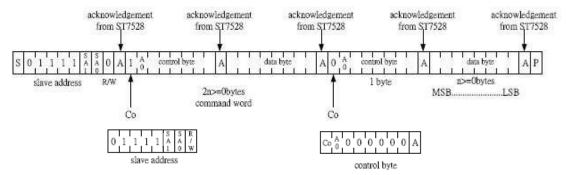

The ST7528 supports command, data write addressed slaves on the bus. Before any data is transmitted on the IIC Interface, the device, which should respond, is addressed first. Four 7-bit slave addresses (0111100, 0111101, 0111110 and 0111111) are reserved for the ST7528. The least significant bit of the slave address is set by connecting the input SA0 and SA1 to either logic 0 (VSS) or logic 1 (VDD). The IIC Interface protocol is illustrated in Figure 6.

#### Note: ST7528 IIC interface can not use with other slaver IIC device

The sequence is initiated with a START condition (S) from the IIC Interface master, which is followed by the slave address. All slaves with the corresponding address acknowledge in parallel, all the others will ignore the IIC Interface transfer. After acknowledgement, one or more command words follow which define the status of the addressed slaves. A command word consists of a control byte, which defines Co and A0, plus a data byte. The last control byte is tagged with a cleared most significant bit (i.e. the continuation bit Co). After a control byte with a cleared Co bit, only data bytes will follow. The state of the A0 bit defines whether the data byte is interpreted as a command or as RAM data. All addressed slaves on the bus also acknowledge the control and data bytes. After the last control byte, depending on the A0 bit setting; either a series of display data bytes or command data bytes may follow. If the A0 bit is set to logic 1, these display bytes are stored in the display RAM at the address specified by the data pointer. The data pointer is automatically updated and the data is directed to the intended ST7528 device. If the A0 bit of the last control byte is set to logic 0, these command bytes will be decoded and the setting of the device will be changed according to the received commands. Only the addressed slave makes the acknowledgement after each byte. At the end of the transmission the IIC INTERFACE-bus master issues a STOP condition (P). If the R/W bit is set to logic 1 the chip will output data immediately after the slave address if the A0 bit, which was sent during the last write access, is set to logic 0. If no acknowledge is generated by the master after a byte, the driver stops transferring data to the master. Write mode:

Figure 6 2-line Interface protocol

| Co | 0 | Last control byte to be sent. Only a stream of data bytes is allowed to follow. This stream may only be terminated by s STOP or RE-START condition. |  |

|----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 00 | 1 | Another control byte will follow the data byte unless a STOP or RE-START condition is received.                                                     |  |

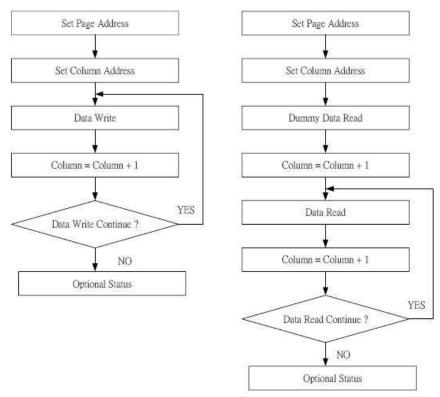

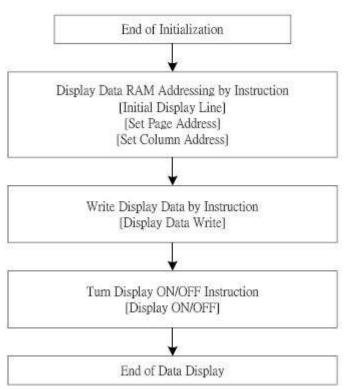

#### **DISPLAY DATA RAM (DDRAM)**

When Mode 0 is selected

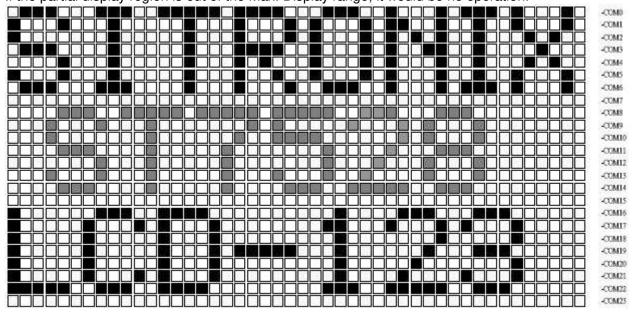

The Display Data RAM stores pixel data for the LCD. It is 129-row (17 pages by 8 bits) by 132-column addressable array.

Each pixel can be selected when the page and column addresses are specified. The 129 rows are divided into 16 pages of 8 lines and the 17th page with a single line (DB0 only). Data is read from or written to the 8 lines of each page directly through DB0 to DB7. The display data of DB0 to DB7 from the microprocessor correspond to the LCD common lines. The microprocessor can read from and write to RAM through the I/O buffer. Since the LCD controller operates independently, data can be written into RAM at the same time as data is being displayed without causing the LCD flicker.

When Mode 1 is selected

The Display Data RAM stores pixel data for the LCD. It is 101-row (13 pages by 8 bits) by 160-column addressable array.

Each pixel can be selected when the page and column addresses are specified. The 101 rows are divided into 12 pages of 8 lines and the 13th page with 4 lines; the Page Address 16 (17th page) is for Icon page with a single line (DB0 only). Data is read from or written to the 8 lines of each page directly through DB0 to DB7. The display data of DB0 to DB7 from the microprocessor correspond to the LCD common lines. The microprocessor can read from and write to RAM through the I/O buffer. Since the LCD controller operates independently, data can be written into RAM at the same time as data is being displayed without causing the LCD flicker.

#### **Page Address Circuit**

In mode 0

It incorporates 4-bit Page Address register changed by only the "Set Page" instruction. Page Address 16 is a

special RAM area for the icons and display data DB0 is only valid. The page address is set from 0 to 15, and Page 16 is for Icon page.

In mode 1

It incorporates 4-bit Page Address register changed by only the "Set Page" instruction. Page Address 16 is a special RAM area for the icons and display data DB0 is only valid. The page address is set from 0 to 12, and Page 16 is for Icon page.

#### **Line Address Circuit**

In mode 0

This circuit assigns DDRAM a Line Address corresponding to the first line (COM0) of the display. Therefore, by setting Line Address repeatedly, it is possible to realize the screen scrolling and page switching without changing the contents of on-chip RAM. It incorporates 7-bit Line Address register changed by only the initial display line instruction and 7-bit counter circuit. At the beginning of each LCD frame, the contents of register are copied to the line counter which is increased by CL signal and generates the line address for transferring the 128-bit RAM data to the display data latch circuit. When icon is enabled by setting icon control register, display data of icons are not scrolled because the MPU can not access Line Address of icons.

The 7-bit Line Address register is set from  $0 \sim 99$ , If the register is set from  $100 \sim 127$ , It will be no operation. The register value will be kept in last value.

#### **Column Address Circuit**

In Mode 0, 1

Column Address Circuit has a 10-bit preset counter that provides Column Address to the Display Data RAM. When set Column Address MSB / LSB instruction is issued, 8-bit [Y9:Y2] are set and lowest 2 bit, Y[1:0] is set to "00". Since this address is increased by 1 each a read or write data instruction, microprocessor can access the display data continuously. However, the counter is not increased and locked if a non-existing address above 9FH. It is unlocked if a column address is set again by set Column Address MSB / LSB instruction. And the column address counter is independent of page address register.

ADC select instruction makes it possible to invert the relationship between the Column Address and the segment outputs. It is necessary to rewrite the display data on built-in RAM after issuing ADC select instruction. Refer to the following Figure 9 and Figure 10.

(Note: in mode read or write in fourth. the column address will turn to next column address)

| MODE 0                                   |    | 823 |         | -  |    | 1281 | 27.22   | -     |    | 0.000 | 20.100  |    |    | 11223 | 29.23   | -   |     | ř    | 8220       | 2002 |       |     | -   | 1000     |     | 7   | 1124    | _125×    |      |     | 2025     | -27.23   |    |

|------------------------------------------|----|-----|---------|----|----|------|---------|-------|----|-------|---------|----|----|-------|---------|-----|-----|------|------------|------|-------|-----|-----|----------|-----|-----|---------|----------|------|-----|----------|----------|----|

| SEG<br>output                            |    |     | EG<br>0 |    |    |      | EG<br>1 |       |    |       | EG<br>2 |    |    |       | EG<br>3 |     | 826 | 44.  | SEG<br>128 |      |       | 44  |     | EG<br>29 |     |     |         | EG<br>30 |      |     |          | EG<br>31 |    |

| Column<br>address<br>[Y9:Y2]             |    | 00  | ЭH      |    |    | 0    | 1H      |       |    | 02    | 2Η      |    |    | 0;    | 3H      |     | *** | 80H  |            |      |       | 8   | ΙH  | 40       |     | 82  | 2H      |          |      | 83H |          |          |    |

| Internal<br>column<br>address<br>[Y9:Y0] | 00 | 01  | 02      | 03 | 04 | 05   | 08      | 07    | 08 | 09    | 0A      | 08 | oc | 00    | 0E      | OF  | *** | 200  | 201        | 202  | 203   | 204 | 205 | 208      | 207 | 208 | 209     | 20A      | 20B  | 20C | 20D      | 20E      | 20 |

| Display<br>data<br>(ADC=0)               | 1  | 1   | 1       | 1  | 1  | 1    | 4       | 0     | 1  | 1     | 0       | 1  | 1  | 1     | D       | 0   | *** | 0    | 0          | 1    | 1     | 0   | 0   | 1        | 0   | 0   | 0       | 0        | 1    | 0   | 0        | 0        | 0  |

| _CD panel<br>display                     |    |     | 4       |    |    |      |         |       |    |       | 10.00   |    |    | e e   |         |     | *** | 1.63 |            |      |       |     | _   |          |     |     | _       | _        |      |     | <b>→</b> |          |    |

| 77                                       | _  | ·   | .4      | _  |    |      | _       | _     | _  |       |         | _  | _  |       |         | _   |     |      |            | _    |       |     |     |          |     | _   |         | _        | _    |     | _        |          |    |

| Display<br>data<br>(ADC=1)               | 0  | 0   | 0       | 0  | 0  | 0    | 0       | 1     | 0  | 0     | 1       | 0  | 0  | 0     | 1       | 1   | *** | 1    | 1          | 0    | 0     | 1   | 1   | 0        | 1   | 1   | 1       | 1        | 0    | 1   | 1        | 1        | S  |

| LCD panel<br>display                     |    |     | 8       |    |    |      |         | *** 1 |    |       |         |    |    | 0/2   |         | *** | 222 |      | Na T       | 0.2  | Ore T |     |     |          | **  |     | \$100 m | 39       | ås . |     |          |          |    |

Figure 9. The Relationship between the Column Address and the Segment Outputs

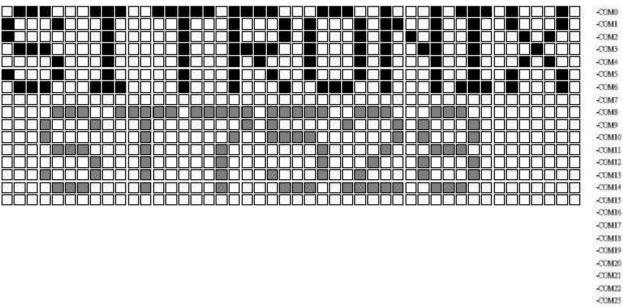

### Mode-0 Display RAM Mapping diagram

| Page Address<br>D3 D2 D1 D | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Line<br>Address COM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 0 0                    | D4 D5 D6 D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00H         COM0           01H         COM1           02H         COM2           03H         COM3           04H         COM4           05H         COM5           06H         COM6           07H         COM7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0 0 0 1                    | D0 D1 D2 D3 Page 1 D5 D6 D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 08H         COM8           09H         COM9           0AH         COM10           0BH         COM11           0CH         COM12           0DH         COM13           0EH         COM14           0FH         COM15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0 0 1 0                    | D0 D1 D2 D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10H   COM16   COM16   COM17   COM17   COM18   COM19   COM19   COM19   COM20   COM20 |

|                            | D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68H COM10 69H COM10 6AH COM10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1 1 0 4                    | D3 D12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6BH COM10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1 1 0 1                    | D4<br>D5<br>D6<br>D7<br>D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6CH COM10 6DH COM10 6EH COM11 6FH COM11 70H COM11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1 1 1 0                    | D4 D5 D6 D7 D0 D1 D2 D3 D4 D5 D6 D7 Page 14 D5 D6 D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6CH COM10 6DH COM10 6EH COM11 70H COM11 71H COM11 72H COM11 73H COM11 73H COM11 75H COM11 75H COM11 75H COM11 76H COM11 77H COM11 77H COM11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 32 245 20 2                | D4 D5 D6 D7 D0 D1 D2 D3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6CH COM10 6DH COM10 6EH COM11 70H COM11 70H COM11 72H COM11 73H COM11 73H COM11 75H COM11 75H COM11 76H COM11 77H COM11 77H COM11 77H COM11 77H COM12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1 1 1 0                    | D4 D5 D6 D7 D0 D1 D2 D3 D4 D5 D6 D7 D0 D1 D2 D3 D4 D5 D6 D7 D0 D1 D2 D3 D4 D7 D0 D1 D2 D3 D4 D5 D6 D7 D6 D7 D8 D8 D8 D8 D9 D9 D9 D1 D9 D9 D1 D9 D8 | 6CH COM10 6DH COM10 6EH COM11 70H COM11 70H COM11 72H COM11 73H COM11 73H COM11 75H COM11 75H COM11 76H COM11 77H COM11 77H COM11 77H COM11 77H COM12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### MODE 1

| SEG<br>output                            |    |    | EG<br>0 |    | 0  |    | EG<br>1 |    |    | SE<br>2 |      |    |      | SEG<br>3 |    |     | 115 |    | SEG<br>156 |      |      | SEG<br>157 |      |      |      |                |     | EG<br>58 |       | SEG<br>159 |     |          |     |     |  |

|------------------------------------------|----|----|---------|----|----|----|---------|----|----|---------|------|----|------|----------|----|-----|-----|----|------------|------|------|------------|------|------|------|----------------|-----|----------|-------|------------|-----|----------|-----|-----|--|

| Column<br>address<br>[Y9:Y2]             |    | 0  | ЭН      |    |    | 0  | 1H      |    |    | 02H 03H |      |    |      |          |    |     | *** |    | ę          | CH   |      |            | 1    | 9DH  |      |                |     | 91       | ΞH    |            | 9FH |          |     |     |  |

| Internal<br>column<br>address<br>[Y9:Y0] | 00 | 01 | 02      | 03 | 04 | 05 | 06      | 07 | 08 | 09      | OA   | ОВ | oc   | 0D       | 0E | OF  | 666 | 27 | 0 27       | 1 27 | 2 27 | 3 27       | 4 27 | 5 27 | 6 27 | 77             | 278 | 279      | 27A   | 278        | 27C | 27D      | 27E | 27F |  |

| Display<br>data<br>(ADC=0)               | 1  | 1  | 1       | 1  | 1  | 1  | 1       | 0  | 1  | 1       | 0    | 1  | 1    | 1        | 0  | 0   | MA  | 0  |            | 1    |      | 0          | c    | 4    |      | )              | 0   | 0        | 0     | 1          | 0   | 0        | 0   | 0   |  |

| LCD panel<br>display                     |    |    | *       |    |    |    |         |    |    |         | -0.0 |    |      |          |    |     | *** |    |            |      |      |            |      |      |      |                |     |          | - E-2 |            |     | <b>→</b> |     |     |  |

|                                          |    |    | 4       | _  | _  | _  | _       | _  | _  |         |      | _  | _    | _        | -  | _   |     | _  | _          | <    |      | _          |      |      | _    | _              |     |          |       |            | _   | _        |     |     |  |

| Display<br>data<br>(ADC=1)               | 0  | 0  | 0       | 0  | 0  | 0  | 0       | 1  | 0  | 0       | 1    | 0  | 0    | 0        | 1  | 1   | *** | 1  | 1          | 0    | c    | 1          | н    | 0    |      | 3 <u>111</u> 3 | 1   | 1        | •     | D          | 1   | 4        | 1   | 1   |  |

| LCD panel<br>display                     |    | 57 | dt - 3  | Ř  |    |    | Ži.     |    |    | ***     |      |    | 22 3 |          | 0  | W() | *** |    | 38         |      | 88   | 06         | 581  | *    | 180  |                | 5   |          |       | i i        |     |          |     |     |  |

Figure 10. The Relationship between the Column Address and the Segment Outputs

# **Mode-1 Display RAM Mapping diagram**

| 0 0 0 | 0   | 0 D0 D1 D2 D3 D4 D5 D6 D7 D7 D7 D8 |   |             | Page 0 Page 1 |  |    | 00H<br>01H<br>02H<br>03H<br>04H<br>05H<br>06H<br>07H<br>08H<br>09H<br>0AH<br>0CH<br>0DH<br>0EH<br>11H<br>12H<br>13H<br>14H<br>15H<br>16H | 00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00      |

|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------|---------------|--|----|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 0 0 1 |     | D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7<br>D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7                                                                                                   |   |             |               |  |    | 08H<br>09H<br>0AH<br>0BH<br>0CH<br>0DH<br>0EH<br>0FH<br>10H<br>11H<br>12H<br>13H<br>14H<br>15H                                           | CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>C |

|       | 1 ( | 0 D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7                                                                                                                                                       |   |             | Page 2        |  |    | 11H<br>12H<br>13H<br>14H<br>15H<br>16H                                                                                                   | C0<br>C0<br>C0<br>C0<br>C0<br>C0                                                |

| 1 0 1 |     | 1                                                                                                                                                                                              | į | 1<br>1<br>1 |               |  | v. |                                                                                                                                          |                                                                                 |

|       | 1 ( | 0 D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7                                                                                                                                                       |   |             | Page 10       |  |    | 50H<br>51H<br>52H<br>53H<br>54H<br>55H<br>56H<br>57H                                                                                     | C0<br>C0<br>C0<br>C0<br>C0<br>C0<br>C0<br>C0<br>C0                              |

|       | 1 ( | 0 D2<br>D3<br>D4<br>D5<br>D6<br>D7<br>D0<br>D1                                                                                                                                                 |   |             | Page 10       |  |    | 52H<br>53H<br>54H<br>55H<br>56H<br>57H<br>58H<br>59H                                                                                     | CC<br>CC<br>CC<br>CC<br>CC<br>CC<br>CC                                          |

| 1 0 1 | 1   | 1 D2<br>D3<br>D4<br>D5<br>D6<br>D7<br>D0<br>D1                                                                                                                                                 |   |             | Page 11       |  |    | 5AH<br>5BH<br>5CH<br>5DH<br>5EH<br>5FH<br>60H<br>61H                                                                                     | CC<br>CC<br>CC<br>CC                                                            |

| 1 1 0 | 0 ( | 0 D3<br>D4<br>D5<br>D6<br>D7                                                                                                                                                                   |   |             | Page 12       |  |    | 62H<br>63H                                                                                                                               | CC                                                                              |

### **LCD DISPLAY CIRCUITS**

FRC (Frame Rate Control) and PWM (Pulse Width Modulation) Function Circuit

The ST7528 incorporates an FRC function and a PWM function circuit to display a 16-level gray scale. The

FRC function and PWM utilize liquid crystal characteristics whose transmittance is changed by an effective

value of applied voltage. The ST7528 provides palette-registers to assign the desired gray level. These registers are set by the instructions and the RESETB.

# - Gray Scale Table of 4 FRC (Frame Rate Control)

| 4 FRC setting | (DB7 to DB0)                                     |

|---------------|--------------------------------------------------|

| 1st FR (FR1)  | Set 1st Frame Pulse Width Modulation Instruction |

| 1st FR (FR1)  | Set 1st Frame Pulse Width Modulation Data        |

| 2nd FR (FR2)  | Set 2nd Frame Pulse Width Modulation Instruction |

| 2nd FR (FR2)  | Set 2nd Frame Pulse Width Modulation Data        |

| 3rd FR (FR3)  | Set 3rd Frame Pulse Width Modulation Instruction |

| 3rd FR (FR3)  | Set 3rd Frame Pulse Width Modulation Data        |

| 4th FR (FR4)  | Set 4th Frame Pulse Width Modulation Instruction |

| 4th FR (FR4)  | Set 4th Frame Pulse Width Modulation Data        |

#### **Gray Scale Table of 3 FRC (Frame Rate Control)**

| 3 FRC setting | (DB7 to DB0)                                     |

|---------------|--------------------------------------------------|

| 1st FR (FR1)  | Set 1st Frame Pulse Width Modulation Instruction |

| 1st FR (FR1)  | Set 1st Frame Pulse Width Modulation Data        |

| 2nd FR (FR2)  | Set 2nd Frame Pulse Width Modulation Instruction |

| 2nd FR (FR2)  | Set 2nd Frame Pulse Width Modulation Data        |

| 3rd FR (FR3)  | Set 3rd Frame Pulse Width Modulation Instruction |

| 3rd FR (FR3)  | Set 3rd Frame Pulse Width Modulation Data        |

| 4th FR (FR4)  | No used                                          |

| 4th FR (FR4)  | No used                                          |

### **Gray Scale Table of 45 PWM (Pulse Width Modulation)**

| Dec    | Hex   | 6-bits  | PWM (on width) | Note              |  |

|--------|-------|---------|----------------|-------------------|--|

| 0      | 00    | 000000  | 0(0/45)        | Brighter          |  |

| 1      | 01    | 000001  | 1/45           |                   |  |

| 2      | 02    | 000010  | 2/45           |                   |  |

| 3      | 03    | 000011  | 3/45           |                   |  |

| 4      | 04    | 000100  | 4/45           |                   |  |

| 324.1  | ***   | ***     | 3333           |                   |  |

| 225.2  | 54445 | 59445   | 3446           |                   |  |

| 388.6  | 1000  | -395    | 322            |                   |  |

| 8222   | 12223 | 1529233 | \$12           |                   |  |

| 42     | 2A    | 101010  | 42/45          |                   |  |

| 43     | 2B    | 101011  | 43/45          |                   |  |

| 44     | 2C    | 101100  | 44/45          | *                 |  |

| 45     | 2D    | 101101  | 1(45/45)       | Darker            |  |

| 999 S  |       |         |                | š                 |  |

| 3349 3 |       |         | 32 3293        | This area is      |  |

| 61     | 3D    | 111101  | 0/45           | selected to OFF   |  |

| 62     | 3E    | 111110  | 0/45           | level (0/45 level |  |

| 63     | 3F    | 111111  | 0/45           |                   |  |

|        |       |         | _              |                   |  |

#### -Gray Scale Table of 60 PWM (Pulse Width Modulation)

| Dec  | Hex    | 6-bits | PWM (on width) | Note              |

|------|--------|--------|----------------|-------------------|

| 0    | 00     | 000000 | 0(0/60)        | Brighter          |

| 1    | 01     | 000001 | 1/60           |                   |

| 2    | 02     | 000010 | 2/60           |                   |

| 3    | 03     | 000011 | 3/60           |                   |

| 4 04 |        | 000100 | 4/60           |                   |

| 355  |        | 344    |                |                   |

| 948  | 82.4   | 2244   | 1459           |                   |

| 52.2 | 1521.1 | 1991   | 0.000          | 8                 |

|      | 8911   | 8911   | 1.23           |                   |

| 322  | 5522   | 5200   | 9928           |                   |

| 333  | 15422  | 1999   | 9985           | li li             |

| 56   | 39     | 111001 | 56/60          | i li              |

| 57   | 3A     | 111010 | 57/60          |                   |

| 58   | 3B     | 111011 | 58/60          |                   |

| 59   | 3C     | 111100 | 59/60          | <b>+</b>          |

| 60   | 39     | 111001 | 1 (60/60)      | Darker            |

| 61   | 3D     | 111101 | 0/60           | This area is      |

| 62   | 3E     | 111110 | 0/60           | selected to OFF   |

| 63   | 3F     | 111111 | 0/60           | level (0/60 level |

#### **Partial Display on LCD**

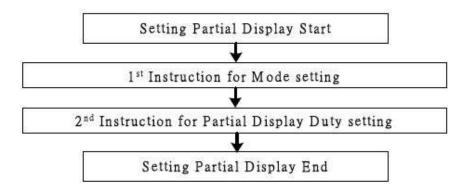

The ST7528 realizes the Partial Display function on LCD with low-ratio driving for saving power consumption and showing the various display ratio. To show the various display ratio on LCD, LCD driving ratio and bias are programmable via the instruction. And, built-in power supply circuits are controlled by the instruction for adjusting the LCD driving voltages.

In mode 0 the partial display ratio could be set from 16 ~ 128.

In mode 1 could be set from 16 ~ 100.

If the partial display region is out of the Max. Display range, it would be no operation.

Figure 13 Reference Example for Partial Display

Figure 14 Partial Display (Partial Display ratio=16,initial COM0=0)

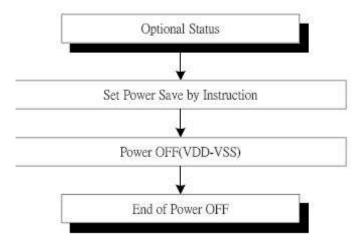

#### **POWER SUPPLY CIRCUITS**

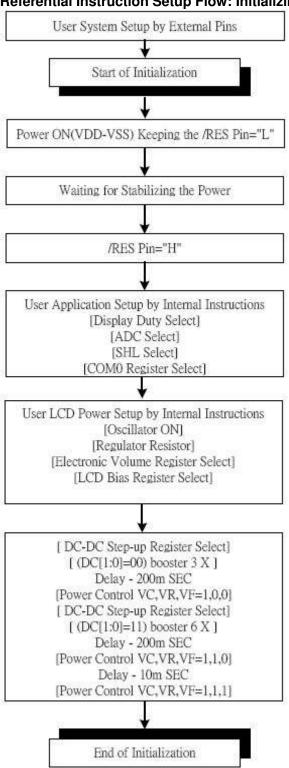

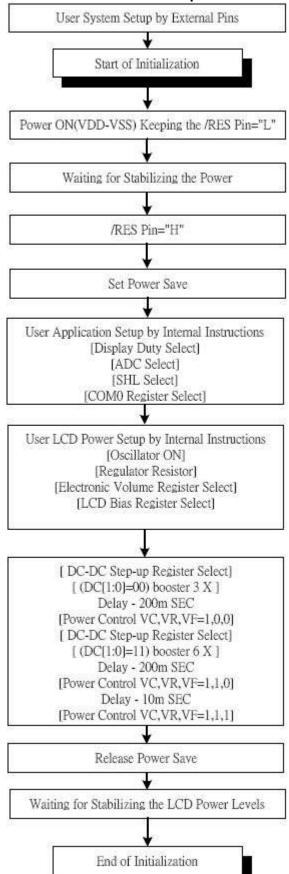

The Power Supply circuits generate the voltage levels necessary to drive liquid crystal driver circuits with low power consumption and the fewest components. There are voltage converter circuits, voltage regulator circuits, and voltage follower circuits. They are controlled by power control instruction. For details, refers to "Instruction Description". Table 4 shows the referenced combinations in using Power Supply circuits.

**Table 4 Recommended Power Supply Combinations**

| User setup                                                                 | Power control<br>(VC VR VF) | V/C<br>circuits | V/R<br>circuits | V/F<br>circuits | VOUT_IN        | V0                | V1 to V4       |

|----------------------------------------------------------------------------|-----------------------------|-----------------|-----------------|-----------------|----------------|-------------------|----------------|

| Only the internal power supply circuits are used                           | 111                         | ON              | ON              | ON              | Internal       | Without capacitor | With capacitor |

| Only the voltage regulator circuits and voltage follower circuits are used | 0 1 1                       | OFF             | ON              | ON              | External input | Without capacitor | With capacitor |

| Only the voltage follower circuits are used                                | 0 0 1                       | OFF             | OFF             | ON              | OPEN           | External input    | With capacitor |

| Only the external power supply circuits are used                           | 0 0 0                       | OFF             | OFF             | OFF             | OPEN           | External input    | External input |

#### **Voltage Converter Circuits**

These circuits boost up the electric potential between VDD2 and Vss to 3, 4, 5 or 6 times toward positive side and boosted voltage is outputted from VOUT pin. It is possible to select the lower boosting level in any boosting circuit by "Set DC-DC Step-up" instruction. When the higher level is selected by instruction, VOUT voltage is not valid.

# Note: we would like to recommend to use the external VOUT when the panel is large than 1.8 inch Voltage Regulator Circuits

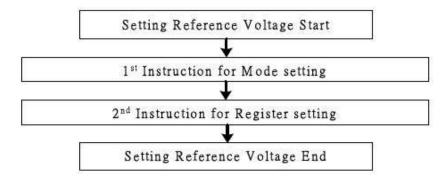

The function of the internal Voltage Regulator circuits is to determine liquid crystal operating voltage, V0, by adjusting resistors, Ra and Rb, within the range of |V0| < |VOUT|. Because VOUT is the operating voltage of operational-amplifier circuits shown in Figure 16, it is necessary to be applied internally or externally. For the Eq. 1, we determine V0 by Ra, Rb and VEV. The Ra and Rb are connected internally or externally by INTRS pin. And VEV called the voltage of electronic volume is determined by Eq. 2, where the parameter a is the value selected by instruction, "Set Reference Voltage Register", within the range 0 to 63. VREF voltage at Ta= 25°C is shown in Table 5.

Rb

$$V0 = (1 + \frac{1}{2}) \times VEV [V] - \cdots (Eq. 1)$$

Ra  $(63 - \alpha)$

$VEV = (1 - \frac{1}{2}) \times VREF [V] - \cdots (Eq. 2)$

#### Table 5 VREF Voltage at Ta = 25° C

| REF | Temp. coefficient | VREF [ V ] |

|-----|-------------------|------------|

| 1   | -0.125% / °C      | 2.1        |

| 0   | External input    | VEXT       |

#### In Case of Using Internal Resistors, Ra and Rb (INTRS = "H")

When INTRS pin is "H", resistor Ra is connected internally between VR pin and VSS, and Rb is connected between V0 and VR. We determine V0 by two instructions, "Regulator Resistor Select" and "Set Reference Voltage".

#### Table 6 Internal Rb / Ra Ratio depending on 3-bit Data (R2 R1 R0)

|               | 3-bit data settings (R2 R1 R0) |       |     |     |     |     |     |     |  |  |  |  |  |

|---------------|--------------------------------|-------|-----|-----|-----|-----|-----|-----|--|--|--|--|--|

|               | 000                            | 0 0 1 | 010 | 011 | 100 | 101 | 110 | 111 |  |  |  |  |  |

| 1 + (Rb / Ra) | 2.3                            | 3.0   | 3.7 | 4.4 | 5.1 | 5.8 | 6.5 | 7.2 |  |  |  |  |  |

#### **RESET CIRCUIT**

Setting RESETB to "L" or Reset instruction can initialize internal function.

When RESETB becomes "L", following procedure is occurred.

Page address: 0 Column address: 0 Read-modify-write: OFF Display ON / OFF: OFF Initial display line: 0 (first) Initial COM0 register: 0 (COM0) Partial display ratio: 1/128

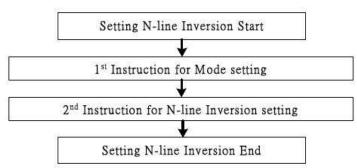

Reverse display ON / OFF: OFF (normal) N-line inversion register: 0 (disable)

Entire Display ON/OFF: OFF

ICON Control register ON/OFF: OFF (ICON disable) Power control register (VC, VR, VF) = (0, 0, 0)

DC-DC converter circuit = (0, 0)Booster Efficiency BE = (1)

Regulator resistor select register: (R2, R1, R0) = (0, 0, 0)

Contrast Level: 32 LCD bias ratio: 1/12 COM Scan Direction: 0

ADC Select: 0 Oscillator: OFF

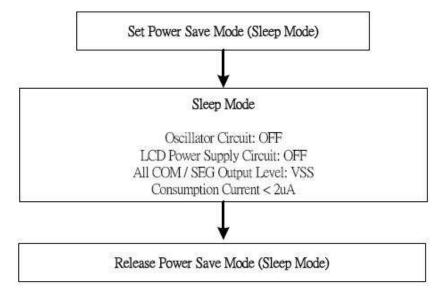

Power Save Mode: Release

Display Data Length register: 0 (for SPI mode)

All Gray Level Set: OFF

In Level0, 2, 4, 6, 8, 10, 12, 14, the Gray Level palette register (GA5, GA4, GA3, GA2, GA1, GA0) = (0,0,0,0,0)

All Gray Level Set: OFF

In Level 1, 3, 5, 7, 9, 11, 13, 15, the Gray Level palette register (GA5, GA4, GA3, GA2, GA1, GA0) = (1,1,1,1,1)

FRC, PWM mode: 4FRC, 45PWM

When RESET instruction is issued, following procedure is occurred.

Page address: 0

Column address: 0 Read-modify-write: OFF Initial display line: 0 (First)

Regulator resistor select register: (R2, R1, R0) = (0, 0, 0)

Contrast Level: 32

Display Data Length register: 0 (for SPI mode)

All Gray Level Set : OFF

In Level 0, 2, 4, 6, 8, 10, 12, 14, the Gray Level palette register (GA5, GA4, GA3, GA2, GA1, GA0) = (0,0,0,0,0)

All Gray Level Set : OFF

In Level 1, 3, 5, 7, 9, 11, 13, 15, the Gray Level palette register (GA5, GA4, GA3, GA2, GA1, GA0) = (1,1,1,1,1)

FRC, PWM mode: 4FRC, 45PWM

While RESETB is "L" or reset instruction is executed, no instruction except read status can be accepted. Reset status appears at DB4. After DB4 becomes "L", any instruction can be accepted. RESETB must be connected to the reset pin of the MPU, and initialize the MPU and this LSI at the same time. The initialization by RESETB is essential before used.

# 10. Table of LCM commands

| Instruction                       | A0 | RW | DB7  | DB6 | DB5 | DB4   | DB3  | DB2 | DB1            | DB0  | Description                                                                                |  |  |

|-----------------------------------|----|----|------|-----|-----|-------|------|-----|----------------|------|--------------------------------------------------------------------------------------------|--|--|

| EXT=0 or 1                        |    |    |      |     |     |       |      |     |                |      | 50                                                                                         |  |  |

|                                   | 0  | 0  | 0    | 0   | 1   | 1     | 1    | 0   | 0              | 0    | 2-byte instruction to set                                                                  |  |  |

| Mode Set                          | 0  | 0  | FR3  | FR2 | FR1 | FR0   | 0    | BE  | x'             | EXT  | Mode and<br>FR( Frame frequency control)<br>BE( Booster efficiency control)                |  |  |

| EXT=0                             |    |    |      |     |     |       |      |     |                |      |                                                                                            |  |  |

| Read display data                 | 1  | 1  |      |     |     | Read  | data |     |                |      | Read data into DDRAM                                                                       |  |  |

| Write display data                | 1  | 0  | G.   |     |     | Write | data |     |                |      | Write data into DDRAM                                                                      |  |  |

| Read status                       | 0  | 1  | BUSY | ON  | RES | MF2   | MF1  | MF0 | DS1            | DS0  | Read the internal status                                                                   |  |  |

| ICON control register ON/OFF      | 0  | 0  | 1    | 0   | 1   | 0     | 0    | 0   | 1              | ICON | ICON=0:<br>ICON disable(default)<br>ICON=1:<br>ICON enable & set the<br>page address to 16 |  |  |

| Set page address                  | 0  | 0  | -1   | 0   | 1   | 1     | Р3   | P2  | P1             | P0   | Set page address                                                                           |  |  |

| Set column address MSB            | 0  | 0  | 0    | 0   | 0   | 1     | Y9   | Y8  | Y7             | Y6   | Set column address MSB                                                                     |  |  |

| Set column address LSB            | 0  | 0  | 0    | 0   | 0   | 0     | Y5   | Y4  | Y3             | Y2   | Set column address LSB                                                                     |  |  |

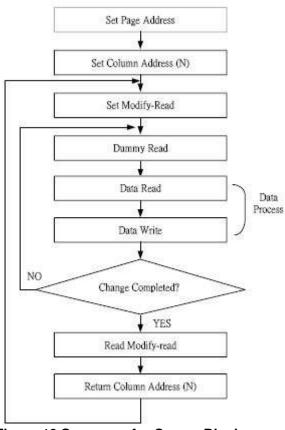

| Set modify-read                   | 0  | 0  | 1    | 1   | 1   | 0     | 0    | 0   | 0              | 0    | Set modify-read mode                                                                       |  |  |

| Reset modify-read                 | 0  | 0  | 1    | 1   | 1   | 0     | 1    | 1   | 1              | 0    | release modify-read mode                                                                   |  |  |

| Display ON/OFF                    | 0  | 0  | 1    | 0   | 1   | 0     | 1    | 1   | 1              | D    | D=0: Display OFF<br>D=1: Display ON                                                        |  |  |

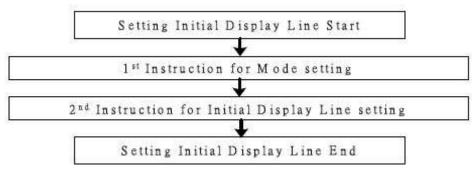

| Set initial display line register | 0  | 0  | 0    | 4   | 0   | 0     | 0    | 0   | X,             | x'   | 2-byte instruction to specify<br>the initial display line to realize                       |  |  |

| Set minar display line register   | 0  | 0  | x'   | S6  | S5  | S4    | S3   | S2  | S1             | S0   | vertical scrolling                                                                         |  |  |

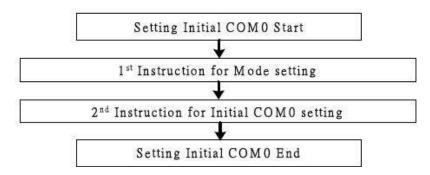

| Set initial COM0 register         | 0  | 0  | 0    | 1   | 0   | 0     | 0    | 1   | X <sup>e</sup> | x'   | 2-byte instruction to specify<br>the initial COM0 to realize                               |  |  |

| Set initial COMb register         | 0  | 0  | x'   | C6  | C5  | C4    | С3   | C2  | C1             | C0   | window scrolling                                                                           |  |  |