# VSC9295, VSC9292

340 Gbps (136 x 136) and 170 Gbps (68 x68) TSI Switches with Dual Rate (2.5G/622M) I/O

## FEATURES:

- ▶ Industry Highest Capacity Single Chip TSI 340 Gbps

- ▶ 25% Less Power Consumption Over Comparable Solutions

- ▶ Scalable to 1.36 Tbps

- ▶ Dual Rate 2.5 G / 622 M Standards Based I/O

### APPLICATIONS:

- ▶ Core/Metro Networks

- ▶ Core/Metro Transport

- ▶ DWDM Switches

- ▶ Central Switch in 170 Gbps to 340 Gbps STS-1 Grooming Fabric

- ▶ Switch Element for 680 Gbps to 1.36 Tbps STS-1 Grooming Fabric

- ▶ Bit-slicing Engine for 680 Gbps to 1.36 Tbps STS-1 Grooming Fabric

- ▶ Ingress/Egress Device for Multi-terabit STS-1 Grooming Clos Fabric

### **BENEFITS:**

- ▶ Allows Highest Capacity Sonet/SDH Systems Increasing Traffic, Lowering Cost of Deployment

- ▶ Saves Power Budget & Lowers Overall System Power Needs

- ▶ Allows Standardization on One Hardware and Software Platform Optimizing Development Resources

- Compatibility with Widely Deployed 622M I/O Based Backplanes, Port Cards and ASICs

#### SPECIFICATIONS:

- ▶ 340 Gbps Aggregate Bandwidth

- ▶ Dual Rate TFI-5 Compliant 2.5 Gbps & 622 Mbps High-speed Interfaces

- ▶ Dual +2.5V/1.2V Power Supply

- ▶ Power Dissipation 19W (typ), 26W (max when VSC9295 is fully utilized) with Power-down for Unused Channels

- ▶ 45.0 mm 1072 fcBGA Package

- ▶ 53 MHz 16-bit CPU Interface

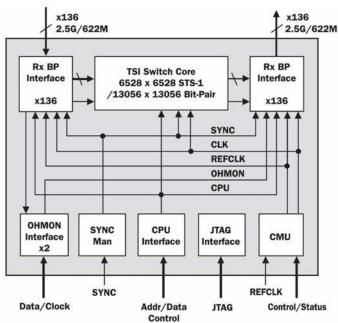

## BLOCK DIAGRAM:

## VSC9295, VSC9292

## 340 Gbps (136 x 136) and 170 Gbps (68 x68) TSI Switches with Dual Rate (2.5G/622M) I/O

## GENERAL DESCRIPTION:

The VSC9295 is a 136 x 136 TSI switch IC supporting TFI-5 (STS-48-like frame) data on every input and output. All data inputs and outputs are differential serial signals running at 2.488 Gbps or 622 Mbps for TDM switching, or 2.488 Gbps,

2.125 Gbps, and 622 Mbps for transparent switching. The device

contains a fully nonblocking STS-1 switch matrix surrounded by serial backplane interfaces that incorporate fully integrated clock recovery and synthesis, input equalization, output pre-emphasis, SONET/SDH compliant scrambling, framing, deskewing, and alarms. Ports to drop and insert overhead bytes are included. A multimode CPU interface is used for device configuration and status monitoring.

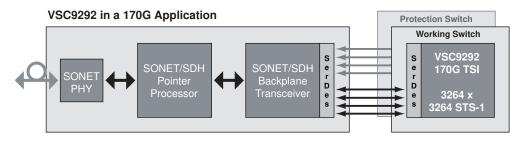

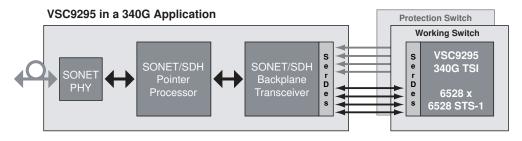

### APPLICATION DIAGRAM:

For more information on Vitesse Products visit the Vitesse web site at www.vitesse.com or contact Vitesse Sales at (800) VITESSE or sales@vitesse.com

Vitesse, ASIC-Friendly, FibreTimer, TimeStream and Snoop Loop are trademarks of Vitesse Semiconductor Corporation.

All other trademarks or registered trademarks mentioned herein are the property of their respective holders. Vitesse Semiconductor Corporation ("Vitesse") retains the right to make changes to its products or specifications to improve performance, reliability or manufacturability. All information in this document, including descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time.

741 Calle Plano Camarillo, CA 93012, USA Tel: +1 805.388.3700 Fax: +1 805.987.5896 www.vitesse.com