# RENESAS

# DATASHEET

FN6884

Rev 0.00 May 11, 2009

## ISL6265A

Multi-Output Controller with Integrated MOSFET Drivers for AMD SVI Capable Mobile CPUs

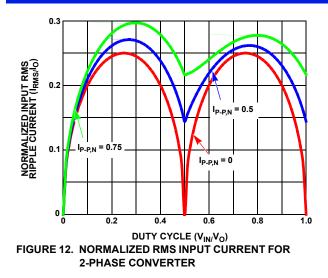

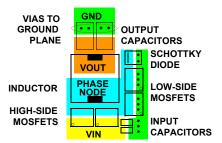

The ISL6265A is a multi-output controller with embedded gate drivers. A single-phase controller powers the Northbridge (VDDNB) portion of the CPU. The two remaining controller channels can be configured for two-phase or individual single-phase outputs. For uniplane CPU applications, the ISL6265A is configured as a two-phase buck converter. This allows the controller to interleave channels to effectively double the output voltage ripple frequency, and thereby reduce output voltage ripple amplitude with fewer components, lower component cost, reduced power dissipation, and smaller area. For dual-plane processors, the ISL6265A can be configured as independent single-phase controllers powering VDD0 and VDD1.

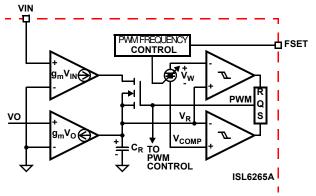

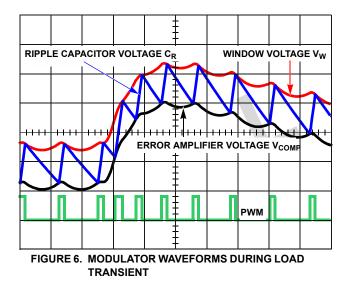

The heart of the ISL6265A is the patented R<sup>3</sup> Technology<sup>TM</sup>, Intersil's Robust Ripple Regulator modulator. Compared with the traditional buck regulator, the R<sup>3</sup> Technology<sup>TM</sup> has a faster transient response. This is due to the R<sup>3</sup> modulator commanding variable switching frequency during a load transient.

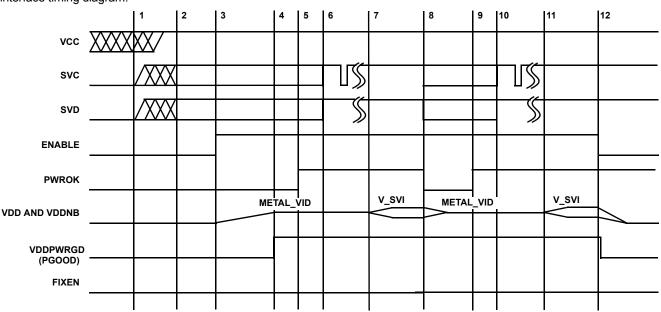

The Serial VID Interface (SVI) allows dynamic adjustment of the Core and Northbridge output voltages independently and in combination from 0.500V to 1.55V. Core and Northbridge output voltages achieve a 0.5% system accuracy over-temperature.

A unity-gain differential amplifier is provided for remote CPU die sensing. This allows the voltage on the CPU die to be accurately regulated per AMD mobile CPU specifications. Core output current sensing is realized using lossless inductor DCR sensing. All outputs feature overcurrent, overvoltage and undervoltage protection.

## Ordering Information

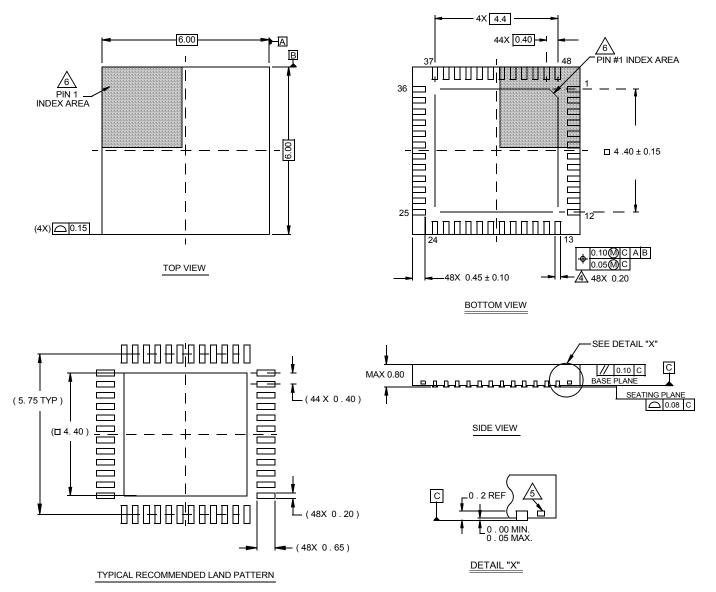

| PART NUMBER<br>(Note) | PART<br>MARKING | TEMP<br>RANGE<br>(°C) | PACKAGE<br>(Pb-Free)            | PKG.<br>DWG. # |

|-----------------------|-----------------|-----------------------|---------------------------------|----------------|

| ISL6265AHRTZ          | 6265A HRTZ      | -10 to +100           | 48 Ld 6x6 TQFN                  | L48.6x6        |

| ISL6265AHRTZ-T*       | 6265A HRTZ      | -10 to +100           | 48 Ld 6x6 TQFN<br>Tape and Reel | L48.6x6        |

\*Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020

## Features

- Core Configuration Flexibility

- Dual Plane, Single-Phase Controllers

- Uniplane, Two-Phase Controller

- Precision Voltage Regulators

- 0.5% System Accuracy Over-temperature

- · Voltage Positioning with Adjustable Load Line and Offset

- Internal Gate Drivers with 2A Driving Capability

- Differential Remote CPU Die Voltage Sensing

- Core Differential Current Sensing: DCR or Resistor

- Northbridge Lossless r<sub>DS(ON)</sub> Current Sensing

- Serial VID Interface

- Two Wire Clock and Data Bus

- Supports High-Speed I<sup>2</sup>C

- 0.500V to 1.55V in 12.5mV Steps

- Supports PSI\_L Power-Saving Mode

- Core Outputs Feature Phase Shedding with PSI\_L

- Adjustable Output-Voltage Offset

- · Digital Soft-Start of all Outputs

- User Programmable Switching Frequency

- Static and Dynamic Current Sharing (Uniplane Core)

- Overvoltage, Undervoltage, and Overcurrent Protection

- Pb-Free (RoHS compliant)

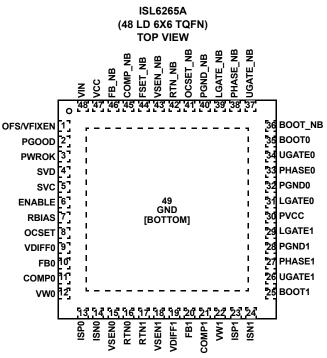

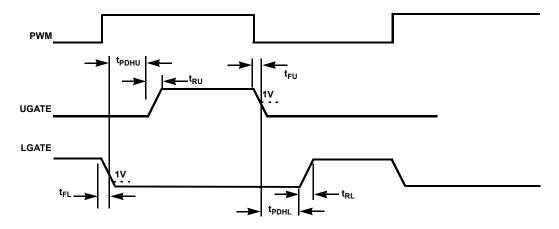

## Pinout

#### Function Block Diagram

FIGURE 1. SIMPLIFIED FUNCTION BLOCK DIAGRAM OF ISL6265A

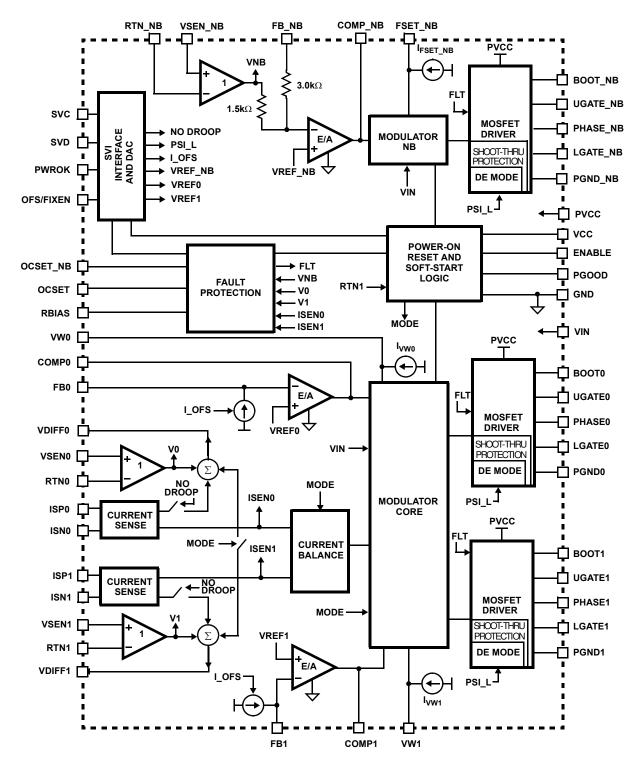

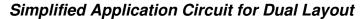

Simplified Application Circuit for Dual Plane and Northbridge Support

FIGURE 2. ISL6265A BASED DUAL-PLANE AND NORTHBRIDGE CONVERTERS WITH INDUCTOR DCR CURRENT SENSING

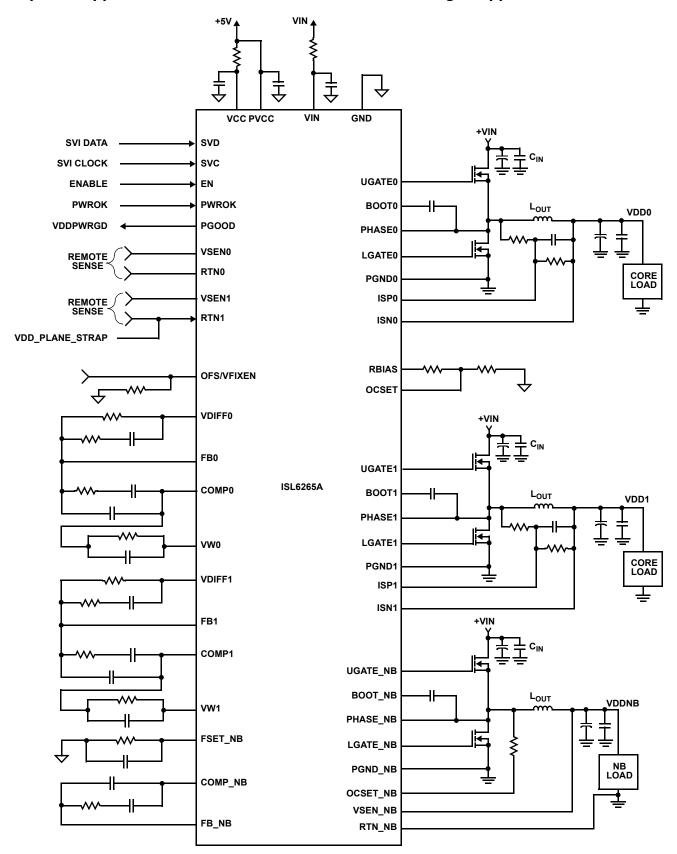

Simplified Application Circuit for Uniplane Core and Northbridge Support

FIGURE 3. ISL6265A BASED UNIPLANE AND NORTHBRIDGE CONVERTERS WITH INDUCTOR DCR CURRENT SENSING

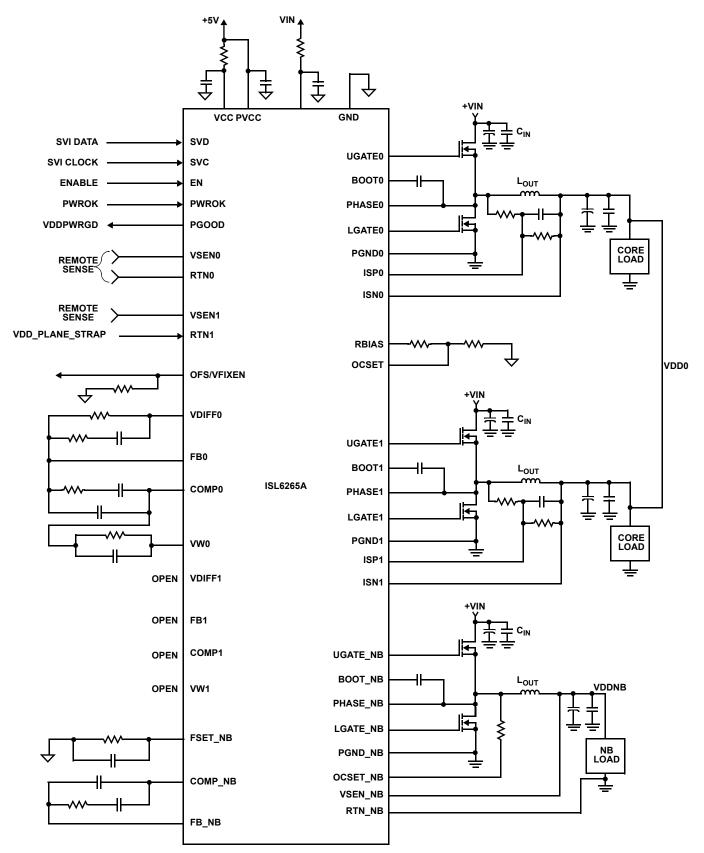

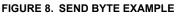

FIGURE 4. ISL6265A BASED UNIPLANE OR DUAL PLANE CORE CONVERTER WITH INDUCTOR DCR CURRENT SENSING

#### **Absolute Maximum Ratings**

| Supply Voltage, VCC, PVCC         -0.3 - +7V           Battery Voltage, VIN         +28V           Boot Voltage (BOOT)         -0.3V to +33V |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| Boot to Phase Voltage (BOOT-PHASE)                                                                                                           |

| -0.3V to +9V (<10ns)                                                                                                                         |

| Phase Voltage (PHASE)                                                                                                                        |

| UGATE Voltage (UGATE) PHASE -0.3V (DC) to BOOT                                                                                               |

| LGATE Voltage (LGATE)                                                                                                                        |

| ALL Other Pins0.3V to (VCC + 0.3V)                                                                                                           |

| Open Drain Outputs, PGOOD                                                                                                                    |

#### **Thermal Information**

| Thermal Resistance (Typical, Notes 1, 2) | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|------------------------------------------|----------------------|----------------------|

| 48 Ld TQFN                               | 32                   | 3.5                  |

| Maximum Junction Temperature             |                      | +150°C               |

| Maximum Storage Temperature Range        | 65°                  | °C to +150°C         |

| Pb-Free Reflow Profile                   |                      | ee link below        |

| http://www.intersil.com/pbfree/Pb-FreeR  | eflow.asp            |                      |

#### **Recommended Operating Conditions**

| Supply Voltage, VCC, PVCC | +5V ±5%        |

|---------------------------|----------------|

| Battery Voltage, VIN      | +6V to 24V     |

| Ambient Temperature       | 10°C to +100°C |

| Junction Temperature      | 10°C to +125°C |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 1. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 2. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

## Electrical Specifications VC

VCC = PVCC = 5V,  $V_{IN}$  = 12V,  $T_A$  = -10°C to +100°C, Unless Otherwise Specified. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested

| PARAMETER                                                                            | SYMBOL                         | TEST CONDITIONS                                                                                                              |      | TYP   | MAX  | UNITS |

|--------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| INPUT POWER SUPPLY                                                                   |                                |                                                                                                                              |      | 1     | 1    |       |

| +5V Supply Current                                                                   | I <sub>VCC</sub>               | EN = 3.3V                                                                                                                    | -    | 7.8   | 10   | mA    |

|                                                                                      |                                | EN = 0V                                                                                                                      | -    | -     | 1    | μA    |

| POR (Power-On Reset) Threshold                                                       | VCC POR <sub>r</sub>           | VCC Rising                                                                                                                   | -    | 4.35  | 4.5  | V     |

|                                                                                      | VCC POR <sub>f</sub>           | VCC Falling                                                                                                                  | 3.9  | 4.1   | -    | V     |

| Battery Supply Current (VIN)                                                         | I <sub>VIN</sub>               | EN = 0V, VIN = 24V                                                                                                           | -    | -     | 1    | μA    |

| SYSTEM AND REFERENCES                                                                |                                | 1                                                                                                                            | 1    | 1     | 1    | 1     |

| System Accuracy<br>(V <sub>core0</sub> , V <sub>core1</sub> , V <sub>core_NB</sub> ) | %Error<br>(V <sub>CORE</sub> ) | No load, closed loop, active mode<br>VID = 0.75V to 1.55V                                                                    | -0.5 | -     | 0.5  | %     |

|                                                                                      |                                | VID = 0.50V to 0.7375V                                                                                                       | -5   | -     | +5   | mV    |

| RBIAS Voltage                                                                        | R <sub>RBIAS</sub>             | R <sub>RBIAS</sub> = 117kΩ                                                                                                   | 1.15 | 1.17  | 1.19 | V     |

| Maximum Output Voltage                                                               | V <sub>COREx</sub><br>(max)    | SVID = [000_0000b]                                                                                                           | -    | 1.55  | -    | V     |

| Minimum Output Voltage                                                               | V <sub>COREx</sub><br>(min)    | SVID = [101_0100b]                                                                                                           | -    | 0.500 | -    | V     |

| CHANNEL FREQUENCY                                                                    |                                | L                                                                                                                            |      | 1     | I    | 1     |

| Nominal CORE Switching Frequency                                                     | f <sub>SW_core0</sub>          | VIN = 15.5V, $V_{DAC}$ = 1.55V, $V_{FB0}$ = 1.60V,<br>force $V_{comp_0}$ = 2V, $R_{VW}$ = 6.81k $\Omega$ , 2-Phase Operation | 285  | 300   | 315  | kHz   |

| Nominal NB Switching Frequency                                                       | f <sub>SW_core_NB</sub>        | $R_{FSET_NB}$ = 22.1k $\Omega$ , $C_{FSET_NB}$ = 1nF, $V_{DAC}$ = 0.5V,<br>$V_{sen_nb}$ = 0.51V                              | 285  | 300   | 315  | kHz   |

| Core Frequency Adjustment Range                                                      |                                |                                                                                                                              | 200  | -     | 500  | kHz   |

| NB Frequency Adjustment Range                                                        |                                |                                                                                                                              | 200  | -     | 500  | kHz   |

| AMPLIFIERS                                                                           | 1                              |                                                                                                                              |      | 1     |      | 1     |

| Error Amp DC Gain (Note 3)                                                           | A <sub>V0</sub>                |                                                                                                                              | -    | 90    | -    | dB    |

| Error Amp Gain-Bandwidth Product<br>(Note 3)                                         | GBW                            | C <sub>L</sub> = 20pF                                                                                                        | -    | 18    | -    | MHz   |

| Error Amp Slew Rate (Note 3)                                                         | SR                             | C <sub>L</sub> = 20pF                                                                                                        | -    | 5.0   | -    | V/µs  |

#### **Electrical Specifications**

VCC = PVCC = 5V,  $V_{IN}$  = 12V,  $T_A$  = -10°C to +100°C, Unless Otherwise Specified. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested (**Continued**)

| PARAMETER                                                           | SYMBOL                  | YMBOL TEST CONDITIONS                                      |                                       | TYP   | MAX   | UNITS    |

|---------------------------------------------------------------------|-------------------------|------------------------------------------------------------|---------------------------------------|-------|-------|----------|

| CORE CURRENT SENSE                                                  |                         |                                                            | · · · · · · · · · · · · · · · · · · · |       |       |          |

| Current Imbalance Threshold                                         |                         |                                                            | -                                     | 4     | -     | mV       |

| Input Bias Current                                                  |                         |                                                            | -                                     | 20    | -     | nA       |

| RTN1 Threshold                                                      |                         |                                                            | -                                     | 0.8   | -     | V        |

| SOFT START/VID-ON-THE-FLY                                           |                         |                                                            |                                       |       |       | 4        |

| Soft-Start Voltage Transition                                       | V <sub>SS</sub>         |                                                            | 1.25                                  | 1.875 | 2.50  | mV/µs    |

| VID on the Fly Transition                                           |                         |                                                            | 5                                     | 7.5   | 10    | mV/µs    |

| GATE DRIVER DRIVING CAPABILI                                        | TY [CORE ANI            | D NB]                                                      |                                       |       |       |          |

| UGATE Source Resistance (Note 4)                                    | R <sub>SRC(UGATE)</sub> | 500mA Source Current                                       | -                                     | 1     | 1.5   | Ω        |

| UGATE Source Current (Note 4)                                       | I <sub>SRC(UGATE)</sub> | V <sub>UGATE_PHASE</sub> = 2.5V                            | -                                     | 2     | -     | Α        |

| UGATE Sink Resistance (Note 4)                                      | R <sub>SNK(UGATE)</sub> | 500mA Sink Current                                         | -                                     | 1     | 1.5   | Ω        |

| UGATE Sink Current (Note 4)                                         | I <sub>SNK(UGATE)</sub> | V <sub>UGATE_PHASE</sub> = 2.5V                            | -                                     | 2     | -     | Α        |

| LGATE Source Resistance (Note 4)                                    | R <sub>SRC(LGATE)</sub> | 500mA Source Current                                       | -                                     | 1     | 1.5   | Ω        |

| LGATE Source Current (Note 4)                                       | I <sub>SRC(LGATE)</sub> | V <sub>LGATE</sub> = 2.5V                                  | -                                     | 2     | -     | А        |

| LGATE Sink Resistance (Note 4)                                      | R <sub>SNK(LGATE)</sub> | 500mA Sink Current                                         | -                                     | 0.5   | 0.9   | Ω        |

| LGATE Sink Current (Note 4)                                         | I <sub>SNK(LGATE)</sub> | V <sub>LGATE</sub> = 2.5V                                  | -                                     | 4     | -     | Α        |

| UGATE to PHASE Resistance                                           | R <sub>p(UGATE)</sub>   |                                                            | -                                     | 1     | -     | kΩ       |

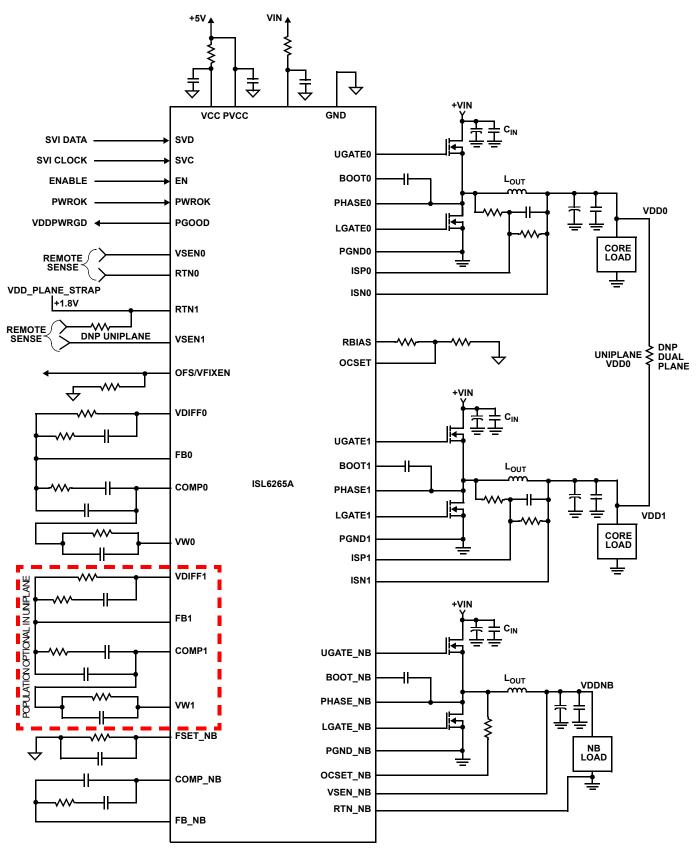

| GATE DRIVER SWITCHING TIMING                                        |                         | L6265A Gate Driver Timing Diagram" on page 8)              |                                       |       |       |          |

| UGATE Rise Time (Note 3)                                            | t <sub>RU</sub>         | PV <sub>CC</sub> = 5V, 3nF Load                            | -                                     | 8.0   | -     | ns       |

| LGATE Rise Time (Note 3)                                            | t <sub>RL</sub>         | PV <sub>CC</sub> = 5V, 3nF Load                            | -                                     | 8.0   | -     | ns       |

| UGATE Fall Time (Note 3)                                            | t <sub>FU</sub>         | PV <sub>CC</sub> = 5V, 3nF Load                            | -                                     | 8.0   | -     | ns       |

| LGATE Fall Time (Note 3)                                            | t <sub>FL</sub>         | PV <sub>CC</sub> = 5V, 3nF Load                            | -                                     | 4.0   | -     | ns       |

| UGATE Turn-on Propagation Delay                                     | t <sub>PDHU</sub>       | PV <sub>CC</sub> = 5V, Outputs Unloaded                    | -                                     | 36    | -     | ns       |

| LGATE Turn-on Propagation Delay                                     | t <sub>PDHL</sub>       | PV <sub>CC</sub> = 5V, Outputs Unloaded                    | -                                     | 20    | -     | ns       |

| BOOTSTRAP DIODE                                                     |                         |                                                            |                                       |       |       | <u> </u> |

| Forward Voltage                                                     |                         | V <sub>DDP</sub> = 5V, Forward Bias Current = 2mA          | 0.43                                  | 0.58  | 0.67  | V        |

| Leakage                                                             |                         | V <sub>R</sub> = 16V                                       | -                                     | -     | 5     | μA       |

| POWER GOOD AND PROTECTION                                           | MONITOR                 | , K                                                        |                                       |       |       |          |

| PGOOD Low Voltage                                                   | V <sub>OL</sub>         | I <sub>PGOOD</sub> = 4mA                                   | -                                     | 0.2   | 0.5   | V        |

| PGOOD Leakage Current                                               | I <sub>OH</sub>         | P <sub>GOOD</sub> = 5V                                     | -1                                    | -     | 1     | μA       |

| PGOOD High After Soft-Start                                         |                         | Enable to PGOOD High, V <sub>COREx</sub> = 1.1V            | 570                                   | 700   | 1010  | μs       |

| PGOOD Low After Fault                                               |                         | Fault to PGOOD Low                                         | 160                                   | 208   | 250   | μs       |

| Undervoltage Threshold                                              | U <sub>VH</sub>         | V <sub>COREx</sub> falls below set-point for 208µs         | 240                                   | 295   | 350   | mV       |

| Overvoltage Threshold                                               | O <sub>VHS</sub>        | $V_{\Omega}$ rising above threshold > 0.5µs                | 1.770                                 | 1.795 | 1.820 | V        |

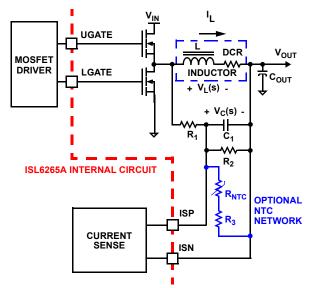

| OVERCURRENT PROTECTION VD                                           |                         |                                                            |                                       |       |       |          |

| OCSET Reference Voltage<br>(V <sub>ISPx</sub> - V <sub>ISNx</sub> ) |                         | V <sub>OCSET</sub> = 180mV; VIN = 15.5V                    | 5                                     | 6.0   | 7     | mV       |

| OVERCURRENT PROTECTION VD                                           | D NB                    | 1                                                          |                                       |       |       | <u> </u> |

| OCSET_NB OCP Current                                                |                         | RBIAS pin to GND = $117k\Omega$ ; Trips after 8 PWM cycles | 9.2                                   | 10    | 10.8  | μA       |

|                                                                     |                         |                                                            | 0.2                                   | 10    | .0.0  | μΛ       |

#### Electrical Specifications

VCC = PVCC = 5V,  $V_{IN}$  = 12V,  $T_A$  = -10°C to +100°C, Unless Otherwise Specified. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested **(Continued)**

| SYMBOL                | TEST CONDITIONS                                                                                      | MIN                                                                                                                                                                                                                                                                                                                                                                                                                        | ТҮР                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MAX                                                                                                                                                                                                                                                  | UNITS                                                                                                                                                                                                                         |

|-----------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                               |

| V <sub>OFS</sub>      | $R_{OFS}$ = 240k $\Omega$ (OFS pin to GND)                                                           | 1.18                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.22                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                             |

| I <sub>FB</sub>       | I <sub>OFS</sub> = 10μA                                                                              | 9.0                                                                                                                                                                                                                                                                                                                                                                                                                        | 9.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10.8                                                                                                                                                                                                                                                 | μA                                                                                                                                                                                                                            |

| V <sub>OFS</sub>      |                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                    | V                                                                                                                                                                                                                             |

| V <sub>OFS</sub>      |                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                    | V                                                                                                                                                                                                                             |

| I <sub>OFS</sub>      | 1.8V < OFS < VCC                                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                    | μA                                                                                                                                                                                                                            |

|                       | 1                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                               |

| V <sub>IL(3.3V)</sub> |                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.9                                                                                                                                                                                                                                                  | V                                                                                                                                                                                                                             |

| V <sub>IH(3.3V)</sub> |                                                                                                      | 2.0                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                    | V                                                                                                                                                                                                                             |

|                       | Logic input is low                                                                                   | -1                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                    | μA                                                                                                                                                                                                                            |

|                       | Logic input is high at 3.3V                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                    | μA                                                                                                                                                                                                                            |

|                       |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                               |

|                       |                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.8                                                                                                                                                                                                                                                  | V                                                                                                                                                                                                                             |

|                       |                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                    | V                                                                                                                                                                                                                             |

|                       |                                                                                                      | 1.05                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                    | V                                                                                                                                                                                                                             |

|                       |                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.45                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                             |

|                       |                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                    | V                                                                                                                                                                                                                             |

|                       | 3mA Sink Current                                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.285                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                             |

|                       | EN = 0V, SVC, SVD = 0V                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                          | < -100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                                                                                    | nA                                                                                                                                                                                                                            |

|                       | EN = 5V, SVC, SVD = 1.8V                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                          | < -100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                                                                                    | nA                                                                                                                                                                                                                            |

|                       |                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                          | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                             |

|                       | VSEN = 0.5V to 1.55V; RTN = 0 ±0.1V                                                                  | -2                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                                                                                                                                                                                                    | mV                                                                                                                                                                                                                            |

|                       | V <sub>OFS</sub><br>I <sub>FB</sub><br>V <sub>OFS</sub><br>I <sub>OFS</sub><br>V <sub>IL(3.3V)</sub> | $V_{OFS} = R_{OFS} = 240 k\Omega \text{ (OFS pin to GND)}$ $I_{FB} = I_{OFS} = 10 \mu A$ $V_{OFS} = 10 \mu A$ $V_{OFS} = 1.8V < OFS < VCC$ $V_{IL(3.3V)} = 1.8V < OFS < VCC$ $V_{IL(3.3V)} = 1.8V < OFS < VCC$ $U_{IL(3.3V)} = 0$ $I_{OFS} = 1.8V < OFS < VCC$ $I_{OFS} = 1.8V < OFS < VCC = 0$ $I_{OFS} = 1.8V < OFS < VCC = 1.8V$ | VOFS         ROFS = 240kQ (OFS pin to GND)         1.18 $I_{FB}$ $I_{OFS}$ = 10µA         9.0           VOFS         -           VIL(3.3V)         -           VIL(3.3V)         2.0           Logic input is low         -1           Logic input is high at 3.3V         -           -         -         -           Image: Input is high at 3.3V         -           -         -         -           Image: Input is high at 3.3V         -           -         -         -           -         -         -           Image: Input is high at 3.3V         -           -         -         -           Image: Input is high at 3.3V         -           Image: | VOFS         ROFS = 240k\Omega (OFS pin to GND)         1.18         1.2           IFB         IOFS = 10µA         9.0         9.9           VOFS         -         1.8           VOFS         -         4.0           IOFS         1.8V < OFS < VCC | $\begin{array}{c c c c c c c c c } V_{OFS} & R_{OFS} = 240 k\Omega  (OFS  pin  to  GND) & 1.18 & 1.2 & 1.22 \\ \hline I_{FB} & I_{OFS} = 10 \mu A & 9.0 & 9.9 & 10.8 \\ \hline V_{OFS} & & & & & & & & & & & & & & & & & & &$ |

NOTES:

3. Limits should be considered typical and are not production tested.

4. Limits established by characterization and are not production tested.

## ISL6265A Gate Driver Timing Diagram

## Functional Pin Description

### VCC

The bias supply for the IC's control circuitry. Connect this pin to a +5V supply and decouple using a quality  $0.1\mu F$  ceramic capacitor.

#### VIN

Battery supply voltage. It is used for input voltage feed-forward to improve the input line transient performance.

#### PVCC

The power supply pin for the internal MOSFET gate drivers of the ISL6265A. Connect this pin to a +5V power supply. Decouple this pin with a quality  $1.0\mu$ F ceramic capacitor.

#### GND

The bias and reference ground for the IC. The GND connection for the ISL6265A is through the thermal pad on the bottom of the package.

#### RBIAS

A 117k $\Omega$  resistor from RBIAS to GND sets internal reference currents. The addition of capacitance to this pin must be avoided and can create instabilities in operation.

#### OFS/VFIXEN

A resistor from this pin to GND programs a DC current source, which generates a positive offset voltage across the resistor between FB and VDIFF pins. In this case, the OFS pin voltage is +1.2V and VFIX mode is not enabled. If OFS is pulled up to +3.3V, VFIX mode is enabled, the DAC decodes the SVC and SVD inputs to determine the programmed voltage, and the OFS function is disabled. If OFS is pulled up to +5V, the OFS function and VFIX mode are disabled.

#### PWROK

System power good input. When this pin is high, the SVI interface is active and I<sup>2</sup>C protocol is running. While this pin is low, the SVC, SVD, and VFIXEN input states determine the pre-PWROK metal VID or VFIX mode voltage. This pin must be low prior to the ISL6265A PGOOD output going high per the AMD SVI Controller Guidelines.

#### PGOOD

Controller power-good open-drain output. This pin is typically pulled up externally by a 2.0k $\Omega$  resistor to +3.3V. During normal operation, this pin indicates whether all output voltages are within specified overvoltage and undervoltage limits and no overcurrent condition is present. If any output voltage exceeds these limits or a reset event occurs, the pin is pulled low. This pin is always low prior to the end of soft-start.

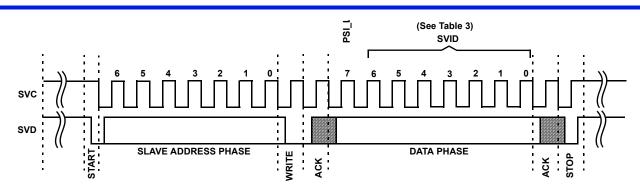

#### SVC

This pin is the serial VID clock input from the AMD processor.

#### SVD

This pin is the serial VID data bidirectional signal to and from the master device on the AMD processor.

#### ENABLE

Digital input enable. A high level logic signal on this pin enables the ISL6265A.

#### FSET\_NB

A resistor from this pin to GND programs the switching frequency of the Northbridge controller (for example,  $22.1k \sim 260kHz$ ).

#### FB\_NB

This pin is the output voltage feedback to the inverting input of the Northbridge controller error amplifier.

#### COMP\_NB