STRUCTURE: Silicon Monolithic Integrated Circuit

PRODUCT NAME Synchronous rectification with built-in FET type DC/DC converter IC

**BD8641EFV** MODEL NAME:

**FEATURES** · Synchronous rectification with built-in FET type DC/DC converter

- Reference voltage accuracy FB 0.8V±1%

- Switching frequency 250kHz~2.3MHz (Synchronizable with external clock.)

Over current protection circuit

· Thermal shutdown

- Output voltage watch (VDET) function

- Input low voltage detection (UVLO) function

- Soft start / Start delay circuit

#### **©ABSOLUTE MAXIMUM RATING** (Ta=25°C)

| Parameter               | Symbol                              | Limits            | Unit |

|-------------------------|-------------------------------------|-------------------|------|

| Input supply voltage    | PV <sub>IN</sub> , SV <sub>IN</sub> | 7                 | V    |

| Input terminal voltage  | $V_{INP}^{*1}$                      | $V_{IN}$          | V    |

| Output terminal voltage | $V_{OUT}^{*_2}$                     | $V_{IN}$          | ٧    |

| Output current          | l <sub>out</sub>                    | 4                 | Α    |

| Power dissipation       | Pd                                  | 3.2 <sup>*3</sup> | W    |

| Operating temperature   | Topr                                | -40 ~ 85          | °C   |

| Storage temperature     | Tstg                                | -55 ~ 150         | °C   |

$<sup>*1\,</sup>V_{\text{INP}}$  Application terminal : SYNCLK, EN, SS/DELAY, FB

Operating at higher than Ta=25°C, 25.6mW shall be reduced per 1

### Operation condition

| Parameter            | Symbol           | MIN | TYP | MAX | Unit |

|----------------------|------------------|-----|-----|-----|------|

| Input supply voltage | $V_{IN}$         | 3.0 | -   | 5.5 | V    |

| Output current       | I <sub>OUT</sub> | -   | -   | 3   | Α    |

This product is not designed for protection against radioactive rays.

# Status of this document

The Japanese version of this document is the formal specification.

A customer may use this translation version only for a reference to help reading the formal version. If there are any differences in translation version of this document, formal version takes priority.

Be careful to handle because the content of the description of this material might correspond to the labor (technology in the design, manufacturing, and use) in foreign country exchange and Foreign Trade Control Law.

<sup>\*2</sup> V<sub>OUT</sub> Application terminal: SW, VDET, FC, RT

<sup>\*3 (70</sup>mm×70mm, thickness 1.6mm, and four layer glass epoxy substrates)When mounting substrate and the package back exposure part are connected with solder.

# ©Electrical characteristic

(Unless otherwise noted Ta=25°C,  $PV_{IN}$ ,  $SV_{IN}$ =3.3V, GND=0V)

| Parameter                         | Symbol                | Specification value |      |       | UNIT | Condition                      |  |

|-----------------------------------|-----------------------|---------------------|------|-------|------|--------------------------------|--|

| Parameter                         | Symbol                | MIN                 | TYP  | MAX   | UNIT | Condition                      |  |

| VIN supply current (operating)    | I <sub>Q_active</sub> | -                   | 380  | 570   | μA   | $V_{FB} = 0.83V, V_{FC} = 1V$  |  |

| VIN supply current (standby)      | $I_{Q\_stby}$         | -                   | 0    | 10    | μA   | V <sub>EN</sub> = 0V           |  |

| Reference voltage (VREF)          | $V_{REF}$             | 0.792               | 0.8  | 0.808 | V    |                                |  |

| Output rise detection voltage     | $V_{OVP}$             | 30                  | 60   | 90    | mV   | Monitoring FB terminal         |  |

| Output decrease detection voltage | $V_{LVP}$             | -90                 | -60  | -30   | mV   | Monitoring FB terminal         |  |

| Terminal VDET output current      | $I_{VDET}$            | 0.4                 | -    | ı     | mA   | V <sub>VDET</sub> < 0.3V       |  |

| Oscillation frequency             | f <sub>OSC</sub>      | 2.0                 | 2.3  | 2.6   | MHz  | $R_{RT} = 43k\Omega$           |  |

| Pch FET ON resistance             | R <sub>PFET</sub>     | -                   | 75   | 110   | mΩ   | I <sub>SW</sub> = 1A           |  |

| Nch FET ON resistance             | R <sub>NFET</sub>     | -                   | 55   | 90    | mΩ   | I <sub>SW</sub> = -1A          |  |

| UVLO voltage                      | $V_{\text{UVLO}}$     | 2.35                | 2.50 | 2.65  | V    |                                |  |

| SW leak current                   | $I_{LSW}$             | -                   | 0    | 10    | μA   | $V_{EN}$ = 0V, $V_{IN}$ = 5.5V |  |

| EN terminal H threshold voltage   | $V_{ENH}$             | 1.1                 | -    | ı     | V    |                                |  |

| EN terminal L threshold voltage   | $V_{ENL}$             | -                   | -    | 0.4   | V    |                                |  |

| FC sink current                   | I <sub>FCSI</sub>     | 5                   | 10   | -     | μA   |                                |  |

| FC source current                 | I <sub>FCSO</sub>     | -                   | -10  | -5    | μA   |                                |  |

| SS/DELAY terminal source current  | I <sub>SSSO</sub>     | 2                   | 4    | 6     | μA   |                                |  |

<sup>●</sup>V<sub>FB</sub>:FB terminal voltage、V<sub>EN</sub>:EN terminal voltage、V<sub>FC</sub>:FC terminal voltage、V<sub>VDET</sub>: VDET terminal voltage

Current capability should not exceed Pd.

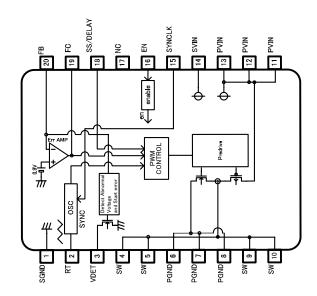

# **©BLOCK DIAGRAM**

# **©PIN ASSIGNMENT**

| No. | Symbol | Description                                         | No. | Symbol   | Description                                        |

|-----|--------|-----------------------------------------------------|-----|----------|----------------------------------------------------|

| 1   | SGND   | Signal GND terminal                                 | 11  | PVIN     | Power supply input terminal                        |

| 2   | RT     | Frequency adjustment resistance connection terminal | 12  | PVIN     | Power supply input terminal                        |

| 3   | VDET   | Output abnormality detection terminal               | 13  | PVIN     | Power supply input terminal                        |

| 4   | SW     | Switching output terminal                           | 14  | SVIN     | Signal system power supply input terminal          |

| 5   | SW     | Switching output terminal                           | 15  | SYNCLK   | Input terminal for external clock synchronization  |

| 6   | PGND   | Power GND terminal                                  | 16  | EN       | Enable input terminal                              |

| 7   | PGND   | Power GND terminal                                  | 17  | NC       | -                                                  |

| 8   | PGND   | Power GND terminal                                  | 18  | SS/DELAY | Soft start adjustment capacity connection terminal |

| 9   | SW     | Switching output terminal                           | 19  | FC       | Phase amends terminal                              |

| 10  | SW     | Switching output terminal                           | 20  | FB       | Feedback terminal                                  |

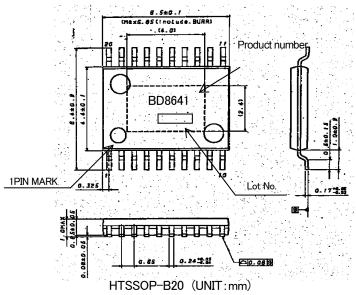

# **OPACKAGE OUTLINE**

#### **ONOTE ON USE**

#### 1. About the absolute maximum rating

Attention is brushed off enough to the quality control, it is likely to destroy when the absolute maximum rating such as impressed voltages (VCC\_IN,DCIN) and ranges (Topr) of the operating temperature as it is exceeded, the mode of breakings of the short or the opening, etc. cannot be specified, and examine it in this IC to give physical measures for safety such as fuses when a special mode that exceeds the absolute maximum rating is assumed.

2. About the reverse-connection of the power supply connector

IC might destroy it by reversely connecting the power supply connector. Give measures such as putting the diode between power supply terminals of power supply and IC outside for the reverse-touching destruction protection.

3. Power supply line

Please do measures such as putting the bypass capacitor in power supply-GND nearest pin of this IC as the route of the resurrection current to cause the return of the current in which it resurrected it by the counter electromotive force of the coil.

Please confirm the characteristic of the electrolytic capacitor enough as the capacity omission etc. at the low temperature never happen, and decide it

4. About grand potential

Any state of operation must become the lowest potential about the potential of the terminal GND. Moreover, confirm whether there is terminal that is actually the voltage of GND or less including transients.

5. About the heat design

Think about permissible loss (Pd) in an actual state of use, and do the heat design with the margin enough.

6. About the short and the miss-installation between terminals

Note the direction and the miss-registration of IC enough when you install it in the set substrate. IC might destroy it as well as reversely connecting the power supply connector when installing it by mistake. Moreover, there is fear of destruction when the foreign body enters between terminals, the terminal, the power supply, and grandeur and it is short-circuited.

7. About operation in strong electromagnetic field

In use in strong electromagnetic field, note that there is a possibility of malfunctioning.

8. About the capacitor during output-GND

The current charged the capacitor with when VCC is 0V or is GND and is short-circuited when a big capacitor is connected between GND output by some factors flows into the output and it is likely to destroy it. Give the capacitor between GND output to 0.1µF or less.

9. About the inspection by the set substrate

It is likely to suffer stress to IC and discharge electricity every one process when you connect the capacitor with the pin with low impedance when inspecting it in the set substrate. Moreover, detach it after connecting after the power supply is turned off without fail when detaching it to G in the inspection process, inspecting, and turning off the power supply. n addition, be give the earth to the assembly process as a static electricity measures, and careful enough when it transports and you preserve it.

10. About each input terminal

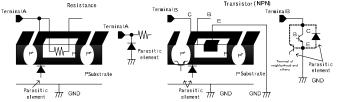

This IC is a monolithic IC which has a  $P^{\dagger}$  isolations and P substrate to isolate elements each other.

This P layer and an N layer in each element form a PN junction to construct various parasitic elements.

For instance, the potential difference operates in resistance as shown in the figure below when resistance and the transistor connect it with the terminal and the playground (GND) >(terminal B) joint of PN operates as a parasitic diode in playground (GND) >(terminal A) transistor (NPN). In addition, the NPN transistor of parasitism works with N layer of the element of the above-mentioned parasitic diode and the neighborhood and others in transistor (NPN). A parasitic element in IC composition is inevitably formed because of the potential relation.

A parasitic element can operate, the interference with the circuit operation be caused, it malfunction, and, consequently, it cause destruction. Therefore, do not do the usage that a parasitic element operates as a voltage that is lower than the playground (GND;P substrate) is impressed to the input terminal enough. Moreover, do not impress the voltage to the input terminal when you do not impress the power-supply voltage to IC. Give each input terminal to me the voltage below the power-supply voltage or in the guarantee value of an electric characteristic when you similarly impress the power-supply voltage.

Example of IC of simple structure

#### 11. Earth wiring pattern

If small signal GND and large current GND exist, disperse their pattern. In addition, for voltage change by pattern wiring impedance and large current not to change voltage of small signal GND, each ground terminal of IC must be connected at the one point on the set circuit board. As for GND of external parts, it is similar to the above-mentioned.

#### 12. Thermal Shut-Down

When a thermal shutdown operates, the DC/DC converter controller of all Ch is turned off. When a thermal shutdown is released, the DC/DC converter controller of all Ch becomes an operation beginning from turning off.

#### **Notes**

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM CO.,LTD.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations.

More detail product informations and catalogs are available, please contact your nearest sales office.

**ROHM Customer Support System**

THE AMERICAS / EUROPE / ASIA / JAPAN

www.rohm.com

Contact us : webmaster@rohm.co.jp

Copyright © 2009 ROHM CO.,LTD.

ROHM Co., Ltd. 21 Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan

TEL:+81-75-311-2121 FAX:+81-75-315-0172