# DUAL CHANNEL SYNCHRONIZED CURRENT-MODE PWM

# FEATURES

- Single Oscillator Synchronizes Two PWMs

- 150-µA Startup Supply Current

- 2-mA Operating Supply Current

- Operation to 1 MHz

- Internal Soft-Start

- Full-Cycle Fault Restart

- Internal Leading-Edge Blanking of the Current Sense Signal

- 1-A Totem Pole Outputs

- 75-ns Typical Response from Current Sense to Output

- 1.5% Tolerance Voltage Reference

# DESCRIPTION

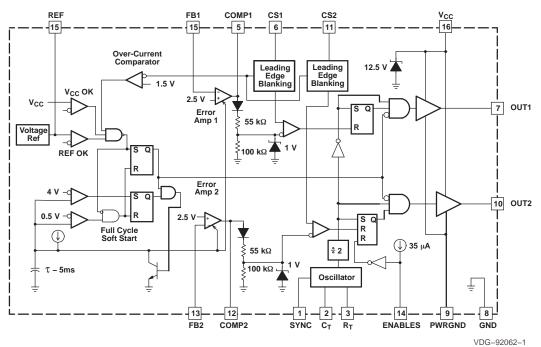

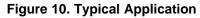

The UCC3810 is a high-speed BiCMOS controller integrating two synchronized pulse width modulators for use in off-line and dc-to-dc power supplies. The UCC3810 family provides perfect synchronization between two PWMs by usin g the same oscillator. The oscillator's sawtooth waveform can be used for slope compensation if required.

Using a toggle flip-flop to alternate between modulators, the UCC3810 ensures that one PWM does not slave, interfere, or otherwise affect the other PWM. This toggle flip- flop also ensures that each PWM is limited to 50% maximum duty cycle, insuring adequate off-time to reset magnetic elements. This device contains many of the same elements of the UC3842 current mode controller family, combined with the enhancements of the UCC3802. This minimizes power supply parts count. Enhancements include leading edge blanking of the current sense signals, full cycle fault restart, CMOS output drivers, and outputs which remain low even when the supply voltage is removed.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ORDERING INFORMATION**

| Tj            | PACKAGED DEVICES <sup>(1)</sup> |               |  |  |  |  |  |  |

|---------------|---------------------------------|---------------|--|--|--|--|--|--|

|               | SOP (DW)                        | PDIP (N)      |  |  |  |  |  |  |

| –40°C to 85°C | UCC2810DW (16)                  | UCC2810N (16) |  |  |  |  |  |  |

| 0°C to 70°C   | UCC3810DW (16)                  | UCC3810N (16) |  |  |  |  |  |  |

All packages are available taped and reeled (indicated by the R suffix on the device type e.g., UCC2810JR)

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                  |                                                  | UNIT         |

|------------------|--------------------------------------------------|--------------|

| V <sub>CC</sub>  | Supply voltage <sup>(3)</sup>                    | 11V          |

| I <sub>CC</sub>  | Supply current                                   | 20mA         |

|                  | Output peak current, OUT1, OUT2, 5% duty cycle   | ±1A          |

|                  | Output energy, OUT1, OUT2, capacitive load 20 µJ | 20µJ         |

|                  | Analog inputs, FB1, FB2, CS1, CS2, SYNC          | -0.3 to 6.3V |

| TJ               | Operating junction temperature                   | 150°C        |

| T <sub>stg</sub> | Storage temperature range                        | –65 to 150°C |

|                  | Lead temperature (soldering, 10 sec)             | 300°C        |

(1) Currents are positive into, negative out of the specified terminal. All voltages are with respect to GND.

- (2) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) In provide the device of the device at these or any other conditions for extended periods may affect device reliability.

(2) In provide the device of the device at the operation of the device reliability.

- (3) In normal operation, V<sub>CC</sub> is powered through a current-limiting resistor. Absolute maximum of 11 V applies when driven from a low impedance such that the V<sub>CC</sub> current does not exceed 20 mA.

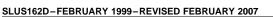

#### **BLOCK DIAGRAM**

## **ELECTRICAL CHARACTERISTICS**

All parameters are the same for both channels, –40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C for the UCC2810, 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C for the UCC3810, V<sub>CC</sub> = 10 V<sup>(1)</sup>; R<sub>T</sub> = 150 kΩ, C<sub>T</sub> = 120 pF; no load; T<sub>A</sub> = T<sub>J</sub>; (unless otherwise specified)

|                    | PARAMETER                            | TEST CO                                                                                                             | NDITIONS                         | MIN   | TYP   | MAX   | UNIT              |  |

|--------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------|-------|-------|-------|-------------------|--|

| REFER              | ENCE                                 |                                                                                                                     |                                  |       |       | L.    |                   |  |

| v                  |                                      | $T_J = 25^{\circ}C$                                                                                                 |                                  | 4.925 | 5.000 | 5.075 | V                 |  |

| V <sub>CC</sub>    | Output voltage                       | T <sub>J</sub> = full range, 0 mA                                                                                   | $A \le I_{REF} \le 5 \text{ mA}$ | 4.85  | 5.00  | 5.10  | v                 |  |

|                    | Load regulation                      | $0 \text{ mA} \le I_{REF} \le 5 \text{ mA}$                                                                         |                                  |       | 5     | 30    |                   |  |

|                    | Line regulation                      | UVLO stop threshold $0.5 \text{ V} \leq \text{V}_{CC} \leq \text{V}_{SHUN}$                                         |                                  |       | 12    |       | mV                |  |

|                    | Output noise voltage <sup>(2)</sup>  | 10Hz <f< 10="" khz,<="" td=""><td><math>T_J = 25^{\circ}C</math></td><td></td><td>235</td><td></td><td>μV</td></f<> | $T_J = 25^{\circ}C$              |       | 235   |       | μV                |  |

|                    | Long term stability <sup>(2)</sup>   | TA = 125°C,                                                                                                         | 1000 hours                       |       | 5     |       | mV                |  |

| I <sub>O(SC)</sub> | Output short circuit current         |                                                                                                                     |                                  |       | -8    | -25   | mA                |  |

| OSCILI             | LATOR                                |                                                                                                                     |                                  |       |       | ·     |                   |  |

| £                  | Oscillator frequency <sup>(3)</sup>  | $R_T = 30 \text{ k}\Omega,$                                                                                         | C <sub>T</sub> = 120 pF          | 860   | 980   | 1100  | kHz               |  |

| f <sub>osc</sub>   | Oscillator frequency (%)             | R <sub>T</sub> = 150 kΩ,                                                                                            | C <sub>T</sub> = 120 pF          | 190   | 220   | 250   | KHZ               |  |

|                    | Temperature stability <sup>(2)</sup> |                                                                                                                     |                                  |       | 2.5%  |       |                   |  |

|                    | Peak voltage                         |                                                                                                                     |                                  |       | 2.5   |       |                   |  |

|                    | Valley voltage                       |                                                                                                                     |                                  |       | 0.05  |       | v                 |  |

|                    | Peak-to-peak amplitude               |                                                                                                                     |                                  | 2.25  | 2.45  | 2.65  | 2.65 <sup>v</sup> |  |

|                    | SYNC threshold voltage               |                                                                                                                     |                                  | 0.80  | 1.65  | 2.20  |                   |  |

|                    | SYNC input current                   | SYNC = 5 V                                                                                                          |                                  |       | 30    |       | μA                |  |

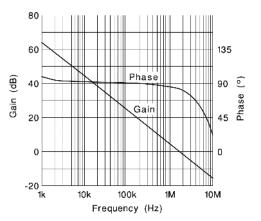

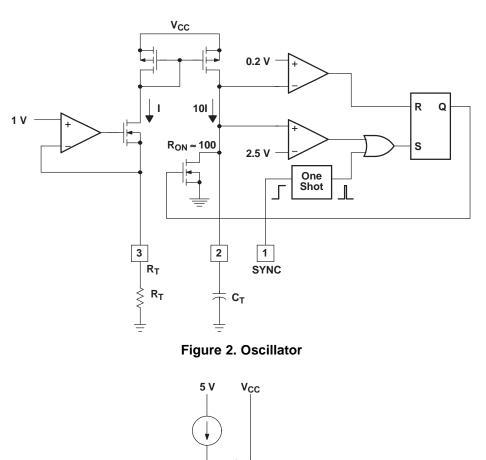

| ERROF              | RAMPLIFIER                           |                                                                                                                     |                                  |       |       | ·     |                   |  |

| V <sub>FB</sub>    | FB input voltage                     | COMP = 2.5 V                                                                                                        |                                  | 2.44  | 2.50  | 2.56  | V                 |  |

| I <sub>FB</sub>    | FB input bias current                |                                                                                                                     |                                  |       |       | ±1    | μA                |  |

|                    | Open loop voltage gain               |                                                                                                                     |                                  | 60    | 73    |       | dB                |  |

| f <sub>GAIN</sub>  | Unity gain bandwidth <sup>(2)</sup>  |                                                                                                                     |                                  |       | 2     |       | MHz               |  |

| I <sub>SINK</sub>  | Sink current, COMP                   | FB = 2.7 V,                                                                                                         | COMP = 1 V                       | 0.3   | 1.4   | 3.5   |                   |  |

| I <sub>SRCE</sub>  | Source current, COMP                 | FB = 1.8 V,                                                                                                         | COMP = 4 V                       | -0.2  | -0.5  | -0.8  | mA                |  |

|                    | Minimum duty cycle                   | COMP = 0 V                                                                                                          |                                  |       |       | 0%    |                   |  |

|                    | Soft-start rise time, COMP           | FB = 1.8 V,<br>Rise from 0.5 V to (F                                                                                | REF – 1.5 V)                     |       |       | 5     | ms                |  |

| CURRE              | ENT SENSE                            |                                                                                                                     |                                  |       |       |       |                   |  |

|                    | Gain <sup>(4)</sup>                  |                                                                                                                     |                                  | 1.20  | 1.55  | 1.80  | V/V               |  |

|                    | Maximum input signal <sup>(5)</sup>  | COMP = 5 V                                                                                                          |                                  | 0.9   | 1.0   | 1.1   | V                 |  |

| I <sub>CS</sub>    | Input bias current, CS               |                                                                                                                     |                                  |       |       | ±200  | nA                |  |

|                    | Propagation delay time (CS to OUT)   | CS steps from 0 V to<br>COMP = 2.5 V                                                                                |                                  | 75    |       | ns    |                   |  |

|                    | Blank time, CS <sup>(6)</sup>        |                                                                                                                     |                                  |       | 55    |       |                   |  |

|                    | Overcurrent threshold voltage, CS    |                                                                                                                     |                                  | 1.35  | 1.55  | 1.85  | 14                |  |

|                    | COMP-to-CS offset voltage            | CS = 0 V                                                                                                            |                                  | 0.45  | 0.90  | 1.35  | V                 |  |

(1) For UCC3810, adjust  $V_{CC}$  above the start threshold before setting at 10 V.

(2) Ensured by design. Not production tested.

$$f_{OSC} = \frac{4}{R_T \times C_T}$$

(3) Oscillator frequency is twice the output frequency.

$$A = \frac{\Delta V_{COMP}}{\Delta V_{COMP}}$$

(4)

Current sense gain A is defined by:  $\Delta V_{CS}$ ,  $0 \text{ V} \le \text{V}_{CS} \le 0.8 \text{ V}$ . Parameter measured at trip point of latch with FB = 0 V. (5)

CS blank time is measured as the difference between the minimum non-zero on-time and the CS-to-OUT delay. (6)

#### **ELECTRICAL CHARACTERISTICS (continued)**

All parameters are the same for both channels,  $-40^{\circ}C \le T_A \le 85^{\circ}C$  for the UCC2810,  $0^{\circ}C \le T_A \le 70^{\circ}C$  for the UCC3810,  $V_{CC} = 10 \text{ V}$ ;  $R_T = 150 \text{ k}\Omega$ ,  $C_T = 120 \text{ pF}$ ; no load;  $T_A = T_{J_2}$  (unless otherwise specified)

|                 | PARAMETER                                                | TEST C                         | ONDITIONS                | MIN  | TYP  | MAX  | UNIT       |  |  |  |

|-----------------|----------------------------------------------------------|--------------------------------|--------------------------|------|------|------|------------|--|--|--|

| PWM             |                                                          |                                |                          |      |      | ¥    |            |  |  |  |

|                 | Movimum duty ovolo <sup>(2)</sup>                        | R <sub>T</sub> = 150 kΩ,       | C <sub>T</sub> = 120 pF  | 45%  | 49%  | 50%  |            |  |  |  |

|                 | Maximum duty cycle <sup>(2)</sup>                        | $R_T = 30 \text{ k}\Omega,$    | C <sub>T</sub> = 120 pF  | 40%  | 45%  | 48%  |            |  |  |  |

|                 | Minimum on-time                                          | CS = 1.2 V,                    | COMP = 5 V               |      | 130  |      | ns         |  |  |  |

| OUTP            | UT                                                       |                                |                          |      |      | L    |            |  |  |  |

|                 |                                                          | I <sub>OUT</sub> = 20 mA       |                          |      | 0.12 | 0.42 |            |  |  |  |

| V <sub>OL</sub> | Low-level output voltage                                 | I <sub>OUT</sub> = 200 mA      |                          |      | 0.48 | 1.10 |            |  |  |  |

|                 |                                                          | I <sub>OUT</sub> = 20 mA,      | $V_{CC} = 0 V$           |      | 0.7  | 1.2  | V          |  |  |  |

|                 |                                                          | I <sub>OUT</sub> = -20 mA      |                          |      | 0.15 | 0.42 |            |  |  |  |

| V <sub>OH</sub> | High-level output voltage ( $V_{CC} - OUT$ )             | I <sub>OUT</sub> = -200 mA     |                          |      | 1.2  | 2.3  | 2.3        |  |  |  |

| t <sub>R</sub>  | Rise time, OUT                                           | C <sub>OUT</sub> = 1 nF        |                          |      | 20   | 50   | <b>n</b> - |  |  |  |

| t <sub>F</sub>  | Fall time, OUT                                           | C <sub>OUT</sub> = 1 nF        |                          |      | 30   | 60   | ns         |  |  |  |

| UNDE            | RVOLTAGE LOCKOUT (UVLO)                                  |                                |                          |      |      |      |            |  |  |  |

|                 | Start threshold voltage                                  |                                |                          | 9.6  | 11.3 | 13.2 |            |  |  |  |

|                 | Stop threshold voltage                                   |                                |                          | 7.1  | 8.3  | 9.5  | V          |  |  |  |

|                 | Start-to-stop hysteresis                                 |                                |                          | 1.7  | 3.0  | 4.7  |            |  |  |  |

|                 | ENABLE2 input bias current                               | ENABLE2 = 0 V                  |                          | -20  | -35  | -55  | μA         |  |  |  |

|                 | ENABLE2 input threshold voltage                          |                                |                          | 0.80 | 1.53 | 2.00 | V          |  |  |  |

| OVER            | ALL                                                      |                                |                          |      |      |      |            |  |  |  |

|                 | Startup current                                          | V <sub>CC</sub> < Start thresh | old voltage              |      | 0.15 | 0.25 |            |  |  |  |

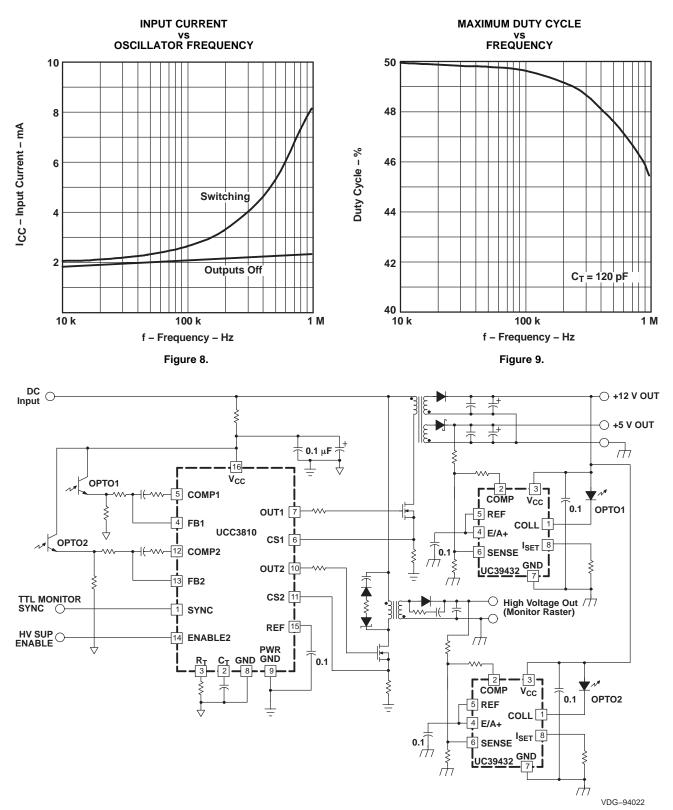

|                 | Operating supply current, outputs off                    | VCC = 10 V,                    | FB = 2.75 V              |      | 2    | 3    |            |  |  |  |

|                 |                                                          | VCC = 10 V,<br>CS = 0 V,       | FB = 0 V,<br>RT = 150 kΩ |      | 3.2  | 5.1  | mA         |  |  |  |

|                 | Operating supply current, outputs on                     | VCC = 10 V,<br>CS = 0 V,       | FB = 0 V,<br>RT = 30 kΩ  |      | 8.5  | 14.5 |            |  |  |  |

|                 | VCC internal zener voltage                               | $I_{CC} = 10 \text{ mA}$       |                          | 11.0 | 12.9 | 14.0 |            |  |  |  |

|                 | VCC internal zener voltage minus start threshold voltage |                                |                          | 0.4  | 1.2  |      | V          |  |  |  |

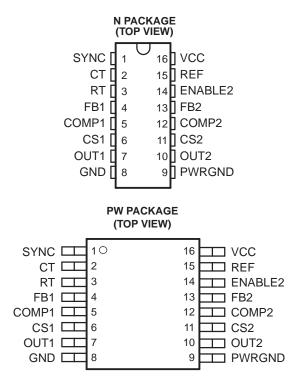

## **DEVICE INFORMATION**

#### **TERMINAL FUNCTIONS**

| TERMINAL |     | 1/0 |                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME     | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| COMP1    | 5   | 0   | Low impodence output of the error amplifiere                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| COMP2    | 12  | 0   | <ul> <li>Low impedance output of the error amplifiers.</li> </ul>                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| CS1      | 6   | I   | Current sense inputs to the PWM comparators. These inputs have leading edge blanking. For                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| CS2      | 11  | I   | most applications, no input filtering is required. Leading edge blanking disconnects the CS inputs from all internal circuits for the first 55 ns of each PWM cycle. When used with very slow diodes or in other applications where the current sense signal is unusually noisy, a small current-sense R-C filter may be required.                                          |  |  |  |  |  |  |

| ст       | 2   | 0   | The timing capacitor of the oscillator. Recommended values of CT are between 100 pF and 1 nF. Connect the timing capacitor directly across CT and GND.                                                                                                                                                                                                                      |  |  |  |  |  |  |

| ENABLE2  | 14  | I   | A logic input which disables PWM 2 when low. This input has no effect on PWM 1. This input is internally pulled high. In most applications it can be left floating. In unusually noisy applications, the input should be bypassed with a 1-nF ceramic capacitor. This input has TTL compatible thresholds.                                                                  |  |  |  |  |  |  |

| FB1      | 4   | I   | The black increases in a discretion in the same second frame                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| FB2      | 13  | I   | The high impedance inverting inputs of the error amplifiers.                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| GND      | 8   | _   | To separate noise from the critical control circuits, this part has two different ground connections:<br>GND and PWRGND. GND and PWRGND must be electrically connected together. However, use<br>care to avoid coupling noise into GND.                                                                                                                                     |  |  |  |  |  |  |

| OUT1     | 7 O |     | The high-current push-pull outputs of the PWM are intended to drive power MOSFET gates                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| OUT2     | 10  | 0   | through a small resistor. This resistor acts as both a current limiting resistor and as a damping impedance to minimize ringing and overshoot.                                                                                                                                                                                                                              |  |  |  |  |  |  |

| PWRGND   | 9   | -   | To separate noise from the critical control circuits, this part has two different ground connections: GND and PWRGND. GND and PWRGND must be electrically connected together.                                                                                                                                                                                               |  |  |  |  |  |  |

| REF      | 15  | 0   | The output of the 5-V reference. Bypass REF to GND with a ceramic capacitor $\geq$ 0.01- $\mu F$ for best performance.                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

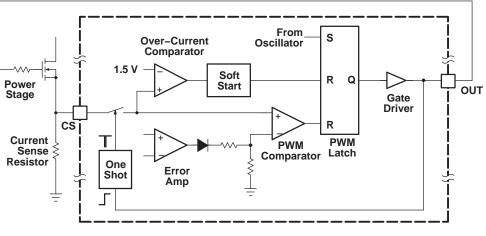

| RT       | 3   | 0   | The oscillator charging current is set by the value of the resistor connected from RT to GND. This pin is regulated to 1 V, but the actual charging current is 10 V/RT. Recommended values of RT are between 10 k $\Omega$ and 470 k $\Omega$ . For a given frequency, higher timing resistors give higher maximum duty cycle and slightly lower overall power consumption. |  |  |  |  |  |  |

| SYNC     | 1   | I   | This logic input can be used to synchronize the oscillator to a free running oscillator in another part. This pin is edge triggered with TTL thresholds, and requires at least a 10-ns-wide pulse. If unused, this pin can be grounded, open circuited, or connected to REF.                                                                                                |  |  |  |  |  |  |

| VCC      | 16  | I   | The power input to the device. This pin supplies current to all functions including the high current output stages and the precision reference. Therefore, it is critical that VCC be directly bypassed to PWRGND with an 0.1-µF ceramic capacitor.                                                                                                                         |  |  |  |  |  |  |

## APPLICATION INFORMATION

## **TIMING RESISTOR**

Supply current decreases with increased  $R_T$  by the relationship:

$$\Delta I_{CC} = \frac{11V}{R_T}$$

For more information, see the detailed oscillator block diagram.

## LEADING EDGE BLANKING AND CURRENT SENSE

Figure 1 shows how an external power stage is connected to the UCC3810. The gate of an external power N-channel MOSFET is connected to OUT through a small current-limiting resistor. For most applications, a  $10-\Omega$  resistor is adequate to limit peak current and also practical at damping resonances between the gate driver and the MOSFET input reactance. Long gate lead length increases gate capacitance and mandates a higher series gate resistor to damp the R-L-C tank formed by the lead, the MOSFET input reactance, and the device's driver output resistance.

The UCC3810 features internal leading edge blanking of the current-sense signal on both current sense inputs. The blank time starts when OUT rises and continues for 55 ns. During that 55 ns period, the signal on CS is ignored. For most PWM applications, this means that the CS input can be connected to the current-sense resistor as shown in Figure 1. However, high speed grounding practices and short lead lengths are still required for good performance.

Figure 1. Detailed Block Diagram

## OSCILLATOR

The UCC3810 oscillator generates a sawtooth wave at CT. The sawtooth rise time is set by the resistor from RT to GND. Since  $R_T$  is biased at 1 V, the current through  $R_T$  is 1 V/ $R_T$ . The actual charging current is 10 times higher. The fall time is set by an internal transistor on-resistance of approximately 100  $\Omega$ . During the fall time, all outputs are off and the maximum duty cycle is reduced to below 50%. Larger timing capacitors increase the discharge time and reduce frequency. However, the percentage maximum duty cycle is only a function of the timing resistor  $R_T$ , and the internal 100- $\Omega$  discharge resistance.

#### ERROR AMPLIFIER OUTPUT STAGE

The UCC3810 error amplifiers are operational amplifiers with low-output resistance and high-input resistance. The output stage of one error amplifier is shown in Figure 3. This output stage allows the error amplifier output to swing close to GND and as high as one diode drop below 5 V with little loss in amplifier performance.

# **APPLICATION INFORMATION (continued)**

COMP

## **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS (continued)**

Texas

STRUMENTS

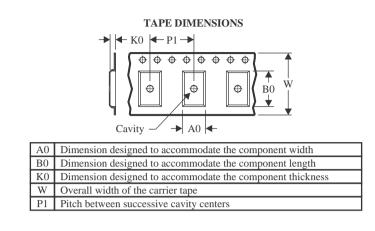

## TAPE AND REEL INFORMATION

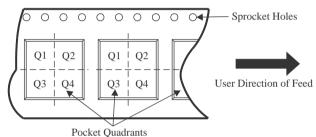

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |      |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | -    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| UCC2810DWTR                 | SOIC | DW                 | 16 | 2000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

| UCC3810DWTR                 | SOIC | DW                 | 16 | 2000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

www.ti.com

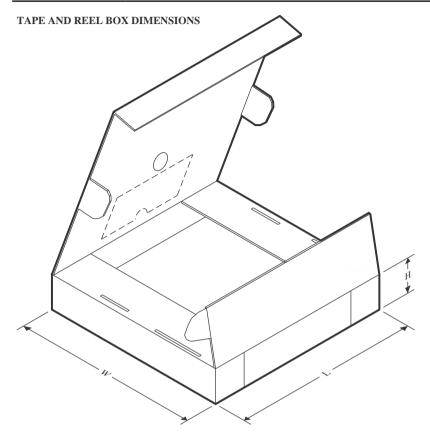

# PACKAGE MATERIALS INFORMATION

3-Jun-2022

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCC2810DWTR | SOIC         | DW              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

| UCC3810DWTR | SOIC         | DW              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

## TEXAS INSTRUMENTS

www.ti.com

3-Jun-2022

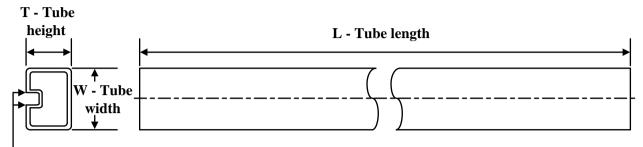

# TUBE

# - B - Alignment groove width

#### \*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| UCC2810DW   | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| UCC2810DWG4 | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| UCC2810N    | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| UCC2810NG4  | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| UCC3810DW   | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| UCC3810N    | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated