MSP430FR2111, MSP430FR2110, MSP430FR2100, MSP430FR2000

SLASE78E - AUGUST 2016 - REVISED JUNE 2021

# MSP430FR21xx, MSP430FR2000 Mixed-Signal Microcontrollers

# 1 Features

- Embedded microcontroller

- 16-bit RISC architecture up to 16 MHz

- Wide supply voltage range from 3.6 V down to 1.8 V (minimum supply voltage is restricted by SVS levels, see the SVS specifications)

- Optimized low-power modes (at 3 V)

- Active mode: 120 µA/MHz

- Standby

- LPM3.5 with VLO: 1 μA

- Real-time clock (RTC) counter (LPM3.5 with 32768-Hz crystal): 1 µA

- Shutdown (LPM4.5): 34 nA without SVS

- High-performance analog

- 8-channel 10-bit analog-to-digital converter (ADC)

- Integrated temperature sensor

- Internal 1.5-V reference

- Sample-and-hold 200 ksps

- Enhanced comparator (eCOMP)

- Integrated 6-bit DAC as reference voltage

- Programmable hysteresis

- Configurable high-power and low-power modes

- Low-power ferroelectric RAM (FRAM)

- Up to 3.75KB of nonvolatile memory

- Built-in error correction code (ECC)

- Configurable write protection

- Unified memory of program, constants, and storage

- 10<sup>15</sup> write cycle endurance

- Radiation resistant and nonmagnetic

- Intelligent digital peripherals

- One 16-bit timer with three capture/compare registers (Timer B3)

- One 16-bit counter-only RTC counter

- 16-bit cyclic redundancy checker (CRC)

- Enhanced serial communications

- Enhanced USCI A (eUSCI A) supports UART, IrDA. and SPI

- Clock system (CS)

- On-chip 32-kHz RC oscillator (REFO)

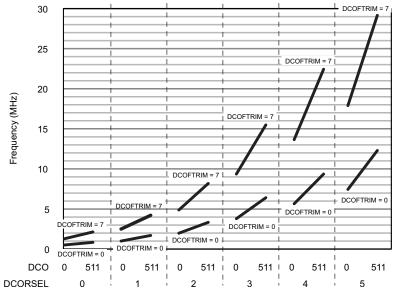

- On-chip 16-MHz digitally controlled oscillator (DCO) with frequency-locked loop (FLL)

- ±1% accuracy with on-chip reference at room temperature

- On-chip very-low-frequency 10-kHz oscillator (VLO)

- On-chip high-frequency modulation oscillator (MODOSC)

- External 32-kHz crystal oscillator (LFXT)

- Programmable MCLK prescalar of 1 to 128

- SMCLK derived from MCLK with programmable prescalar of 1, 2, 4, or 8

- General input/output and pin functionality

- 12 I/Os on 16-pin package

- 8 interrupt pins (4 pins of P1 and 4 pins of P2) can wake MCU from LPMs

- All I/Os are capacitive touch I/Os

- Development tools and software (also see Tools and Software)

- Free professional development environments

- Development kits

- MSP-TS430PW20

- MSP-FET430U20

- MSP-EXP430FR2311

- MSP-EXP430FR4133

- Family members (also see Device Comparison)

- MSP430FR2111: 3.75KB of program FRAM, 1KB of RAM

- MSP430FR2110: 2KB of program FRAM, 1KB of RAM

- MSP430FR2100: 1KB of program FRAM, 512 bytes of RAM

- MSP430FR2000: 0.5KB of program FRAM, 512 bytes of RAM

- Package options

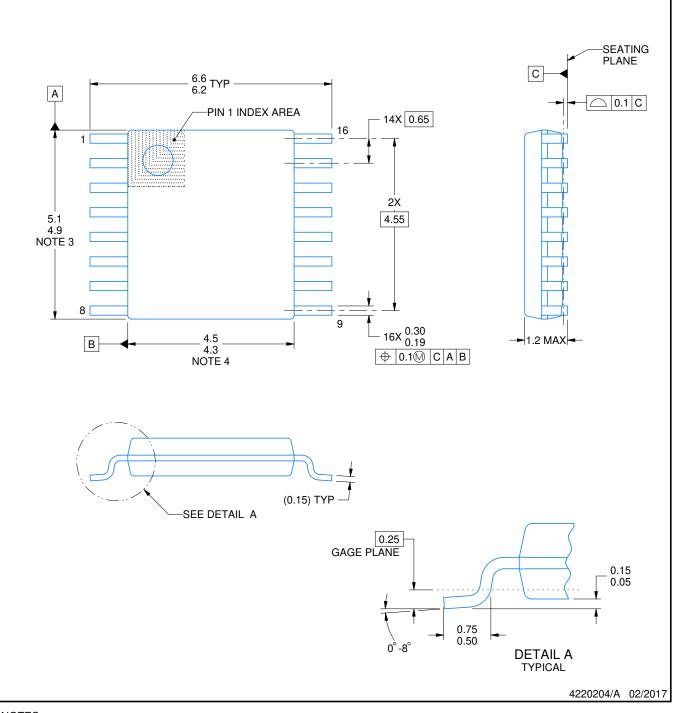

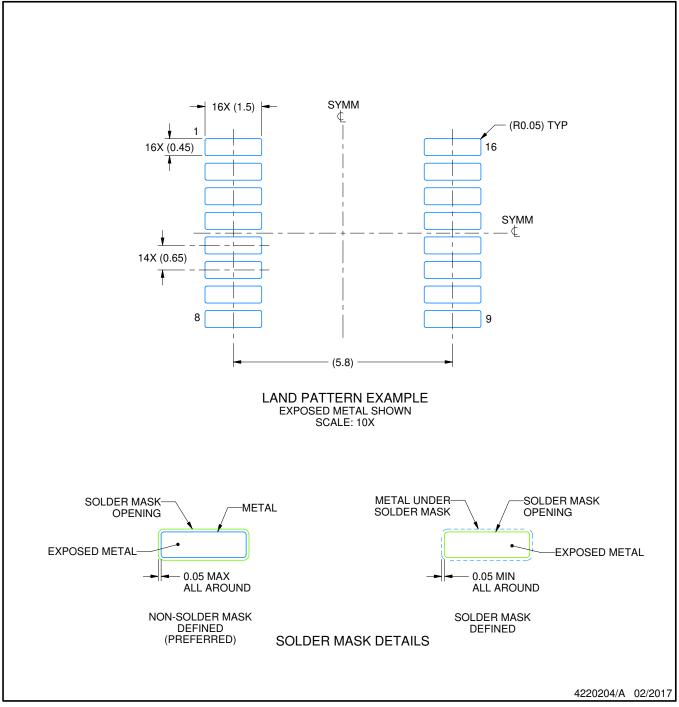

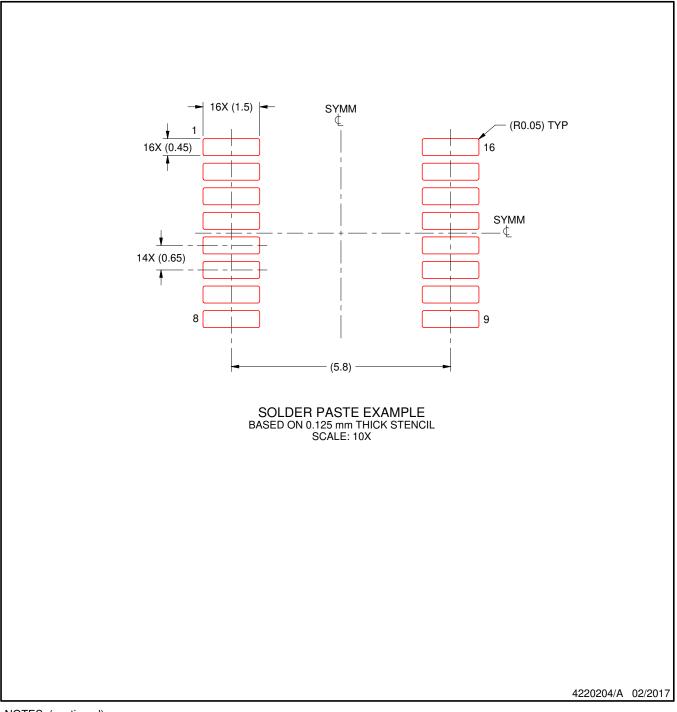

- 16-pin: TSSOP (PW16)

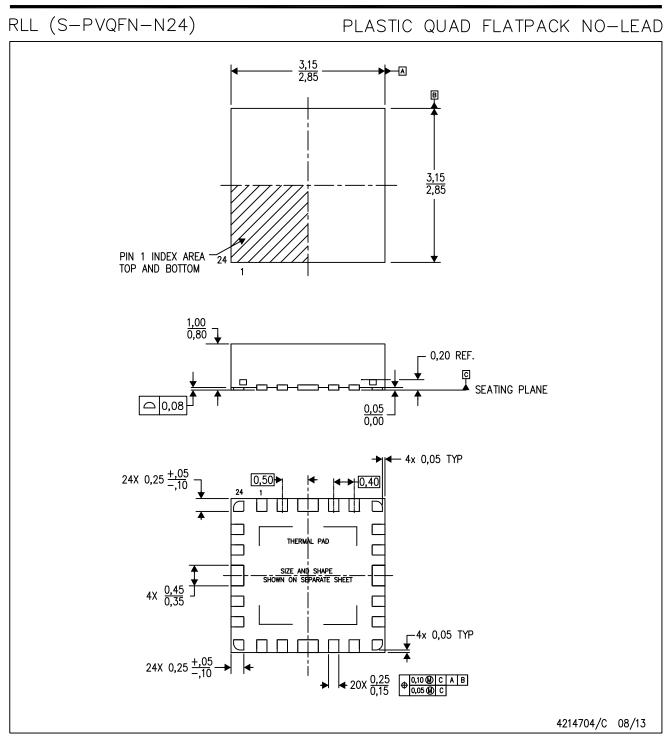

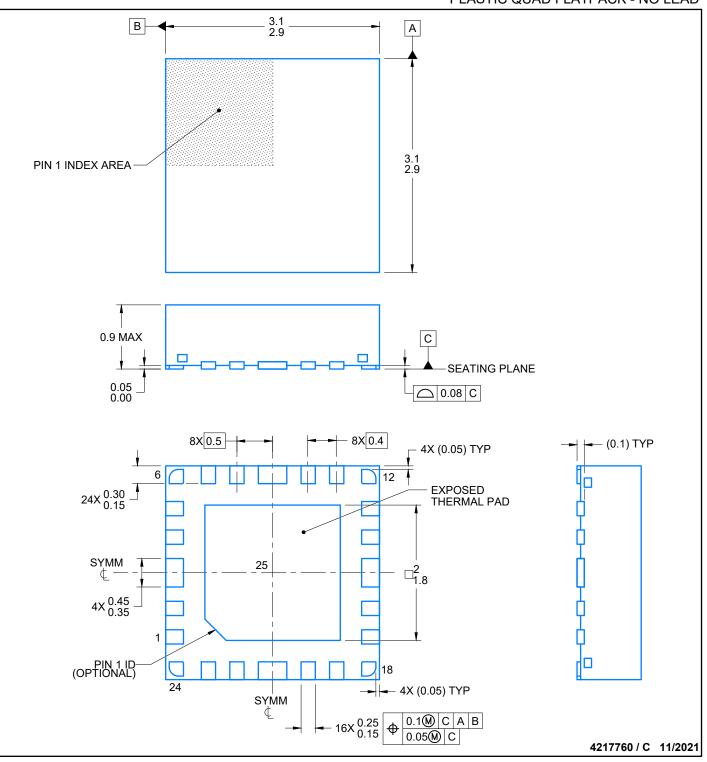

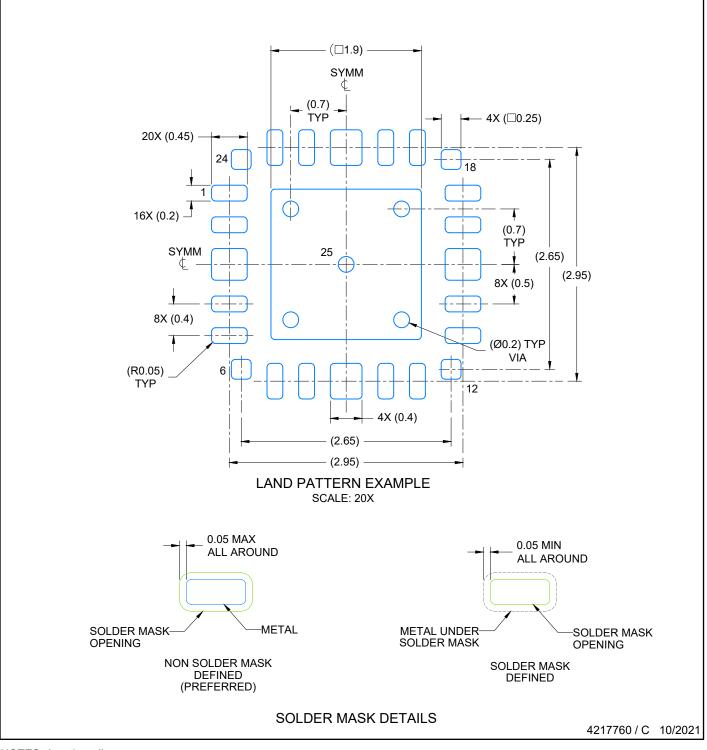

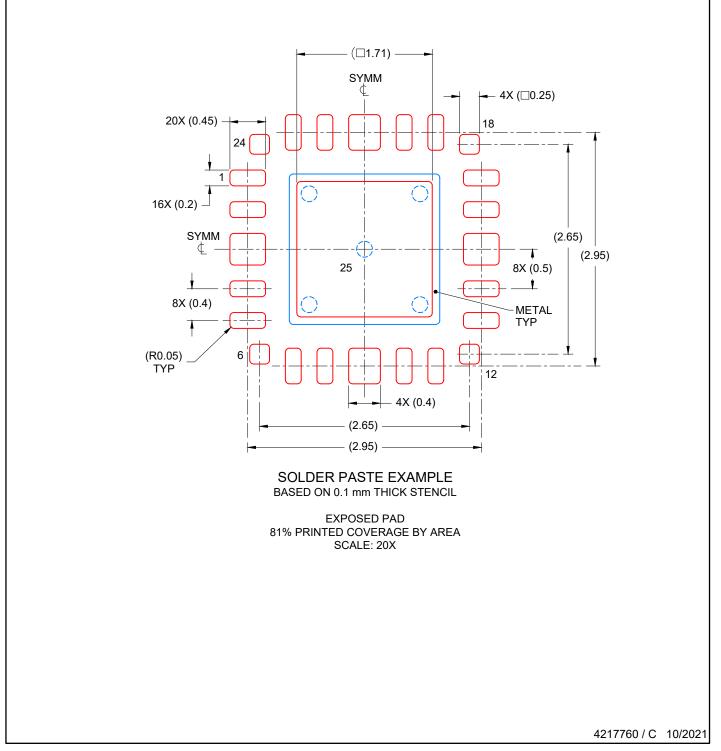

- 24-pin: VQFN (RLL)

# 2 Applications

- Appliance battery packs

- Smoke and heat detectors

- Door and window sensors

- Lighting sensors

- Power monitoring

- Personal care electronics

- Portable health and fitness devices

# **3 Description**

MSP430FR2000 and MSP430FR21xx devices are part of the MSP430<sup>™</sup> microcontroller (MCU) value line sensing portfolio. This ultra-low-power, low-cost MCU family offers memory sizes from 0.5KB to 4KB of FRAM unified memory with several package options including a small 3-mm×3-mm VQFN package. The architecture, FRAM, and integrated peripherals, combined with extensive low-power modes, are optimized to achieve extended battery life in portable, battery-powered sensing applications. MSP430FR2000 and MSP430FR21xx devices offer a migration path for 8-bit designs to gain additional features and functionality from peripheral integration and the data-logging and low-power benefits of FRAM. Additionally, existing designs using MSP430G2x MCUs can migrate to the MSP430FR2000 and MSP430F21xx family to increase performance and get the benefits of FRAM.

The MSP430FR2000 and MSP430FR21xx MCUs feature a powerful 16-bit RISC CPU, 16-bit registers, and a constant generator that contribute to maximum code efficiency. The digitally controlled oscillator (DCO) also allows the device to wake up from low-power modes to active mode typically in less than 10 µs. The feature set of this MCU meets the needs of applications ranging from appliance battery packs and battery monitoring to smoke detectors and fitness accessories.

The MSP ultra-low-power (ULP) FRAM microcontroller platform combines uniquely embedded FRAM and a holistic ultra-low-power system architecture, allowing system designers to increase performance while lowering energy consumption. FRAM technology combines the low-energy fast writes, flexibility, and endurance of RAM with the nonvolatile behavior of flash.

MSP430FR2000 and MSP430FR21x MCUs are supported by an extensive hardware and software ecosystem with reference designs and code examples to get your design started quickly. Development kits include the MSP-EXP430FR2311 and MSP430FR4133 LaunchPad<sup>™</sup> development kit and the MSP-TS430PW20 20-pin target development board. TI also provides free MSP430Ware<sup>™</sup> software, which is available as a component of Code Composer Studio<sup>™</sup> IDE desktop and cloud versions within TI Resource Explorer. MSP430 MCUs are also supported by extensive online collateral, such as our housekeeping example series, MSP Academy training, and online support through the TI E2E<sup>™</sup> support forums.

For complete module descriptions, see the MSP430FR4xx and MSP430FR2xx Family User's Guide.

| PART NUMBER <sup>(1)</sup> | PACKAGE    | BODY SIZE <sup>(2)</sup> |  |  |

|----------------------------|------------|--------------------------|--|--|

| MSP430FR2111IPW16          |            |                          |  |  |

| MSP430FR2110IPW16          | TSSOP (16) | 5 mm × 4 4 mm            |  |  |

| MSP430FR2100IPW16          | 1350P (10) | 5 1111 ^ 4.4 1111        |  |  |

| MSP430FR2000IPW16          |            |                          |  |  |

| MSP430FR2111IRLL           |            |                          |  |  |

| MSP430FR2110IRLL           |            | 3 mm × 3 mm              |  |  |

| MSP430FR2100IRLL           | VQFN (24)  | 5 11111 * 5 11111        |  |  |

| MSP430FR2000IRLL           |            |                          |  |  |

**Device Information**

(1) For the most current part, package, and ordering information, see the *Package Option Addendum* in Section 12, or see the TI website at www.ti.com.

(2) The sizes shown here are approximations. For the package dimensions with tolerances, see the *Mechanical Data* in Section 12.

# CAUTION

System-level ESD protection must be applied in compliance with the device-level ESD specification to prevent electrical overstress or disturbing of data or code memory. See MSP430<sup>™</sup> System-Level ESD Considerations for more information.

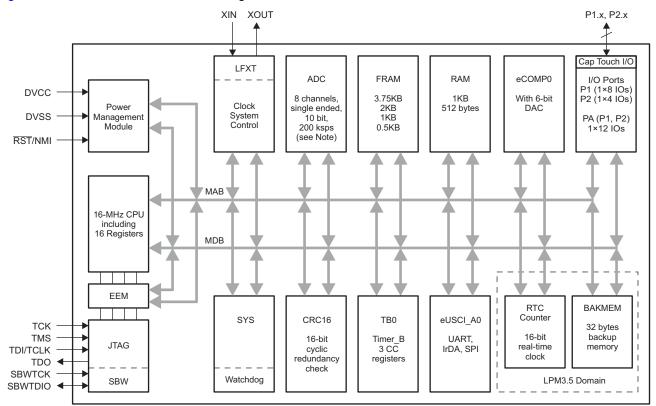

# **4** Functional Block Diagram

Figure 4-1 shows the functional block diagram.

NOTE: The ADC is not available on the MSP430FR2000 device.

#### Figure 4-1. Functional Block Diagram

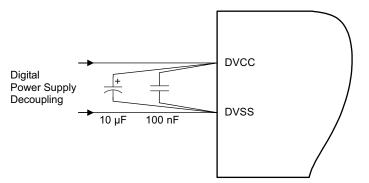

- The device has one main power pair of DVCC and DVSS that supplies both digital and analog modules. Recommended bypass and decoupling capacitors are 4.7 μF to 10 μF and 0.1 μF, respectively, with ±5% accuracy.

- Four pins of P1 and four pins of P2 feature the pin-interrupt function and can wake the MCU from all LPMs, including LPM4, LPM3.5, and LPM4.5.

- The Timer\_B3 has three capture/compare registers. Only CCR1 and CCR2 are externally connected. CCR0 registers can be used only for internal period timing and interrupt generation.

- In LPM3.5, the RTC counter and backup memory can be functional while the rest of peripherals are off.

- All general-purpose I/Os can be configured as Capacitive Touch I/Os.

# **Table of Contents**

| 1 | Features1                                              |

|---|--------------------------------------------------------|

| 2 | Applications1                                          |

|   | Description2                                           |

| 4 | Functional Block Diagram3                              |

|   | Revision History5                                      |

| 6 | Device Comparison7                                     |

|   | 6.1 Related Products7                                  |

| 7 | Terminal Configuration and Functions8                  |

|   | 7.1 Pin Diagrams8                                      |

|   | 7.2 Pin Attributes9                                    |

|   | 7.3 Signal Descriptions 11                             |

|   | 7.4 Pin Multiplexing13                                 |

|   | 7.5 Connection of Unused Pins 13                       |

|   | 7.6 Buffer Type13                                      |

| 8 | Specifications14                                       |

|   | 8.1 Absolute Maximum Ratings14                         |

|   | 8.2 ESD Ratings14                                      |

|   | 8.3 Recommended Operating Conditions14                 |

|   | 8.4 Active Mode Supply Current Into $V_{CC}$ Excluding |

|   | External Current                                       |

|   | 8.5 Active Mode Supply Current Per MHz                 |

|   | 8.6 Low-Power Mode LPM0 Supply Currents Into           |

|   | V <sub>CC</sub> Excluding External Current             |

|   | 8.7 Low-Power Mode LPM3, LPM4 Supply Currents          |

|   | (Into $V_{CC}$ ) Excluding External Current            |

|   | 8.8 Low-Power Mode LPMx.5 Supply Currents (Into        |

|   | V <sub>CC</sub> ) Excluding External Current           |

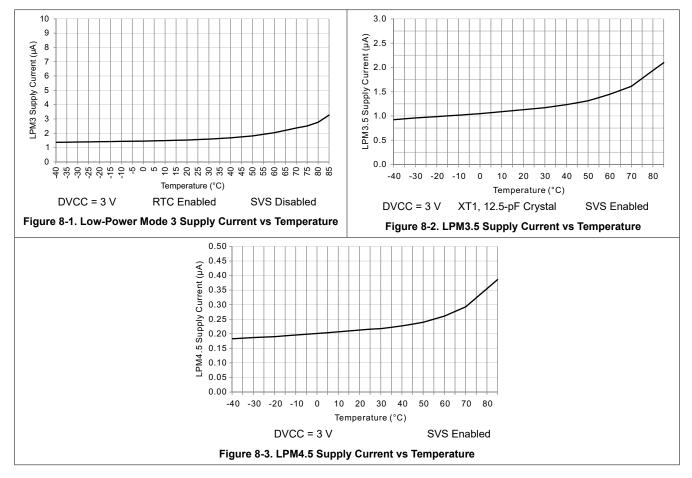

|   | 8.9 Typical Characteristics – LPM Supply Currents18    |

|   | 8.10 Current Consumption Per Module                    |

|   | 8.11 Thermal Resistance Characteristics                |

|   | 8.12 Timing and Switching Characteristics              |

| 9 Detailed Description                         | 38 |

|------------------------------------------------|----|

| 9.1 Overview                                   | 38 |

| 9.2 CPU                                        | 38 |

| 9.3 Operating Modes                            | 38 |

| 9.4 Interrupt Vector Addresses                 | 40 |

| 9.5 Memory Organization                        | 41 |

| 9.6 Bootloader (BSL)                           | 41 |

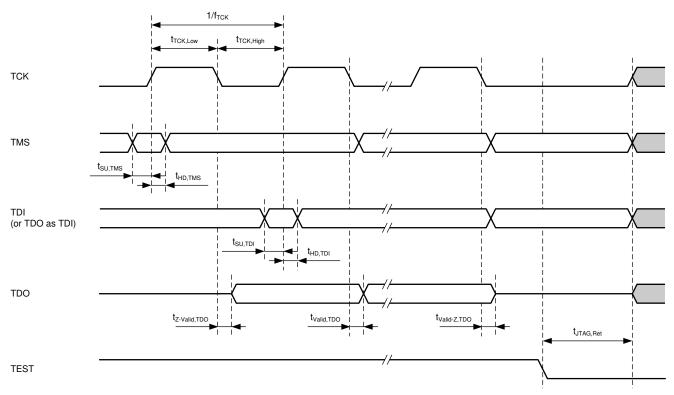

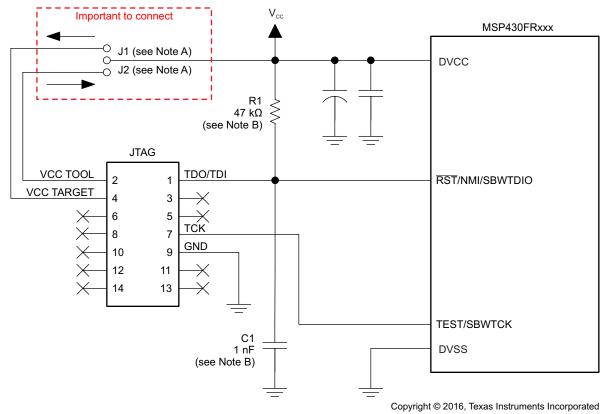

| 9.7 JTAG Standard Interface                    | 41 |

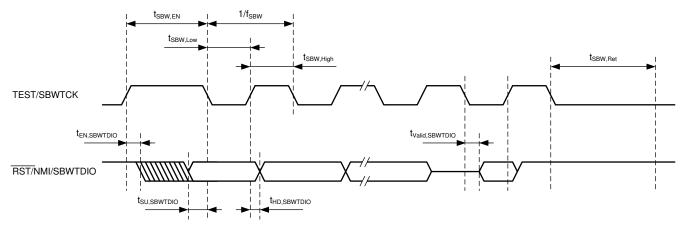

| 9.8 Spy-Bi-Wire Interface (SBW)                | 42 |

| 9.9 FRAM                                       | 42 |

| 9.10 Memory Protection                         | 42 |

| 9.11 Peripherals                               | 42 |

| 9.12 Device Descriptors (TLV)                  |    |

| 9.13 Identification                            |    |

| 10 Applications, Implementation, and Layout    | 62 |

| 10.1 Device Connection and Layout Fundamentals | 62 |

| 10.2 Peripheral- and Interface-Specific Design |    |

| Information                                    |    |

| 10.3 Typical Applications                      |    |

| 11 Device and Documentation Support            | 67 |

| 11.1 Getting Started                           | 67 |

| 11.2 Device Nomenclature                       |    |

| 11.3 Tools and Software                        | 68 |

| 11.4 Documentation Support                     |    |

| 11.5 Support Resources                         | 71 |

| 11.6 Trademarks                                |    |

| 11.7 Electrostatic Discharge Caution           | 71 |

| 11.8 Glossary                                  | 71 |

| 12 Mechanical, Packaging, and Orderable        |    |

| Information                                    | 72 |

# **5** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from revision D to revision E

| C | hanges from December 11, 2019 to June 2, 2021 Parallel Paralle |                 |  |  |  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| • | Updated the numbering format for tables, figures, and cross references throughout the document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1               |  |  |  |

| • | Updated Section 3, Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <mark>2</mark>  |  |  |  |

| • | Updated Section 6.1, Related Products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7               |  |  |  |

|   | Added a note about the specifications for the 1.5-V internal reference in Section 8.12.5, VREF+ Built-in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |  |  |  |

|   | Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <mark>27</mark> |  |  |  |

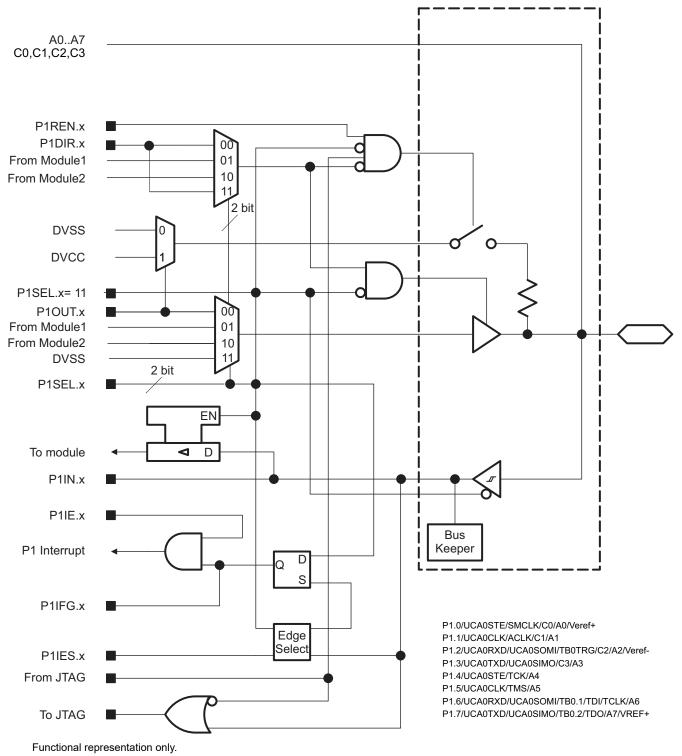

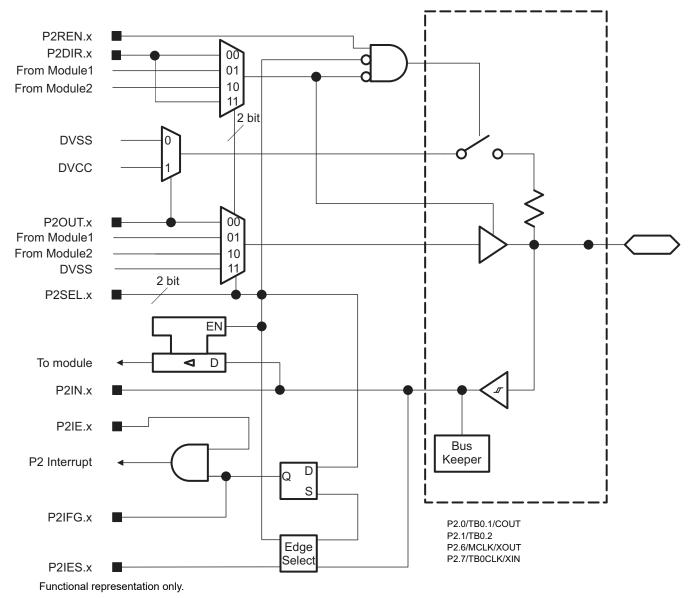

| • | Added inverter to Schmitt-trigger enable in Figure 9-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <mark>56</mark> |  |  |  |

#### Changes from revision C to revision D

| Cł | nanges from August 30, 2018 to December 10, 2019                                                                                                                                                                                     | Page      |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| •  | Changed the note that begins "Supply voltage changes faster than 0.2 V/µs can trigger a BOR reset" i<br>Section 8.3, Recommended Operating Conditions                                                                                | in<br>14  |

| •  | Added the note that begins "TI recommends that power to the DVCC pin must not exceed the limits" in                                                                                                                                  |           |

|    | Section 8.3, Recommended Operating Conditions                                                                                                                                                                                        | 14        |

| •  | Added the note that begins "A capacitor tolerance of ±20% or better is required" in Section 8.3,                                                                                                                                     |           |

|    | Recommended Operating Conditions                                                                                                                                                                                                     | 14        |

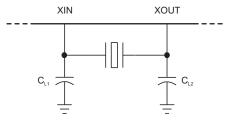

| •  | Added the note "See MSP430 32-kHz Crystal Oscillators for details on crystal section, layout, and testin Section 8.12.3.1, XT1 Crystal Oscillator (Low Frequency)                                                                    |           |

| •  | Changed the note that begins "Requires external capacitors at both terminals" in Section 8.12.3.1, XT Crystal Oscillator (Low Frequency)                                                                                             | 1         |

| •  | Added the t <sub>(int)</sub> parameter in Section 8.12.4.1, <i>Digital Inputs</i>                                                                                                                                                    |           |

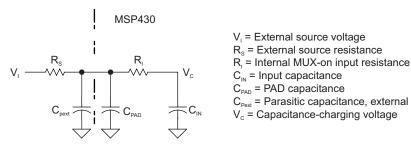

| •  | Changed the parameter symbol from R <sub>I</sub> to R <sub>I,MUX</sub> in Section 8.12.8.1, ADC, Power Supply and Input Rate Conditions                                                                                              | nge<br>32 |

| •  | Corrected the test conditions for the R <sub>I,MUX</sub> parameter in Section 8.12.8.1, ADC, Power Supply and Input                                                                                                                  | ıt        |

|    | Range Conditions                                                                                                                                                                                                                     | 32        |

| •  | Added R <sub>I,Misc</sub> TYP value of 34 kΩ in Section 8.12.8.1, <i>ADC, Power Supply and Input Range Conditions</i>                                                                                                                |           |

| •  | Added t <sub>CONVERT</sub> for external ADCCLK source in Section 8.12.8.2, ADC, 10-Bit Timing Parameters                                                                                                                             |           |

| •  | Added formula for R <sub>I</sub> in Section 8.12.8.2, ADC, 10-Bit Timing Parameters                                                                                                                                                  |           |

| •  | Added the note that begins " $t_{Sample} = ln(2^{n+1}) \times \tau$ " in Section 8.12.8.2, ADC, 10-Bit Timing Parameters<br>Removed the description of "±3°C" in table note that starts "The device descriptor structure" of Section |           |

| •  | 8.12.8.3, ADC, 10-Bit Linearity Parameters                                                                                                                                                                                           |           |

| •  | Corrected bitfield from IRDSEL to IRDSSEL in Section 9.11.8, <i>Timers (Timer0_B3)</i> , in the description th                                                                                                                       |           |

|    | starts "The interconnection of Timer0 B3 "                                                                                                                                                                                           |           |

| •  | Corrected the ADCINCHx column heading in Table 9-14, ADC Channel Connections                                                                                                                                                         |           |

| •  | Added P1SELC information in Table 9-26, Port P1, P2 Registers (Base Address: 0200h)                                                                                                                                                  |           |

| •  | Added P2SELC information in Table 9-26, Port P1, P2 Registers (Base Address: 0200h)                                                                                                                                                  |           |

#### Changes from revision B to revision C

| Cł | nanges from July 14, 2017 to August 29, 2018                                                                  | Page    |

|----|---------------------------------------------------------------------------------------------------------------|---------|

| •  | Added note to V <sub>SVSH-</sub> and V <sub>SVSH+</sub> parameters in Section 8.12.1.1, PMM, SVS and BOR      | 20      |

| •  | Added the note "Controlled by the RTCCKSEL bit in the SYSCFG2 register" on Table 9-7, <i>Clock Distrib</i> 43 | ution . |

| •  | Changed 1 µF capacitor to 10 µF in Figure 10-1, Power Supply Decoupling                                       | 62      |

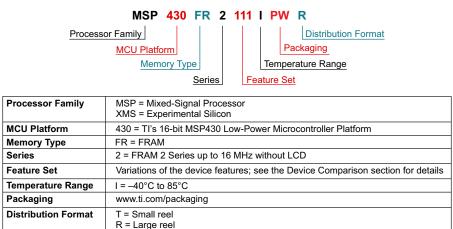

| •  | Updated text and figure in Section 11.2, Device Nomenclature                                                  | 67      |

# MSP430FR2111, MSP430FR2110, MSP430FR2100, MSP430FR2000 SLASE78E – AUGUST 2016 – REVISED JUNE 2021

Changes from revision A to revision B

# Changes from August 13, 2016 to July 13, 2017

| C | hanges from August 13, 2016 to July 13, 2017                                                           | Page              |

|---|--------------------------------------------------------------------------------------------------------|-------------------|

| • | Added MSP430FR2100 and MSP430FR2000 devices.                                                           | 1                 |

| • | Rearranged items in Section 1, Features                                                                | 1                 |

| • | Corrected the package family for the RLL package throughout document (changed QFN to VQFN)             | 1                 |

| • | Upated list of applications in Section 2                                                               |                   |

| • | Updated Section 3, Description                                                                         | 2                 |

| • | Corrected number of bits in port P1 in Figure 4-1, Functional Block Diagram                            | 3                 |

| • | Updated the note that starts "This is the remapped functionality controlled by the TBRMP bit" in Table | <b>7-2</b> ,      |

|   | Signal Descriptions                                                                                    | 11                |

| • | Updated the note that starts "This is the remapped functionality controlled by the USCIARMP bit" in Ta | able              |

|   | 7-2, Signal Descriptions                                                                               | 11                |

| • | Removed former Figure 5-2, Low-Power Mode 3 Supply Current vs Temperature                              | 18                |

| • | Updated notes on Section 8.11, Thermal Resistance Characteristics                                      | 19                |

| • | Changed the entry for eUSCI_A in the LPM3 column from Off to Optional in Table 9-1, Operating Modes    | 3 <mark>38</mark> |

| • | Updated the note that starts "This is the remapped functionality controlled by the USCIARMP bit" in Ta | able              |

|   | 9-11, eUSCI Pin Configurations                                                                         |                   |

| • | Updated the note that starts "This is the remapped functionality controlled by the TBRMP bit" in Table | 9-12,             |

|   | Timer0_B3 Signal Connections                                                                           |                   |

| • | Removed SYSBERRIV register (not supported) from Table 9-21, SYS Registers                              |                   |

| • | Updated descriptions of "Design Kits and Evaluation Modules" in Section 11.3, Tools and Software       | <mark>68</mark>   |

|   |                                                                                                        |                   |

Changes from initial release to revision A

| Cł | nanges from August 11, 2016 to August 12, 2016                  | Page |

|----|-----------------------------------------------------------------|------|

| •  | Changed document status from PRODUCT PREVIEW to PRODUCTION DATA | 1    |

# 6 Device Comparison

| Table 6-1. Device Comparison     |                          |                 |                        |         |                        |        |     |               |

|----------------------------------|--------------------------|-----------------|------------------------|---------|------------------------|--------|-----|---------------|

| <b>DEVICE</b> <sup>(1)</sup> (2) | PROGRAM FRAM<br>(Kbytes) | SRAM<br>(Bytes) | ТВ0                    | eUSCI_A | 10-BIT ADC<br>CHANNELS | eCOMP0 | I/O | PACKAGE       |

| MSP430FR2111IPW16                | 3.75                     | 1024            | 3 × CCR <sup>(3)</sup> | 1       | 8                      | 1      | 12  | 16 PW (TSSOP) |

| MSP430FR2110IPW16                | 2                        | 1024            | 3 × CCR <sup>(3)</sup> | 1       | 8                      | 1      | 12  | 16 PW (TSSOP) |

| MSP430FR2100IPW16                | 1                        | 512             | 3 × CCR <sup>(3)</sup> | 1       | 8                      | 1      | 12  | 16 PW (TSSOP) |

| MSP430FR2000IPW16                | 0.5                      | 512             | 3 × CCR <sup>(3)</sup> | 1       | -                      | 1      | 12  | 16 PW (TSSOP) |

| MSP430FR2111IRLL                 | 3.75                     | 1024            | 3 × CCR <sup>(3)</sup> | 1       | 8                      | 1      | 12  | 24 RLL (VQFN) |

| MSP430FR2110IRLL                 | 2                        | 1024            | 3 × CCR <sup>(3)</sup> | 1       | 8                      | 1      | 12  | 24 RLL (VQFN) |

| MSP430FR2100IRLL                 | 1                        | 512             | 3 × CCR <sup>(3)</sup> | 1       | 8                      | 1      | 12  | 24 RLL (VQFN) |

| MSP430FR2000IRLL                 | 0.5                      | 512             | 3 × CCR <sup>(3)</sup> | 1       | -                      | 1      | 12  | 24 RLL (VQFN) |

Table 6-1 summarizes the features of the available family members.

(1) For the most current device, package, and ordering information, see the *Package Option Addendum* in Section 12, or see the TI website at www.ti.com.

(2) Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/ packaging

(3) A CCR register is a configurable register that provides internal and external capture or compare inputs, or internal and external PWM outputs.

## **6.1 Related Products**

For information about other devices in this family of products or related products, see the following links.

#### Overview of Microcontrollers (MCUs) & processors

Our diverse portfolio of 16- and 32-bit microcontrollers (MCUs) with real-time control capabilities and highprecision analog integration are optimized for industrial and automotive applications. Backed by decades of expertise and innovative hardware and software solutions, our MCUs can meet the needs of any design and budget.

#### Overview of MSP430<sup>™</sup> microcontrollers (MCUs)

Our 16-bit MSP430<sup>™</sup> microcontrollers (MCUs) provide affordable solutions for all applications. Our leadership in integrated precision analog enables designers to enhance system performance and lower system costs. Designers can find a cost-effective MCU within the broad MSP430 portfolio of over 2000 devices for virtually any need. Get started quickly and reduce time to market with our simplified tools, software, and best-in-class support.

#### Reference designs

Find reference designs leveraging the best in TI technology – from analog and power management to embedded processors.

# 7 Terminal Configuration and Functions 7.1 Pin Diagrams

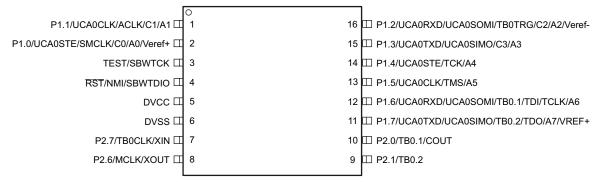

Figure 7-1 shows the pinout of the 16-pin PW package.

The ADC (signals A0 to A7, Veref+, and Veref-) is not available on the MSP430FR2000 device.

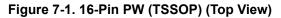

Figure 7-2 shows the pinout of the 24-pin RLL package.

The ADC (signals A0 to A7, Veref+, and Veref-) is not available on the MSP430FR2000 device.

Figure 7-2. 24-Pin RLL (VQFN) (Top View)

Copyright © 2021 Texas Instruments Incorporated

# 7.2 Pin Attributes

Table 7-1 lists the attributes of all pins.

| PIN NU | MBER |                                | SIGNAL              |                            |              | RESET STATE              |

|--------|------|--------------------------------|---------------------|----------------------------|--------------|--------------------------|

| PW16   | RLL  | SIGNAL NAME <sup>(1) (2)</sup> | TYPE <sup>(3)</sup> | BUFFER TYPE <sup>(4)</sup> | POWER SOURCE | AFTER BOR <sup>(5)</sup> |

|        |      | P1.1 (RD)                      | I/O                 | LVCMOS                     | DVCC         | OFF                      |

|        |      | UCA0CLK                        | I/O                 | LVCMOS                     | DVCC         | _                        |

| 1      | 23   | ACLK                           | 0                   | LVCMOS                     | DVCC         | _                        |

|        |      | C1                             | I                   | Analog                     | DVCC         | _                        |

|        |      | A1 <sup>(6)</sup>              | I                   | Analog                     | DVCC         | _                        |

|        |      | P1.0 (RD)                      | I/O                 | LVCMOS                     | DVCC         | OFF                      |

|        |      | UCA0STE                        | I/O                 | LVCMOS                     | DVCC         | -                        |

| 0      | 20   | SMCLK                          | 0                   | LVCMOS                     | DVCC         | _                        |

| 2      | 20   | C0                             | I                   | Analog                     | DVCC         | _                        |

|        |      | A0 <sup>(6)</sup>              | I                   | Analog                     | DVCC         | _                        |

|        |      | Veref+ <sup>(6)</sup>          | I                   | Power                      | DVCC         | _                        |

| 2      | 4    | TEST (RD)                      | I                   | LVCMOS                     | DVCC         | OFF                      |

| 3      | 1    | SBWTCK                         | I                   | LVCMOS                     | DVCC         | _                        |

|        |      | RST (RD)                       | I/O                 | LVCMOS                     | DVCC         | OFF                      |

| 4      | 2    | NMI                            | I                   | LVCMOS                     | DVCC         | _                        |

|        |      | SBWTDIO                        | I/O                 | LVCMOS                     | DVCC         | _                        |

| 5      | 3    | DVCC                           | Р                   | Power                      | DVCC         | N/A                      |

| 6      | 4    | DVSS                           | Р                   | Power                      | DVCC         | N/A                      |

|        |      | P2.7 (RD)                      | I/O                 | LVCMOS                     | DVCC         | OFF                      |

| 7      | 5    | TB0CLK                         | I                   | LVCMOS                     | DVCC         | _                        |

|        |      | XIN                            | I                   | LVCMOS                     | DVCC         | _                        |

|        |      | P2.6 (RD)                      | I/O                 | LVCMOS                     | DVCC         | OFF                      |

| 8      | 7    | MCLK                           | 0                   | LVCMOS                     | DVCC         | _                        |

|        |      | XOUT                           | 0                   | LVCMOS                     | DVCC         | _                        |

| 9      |      | P2.1(RD)                       | I/O                 | LVCMOS                     | DVCC         | OFF                      |

| 9      | 11   | TB0.2                          | I/O                 | LVCMOS                     | DVCC         | _                        |

|        |      | P2.0 (RD)                      | I/O                 | LVCMOS                     | DVCC         | OFF                      |

| 10     | 8    | TB0.1                          | I/O                 | LVCMOS                     | DVCC         | _                        |

|        |      | COUT                           | 0                   | LVCMOS                     | DVCC         | _                        |

|        |      | P1.7 (RD)                      | I/O                 | LVCMOS                     | DVCC         | OFF                      |

|        |      | UCA0TXD                        | 0                   | LVCMOS                     | DVCC         | _                        |

|        |      | UCA0SIMO                       | I/O                 | LVCMOS                     | DVCC         | _                        |

| 11     | 13   | TB0.2                          | I/O                 | LVCMOS                     | DVCC         | _                        |

|        |      | TDO                            | 0                   | LVCMOS                     | DVCC         | _                        |

|        |      | A7 <sup>(6)</sup>              | I                   | Analog                     | DVCC         | -                        |

|        |      | VREF+                          | 0                   | Power                      | DVCC         | _                        |

Table 7-1. Pin Attributes

#### MSP430FR2111, MSP430FR2110, MSP430FR2100, MSP430FR2000 SLASE78E - AUGUST 2016 - REVISED JUNE 2021

| PIN NUMBER |                                    | $\mathcal{O}(\mathcal{O})$     | SIGNAL              |                            |              | RESET STATE              |

|------------|------------------------------------|--------------------------------|---------------------|----------------------------|--------------|--------------------------|

| PW16       | RLL                                | SIGNAL NAME <sup>(1) (2)</sup> | TYPE <sup>(3)</sup> | BUFFER TYPE <sup>(4)</sup> | POWER SOURCE | AFTER BOR <sup>(5)</sup> |

|            |                                    | P1.6 (RD)                      | I/O                 | LVCMOS                     | DVCC         | OFF                      |

|            |                                    | UCA0RXD                        | I                   | LVCMOS                     | DVCC         | -                        |

|            |                                    | UCA0SOMI                       | I/O                 | LVCMOS                     | DVCC         | -                        |

| 12         | 14                                 | TB0.1                          | I/O                 | LVCMOS                     | DVCC         | -                        |

|            |                                    | TDI                            | I                   | LVCMOS                     | DVCC         | -                        |

|            |                                    | TCLK                           | I                   | LVCMOS                     | DVCC         | _                        |

|            |                                    | A6 <sup>(6)</sup>              | I                   | Analog                     | DVCC         | _                        |

|            |                                    | P1.5 (RD)                      | I/O                 | LVCMOS                     | DVCC         | OFF                      |

| 13         | 15                                 | UCA0CLK                        | I/O                 | LVCMOS                     | DVCC         | _                        |

| 15         | 15                                 | TMS                            | I                   | LVCMOS                     | DVCC         | _                        |

|            |                                    | A5 <sup>(6)</sup>              | I                   | Analog                     | DVCC         |                          |

|            |                                    | P1.4 (RD)                      | I/O                 | LVCMOS                     | DVCC         | OFF                      |

| 14         | 16                                 | UCA0STE                        | I/O                 | LVCMOS                     | DVCC         | _                        |

| 14         | 10                                 | ТСК                            | I                   | LVCMOS                     | DVCC         | _                        |

|            |                                    | A4 <sup>(6)</sup>              | I                   | Analog                     | DVCC         | _                        |

|            |                                    | P1.3 (RD)                      | I/O                 | LVCMOS                     | DVCC         | OFF                      |

|            |                                    | UCA0TXD                        | 0                   | LVCMOS                     | DVCC         | _                        |

| 15         | 17                                 | UCA0SIMO                       | I/O                 | LVCMOS                     | DVCC         | _                        |

|            |                                    | C3                             | I                   | Analog                     | DVCC         | _                        |

|            |                                    | A3 <sup>(6)</sup>              | I                   | Analog                     | DVCC         | _                        |

|            |                                    | P1.2 (RD)                      | I/O                 | LVCMOS                     | DVCC         | OFF                      |

|            |                                    | UCA0RXD                        | I                   | LVCMOS                     | DVCC         | _                        |

|            |                                    | UCA0SOMI                       | I/O                 | LVCMOS                     | DVCC         | _                        |

| 16         | 19                                 | TB0TRG                         | I                   | LVCMOS                     | DVCC         | _                        |

|            |                                    | C2                             | Ι                   | Analog                     | DVCC         | _                        |

|            |                                    | A2 <sup>(6)</sup>              | I                   | Analog                     | DVCC         | _                        |

|            |                                    | Veref- <sup>(6)</sup>          | Ι                   | Power                      | DVCC         | _                        |

|            | 6, 9, 10,<br>12, 18, 21,<br>22, 24 | NC <sup>(7)</sup>              | _                   | _                          | _            | _                        |

#### Table 7-1, Pin Attributes (continued)

(1) (2) Signals names with (RD) denote the reset default pin name.

To determine the pin mux encodings for each pin, see Section 9.11.15.

(3) Signal Types: I = Input, O = Output, I/O = Input or Output.

(4) Buffer Types: LVCMOS, Analog, or Power (see Section 7.6)

Reset States: (5)

OFF = High-impedance input with pullup or pulldown disabled (if available) N/A = Not applicable

The ADC is not available on the MSP430FR2000 device. (6)

(7) NC = Not connected

# 7.3 Signal Descriptions

Table 7-2 describes the signals for all device variants and package options.

| PIN NUMBER         |             |      |     |             |                                                               |

|--------------------|-------------|------|-----|-------------|---------------------------------------------------------------|

| FUNCTION           | SIGNAL NAME | PW16 | RLL | PIN<br>TYPE | DESCRIPTION                                                   |

|                    | A0          | 2    | 20  | 1           | Analog input A0                                               |

|                    | A1          | 1    | 23  | 1           | Analog input A1                                               |

|                    | A2          | 16   | 19  | 1           | Analog input A2                                               |

|                    | A3          | 15   | 17  | 1           | Analog input A3                                               |

| (1)                | A4          | 14   | 16  | 1           | Analog input A4                                               |

| ADC <sup>(1)</sup> | A5          | 13   | 15  | 1           | Analog input A5                                               |

|                    | A6          | 12   | 14  | 1           | Analog input A6                                               |

|                    | A7          | 11   | 13  | I           | Analog input A7                                               |

|                    | Veref+      | 2    | 20  | I           | ADC positive reference                                        |

|                    | Veref-      | 16   | 19  | I           | ADC negative reference                                        |

|                    | CO          | 2    | 20  | I           | Comparator input channel C0                                   |

|                    | C1          | 1    | 23  | I           | Comparator input channel C1                                   |

| eCOMP0             | C2          | 16   | 19  | I           | Comparator input channel C2                                   |

|                    | C3          | 15   | 17  | I           | Comparator input channel C3                                   |

|                    | COUT        | 10   | 8   | 0           | Comparator output channel COUT                                |

|                    | ACLK        | 1    | 23  | 0           | ACLK output                                                   |

|                    | MCLK        | 8    | 7   | 0           | MCLK output                                                   |

| Clock              | SMCLK       | 2    | 20  | 0           | SMCLK output                                                  |

|                    | XIN         | 7    | 5   | I           | Input terminal for crystal oscillator                         |

|                    | XOUT        | 8    | 7   | 0           | Output terminal for crystal oscillator                        |

|                    | SBWTCK      | 3    | 1   | I           | Spy-Bi-Wire input clock                                       |

|                    | SBWTDIO     | 4    | 2   | I/O         | Spy-Bi-Wire data input/output                                 |

|                    | ТСК         | 14   | 16  | I           | Test clock                                                    |

| Dobug              | TCLK        | 12   | 14  | I           | Test clock input                                              |

| Debug              | TDI         | 12   | 14  | I           | Test data input                                               |

|                    | TDO         | 11   | 13  | 0           | Test data output                                              |

|                    | TMS         | 13   | 15  | I           | Test mode select                                              |

|                    | TEST        | 3    | 1   | I           | Test mode pin – selected digital I/O on JTAG pins             |

| System             | NMI         | 4    | 2   | I           | Nonmaskable interrupt input                                   |

| System             | RST         | 4    | 2   | I/O         | Reset input, active low                                       |

|                    | DVCC        | 5    | 3   | Р           | Power supply                                                  |

| Power              | DVSS        | 6    | 4   | Р           | Power ground                                                  |

|                    | VREF+       | 11   | 13  | Р           | Output of positive reference voltage with ground as reference |

## Table 7-2. Signal Descriptions

| Table 7-2. Signal Descriptions (continued)                                                       |                         |                |     |      |                                                               |  |  |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------|----------------|-----|------|---------------------------------------------------------------|--|--|--|--|

| FUNCTION                                                                                         | SIGNAL NAME             | PIN NUMBER     |     | PIN  | DESCRIPTION                                                   |  |  |  |  |

| FUNCTION                                                                                         | SIGNAL NAME             | PW16           | RLL | TYPE | DESCRIPTION                                                   |  |  |  |  |

|                                                                                                  | P1.0                    | 2              | 20  | I/O  | General-purpose I/O                                           |  |  |  |  |

|                                                                                                  | P1.1                    | 1              | 23  | I/O  | General-purpose I/O                                           |  |  |  |  |

|                                                                                                  | P1.2                    | 16             | 19  | I/O  | General-purpose I/O                                           |  |  |  |  |

|                                                                                                  | P1.3                    | 15             | 17  | I/O  | General-purpose I/O                                           |  |  |  |  |

|                                                                                                  | P1.4                    | 14             | 16  | I/O  | General-purpose I/O <sup>(2)</sup>                            |  |  |  |  |

| GPIO                                                                                             | P1.5                    | 13             | 15  | I/O  | General-purpose I/O <sup>(2)</sup>                            |  |  |  |  |

| GPIO                                                                                             | P1.6                    | 12             | 14  | I/O  | General-purpose I/O <sup>(2)</sup>                            |  |  |  |  |

|                                                                                                  | P1.7                    | 11             | 13  | I/O  | General-purpose I/O <sup>(2)</sup>                            |  |  |  |  |

|                                                                                                  | P2.0                    | 10             | 8   | I/O  | General-purpose I/O                                           |  |  |  |  |

|                                                                                                  | P2.1                    | 9              | 11  | I/O  | General-purpose I/O                                           |  |  |  |  |

|                                                                                                  | P2.6                    | 8              | 7   | I/O  | General-purpose I/O                                           |  |  |  |  |

|                                                                                                  | P2.7                    | 7              | 5   | I/O  | General-purpose I/O                                           |  |  |  |  |

|                                                                                                  | UCA0CLK                 | 13             | 15  | I/O  | eUSCI_A0 SPI clock input/output                               |  |  |  |  |

|                                                                                                  | UCA0RXD                 | 12             | 14  | I    | eUSCI_A0 UART receive data                                    |  |  |  |  |

|                                                                                                  | UCA0SIMO                | 11             | 13  | I/O  | eUSCI_A0 SPI slave in/master out                              |  |  |  |  |

|                                                                                                  | UCA0SOMI                | 12             | 14  | I/O  | eUSCI_A0 SPI slave out/master in                              |  |  |  |  |

|                                                                                                  | UCA0STE                 | 14             | 16  | I/O  | eUSCI_A0 SPI slave transmit enable                            |  |  |  |  |

| SPI and UART                                                                                     | UCA0TXD                 | 11             | 13  | 0    | eUSCI_A0 UART transmit data                                   |  |  |  |  |

| SPI and UART                                                                                     | UCA0CLK <sup>(4)</sup>  | 1              | 23  | I/O  | eUSCI_A0 SPI clock input/output                               |  |  |  |  |

|                                                                                                  | UCA0RXD <sup>(4)</sup>  | 16             | 19  | I    | eUSCI_A0 UART receive data                                    |  |  |  |  |

|                                                                                                  | UCA0SIMO <sup>(4)</sup> | 15             | 17  | I/O  | eUSCI_A0 SPI slave in/master out                              |  |  |  |  |

|                                                                                                  | UCA0SOMI <sup>(4)</sup> | 16             | 19  | I/O  | eUSCI_A0 SPI slave out/master in                              |  |  |  |  |

|                                                                                                  | UCA0STE <sup>(4)</sup>  | 2              | 20  | I/O  | eUSCI_A0 SPI slave transmit enable                            |  |  |  |  |

|                                                                                                  | UCA0TXD <sup>(4)</sup>  | 15             | 17  | 0    | eUSCI_A0 UART transmit data                                   |  |  |  |  |

|                                                                                                  | TB0.1                   | 12             | 14  | I/O  | Timer TB0 CCR1 capture: CCI1A input, compare: Out1 outputs    |  |  |  |  |

|                                                                                                  | TB0.2                   | 11             | 13  | I/O  | Timer TB0 CCR2 capture: CCI2A input, compare: Out2 outputs    |  |  |  |  |

| Timer B                                                                                          | TB0CLK                  | 7              | 5   | I    | Timer clock input TBCLK for TB0                               |  |  |  |  |

| TIMEL_D                                                                                          | TB0TRG                  | 16             | 19  | I    | TB0 external trigger input for TB0OUTH                        |  |  |  |  |

|                                                                                                  | TB0.1 <sup>(3)</sup>    | 10             | 8   | I/O  | Timer TB0 CCR1 capture: CCI1A input, compare: Out1 outputs    |  |  |  |  |

|                                                                                                  | TB0.2 <sup>(3)</sup>    | 9              | 11  | I/O  | Timer TB0 CCR2 capture: CCI2A input, compare: Out2 outputs    |  |  |  |  |

| NC pad NC - $\begin{pmatrix} 6, 9, \\ 10, 12, \\ 18, 21, \\ 22, 24 \end{pmatrix}$ Do not connect |                         | Do not connect |     |      |                                                               |  |  |  |  |

| VQFN pad                                                                                         | Pad                     | _              | Pad |      | VQFN package (RLL) exposed thermal pad. Connect to $V_{SS}$ . |  |  |  |  |

# Table 7-2. Signal Descriptions (continued)

(1) The ADC is not available on the MSP430FR2000 device.

(2) Because this pin is multiplexed with the JTAG function, TI recommends disabling the pin interrupt function while in JTAG debug to prevent collisions.

(3) This is the remapped functionality controlled by the TBRMP bit in the SYSCFG3 register. Only one selected port is valid at the same time when TB0 acts as capture input functionality. TB0 PWM outputs regardless of the setting on this remap bit.

(4) This is the remapped functionality controlled by the USCIARMP bit in the SYSCFG3 register. Only one selected port is valid at the same time.

#### 7.4 Pin Multiplexing

Pin multiplexing for these devices is controlled by both register settings and operating modes (for example, if the device is in test mode). For details of the settings for each pin and schematics of the multiplexed ports, see Section 9.11.15.

## 7.5 Connection of Unused Pins

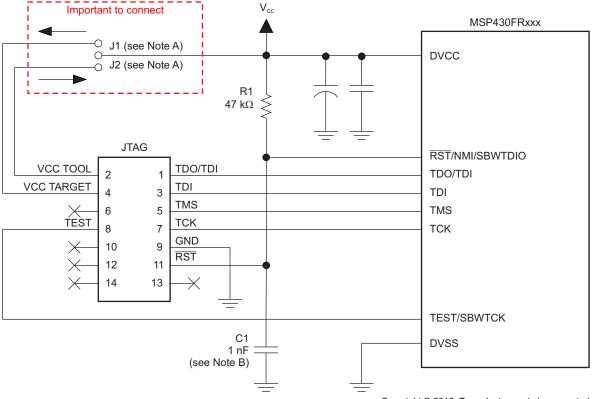

Table 7-3 lists the correct termination of unused pins.

| PIN <sup>(1)</sup> | POTENTIAL | COMMENT                                                                              |

|--------------------|-----------|--------------------------------------------------------------------------------------|

| Px.0 to Px.7       | Open      | Set to port function, output direction (PxDIR.n = 1)                                 |

| RST/NMI            | DVCC      | 47-kΩ pullup or internal pullup selected with 10-nF (1.1 nF) pulldown <sup>(2)</sup> |

| TEST               | Open      | This pin always has an internal pulldown enabled.                                    |

(1) Any unused pin with a secondary function that is shared with general-purpose I/O should follow the Px.0 to Px.7 unused pin connection guidelines.

(2) The pulldown capacitor should not exceed 1.1 nF when using devices with Spy-Bi-Wire interface in Spy-Bi-Wire mode with TI tools like FET interfaces or GANG programmers.

# 7.6 Buffer Type

Table 7-4 defines the pin buffer types that are listed in Table 7-1.

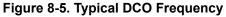

| BUFFER TYPE<br>(STANDARD) | NOMINAL<br>VOLTAGE | HYSTERESIS | PU OR PD     | NOMINAL<br>PU OR PD<br>STRENGTH<br>(µA) | OUTPUT DRIVE<br>STRENGTH<br>(mA) | OTHER<br>CHARACTERISTICS                         |

|---------------------------|--------------------|------------|--------------|-----------------------------------------|----------------------------------|--------------------------------------------------|

| LVCMOS                    | 3.0 V              | Y(1)       | Programmable | See Section<br>8.12.4                   | See Section<br>8.12.4.3          |                                                  |

| Analog                    | 3.0 V              | No         | No           | N/A                                     | N/A                              | See the analog modules in Section 8 for details. |

| Power (DVCC)              | 3.0 V              | No         | No           | N/A                                     | N/A                              | SVS enables hysteresis on DVCC.                  |

| Power (AVCC)              | 3.0 V              | No         | No           | N/A                                     | N/A                              |                                                  |

Table 7-4. Buffer Type

(1) Only for input pins

# 8 Specifications

# 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                            | MIN  | MAX                                  | UNIT |

|------------------------------------------------------------|------|--------------------------------------|------|

| Voltage applied at DVCC pin to V <sub>SS</sub>             | -0.3 | 4.1                                  | V    |

| Voltage applied to any pin <sup>(2)</sup>                  | -0.3 | V <sub>CC</sub> + 0.3<br>(4.1 V Max) | V    |

| Diode current at any device pin                            |      | ±2                                   | mA   |

| Maximum junction temperature, T <sub>J</sub>               |      | 85                                   | °C   |

| Storage temperature range, T <sub>stg</sub> <sup>(3)</sup> | -40  | 125                                  | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are referenced to V<sub>SS</sub>.

(3) Higher temperature may be applied during board soldering according to the current JEDEC J-STD-020 specification with peak reflow temperatures not higher than classified on the device label on the shipping boxes or reels.

## 8.2 ESD Ratings

|                   |                         |                                                                                | VALUE | UNIT |

|-------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                 | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              |       | V    |

| V <sub>(ESI</sub> |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±1000 V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±250 V may actually have higher performance.

# 8.3 Recommended Operating Conditions

|                     |                                                               |                                                               | MIN | NOM | MAX               | UNIT  |

|---------------------|---------------------------------------------------------------|---------------------------------------------------------------|-----|-----|-------------------|-------|

| V <sub>CC</sub>     | Supply voltage applied at DVCC pin <sup>(1) (2) (3) (4)</sup> | Supply voltage applied at DVCC pin <sup>(1) (2) (3) (4)</sup> |     |     | 3.6               | V     |

| V <sub>SS</sub>     | Supply voltage applied at DVSS pin                            | Supply voltage applied at DVSS pin                            |     |     |                   | V     |

| T <sub>A</sub>      | Operating free-air temperature                                |                                                               |     |     | 85                | °C    |

| TJ                  | Operating junction temperature                                |                                                               |     |     | 85                | °C    |

| C <sub>DVCC</sub>   | Recommended capacitor at DVCC <sup>(5)</sup>                  |                                                               |     | 10  |                   | μF    |

|                     | Drococces from upper (movimum MCLK from upper) (6)            | No FRAM wait states<br>(NWAITSx = 0)                          | 0   |     | 8                 | MHz   |

| f <sub>system</sub> | Processor frequency (maximum MCLK frequency) <sup>(6)</sup>   | With FRAM wait states $(NWAITSx = 1)^{(7)}$                   | 0   |     | 16 <sup>(8)</sup> | IVITZ |

| f <sub>ACLK</sub>   | Maximum ACLK frequency                                        | quency                                                        |     |     | 40                | kHz   |

| f <sub>SMCLK</sub>  | Maximum SMCLK frequency                                       |                                                               |     |     | 16 <sup>(8)</sup> | MHz   |

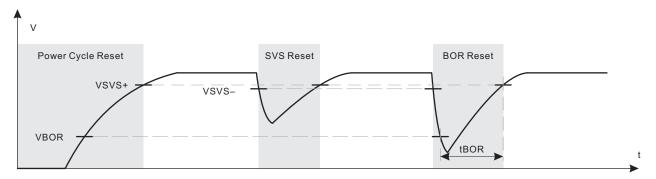

(1) Supply voltage changes faster than 0.2 V/µs can trigger a BOR reset even within the recommended supply voltage range. Following the data sheet recommendation for capacitor C<sub>DVCC</sub> limits the slopes accordingly.

(2) Modules may have a different supply voltage range specification. See the specification of the respective module in this data sheet.

(3) TI recommends that power to the DVCC pin must not exceed the limits specified in *Recommended Operating Conditions*. Exceeding the specified limits can cause malfunction of the device including erroneous writes to RAM and FRAM.

(4) The minimum supply voltage is defined by the SVS levels. See the SVS threshold parameters in Section 8.12.1.1.

(5) A capacitor tolerance of ±20% or better is required. A low-ESR ceramic capacitor of 100 nF (minimum) should be placed as close as possible (within a few millimeters) to the respective pin pair.

(6) Modules may have a different maximum input clock specification. See the specification of the respective module in this data sheet.

(7) Wait states only occur on actual FRAM accesses (that is, on FRAM cache misses). RAM and peripheral accesses are always executed without wait states.

(8) If clock sources such as HF crystals or the DCO with frequencies >16 MHz are used, the clock must be divided in the clock system to comply with this operating condition.

# 8.4 Active Mode Supply Current Into V<sub>CC</sub> Excluding External Current

|                                     |                         |                   |                                         | FRE | QUENCY (f <sub>M</sub>                  | <sub>CLK</sub> = f <sub>SN</sub> | ісік)                                   |     |      |

|-------------------------------------|-------------------------|-------------------|-----------------------------------------|-----|-----------------------------------------|----------------------------------|-----------------------------------------|-----|------|

| PARAMETER                           | EXECUTION<br>MEMORY     | TEST<br>CONDITION | 1 MHz<br>0 WAIT STATES<br>(NWAITSx = 0) |     | 8 MHz<br>0 WAIT STATES<br>(NWAITSx = 0) |                                  | 16 MHz<br>1 WAIT STATE<br>(NWAITSx = 1) |     | UNIT |

|                                     |                         |                   | TYP                                     | MAX | TYP                                     | MAX                              | TYP                                     | MAX |      |

| 1                                   | FRAM                    | 3.0 V, 25°C       | 460                                     |     | 2670                                    |                                  | 2940                                    |     |      |

| IAM, FRAM (0%)                      | 0% cache hit ratio      | 3.0 V, 85°C       | 475                                     |     | 2730                                    |                                  | 2980                                    |     | μA   |

| I <sub>AM, FRAM</sub> (100%)        | FRAM                    | 3.0 V, 25°C       | 191                                     |     | 570                                     |                                  | 942                                     |     |      |

|                                     | 100% cache hit<br>ratio | 3.0 V, 85°C       | 199                                     |     | 585                                     |                                  | 960                                     |     | μA   |

| I <sub>AM, RAM</sub> <sup>(2)</sup> | RAM                     | 3.0 V, 25°C       | 213                                     |     | 739                                     |                                  | 1244                                    |     | μA   |

All inputs are tied to 0 V or to V<sub>CC</sub>. Outputs do not source or sink any current. Characterized with program executing typical data (1) processing.

f<sub>ACLK</sub> = 32768 Hz, f<sub>MCLK</sub> = f<sub>SMCLK</sub> = f<sub>DCO</sub> at specified frequency Program and data entirely reside in FRAM. All execution is from FRAM.

(2) Program and data reside entirely in RAM. All execution is from RAM. No access to FRAM.

## 8.5 Active Mode Supply Current Per MHz

#### $V_{CC}$ = 3.0 V, $T_A$ = 25°C (unless otherwise noted)

| PARAMETER |                                                                                                                       | TEST CONDITIONS                                                                                            | TYP | UNIT   |

|-----------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|--------|

|           | dI <sub>AM,FRAM</sub> /df Active mode current consumption per MHz, execution from FRAM, no wait states <sup>(1)</sup> | [(I <sub>AM</sub> 75% cache hit rate at 8 MHz) –<br>(I <sub>AM</sub> 75% cache hit rate at 1 MHz)] / 7 MHz | 120 | µA/MHz |

(1) All peripherals are turned on in default settings.

# 8.6 Low-Power Mode LPM0 Supply Currents Into V<sub>CC</sub> Excluding External Current

$V_{CC}$  = 3.0 V,  $T_A$  = 25°C (unless otherwise noted)<sup>(1)</sup> (2)

|          |           |                 | FREQUENCY (f <sub>SMCLK</sub> ) |     |       |     |        |     |      |

|----------|-----------|-----------------|---------------------------------|-----|-------|-----|--------|-----|------|

|          | PARAMETER | V <sub>cc</sub> | 1 MHz                           |     | 8 MHz |     | 16 MHz |     | UNIT |

|          |           |                 | TYP                             | MAX | ТҮР   | MAX | TYP    | MAX |      |

|          |           | 2.0 V           | 148                             |     | 295   |     | 398    |     |      |

| <u>"</u> | PMO       | 3.0 V           | 157                             |     | 304   |     | 402    |     | μA   |

All inputs are tied to 0 V or to V<sub>CC</sub>. Outputs do not source or sink any current. (1)

Current for watchdog timer clocked by SMCLK included. (2)

f<sub>ACLK</sub> = 32768 Hz, f<sub>MCLK</sub> = 0 MHz, f<sub>SMCLK</sub> at specified frequency.

# 8.7 Low-Power Mode LPM3, LPM4 Supply Currents (Into V<sub>CC</sub>) Excluding External Current

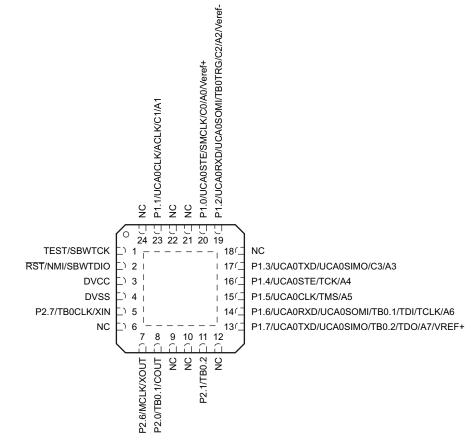

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) <sup>(1)</sup> (see Figure 8-1)

| PARAMETER                    |                                                       |       | TEMPERATURE |     |      |     |      |      |      |

|------------------------------|-------------------------------------------------------|-------|-------------|-----|------|-----|------|------|------|

|                              |                                                       |       | –40°C       |     | 25°C |     | 85°C |      | UNIT |

|                              |                                                       |       | TYP         | MAX | TYP  | MAX | ТҮР  | MAX  |      |

| 1                            | Low-power mode 3, includes SVS <sup>(2)</sup> (3) (4) | 3.0 V | 0.95        |     | 1.07 |     | 2.13 | 6.00 |      |