# ACSL-6xx0 Multi-Channel and Bi-Directional, 15 MBd Digital Logic Gate Optocoupler

**Data Sheet**

## Description

ACSL-6xx0 are truly isolated, multi-channel and bi-directional, high-speed optocouplers. Integration of multiple optocouplers in monolithic form is achieved through patented process technology. These devices provide full duplex and bi-directional isolated data transfer and communication capability in compact surface mount packages. Available in 15 Mbd speed option and wide supply voltage range.

These high channel density make them ideally suited to isolating data conversion devices, parallel buses and peripheral interfaces.

They are available in 8-pin and 16-pin narrow-body SOIC package and are specified over the temperature range of -40°C to +100°C.

## Applications

- Full duplex communication

- Isolated line receiver

- · Computer-peripheral interfaces

- Microprocessor system interfaces

- Digital isolation for A/D and D/A conversion

- Switching power supply

- Instrument input/output isolation

- Ground loop elimination

- Pulse transformer replacement

## Features

- Available in dual, triple and quad channel configurations

- Bi-directional

- Wide supply voltage range 3.0V to 5.5V

- High-speed: 15 MBd typical, 10 MBd minimum

- 10 kV/µs minimum Common Mode Rejection (CMR) at Vcm = 1000 V

- LSTTL/TTL compatible

- Safety and regulatory approvals (Pending)

- 2500Vrms for 1 min per UL1577

- CSA Component Acceptance

- IEC/EN/DIN EN 60747-5-2

- 16 Pin narrow-body SOIC package for triple and quad channel

- -40 to 100°C temperature range

## CAUTION:

It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation, which may be induced by ESD.

#### **Device Selection Guide**

| Device Number | Channel Configuration       | Package              |

|---------------|-----------------------------|----------------------|

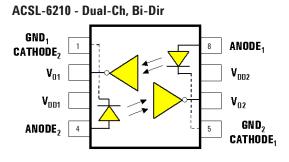

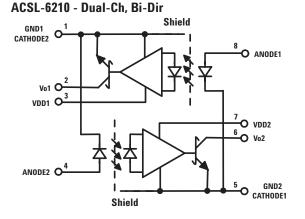

| ACSL-6210     | Dual, Bi-Directional`       | 8-pin Small Outline  |

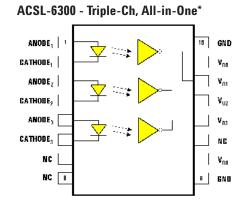

| ACSL-6300*    | Triple, All-in-One          | 16-pin Small Outline |

| ACSL-6310*    | Triple, Bi-Directional, 2/1 | 16-pin Small Outline |

| ACSL-6400     | Quad, All-in-One            | 16-pin Small Outline |

| ACSL-6410*    | Quad, Bi-Directional, 3/1   | 16-pin Small Outline |

| ACSL-6420*    | Quad, Bi-Directional, 2/2   | 16-pin Small Outline |

\* Advanced Information

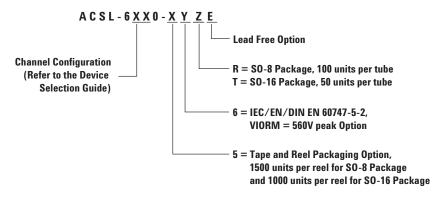

## **Ordering Information**

## **Pin Description**

| Symbol               | Description    | Symbol           | Description           |

|----------------------|----------------|------------------|-----------------------|

| V <sub>DD1</sub>     | Power Supply 1 | GND <sub>1</sub> | Power Supply Ground 1 |

| V <sub>DD2</sub>     | Power Supply 2 | GND <sub>2</sub> | Power Supply Ground 2 |

| ANODE <sub>x</sub>   | LED Anode      | NC               | Not Connected         |

| CATHODE <sub>x</sub> | LED Cathode    | V <sub>OX</sub>  | Output Signal         |

|                      |                |                  |                       |

## Truth Table (Positive Logic)

| LED | OUTPUT |

|-----|--------|

| ON  | L      |

| OFF | Н      |

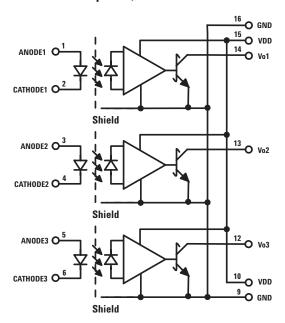

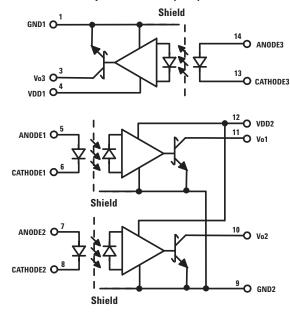

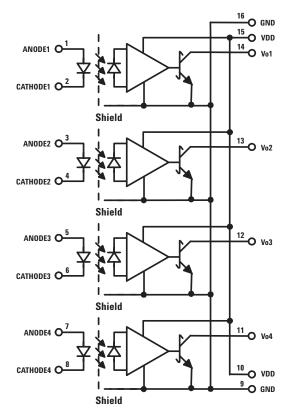

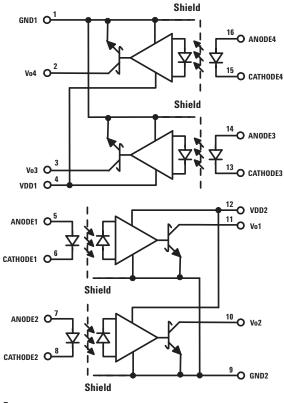

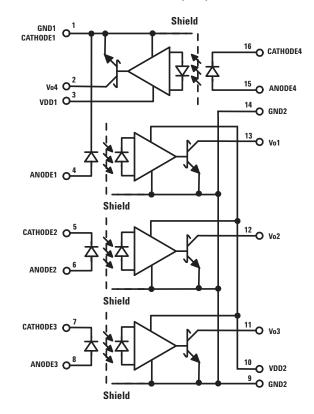

### **Functional Diagrams**

16 GND

V<sub>nn</sub>

V<sub>N1</sub>

V<sub>U2</sub>

V<sub>na</sub>

V<sub>U1</sub>

V<sub>nn</sub>

9 GND

AN ODE,

AN ODE,

AN ODE:

CATHODE<sub>1</sub>

CATHODE,

CATHODE

ANODE

CATHODE<sub>4</sub>

8

ACSL-6410 - Quad-Ch, Bi-Dir (3/1)\*

ACSL-6420 - Quad-Ch, Bi-Dir (2/2)\*

\* Advanced Information

# i anctional Didy

#### **Schematic Diagrams**

The ACSL-6xx0 series optocouplers feature the GaAsP LEDs with proprietary back emission design. They offer the designer a broad range of input drive current, from 7 mA to 15 mA, thus providing greater flexibility in designing the drive circuit. The output detector integrated circuit (IC) in the optocoupler consists of a photodiode at the input of a two-stage amplifier that provides both high gain and high bandwidth. The secondary amplifier stage of the detector IC feeds into an open collector Schottky-clamped transistor. The entire output circuit is electrically shielded so that any commonmode transient capacitively coupled from the LED side of the optocoupler is diverted from the photodiode to ground. With this electric shield, the optocoupler can withstand transients that slopes up to  $10,000V/\mu$ s, and amplitudes up to 1,000V.

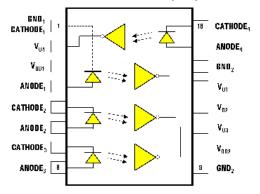

ACSL-6300 - Triple-Ch, All-in-One\*

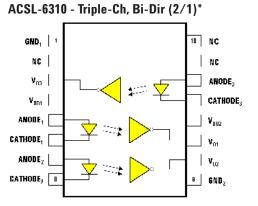

ACSL-6310 - Triple-Ch, Bi-Dir (2/1)\*

\* Advanced Information

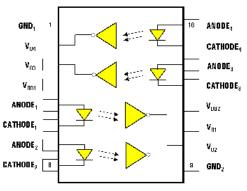

## ACSL-6400 - Quad-Ch, All-in-One

## ACSL-6420 - Quad-Ch, Bi-Dir (2/2)\*

ACSL-6410 - Quad-Ch, Bi-Dir (3/1)\*

\* Advanced Information

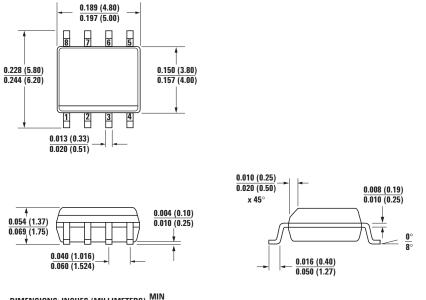

### **Package Outline Drawings**

### ACSL-6210 Small Outline SO-8 Package

DIMENSIONS: INCHES (MILLIMETERS)  $\frac{\text{MIN}}{\text{MAX}}$

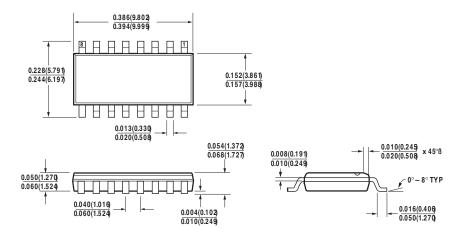

# ACSL-6300\*, ACSL-6310\*, ACSL-6400, ACSL-6410\* and ACSL-6420\* Small Outline SO-16 Package

DIMENSIONS: INCHES (MILLIMETERS)  $\frac{\text{MIN}}{\text{MAX}}$

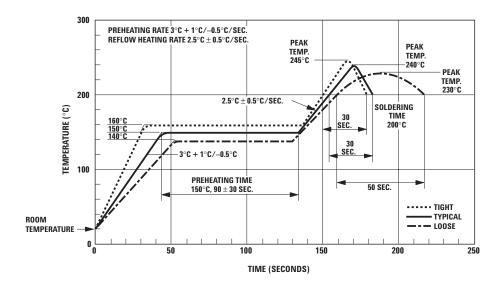

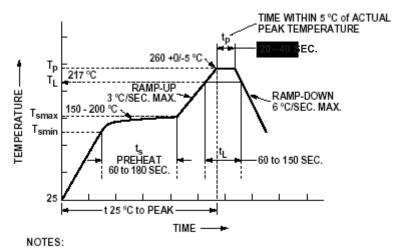

### **Solder Reflow Temperature Profile**

**Recommended Pb-free IR Profile**

THE TIME FROM 25 °C to PEAK TEMPERATURE = 8 MINUTES MAX.  $T_{smax}$  = 200 °C,  $T_{smin}$  = 150 °C

# Regulatory Information Insulation and Safety Related Specifications

| Parameter                                         | Symbol | Value | Units | Conditions                                                                                      |

|---------------------------------------------------|--------|-------|-------|-------------------------------------------------------------------------------------------------|

| Minimum External Air Gap (Clearance)              | L(101) | 4.9   | mm    | Measured from input terminals to output terminals, shortest distance through air                |

| Minimum Externa I Tracking(Creepage)              | L(102) | 4.5   | mm    | Measured from input terminals to output terminals,<br>shortest distance path through body       |

| Minimum Internal Plastic Gap (Internal Clearance) |        | 0.08  | mm    | Insulation thickness between emitter and detector;<br>also known as distance through insulation |

| Tracking Resistance (Comparative Tracking Index)  | СТІ    | 175   | Volts | DIN IEC 112/VDE0303 Part 1                                                                      |

| Isolation Group                                   |        | Illa  |       | Material Group (DIN VDE 0110, 1/89, Table 1)                                                    |

# IEC/EN/DIN EN 60747-5-2 Insulation Related Characteristics (Option X6X Only)

| Description                                                      | Symbol                | ACSL-6XX0-X6X   | Units             |

|------------------------------------------------------------------|-----------------------|-----------------|-------------------|

| Installation Classification per DIN VDE 0110/1.89, Table 1       |                       |                 |                   |

| for rated mains voltage $\leq$ 150V rms                          |                       | I-IV            |                   |

| for rated mains voltage $\leq$ 300V rms                          |                       | 1-111           |                   |

| Climatic Classification                                          |                       | 55/100/21       |                   |

| Pollution Degree (DIN VDE 0110/1.89)                             |                       | 2               |                   |

| Maximum Working Insulation Voltage                               | V <sub>IORM</sub>     | 560             | V <sub>peak</sub> |

| Input to Output Test Voltage, Method b *                         | V <sub>PR</sub>       | 1050            | V <sub>peak</sub> |

| V <sub>IORM</sub> x 1.875 = V <sub>PR</sub> , 100% Production    |                       |                 |                   |

| Test with $t_m = 1$ sec, Partial Discharge < 5 pC                |                       |                 |                   |

| Input to Output Test Voltage, Method a *                         | V <sub>PR</sub>       | 840             | V <sub>peak</sub> |

| $V_{IORM} \times 1.5 = V_{PR}$ , Type and Sample Test,           |                       |                 | pour              |

| T <sub>m</sub> = 60 sec, Partial Discharge < 5 pC                |                       |                 |                   |

| Highest Allowable Overvoltage *                                  | V <sub>IOTM</sub>     | 4000            | V <sub>peak</sub> |

| (Transient Overvoltage, t <sub>ini</sub> = 10 sec)               | 101111                |                 | pour              |

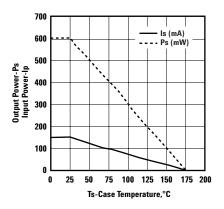

| Safety Limiting Values                                           |                       |                 |                   |

| (Maximum values allowed in the event of a failure)               |                       |                 |                   |

| Case Temperature                                                 | Τ <sub>S</sub>        | 175             | ۵°                |

| Input Current                                                    | I <sub>S,INPUT</sub>  | 150             | mA                |

| Output Power                                                     | P <sub>S,OUTPUT</sub> | 600             | mW                |

| Insulation Resistance at T <sub>S</sub> , V <sub>I0</sub> = 500V | R <sub>IO</sub>       | 10 <sup>9</sup> | Ω                 |

\*Refer to the front of the optocoupler section of the current catalog, under Product Safety Regulations section, IEC/EN/DIN EN 60747-5-2, for a detailed description.

Note: Isolation characteristics are guaranteed only within the safety maximum ratings, which must be ensured by protective circuits in application.

#### **Absolute Maximum Ratings**

| Parameter                                                  | Symbol                              | Min. | Max.     | Units    |

|------------------------------------------------------------|-------------------------------------|------|----------|----------|

| -<br>Storage Temperature                                   | Τ <sub>s</sub>                      | -55  | 125      | °C       |

| Operating Temperature                                      | T <sub>A</sub>                      | -40  | 100      | °C       |

| Supply Voltage (1 Minute Maximum)                          | V <sub>DD1</sub> , V <sub>DD2</sub> |      | 7        | V        |

| Reverse Input Voltage (Per Channel)                        | V <sub>R</sub>                      |      | 5        | V        |

| Output Voltage (Per Channel)                               | V <sub>0</sub>                      |      | 7        | V        |

| Average Forward Input Current <sup>[1]</sup> (Per Channel) | ۱ <sub>F</sub>                      |      | 15       | mA       |

| Output Current (Per Channel)                               | ۱ <sub>0</sub>                      |      | 50       | mA       |

| Input Power Dissipation <sup>[2]</sup> (Per Channel)       | P <sub>1</sub>                      |      | 24       | mW       |

| Output Power Dissipation <sup>[2]</sup> (Per Channel)      | P <sub>0</sub>                      |      |          |          |

| SO8 package<br>SO16 package                                | -                                   |      | 60<br>40 | mW<br>mW |

## **Recommended Operating Conditions**

| Parameter                                | Symbol             | Min. | Max. | Units     |  |

|------------------------------------------|--------------------|------|------|-----------|--|

| Operating Temperature                    | T <sub>A</sub>     | -40  | 100  | ٦°        |  |

| Input Current, Low Level <sup>[3]</sup>  | I <sub>FL</sub>    | 0    | 250  | μΑ        |  |

| Input Current, High Level <sup>[4]</sup> | I <sub>FH</sub>    | 7    | 15   | mA        |  |

| Supply Voltage                           | $V_{DD1}, V_{DD2}$ | 3.0  | 5.5  | V         |  |

| Fan Out (at R <sub>L</sub> = 1kΩ)        | Ν                  |      | 5    | TTL Loads |  |

| Output Pull-up Resistor                  | RL                 | 330  | 4k   | Ω         |  |

#### Notes:

- Peaking circuits may produce transient input currents up to 50 mA, 50 ns max. pulse width, provided average current does not exceed its max. values.

- Derate total package power dissipation, PT linearly above +85°C free-air temperature at a rate of 6.4 mW/°C for the S08 package mounted on low conductivity board per JESD 51-3. Derate total package power dissipation, PT linearly above +78°C free-air temperature

at a rate of 7.98 mW/°C for the S016 package mounted on low conductivity board per JESD 51-3. PT= number of channels multiplied by (PI+PO).

- 3. The off condition can be guaranteed by ensuring that  $V_{FL} \leq 0.8 \text{V}.$

- The initial switching threshold is 7 mA or less. It is recommended that minimum 8 mA be used for best performance and to permit guardband for LED degradation.

#### **Electrical Specifications**

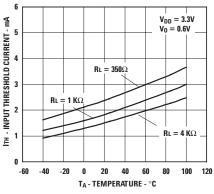

Over recommended operating range (3.0V  $\leq$   $V_{\rm DD1}$   $\leq$  3.6V, 3.0V  $\leq$   $V_{\rm DD2}$   $\leq$  3.6V,  $T_{\rm A}$  = -40°C to +100°C) unless otherwise specified.

All typical specifications are at  $T_{\rm A}$  = +25°C ,  $V_{\rm DD1}$  =  $V_{\rm DD2}$  = +3.3V.

| Parameter                               | Symbol                    | Min. | Тур. | Max.  | Units | Test Conditions                                       |

|-----------------------------------------|---------------------------|------|------|-------|-------|-------------------------------------------------------|

| Input Threshold Current                 | I <sub>TH</sub>           |      | 2.7  | 7.0   | mA    | $I_{OL(Sinking)} = 13 \text{ mA}, V_0 = 0.6 \text{V}$ |

| High Level Output Current               | I <sub>он</sub>           |      | 4.7  | 100.0 | μΑ    | I <sub>F</sub> =250 μA, V <sub>0</sub> =3.3V          |

| Low Level Output Voltage                | V <sub>OL</sub>           |      | 0.36 | 0.68  | V     | I <sub>OL(Sinking)</sub> =13 mA, I <sub>F</sub> =7mA  |

| High Level Supply Current (per channel) | I <sub>DDH</sub>          |      | 3.2  | 5.0   | mA    | I <sub>F</sub> =0 mA                                  |

| Low Level Supply Current (per channel)  | I <sub>DDL</sub>          |      | 4.6  | 7.5   | mA    | I <sub>F</sub> = 10 mA                                |

| Input Forward Voltage                   | V <sub>F</sub>            | 1.25 | 1.52 | 1.80  | V     | I <sub>F</sub> =10 mA, T <sub>A</sub> = 25°C          |

| Input Reverse Breakdown Voltage         | BV <sub>R</sub>           | 5.0  |      |       | V     | I <sub>R</sub> =10 μA                                 |

| Input Diode Temperature Coefficient     | $\Delta V_F / \Delta T_A$ |      | -1.8 |       | mV/°C | I <sub>F</sub> =10 mA                                 |

| Input Capacitance                       | C <sub>IN</sub>           |      | 80   |       | pF    | $f = 1 MHz, V_F = 0V$                                 |

## **Switching Specifications**

Over recommended operating range ( $3.0V \le V_{DD1} \le 3.6V$ ,  $3.0V \le V_{DD2} \le 3.6V$ ,  $I_F = 8.0$  mA,  $T_A = -40^{\circ}$ C to  $+100^{\circ}$ C) unless otherwise specified.

All typical specifications are at  $T_{\rm A}$  = +25°C ,  $V_{\rm DD1}$  =  $V_{\rm DD2}$  = +3.3V.

| Parameter                                                        | Symbol           | Min. | Тур. | Max. | Units | Test Conditions                                                              |

|------------------------------------------------------------------|------------------|------|------|------|-------|------------------------------------------------------------------------------|

| Maximum Data Rate                                                |                  | 10   | 15   |      | MBd   | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                    |

| Pulse Width                                                      | t <sub>PW</sub>  | 100  |      |      | ns    | $R_L = 350\Omega, C_L = 15 \text{ pF}$                                       |

| Propagation Delay Time to Logic High Output Level <sup>[5]</sup> | t <sub>PLH</sub> |      | 52   | 100  | ns    | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                    |

| Propagation Delay Time to Logic Low Output Level <sup>[6]</sup>  | t <sub>PHL</sub> |      | 44   | 100  | ns    | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                    |

| Pulse Width Distortion  t <sub>PHL</sub> - t <sub>PLH</sub>      | PWD              |      | 8    | 35   | ns    | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                    |

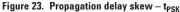

| Propagation Delay Skew <sup>[7]</sup>                            | t <sub>PSK</sub> |      |      | 40   | ns    | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                    |

| Output Rise Time (10 – 90%)                                      | t <sub>R</sub>   |      | 35   |      | ns    | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                    |

| Output Fall Time (10–90%)                                        | t <sub>F</sub>   |      | 12   |      | ns    | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                    |

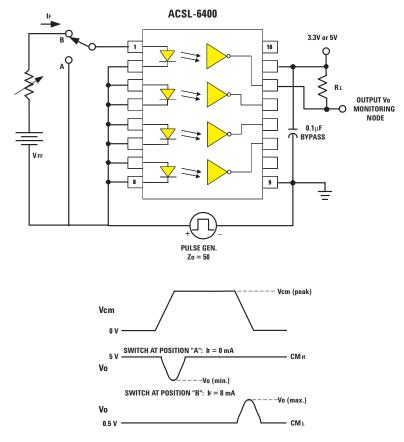

| Logic High Common Mode Transient Immunity <sup>[8]</sup>         | CM <sub>H</sub>  | 10   |      |      | kV∕µs | $V_{cm} = 1000V, I_F = 0 mA, V_0 = 2.0V, R_L = 350\Omega, T_A = 25^{\circ}C$ |

| Logic Low Common Mode Transient Immunity <sup>[8]</sup>          | CM <sub>L</sub>  | 10   |      |      | kV∕µs | $V_{cm} = 1000V, I_F = 8 mA, V_0 = 0.8V, R_L = 350\Omega, T_A = 25^{\circ}C$ |

#### Notes:

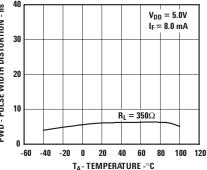

- t<sub>PLH</sub> is measured from the 4.0 mA level on the falling edge of the input pulse to the 1.5V level on the rising edge of the output pulse.

- t<sub>PHL</sub> is measured from the 4.0 mA level on the rising edge of the input pulse to the 1.5V level on the falling edge of the output pulse.

- 7.  $t_{PSK}$  is equal to the worst case difference in  $t_{PHL}$  and/or  $t_{PLH}$  that will be seen between units at any given temperature and specified test conditions.

- 8. CM<sub>H</sub> is the maximum common mode voltage slew rate that can be sustained while maintaining  $V_0 > 2.0V$ . CM<sub>L</sub> is the maximum common mode voltage slew rate that can be sustained while maintaining  $V_0 < 0.8V$ . The common mode voltage slew rates apply to both rising and falling common mode voltage edges.

#### **Electrical Specifications**

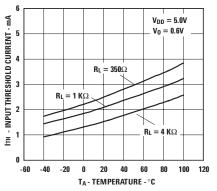

Over recommended operating range (4.5V  $\leq$  V<sub>DD1</sub>  $\leq$  5.5V, 4.5V  $\leq$  V<sub>DD2</sub>  $\leq$  5.5V, T<sub>A</sub> = -40°C to +100°C) unless otherwise specified.

All typical specifications are at  $T_{\rm A}$  = +25°C,  $V_{\rm DD1}$  =  $V_{\rm DD2}$  = +5.0V.

| Parameter                               | Symbol                                | Min. | Тур. | Max.  | Units | Test Conditions                                       |

|-----------------------------------------|---------------------------------------|------|------|-------|-------|-------------------------------------------------------|

| Input Threshold Current                 | I <sub>TH</sub>                       |      | 2.7  | 7.0   | mA    | $I_{OL(Sinking)} = 13 \text{ mA}, V_0 = 0.6 \text{V}$ |

| High Level Output Current               | I <sub>OH</sub>                       |      | 3.8  | 100.0 | μΑ    | I <sub>F</sub> =250 μA, V <sub>0</sub> =5.5V          |

| Low Level Output Voltage                | V <sub>OL</sub>                       |      | 0.36 | 0.6   | V     | I <sub>OL(Sinking)</sub> =13 mA, I <sub>F</sub> =7 mA |

| High Level Supply Current (per channel) | I <sub>DDH</sub>                      |      | 4.3  | 7.5   | mA    | I <sub>F</sub> =0 mA                                  |

| Low Level Supply Current (per channel)  | I <sub>DDL</sub>                      |      | 5.8  | 10.5  | mA    | I <sub>F</sub> = 10 mA                                |

| Input Forward Voltage                   | V <sub>F</sub>                        | 1.25 | 1.52 | 1.8   | V     | I <sub>F</sub> = 10 mA, T <sub>A</sub> = 25°C         |

| Input Reverse Breakdown Voltage         | BV <sub>R</sub>                       | 5.0  |      |       | V     | I <sub>R</sub> =10 μA                                 |

| Input Diode Temperature Coefficient     | $\Delta V_{\rm F} / \Delta T_{\rm A}$ |      | -1.8 |       | mV/°C | I <sub>F</sub> = 10 mA                                |

| Input Capacitance                       | C <sub>IN</sub>                       |      | 80   |       | pF    | f = 1 MHz, V <sub>F</sub> = 0 V                       |

## **Switching Specifications**

Over recommended operating range (4.5V  $\leq$  V<sub>DD1</sub>  $\leq$  5.5V, 4.5V  $\leq$  V<sub>DD2</sub>  $\leq$  5.5V, I<sub>F</sub> = 8.0 mA, T<sub>A</sub> = -40°C to +100°C) unless otherwise specified.

All typical specifications are at  $T_A$ =+25°C,  $V_{DD1}$ =  $V_{DD2}$ = +5.0V.

| Parameter                                                        | Symbol           | Min. | Тур. | Max. | Units | Test Conditions                                                                                                             |

|------------------------------------------------------------------|------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------|

| Maximum Data Rate                                                |                  | 10   | 15   |      | MBd   | $R_L = 350\Omega, C_L = 15 \text{ pF}$                                                                                      |

| Pulse Width                                                      | t <sub>PW</sub>  | 100  |      |      | ns    | $R_L = 350 \Omega$ , $C_L = 15 \text{ pF}$                                                                                  |

| Propagation Delay Time to Logic High Output Level <sup>[5]</sup> | t <sub>PLH</sub> |      | 46   | 100  | ns    | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                                                                   |

| Propagation Delay Time to Logic Low Output Level <sup>[6]</sup>  | t <sub>PHL</sub> |      | 43   | 100  | ns    | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                                                                   |

| Pulse Width Distortion   t <sub>PHL</sub> – t <sub>PLH</sub>     | PWD              |      | 5    | 35   | ns    | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                                                                   |

| Propagation Delay Skew <sup>[7]</sup>                            | t <sub>PSK</sub> |      |      | 40   | ns    | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                                                                   |

| Output Rise Time (10 – 90%)                                      | t <sub>R</sub>   |      | 30   |      | ns    | $R_L = 350\Omega, C_L = 15 \text{ pF}$                                                                                      |

| Output Fall Time (10–90%)                                        | t <sub>F</sub>   |      | 12   |      | ns    | $R_L = 350\Omega$ , $C_L = 15 \text{ pF}$                                                                                   |

| Logic High Common Mode Transient Immunity <sup>[8]</sup>         | CM <sub>H</sub>  | 10   |      |      | kV∕µs | $V_{cm}$ = 1000V, I <sub>F</sub> =0 mA,<br>V <sub>0</sub> = 2.0V, R <sub>L</sub> =350\Omega,<br>T <sub>A</sub> = 25°C       |

| Logic Low Common Mode Transient Immunity <sup>[8]</sup>          | CM <sub>L</sub>  | 10   |      |      | kV∕µs | $V_{cm}$ = 1000V, I <sub>F</sub> = 8 mA,<br>V <sub>0</sub> = 0.8V, R <sub>L</sub> = 350 $\Omega$ ,<br>T <sub>A</sub> = 25°C |

#### Notes:

- t<sub>PLH</sub> is measured from the 4.0 mA level on the falling edge of the input pulse to the 1.5V level on the rising edge of the output pulse.

- $\begin{array}{l} \text{6. } t_{\text{PHL}} \text{ is measured from the 4.0 mA level on the} \\ \text{rising edge of the input pulse to the 1.5V level} \\ \text{on the falling edge of the output pulse.} \end{array}$

- t<sub>PSK</sub> is equal to the worst case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that will be seen between units at any given temperature and specified test conditions.

- 8. CM<sub>H</sub> is the maximum common mode voltage slew rate that can be sustained while maintaining  $V_0 > 2.0V$ . CM<sub>L</sub> is the maximum common mode voltage slew rate that can be sustained while maintaining  $V_0 < 0.8V$ . The common mode voltage slew rates apply to both rising and falling common mode voltage edges.

## **Package Characteristics**

All specifications are at  $T_A$ =+25°C.

| Parameter                                                  |             | Symbol                               | Min.                               | Тур.                                 | Max.   | Units            | Test Conditions                                                                                                                                                        |

|------------------------------------------------------------|-------------|--------------------------------------|------------------------------------|--------------------------------------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input-Output Momentary<br>Withstand Voltage <sup>[9]</sup> | SO8<br>SO16 | V <sub>ISO</sub><br>V <sub>ISO</sub> | 2500<br>2500                       |                                      |        | V <sub>RMS</sub> | RH≤50%, t = 1 min<br>RH≤50%, t = 1 min                                                                                                                                 |

| Input-Output Insulation <sup>[10][11]</sup>                | SO8<br>SO16 | <sub>1-0</sub><br>  <sub>1-0</sub>   |                                    |                                      | 5<br>5 | μΑ               | 45% RH, t=5 sec, V <sub>I-0</sub> =3kV DC<br>45% RH, t=5 sec, V <sub>I-0</sub> =3kV DC                                                                                 |

| Input-Output Resistance <sup>[10]</sup>                    | SO8<br>SO16 | R <sub>I-0</sub><br>R <sub>I-0</sub> | 10 <sup>9</sup><br>10 <sup>9</sup> | 10 <sup>11</sup><br>10 <sup>11</sup> |        | Ω                | V <sub>1-0</sub> = 500V DC<br>V <sub>1-0</sub> = 500V DC                                                                                                               |

| Input-Output Capacitance <sup>[10]</sup>                   | SO8<br>SO16 | C <sub>I-0</sub><br>C <sub>I-0</sub> |                                    | 0.7<br>0.7                           |        | pF               | f = 1 MHz<br>f = 1 MHz                                                                                                                                                 |

| Input-Input Insulation<br>Leakage Current <sup>[12]</sup>  | S08<br>S016 | І <sub>І-1</sub><br>І <sub>І-1</sub> |                                    | 0.005<br>0.005                       |        | μΑ               | $\begin{array}{l} RH \leq\!\! 45\%, t\!=\!5 \; \text{sec}, V_{1\!-\!1}\!=\!500V \\ RH \leq\!\! 45\%, t\!=\!5 \; \text{sec}, V_{1\!-\!1}\!=\!500V \end{array}$          |

| Input-Input Resistance <sup>[12]</sup>                     | S08<br>S016 | R <sub>I-I</sub><br>R <sub>I-I</sub> |                                    | 10 <sup>11</sup><br>10 <sup>11</sup> |        | Ω                | $\begin{array}{l} RH \leq\!\! 45\%, t\!=\! 5 \; \text{sec},  V_{1\!-\!1} \!=\! 500V \\ RH \leq\!\! 45\%,  t\!=\! 5 \; \text{sec},  V_{1\!-\!1} \!=\! 500V \end{array}$ |

| Input-Input Capacitance <sup>[12]</sup>                    | SO8<br>SO16 | C <sub>I-I</sub><br>C <sub>I-I</sub> |                                    | 0.1<br>0.12                          |        | pF               | f = 1 MHz<br>f = 1 MHz                                                                                                                                                 |

#### Electrostatic Discharge Sensitivity

This product has been tested for electrostatic sensitivity to the limits stated in the specifications. However, Avago recommends that all integrated circuits be handled with appropriate care to avoid damage. Damage caused by inappropriate handling or storage could range from performance degradation to complete failure.

#### Notes:

- V<sub>ISO</sub> is a dielectric voltage rating that should not be interpreted as an input-output continuous voltage rating. For continuous voltage rating, refer to the IEC/EN/DIN EN 60747-5-2 Insulation Characteristics Table (if applicable), the equipment level safety specification or Avago Application Note 1074 entitled "Optocoupler Input-Output Endurance Voltage."

- 10. Measured between each input pair shorted together and all output connections for that channel shorted together.

- 11. In accordance to UL1577, each optocoupler is proof tested by applying an insulation test voltage  $\geq$  3000 Vrms for 1 sec (leakage detection current limit, I<sub>I-0</sub>  $\leq$  5 µA). This test is performed before the 100% production test for partial discharge (Method b) shown in the IEC/EN/DIN EN 60747-5-2 Insulation Characteristics Table, if applicable.

- 12. Measured between inputs with the LED anode and cathode shorted together.

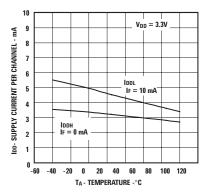

#### **Typical Performance**

Figure 1. Typical input threshold current vs. temperature for 3.3V operation.

Figure 2. Typical input threshold current vs. temperature for 5V operation.

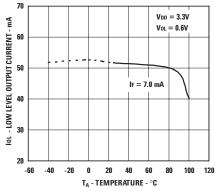

Figure 3. Typical low level output current vs. temperature for 3.3V operation.

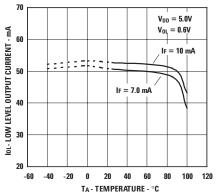

Figure 4. Typical low level output current vs. temperature for 5V operation.

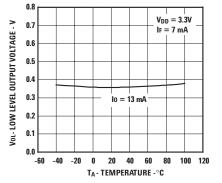

Figure 7. Typical low level output voltage vs. temperature for 3.3V operation.

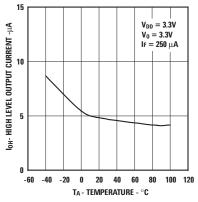

Figure 5. Typical high level output current vs. temperature for 3.3V operation.

Figure 8. Typical low level output voltage vs. temperature for 5V operation.

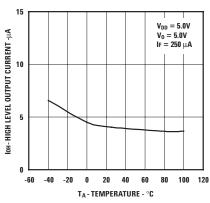

Figure 6. Typical high level output current vs. temperature for 5V operation.

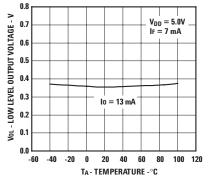

Figure 9. Typical supply current per channel vs. temperature for 3.3V operation.

13

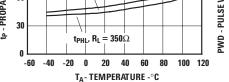

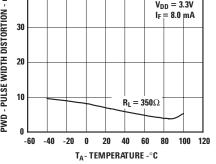

### Typical Performance, continued

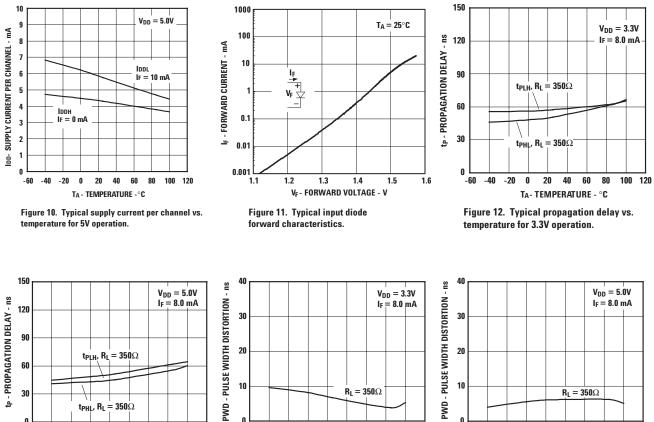

Figure 13. Typical propagation delay vs. temperature for 5V operation.

Figure 14. Typical pulse width distortion vs. temperature for 3.3V operation.

Figure 15. Typical pulse width distortion vs. temperature for 5V operation.

**Test Circuits**

Figure 16. Test circuit for  $t_{PHL},\,t_{PLH},\,t_{F_{\!\!}}$  and  $t_{R}.$

Figure 17. Test circuit for common mode transient immunity and typical waveforms.

# Application Information ON and OFF Conditions

The ACSL-6xx0 series has the ON condition defined by current, and the OFF condition defined by voltage. In order to guarantee that the optocoupler is OFF, the forward voltage across the LED must be less than or equal to 0.8 volt for the entire operating temperature range. This has direct implications for the input drive circuit. If the design uses a TTL gate to drive the input LED, then one has to ensure that the gate output voltage is sufficient to cause the forward voltage to be less than 0.8 volt. The typical threshold current for the ACSL-6xx0 series optocouplers is 2.7 mA; however, this threshold could increase over time due to the aging effects of the LED. Drive circuit arrangements must provide for the ON state LED forward current of at least 7 mA, or more if faster operation is desired.

## Maximum Input Current and Reverse Voltage

The average forward input current should not exceed the 15 mA Absolute Maximum Rating as stated; however, peaking circuits with transient input currents up to 50 mA are allowed provided the average current does not exceed 15 mA. If the input current maximum rating is exceeded, the local temperature of the LED can rise, which in turn may affect the longterm reliability of the device. When designing the input circuit, one must also ensure that the input reverse voltage does not exceed 5V. If the optocoupler is subjected to reverse voltage transients or accidental situations that may cause a reverse voltage to be applied, thus an anti-parallel diode across the LED is recommended.

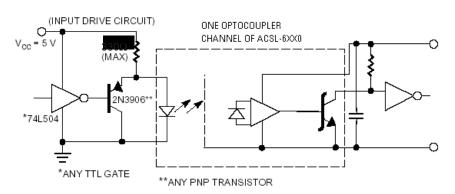

## Suggested Input Circuits for Driving the LED

Figures 18, 19, and 20 show some of the several techniques for driving the ACSL-6xx0 LED. Figure 18 shows the recommended circuit when using any type of TTL gate. The buffer PNP transistor allows the circuit to be used with TTL or CMOS gates that have low sinking current capability. One advantage of this circuit is that there is very little variation in power supply current due to the switching of the optocoupler LED. This can be important in high-resolution analog-to-digital (A/D) systems where ground loop currents due to the switching of the LEDs can cause distortion in the A/D output.

Figure 18. TTL interface circuit for the ACSL-6xx0.

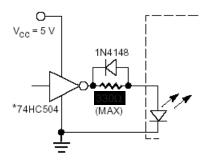

With a CMOS gate to drive the optocoupler, the circuit shown in Figure 19 can be used. The diode in parallel to the current limiting resistor speeds the turn-off of the optocoupler LED. Any HC or HCT series CMOS gate can be used in this circuit.

\*ANY CMOS HC OR HCT GATE

Figure 19. CMOS drive circuit for the ACSL-6xx0.

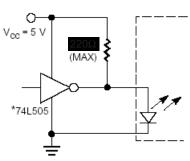

For high common-mode rejection applications, the drive circuit shown in Figure 20 is recommended. In this circuit, only an open-collector TTL, or an open drain CMOS gate can be used. This circuit drives the optocoupler LED with a 220 ohm current-limiting resistor to ensure that an  $I_F$  of 7 mA is applied under worst case conditions and thus guarantee the 10,000 V/ $\mu$ s optocoupler common mode rejection rating. The designer can obtain even higher common-mode rejection performance than 10,000 V/ $\mu$ s by driving the LED harder than 7 mA.

#### **Phase Relationship to Input**

The output of the optocoupler is inverted when compared to the input. The input is defined to be logic HIGH when the LED is ON. If there is a design that requires the optocoupler to behave as a non-inverting gate, then the series input drive circuit shown in Figure 19 can be used. This input drive circuit has an inverting function, and since the optocoupler also behaves as an inverter, the total circuit is noninverting. The shunt drive circuits shown in Figures 18 and 20 will cause the optocoupler to function as an inverter.

#### **Current and Voltage Limitations**

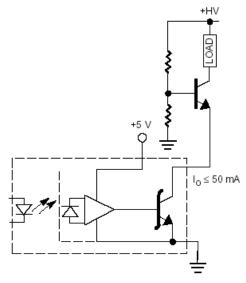

The absolute maximum voltage allowable at the output supply voltage pin and the output voltage pin of the optocoupler is 7 volts. However, the recommended maximum voltage at these two pins is 5.5 volts. The output sinking current should not exceed 13 mA in order to make the Low Level Output Voltage be less than 0.6 volt. If the output voltage is not a consideration, then the absolute maximum current allowed through the ACSL-6xx0 is 50 mA. If the output requires switching either higher currents or voltages, output buffer stages as shown in Figures 21 and 22 are suggested.

Figure 21. High voltage switching with ACSL-6xx0.

\*ANY OPEN COLLECTOR TTL OR OPEN DRAIN CMOS GATE.

Figure 22. High voltage and high current switching with ACSL-6xx0.

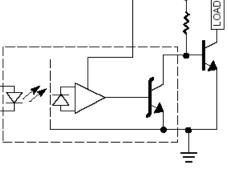

## Propagation Delay, Pulse-Width Distortion and Propagation Delay Skew

Propagation delay is a figure of merit which describes how quickly a logic signal propagates through a system. The propagation delay from low to high  $(t_{PLH})$  is the amount of time required for an input signal to propagate to the output, causing the output to change from low to high. Similarly, the propagation delay from high to low  $(t_{PHL})$  is the amount of time required for the input signal to propagate to the output causing the output to change from high to low (see Figure 16).

Pulse-width distortion (PWD) results when  $t_{PLH}$  and  $t_{PHL}$  differ in value. PWD is defined as the difference between  $t_{PLH}$  and  $t_{PHL}$  and often determines the maximum data rate capability of a transmission system. PWD can be expressed in percent by dividing the PWD (in ns) by the minimum pulse width (in ns) being transmitted. Typically, PWD on the order of 20-30% of the minimum pulse width is tolerable; the exact figure depends on the particular application (RS232, RS422, T-l, etc.).

Propagation delay skew, $t_{PSK}$ , is an important parameter to consider in parallel data applications where synchronization of signals on parallel data lines is a concern. If the parallel data is being sent through a group of optocouplers, differences in propagation delays will cause the data to arrive at the outputs of the optocouplers at different times. If this difference in propagation delays is large enough, it will determine the maximum rate at which parallel data can be sent through the optocouplers.

Propagation delay skew is defined as the difference between the minimum and maximum propagation delays, either  $t_{PLH}$  or  $t_{PHL}$ , for any given group of optocouplers which are operating under the same conditions (i.e., the same drive current, supply voltage, output load, and operating temperature). As illustrated in Figure 23, if the inputs of a group of optocouplers are switched either ON or OFF at the same time,  $t_{PSK}$  is the difference between the shortest propagation delay, either t<sub>PLH</sub> or tPHL, and the longest propagation delay, either  $t_{\rm PLH}$  or  $t_{\rm PHL}.$

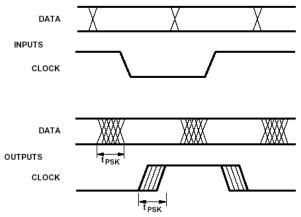

As mentioned earlier,  $t_{PSK}$  can determine the maximum parallel data transmission rate. Figure 24 is the timing diagram of a typical parallel data application with both the clock and the data lines being sent through optocouplers. The figure shows data and clock signals at the inputs and outputs of the optocouplers. To obtain the maximum data transmission rate, both edges of the clock signal are being used to clock the data; if only one edge were used, the clock signal would need to be twice as fast.

Propagation delay skew represents the uncertainty of where an edge might be after being sent through an optocoupler. Figure 24 shows that there will be uncertainty in both the data and the clock lines. It is important that these two areas of uncertainty not overlap, otherwise the clock signal might arrive before all of the data outputs have settled, or some of the data outputs may start to change before the clock signal has arrived. From these considerations, the absolute minimum pulse width that can be sent through optocouplers in a parallel application is twice  $t_{PSK}$ . A cautious design should use a slightly longer pulse width to ensure that any additional uncertainty in the rest of the circuit does not cause a problem.

The  $t_{PSK}$  specified optocouplers offer the advantages of guaranteed specifications for propagation delays, pulsewidth distortion and propagation delay skew over the recommended temperature, input current, and power supply ranges.

For product information and a complete list of distributors, please go to our web site: **www.avagotech.com**

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies, Pte. in the United States and other countries. Data subject to change. Copyright © 2006 Avago Technologies Pte. All rights reserved. Obsoletes 5989-1343EN 5989-2159EN January 16, 2006