## **TMC2246A**

# Image Filter 11 x 10 bit, 60 MHz

#### **Features**

- 60 MHz computation rate

- 60 MHz data and coefficient input

- Four 11 x 10-bit multipliers

- · Individual data and coefficient inputs

- 25-Bit accumulator

- Fractional and integer two's complement data formats

- Input and output data latches with user-configurable enables

- · Selectable 16-bit rounded output

- Internal 1/2 LSB rounding

- · Available in 120-pin CPGA, PPGA, MPGA, or MQFP

#### **Applications**

- · Fast pixel interpolation

- · Fast image manipulation

- · Image mixing and keying

- High-performance FIR filters

- · Adaptive digital filters

- · One- and two-dimensional image processing

#### **Description**

The TMC2246A is a video-speed convolutional array composed of four 11 x 10 bit registered multipliers followed by a summer and an accumulator. All eight multiplier inputs are accessible to the user and may be updated every clock cycle with integer or fractional two's complement data. A pipelined architecture, fully registered input and output ports, and asynchronous three-state output enable control simplify the design of complex systems.

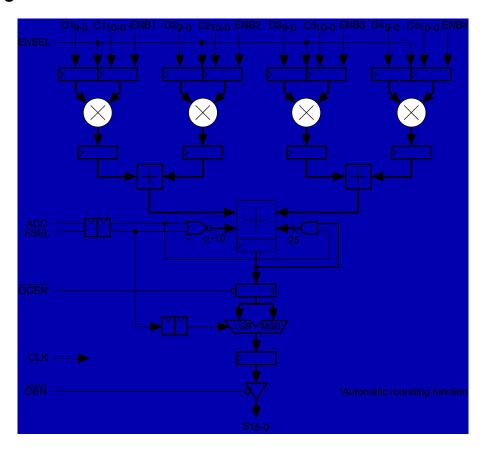

## **Logic Symbol**

The data or coefficient inputs to the multipliers may be held over multiple clock cycles, providing storage for mixing and filtering coefficients. The 25-bit internal accumulator path allows two bits of cumulative word growth and may be internally rounded to 16 bits. Output data are updated every clock cycle, or may be held under user control. All data inputs, outputs, and controls are TTL compatible and (except for the three-state output enable) are registered on the rising edge of CLK.

The TMC2246A is uniquely suited to performing pixel interpolation in image manipulation and filtering applications. As a companion to the Fairchild Semiconductor TMC2301 and TMC2302 Image Manipulation Sequencers, the TMC2246A can execute a bilinear interpolation of an image (4-pixel kernels) at real-time video rates. Larger kernels or other, more complex, functions can be realized with no loss in performance by utilizing multiple devices.

With unrestricted access to all data and coefficient input ports, the TMC2246A offers considerable flexibility in applications performing digital filtering, adaptive FIR filters, mixers, and other similar systems requiring high-speed processing.

Fabricated in a submicron CMOS process, the TMC2246A operates at a guaranteed clock rate of 60 MHz over the full temperature and supply voltage ranges. It is pin- and function-compatible with Fairchild's TMC2246, while providing higher speed operation and lower power dissipation. It is available in a 120 pin Plastic Pin Grid Array (PPGA), 120 pin Ceramic Pin Grid Array (CPGA), 120 lead MQFP to PPGA (MPGA), and a 120 lead Metric Quad FlatPack (MQFP).

#### **Block Diagram**

#### **Functional Description**

The TMC2246A Image Filter is a flexible multiplier-summer array which computes the accumulated sum of four 11x10 bit products, allowing word growth up to 25 bits.

The inputs are user-configurable, allowing latching of either the 10- or 11-bit input data. The data format is user-selectable between integer or fractional two's complement arithmetic. Total latency from input registers to output data port is 5 clocks.

The output data path is 16 bits wide, providing the lower 16 bits of the accumulator when in integer format or the upper 16 bits of the 25-bit accumulator path when fractional two's complement notation is selected. One-time rounding to 16 bits is performed automatically when accumulating fractional data, but is disabled when operating in integer format to maintain the integrity of the least-significant bits.

## **Pin Assignments**

120 Pin Plastic Pin Grid Array, H5 Package, 120 Pin Ceramic Pin Grid Array, G1 Package, and 120 Pin Metric Quad FlatPack to 120 Pin Plastic Pin Array, H6 Package

# **Pin Assignments**

120 Lead Metric Quad Flat Pack (KE) Package

# **Pin Descriptions**

|                    | Pin Nu                                                                  | ımber                                                                |                                                                                                                                                                                                   |

|--------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name           | CPGA/PPGA/<br>MPGA                                                      | MQFP                                                                 | Pin Function Description                                                                                                                                                                          |

| Power              |                                                                         | •                                                                    |                                                                                                                                                                                                   |

| V <sub>DD</sub>    | F3, H3, L7, C8                                                          | 12, 20, 46, 102                                                      | <b>Supply Voltage.</b> The TMC2246A operates from a single +5V supply. All power and ground pins must be connected.                                                                               |

| GND                | E3, G3, J3, L6,<br>H11, C7                                              | 8, 16, 24, 42,<br>72, 106                                            | <b>Ground.</b> The TMC2246A operates from a single +5V supply. All power and ground pins must be connected.                                                                                       |

| Clock              |                                                                         |                                                                      |                                                                                                                                                                                                   |

| CLK                | C3                                                                      | 1                                                                    | System Clock. The TMC2246A operates from a single master clock input. The rising edge of clock strobes all enabled registers. All timing specifications are referenced to the rising edge of CLK. |

| Inputs             |                                                                         |                                                                      |                                                                                                                                                                                                   |

| D1 <sub>9-0</sub>  | M1, K3, L2, N1,<br>L3, M2, N2, L4,<br>M3, N3                            | 27, 28, 29, 30,<br>31, 32, 33, 34,<br>35, 36                         | <b>Data Input Ports.</b> D1 through D4 are the 10-bit data input ports. The LSB is Dx <sub>0</sub> .                                                                                              |

| D2 <sub>9-0</sub>  | J12, K13, J11,<br>K12, L13, L12,<br>K11, M13, M12,<br>L11               | 70, 69, 68, 67,<br>66, 65, 64, 63,<br>62, 61                         |                                                                                                                                                                                                   |

| D3 <sub>9-0</sub>  | J13, H12, H13,<br>G12, G11, G13,<br>F13, F12, F11,<br>E13               | 71, 73, 74, 75,<br>76, 77, 78, 79,<br>80, 81                         |                                                                                                                                                                                                   |

| D4 <sub>9-0</sub>  | B4, C5, A4, B5,<br>A5, C6, B6, A6,<br>A7, B7                            | 115, 114, 113,<br>112, 111, 110,<br>109, 108, 107,<br>105            |                                                                                                                                                                                                   |

| C1 <sub>10-0</sub> | M4, L5, N4, M5,<br>N5, M6, N6, M7,<br>N7, N8, M8                        | 37, 38, 39, 40,<br>41, 43, 44, 45,<br>47, 48, 49                     | Coefficient Input Ports. C1 through C4 are the 11-bit coefficient input ports. The LSB is $\mathrm{Cx}_0$ .                                                                                       |

| C2 <sub>10-0</sub> | N13, M11, L10,<br>N12, N11, M10,<br>L9, N10, M9,<br>N9, L8              | 60, 59, 58, 57,<br>56, 55, 54, 53,<br>52, 51, 50                     |                                                                                                                                                                                                   |

| C3 <sub>10-0</sub> | E12, D13, E11,<br>D12, C13, B13,<br>D11, C12, A13,<br>C11, B12          | 82, 83, 84, 85,<br>86, 87, 88, 89,<br>90, 91, 92                     |                                                                                                                                                                                                   |

| C4 <sub>10-0</sub> | A8, B8, A9, B9,<br>A10, C9, B10,<br>A11, B11, C10,<br>A12               | 104, 103, 101,<br>100, 99, 98, 97,<br>96, 95, 94, 93                 |                                                                                                                                                                                                   |

| Outputs            |                                                                         |                                                                      |                                                                                                                                                                                                   |

| S <sub>15-0</sub>  | C1, D2, D1, E2,<br>E1, F2, F1, G2,<br>G1, H1, H2, J1,<br>J2, K1, K2, L1 | 6, 7, 9, 10, 11,<br>13, 14, 15, 17,<br>18, 19, 21, 22,<br>23, 25, 26 | Sum Output. The current 16-bit result is available at the Sum output. The LSB is $S_0$ . See the Functional Block Diagram.                                                                        |

# Pin Descriptions (continued)

|               | Pin Nu             | ımber                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|--------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name      | CPGA/PPGA/<br>MPGA | MQFP                  | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Controls      |                    | 1                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FSEL          | B2                 | 2                     | Format Select. Coefficients input during the current clock are assumed to be in fractional two's complement format. Rounding to 16 bits is performed as determined by the accumulator control, ACC, and the upper 16 bits of the accumulator are output when the registered Format Select input (FSEL) is LOW. When FSEL is HIGH, two's complement integer format is assumed, and the lower 16 bits of the accumulator are presented at the output. No rounding is performed when operating in integer mode. See the Functional Block Diagram and the Applications Discussion. |

| ENSEL         | A1                 | 120                   | Enable Select. The registered Enable Select determines whether the data or the coefficient input registers may be held on the next rising edge of clock, in conjunction with the individual input enables ENB1–ENB4. See Table 1.                                                                                                                                                                                                                                                                                                                                              |

| ENB1–<br>ENB4 | C4, A2, A3, B3     | 118, 117, 116,<br>119 | Input Enables. When ENBi (i=1, 2, 3, or 4) is LOW, registers Ci and Di are both strobed by the next rising edge of CLK. When ENBi is HIGH and ENSEL is LOW, Di is strobed, but Ci is held. When ENBi and ENSEL are both HIGH, Di is held and Ci is strobed. See Table 1. Thus, either or both input registers to each multiplier are updated on each clock cycle.                                                                                                                                                                                                              |

| ACC           | B1                 | 3                     | Accumulate. When the registered ACCumulator control is LOW, no internal accumulation will be performed on the data input during the current clock, effectively clearing the prior accumulated sum. If operating in fractional two's complement format (FSEL = LOW), one-half LSB rounding to 16 bits is performed on the result. This allows the user to perform summations without propagating roundoff errors.                                                                                                                                                               |

|               |                    |                       | When ACC is HIGH, the internal accumulator adds the emerging products to the sum of previous products, without performing additional rounding.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OCEN          | D3                 | 4                     | Output Register Enable. The output of the accumulator is latched into the output register on the next clock when the Output Register Clock Enable is LOW. When OCEN is HIGH the contents of the output register remain unchanged; however, accumulation will continue internally if ACC remains HIGH.                                                                                                                                                                                                                                                                          |

| ŌĒÑ           | C2                 | 5                     | <b>Output Enable.</b> Data currently in the output registers is available at the output bus $S_{15-0}$ when the asynchronous Output Enable is LOW. When $\overline{\text{OEN}}$ is HIGH, the outputs are in the high-impedance state.                                                                                                                                                                                                                                                                                                                                          |

| No Connec     | et                 |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NC            | D4 (Index Pin)     |                       | Not Connected. (Optional)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### Note:

- 1. X denotes a "Don't Care" condition.

- 2. Any register not explicitly held is updated on the next rising edge of CLK.

**Table 1. Input Register Control**

| ENB1-4 | ENSEL | Input Register Held |

|--------|-------|---------------------|

| 1      | 1     | Data i              |

| 1      | 0     | Coefficient i       |

| 0      | Х     | None                |

#### **Data Formats**

#### Fractional Two's Complement Format (FSEL = LOW)

| 15              | 14                    | 13             | 12                    | 11                    | 10              | 9                 | 8               | 7                      | 6               | 5               | 4                      | 3               | 2               | 1               | 0               |

|-----------------|-----------------------|----------------|-----------------------|-----------------------|-----------------|-------------------|-----------------|------------------------|-----------------|-----------------|------------------------|-----------------|-----------------|-----------------|-----------------|

|                 |                       |                | -                     |                       |                 | -2 <sup>0</sup> . | 2 <sup>-1</sup> | 2 <sup>-2</sup>        | 2 <sup>-3</sup> | 2 <sup>-4</sup> | 2 <sup>-5</sup>        | 2 <sup>-6</sup> | 2 <sup>-7</sup> | 2 <sup>-8</sup> | 2 <sup>-9</sup> |

|                 |                       |                |                       |                       | -2 <sup>1</sup> | 2 <sup>0</sup> .  | 2 <sup>-1</sup> | <b>2</b> <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup> | <b>2</b> <sup>-5</sup> | 2 <sup>-6</sup> | 2 <sup>-7</sup> | 2 <sup>-8</sup> | 2 <sup>-9</sup> |

| -2 <sup>6</sup> | <b>2</b> <sup>5</sup> | 2 <sup>4</sup> | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>  | 2 <sup>0</sup> .  | 2 <sup>-1</sup> | 2 <sup>-2</sup>        | 2 <sup>-3</sup> | 2 <sup>-4</sup> | 2 <sup>-5</sup>        | 2 <sup>-6</sup> | 2 <sup>-7</sup> | 2 <sup>-8</sup> | 2 <sup>-9</sup> |

BIT DATA (D1-4) COEFFICIENT (C1-4) SUM

#### Integer Two's Complement Format (FSEL = HIGH)

| 15               | 14              | 13              | 12  | 11              | 10               | 9                     | 8              | 7  | 6              | 5                     | 4              | 3                     | 2                     | 1              | 0                |

|------------------|-----------------|-----------------|-----|-----------------|------------------|-----------------------|----------------|----|----------------|-----------------------|----------------|-----------------------|-----------------------|----------------|------------------|

|                  |                 |                 |     |                 |                  | -2 <sup>9</sup>       | 2 <sup>8</sup> | 27 | 2 <sup>6</sup> | <b>2</b> <sup>5</sup> | 2 <sup>4</sup> | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | 2 <sup>1</sup> | 2º.              |

|                  |                 |                 |     |                 | -2 <sup>10</sup> | <b>2</b> <sup>9</sup> | 2 <sup>8</sup> | 27 | 2 <sup>6</sup> | <b>2</b> <sup>5</sup> | 2 <sup>4</sup> | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | 2 <sup>1</sup> | 2º.              |

| -2 <sup>15</sup> | 2 <sup>14</sup> | 2 <sup>13</sup> | 212 | 2 <sup>11</sup> | 2 <sup>10</sup>  | <b>2</b> <sup>9</sup> | 2 <sup>8</sup> | 27 | 2 <sup>6</sup> | <b>2</b> <sup>5</sup> | 2 <sup>4</sup> | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> . |

BIT DATA (D1-4) COEFFICIENT (C1-4) SUM

#### Integer Two's Complement Data / Fractional Two's Complement Coefficient Format (FSEL = LOW)

| 15               | 14              | 13              | 12              | 11              | 10              | 9                | 8               | 7               | 6               | 5                     | 4               | 3                     | 2                     | 1               | 0                |

|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|-----------------|-----------------|-----------------|-----------------------|-----------------|-----------------------|-----------------------|-----------------|------------------|

|                  |                 |                 | -               |                 |                 | -2 <sup>9</sup>  | 2 <sup>8</sup>  | 2 <sup>7</sup>  | 2 <sup>6</sup>  | <b>2</b> <sup>5</sup> | 2 <sup>4</sup>  | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>  | 2º.              |

|                  |                 |                 |                 |                 | -2 <sup>1</sup> | 2 <sup>0</sup> . | 2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup>       | 2 <sup>-5</sup> | 2 <sup>-6</sup>       | 2 <sup>-7</sup>       | 2 <sup>-8</sup> | 2 <sup>-9</sup>  |

| -2 <sup>15</sup> | 2 <sup>14</sup> | 2 <sup>13</sup> | 2 <sup>12</sup> | 2 <sup>11</sup> | 2 <sup>10</sup> | 2 <sup>9</sup>   | 2 <sup>8</sup>  | 2 <sup>7</sup>  | 2 <sup>6</sup>  | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>        | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>  | 2 <sup>0</sup> . |

BIT DATA (D1-4) COEFFICIENT (C1-4) SUM

Note: A minus sign indicates the sign bit.

Figure 1. Data Formats

# **Equivalent Circuits and Threshold Levels**

Figure 2. Equivalent Digital Input Circuit

Figure 3. Equivalent Digital Output Circuit

Figure 4. Threshold Levels for Three-State Measurement

## Absolute Maximum Ratings (beyond which the device may be damaged)<sup>1</sup>

| Parameter                                                              | Min  | Max                   | Unit |

|------------------------------------------------------------------------|------|-----------------------|------|

| Supply Voltage                                                         | -0.5 | 7.0                   | V    |

| Input Voltage                                                          | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Output, Applied Voltage <sup>2</sup>                                   | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Output, Externally Forced Current <sup>3,4</sup>                       | -3.0 | 6.0                   | mA   |

| Output, Short Circuit Duration (single output in HIGH state to ground) |      | 1                     | sec  |

| Operating, Ambient Temperature                                         | -20  | 110                   | °C   |

| Junction Temperature                                                   |      | 140                   | °C   |

| Storage Temperature                                                    | -65  | 150                   | °C   |

| Lead Soldering (10 seconds)                                            |      | 300                   | °C   |

#### Notes:

- 1. Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if Operating Conditions are not exceeded.

- 2. Applied voltage must be current limited to specified range.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

## **Operating Conditions**

| Param            | eter                           |            | Min  | Nom | Max  | Units |

|------------------|--------------------------------|------------|------|-----|------|-------|

| V <sub>DD</sub>  | Power Supply Voltage           |            | 4.75 | 5.0 | 5.25 | V     |

| f <sub>CLK</sub> | Clock frequency                | TMC2246A   |      |     | 30   | MHz   |

|                  |                                | TMC2246A-1 |      |     | 40   | MHz   |

|                  |                                | TMC2246A-2 |      |     | 60   | MHz   |

| t <sub>PWH</sub> | CLK pulse width, HIGH          |            | 8    |     |      | ns    |

| t <sub>PWL</sub> | CLK pulse width, LOW           |            | 6    |     |      | ns    |

| t <sub>S</sub>   | Input Data Set-up Time         |            | 6    |     |      | ns    |

| t <sub>H</sub>   | Input Data Hold Time           |            | 1.5  |     |      | ns    |

| V <sub>IH</sub>  | Input Voltage, Logic HIGH      |            | 2.0  |     |      | V     |

| V <sub>IL</sub>  | Input Voltage, Logic LOW       |            |      |     | 0.8  | V     |

| I <sub>OH</sub>  | Output Current, Logic HIGH     |            |      |     | -2.0 | mA    |

| I <sub>OL</sub>  | Output Current, Logic LOW      |            |      |     | 4.0  | mA    |

| T <sub>A</sub>   | Ambient Temperature, Still Air |            | 0    |     | 70   | °C    |

## **Electrical Characteristics**

| Param            | neter                                       | Conditions                                                           | Min | Тур | Max | Units |

|------------------|---------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>DD</sub>  | Total Power Supply Current                  | $V_{DD} = Max, C_{LOAD} = 25pF, f_{CLK} = Max$                       |     |     |     |       |

|                  |                                             | TMC2246A                                                             |     |     | 95  | mA    |

|                  |                                             | TMC2246A-1                                                           |     |     | 120 | mA    |

|                  |                                             | TMC2246A-2                                                           |     |     | 170 | mA    |

| I <sub>DDU</sub> | Power Supply Current,                       | V <sub>DD</sub> = Max, <del>OEN</del> = HIGH, f <sub>CLK</sub> = Max |     |     |     |       |

|                  | Unloaded                                    | TMC2246A                                                             |     |     | 80  | mA    |

|                  |                                             | TMC2246A-1                                                           |     |     | 100 | mA    |

|                  |                                             | TMC2246A-2                                                           |     |     | 140 | mA    |

| I <sub>DDQ</sub> | Power Supply Current,<br>Quiescent          | V <sub>DD</sub> = Max, CLK = LOW                                     |     |     | 5   | mA    |

| C <sub>PIN</sub> | I/O Pin Capacitance                         |                                                                      |     | 5   |     | pF    |

| I <sub>IH</sub>  | Input Current, HIGH                         | $V_{DD} = Max, V_{IN} = V_{DD}$                                      |     |     | ±10 | μA    |

| I <sub>IL</sub>  | Input Current, LOW                          | $V_{DD} = Max, V_{IN} = 0 V$                                         |     |     | ±10 | μA    |

| l <sub>OZH</sub> | Hi-Z Output Leakage Current,<br>Output HIGH | $V_{DD} = Max, V_{IN} = V_{DD}$                                      |     |     | ±10 | μA    |

| I <sub>OZL</sub> | Hi-Z Output Leakage Current,<br>Output LOW  | $V_{DD} = Max, V_{IN} = 0 V$                                         |     |     | ±10 | μA    |

| los              | Short-Circuit Current                       |                                                                      | -20 |     | -80 | mA    |

| V <sub>OH</sub>  | Output Voltage, HIGH                        | S <sub>15-0</sub> , I <sub>OH</sub> = Max                            | 2.4 |     |     | V     |

| V <sub>OL</sub>  | Output Voltage, LOW                         | S <sub>15-0</sub> , I <sub>OL</sub> = Max                            |     |     | 0.4 | V     |

# **Switching Characteristics**

| Paramo           | eter                             | Conditions <sup>1</sup>   | Min | Тур | Max | Units |

|------------------|----------------------------------|---------------------------|-----|-----|-----|-------|

| t <sub>DO</sub>  | Output Delay Time                | C <sub>LOAD</sub> = 25 pF |     |     | 14  | ns    |

| t <sub>HO</sub>  | Output Hold Time                 | C <sub>LOAD</sub> = 25 pF | 4   |     |     | ns    |

| t <sub>ENA</sub> | Three-State Output Enable Delay  | C <sub>LOAD</sub> = 0 pF  |     |     | 10  | ns    |

| t <sub>DIS</sub> | Three-State Output Disable Delay | C <sub>LOAD</sub> = 0 pF  |     |     | 10  | ns    |

#### Note:

<sup>1.</sup> All transitions are measured at a 1.5V level except for  $t_{\mbox{\footnotesize{ENA}}}$  and  $t_{\mbox{\footnotesize{DIS}}}.$

#### **Timing Diagram**

#### **Application Notes**

#### **Typical Operation**

The versatile input clock enables and unrestricted data and coefficient inputs provided on the TMC2246A allow considerable flexibility in numerous image and signal processing architectures.

Table 2 shows a typical sequence of operations which clarifies the inherent latencies of the device and illustrates fixed coefficient storage, product accumulation, and device reconfiguration prior to beginning a new accumulation. This assumes that the device is set to fractional two's complement mode (FSEL = LOW) with  $\overline{OCEN}$  = LOW,  $\overline{OEN}$  = LOW, and the input registers configured to hold coefficients only (ENSEL = LOW). X= "don't care."

#### Using the TMC2246A for Pixel Interpolation

As a companion product to the TMC2301 Image Resampling Sequencer, the TMC2246A offers an excellent tool for performing high-speed pixel interpolation and image filtering.

Any pixel resampling operation with multiple-pixel kernels must utilize some parallel-processing technique, such as memory banding, to maintain high-speed image throughput rates. Memory banding utilizes adders to generate parallel offset addresses, allowing the user to access multiple pixel locations simultaneously. Using such techniques, one TMC2246A can perform bilinear interpolation (four-pixel kernel) with no loss in system performance.

Larger kernels can be realized in similar systems with additional TMC2246As. Figure 5 illustrates a basic pixel interpolation application.

Table 2. Typical TMC2246A Operation Sequence

| CLK | D1    | C1    | ENB1 | D2    | C2    | ENB2 | D3    | C3    | ENB3 | D4    | C4    | ENB4 | ACC | Sum                                                                    |

|-----|-------|-------|------|-------|-------|------|-------|-------|------|-------|-------|------|-----|------------------------------------------------------------------------|

| 0   | -     | -     | 0    | -     | -     | 0    | -     | -     | 0    | -     | -     | 0    | -   | -                                                                      |

| 1   | D1(1) | C1(1) | 1    | D2(1) | C2(1) | 1    | D3(1) | C3(1) | 1    | D4(1) | C4(1) | 1    | 0   | -                                                                      |

| 2   | D1(2) | Х     | 0    | D2(2) | C2(2) | 0    | D3(2) | Х     | 1    | D4(2) | Х     | 1    | 1   | -                                                                      |

| 3   | D1(3) | C1(3) | 0    | D2(3) | C2(3) | 0    | D3(3) | Х     | 0    | D4(3) | Х     | 0    | 1   |                                                                        |

| 4   | D1(4) | C1(4) | -    | D2(4) | C2(4) | -    | D3(4) | C3(4) | -    | D4(4) | C4(4) | -    | 0   |                                                                        |

| 5   |       |       |      |       |       |      |       |       |      |       |       |      |     | S(5)=D1(1)C1(1)+D2(1)C2(1)<br>+D3(1)C3(1)+D4(1)C4(1)+ 2 <sup>-10</sup> |

| 6   |       |       |      |       |       |      |       |       |      |       |       |      |     | S(6)=S(5)+D1(2)C1(1)+D2(2)C2(1)<br>+D3(2)C3(1)+D4(2)C4(1)              |

| 7   |       |       |      |       |       |      |       |       |      |       |       |      |     | S(7)=S(6)+D1(3)C1(3)+D2(3)C2(3)<br>+D3(3)C3(1)+D4(3)C4(1)              |

| 8   |       |       |      |       |       |      |       |       |      |       |       |      |     | S(8)=D1(4)C1(4)+D2(4)C2(4)<br>+D3(4)C3(4)+D4(4)C4(4)+2 <sup>-10</sup>  |

Notice in this example, operating in fractional two's complement mode, that rounding is imposed on the first cycle only of an accumulation. This avoids the propagation of accumulated roundoff errors.

Figure 5. Bilinear Interpolation Using the TMC2246A

# TMC2246A Applications in Digital Filtering

Unrestricted access to all input ports of the TMC2246A allows the user considerable flexibility in realizing numerous digital filter architectures. Figure 6 illustrates how the device may be utilized as a flexible high-speed FIR filter with the ability to modify all of the filter coefficients dynamically or to store a fixed set if desired.

Longer filters, with more taps, are realized by including an external adder (such as the common 74381 type) to cascade multiple TMC2246As. Alternatively, two additional taps and a cascading adder are available in the Fairchild TMC2249A Digital Mixer.

Figure 6. Using the TMC2246A For FIR Filtering

#### **Related Products**

- TMC2301 Image Resampling Sequencer

- TMC2302A Image Manipulation Sequencer

- TMC2249A Video Mixer

- TMC2242B Half-Band Filter

## **Mechanical Dimensions**

## 120-Lead CPGA Package

## **Mechanical Dimensions**

## 120-Lead PPGA Package

## **Mechanical Dimensions**

120-Lead Metric Quad Flat Package to Pin Grid Array Package (MPGA)

# **Mechanical Dimensions**

## 120-Lead MQFP Package

#### **Ordering Information**

| Product<br>Number | Temperature<br>Range | Speed<br>Grade | Screening  | Package                                             | Package<br>Marking |

|-------------------|----------------------|----------------|------------|-----------------------------------------------------|--------------------|

| TMC2246AG1C       | 0°C to 70°C          | 30 MHz         | Commercial | 120 Pin Ceramic Pin Grid Array                      | 2246AG1C           |

| TMC2246AG1C1      | 0°C to 70°C          | 40 MHz         | Commercial | 120 Pin Ceramic Pin Grid Array                      | 2246AG1C1          |

| TMC2246AG1C2      | 0°C to 70°C          | 60 MHz         | Commercial | 120 Pin Ceramic Pin Grid Array                      | 2246AG1C2          |

| TMC2246AH5C       | 0°C to 70°C          | 30 MHz         | Commercial | 120 Pin Plastic Pin Grid Array                      | 2246AH5C           |

| TMC2246AH5C1      | 0°C to 70°C          | 40 MHz         | Commercial | 120 Pin Plastic Pin Grid Array                      | 2246AH5C1          |

| TMC2246AH5C2      | 0°C to 70°C          | 60 MHz         | Commercial | 120 Pin Plastic Pin Grid Array                      | 2246AH5C2          |

| TMC2246AH6C       | 0°C to 70°C          | 30 MHz         | Commercial | 120 Lead Metric Quad Flat Pack<br>to Pin Grid Array | N/A                |

| TMC2246AH6C1      | 0°C to 70°C          | 40 MHz         | Commercial | 120 Lead Metric Quad Flat Pack<br>to Pin Grid Array | N/A                |

| TMC2246AH6C2      | 0°C to 70°C          | 60 MHz         | Commercial | 120 Lead Metric Quad Flat Pack<br>to Pin Grid Array | N/A                |

| TMC2246AKEC       | 0°C to 70°C          | 30 MHz         | Commercial | 120 Lead Metric Quad FlatPack                       | 2246AKEC           |

| TMC2246AKEC1      | 0°C to 70°C          | 40 MHz         | Commercial | 120 Lead Metric Quad FlatPack                       | 2246AKEC1          |

| TMC2246AKEC2      | 0°C to 70°C          | 60 MHz         | Commercial | 120 Lead Metric Quad FlatPack                       | 2246AKEC2          |

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### **LIFE SUPPORT POLICY**

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.