# L6460

## SPI configurable stepper and DC multi motor driver

#### Features

- Operating supply voltage from 13 V to 38 V

- 4 full bridge driver configurable in multi-motor application to drive:

- 2 DC and 1 stepper motor

- 4 DC motor

- Bridge 1 and 2 (R<sub>DSon</sub> = 0.60 Ω) can be configured to work as:

- Dual full bridge driver

- Super DC driver

- 2 half bridge driver

- 1 super half bridge

- 2 power switches

- 1 super power switch

- Bridge 3 and 4 (R<sub>DSon</sub> = 0.85 Ω) can be configured to work as:

- Same as bridges 1 and 2, listed above

- Stepper motor driver: up to 1/16 microstepping

- 2 buck regulators (bridge 3)

- 1 super buck regulator

- Battery charger (bridge 4)

- Power supply management

- One switching buck regulator

- One switching regulator controller

- One linear regulator

- One battery charger

- Fully protected through

- Thermal warning and shutdown

- Overcurrent protection

- Undervoltage lock-out

- SPI interface

- Programmable watchdog function

- Integrated power sequencing and supervisory functions with fault signaling through serial interface and external reset pin

- Very low power dissipation in shut-down mode (~35 mW)

- Auxiliary features

- Multi-channels 9 bit ADC

- 2 operational amplifiers

- Digital comparator

- 2 low voltage power switches

- 3 general purpose PWM generators

- 14 GPIOs

### Description

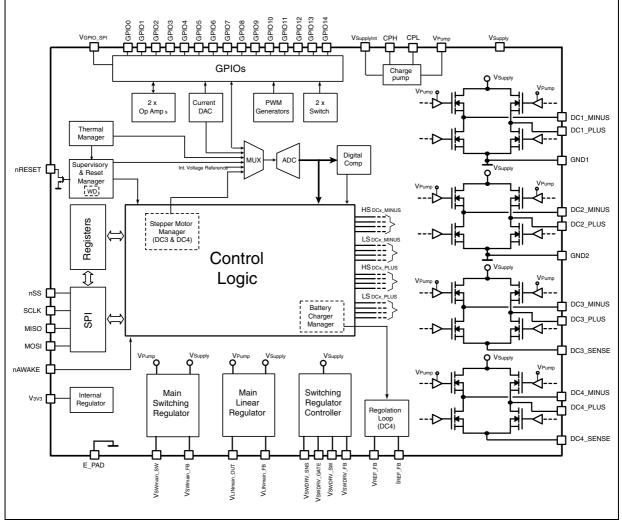

The L6460 is optimized to control and drive multimotor system providing a unique level of integration in term of control, power and auxiliary features. Thanks to the high configurability L6460 can be customized to drive different motor architectures and to optimize the number of embedded features, such as the voltage regulators, the high precision A/D converter, the operational amplifier and the voltage comparators. The possibility to drive simultaneously stepper and DC motor makes L6460 the ideal solution for all the application featuring multi motors.

#### Table 1. Device summary

| Order code | Package | Packing       |

|------------|---------|---------------|

| L6460      | TQFP64  | Tray          |

| L6460TR    | TQFF04  | Tape and reel |

Doc ID 17713 Rev 1

## Contents

| 1 | Gen   | eral description                                               |

|---|-------|----------------------------------------------------------------|

|   | 1.1   | Overview                                                       |

|   | 1.2   | Pin connection                                                 |

|   | 1.3   | Pin list                                                       |

| 2 | L646  | 60's main features                                             |

| 3 | Elec  | trical specifications                                          |

|   | 3.1   | Absolute maximum rating 16                                     |

|   | 3.2   | Operating ratings specifications 16                            |

|   | 3.3   | Electrical characteristics 17                                  |

| 4 | Inter | nal supplies                                                   |

|   | 4.1   | V <sub>SupplyInt</sub> regulator                               |

|   | 4.2   | Charge pump regulator                                          |

|   | 4.3   | V3v3 regulator                                                 |

| 5 | Supe  | ervisory system                                                |

|   | 5.1   | Power on reset (POR) circuit                                   |

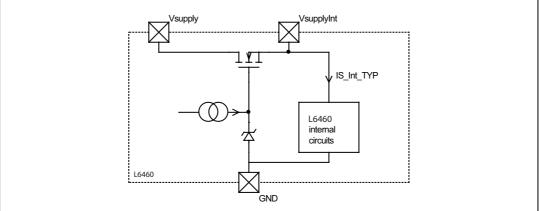

|   | 5.2   | nRESET generation circuit 32                                   |

|   | 5.3   | Thermal shut down generation circuit                           |

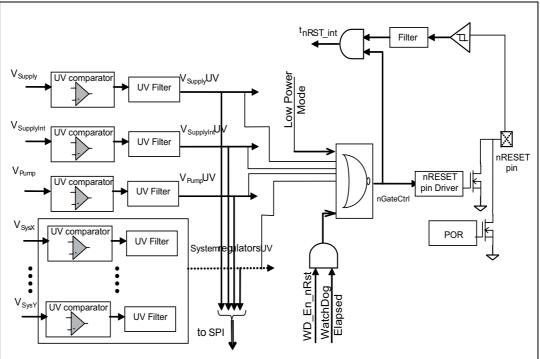

| 6 | Wate  | chdog circuit                                                  |

| 7 | Inter | nal clock oscillator                                           |

| 8 | Star  | t-up configurations                                            |

|   | 8.1   | Operation modes                                                |

|   | 8.2   | Basic device mode 40                                           |

|   | 8.3   | Slave device mode                                              |

|   | 8.4   | Master device mode 41                                          |

|   | 8.5   | Single device mode                                             |

|   | 8.6   | Sub-configurations for slave, master or single device modes 41 |

|    |       | 8.6.1    | Bridge mode                                         | 41    |

|----|-------|----------|-----------------------------------------------------|-------|

|    |       | 8.6.2    | Primary regulator mode (KP)                         | 42    |

|    |       | 8.6.3    | Regulators mode                                     | 42    |

|    |       | 8.6.4    | Simple regulator mode (KT)                          | 42    |

|    |       | 8.6.5    | Bridge + V <sub>EXT</sub> mode                      | 42    |

|    |       | 8.6.6    | Secondary regulators mode                           | 43    |

| 9  | Powe  | er sequ  | encing                                              | 44    |

| 10 | Powe  | er savin | ig modes                                            | 45    |

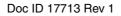

|    | 10.1  | Standt   | by mode                                             | 45    |

|    | 10.2  | Hibern   | ate mode                                            |       |

|    | 10.3  | Low po   | ower mode                                           |       |

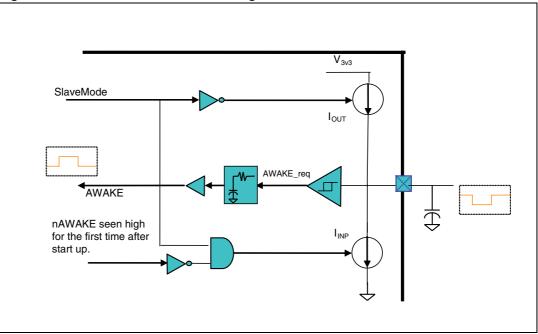

|    | 10.4  | nAWAI    | KE pin                                              | 46    |

| 11 | Linea | ar main  | regulator                                           | 48    |

| 12 | Main  | switch   | ing regulator                                       | 50    |

|    | 12.1  | Pulse    | skipping operation                                  | 50    |

| 13 | Swite | ching re | egulator controller                                 |       |

|    | 13.1  | Pulse    | skipping operation                                  |       |

|    | 13.2  | Output   | t equivalent circuit                                |       |

|    | 13.3  | Switch   | ing regulator controller application considerations | 54    |

| 14 | Powe  | er bridg | jes                                                 | 56    |

|    | 14.1  | Possib   | le configurations                                   |       |

|    |       | 14.1.1   | Full bridge                                         | 60    |

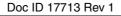

|    |       | 14.1.2   | Parallel configuration (super bridge)               | 61    |

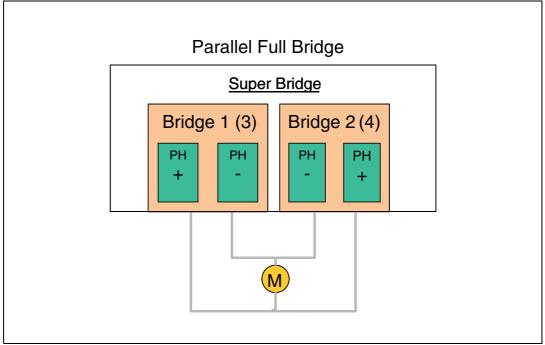

|    |       | 14.1.3   | Half bridge configuration                           | 61    |

|    |       | 14.1.4   | Switch configuration                                | 63    |

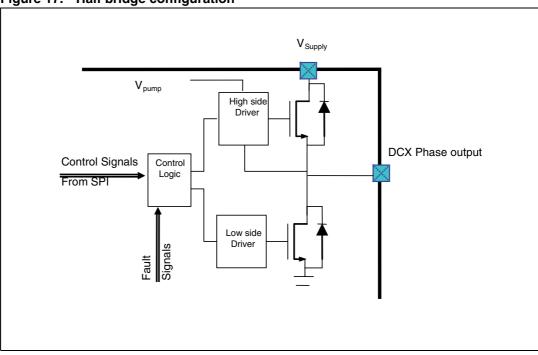

|    |       | 14.1.5   | Bipolar stepper configuration                       | 63    |

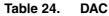

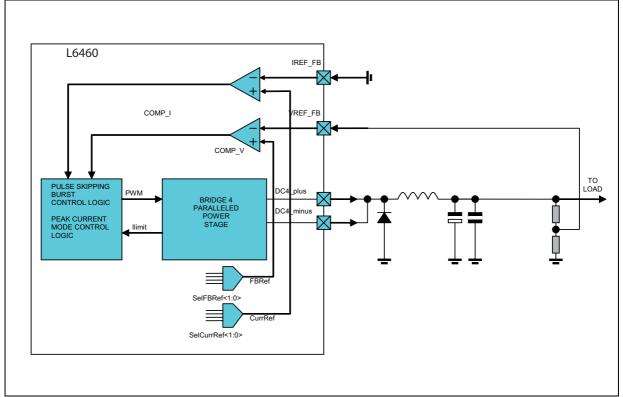

|    |       | 14.1.6   | Synchronous buck regulator configuration (Bridge 3) | 73    |

|    |       | 14.1.7   | Regulation loop                                     |       |

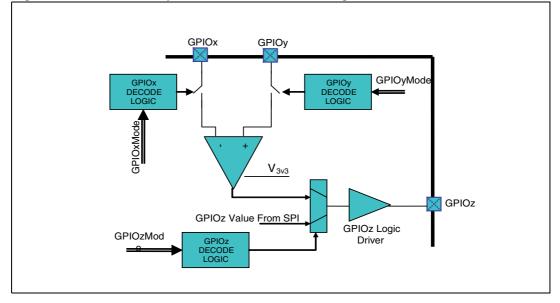

|    |       | 14.1.8   | Battery charger or switching regulator (Bridge 4)   | 76    |

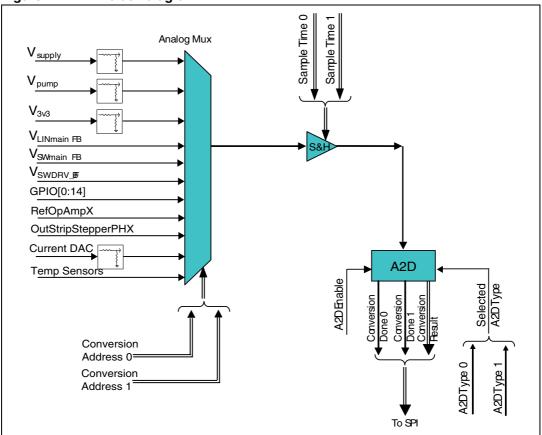

| 15 | AD c  | onverte  | er                                                  |       |

| 57 |       |          | Doc ID 17713 Rev 1                                  | 3/139 |

57

|    | 15.1   | Voltage divider specifications 84                                       |

|----|--------|-------------------------------------------------------------------------|

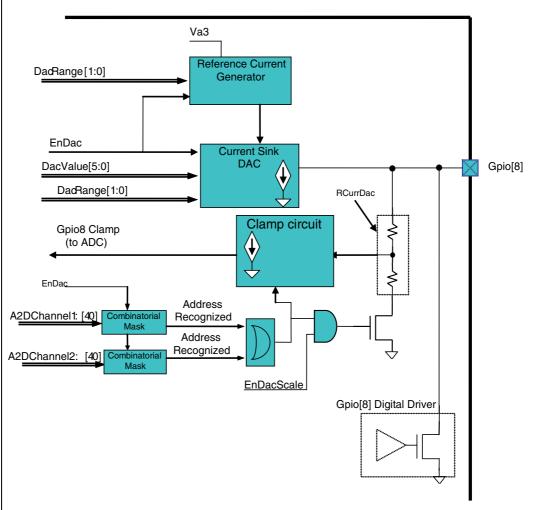

| 16 | Curre  | nt DAC circuit                                                          |

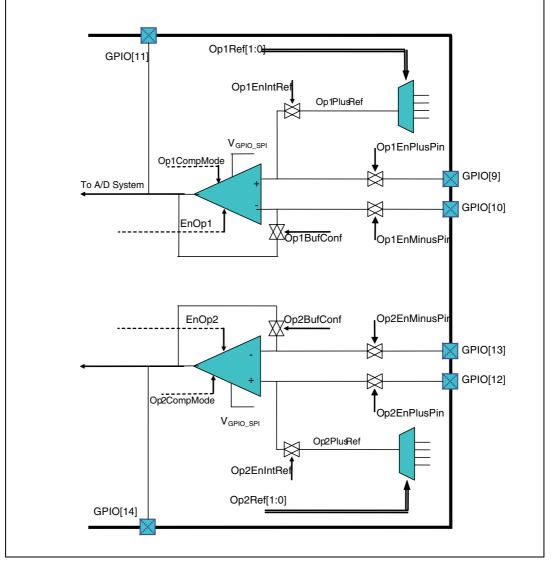

| 17 | Opera  | ational amplifiers                                                      |

| 18 | Low v  | voltage power switches                                                  |

| 19 | Gene   | ral purpose PWM90                                                       |

|    | 19.1   | General purpose PWM generators 1 and 2 (AuxPwm1 and AuxPwm2) $\ . \ 90$ |

|    | 19.2   | Programmable PWM generator (GpPwm) 90                                   |

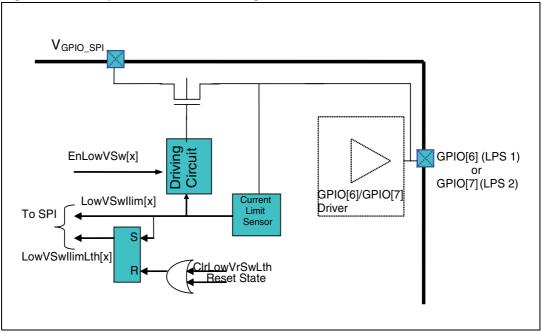

| 20 | Interr | upt controller                                                          |

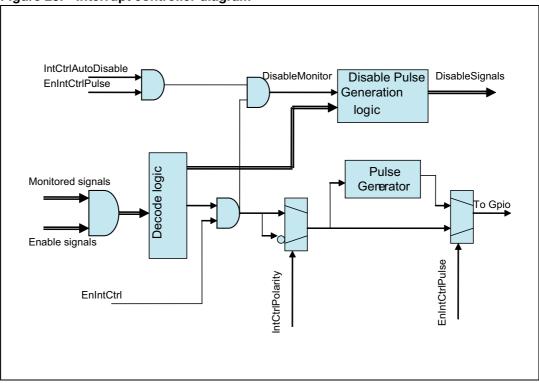

| 21 | Digita | Il comparator                                                           |

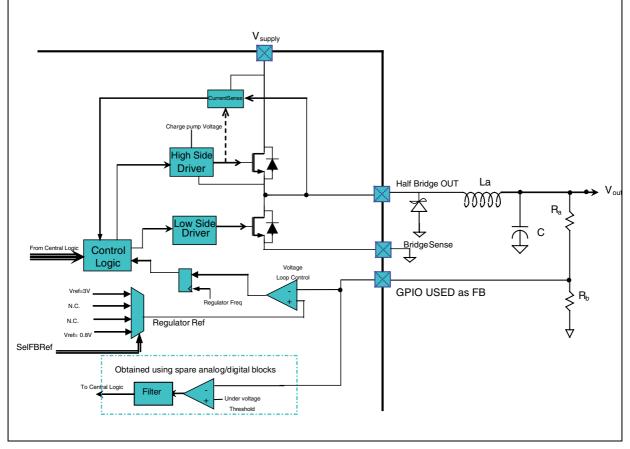

| 22 | GPIO   | pins                                                                    |

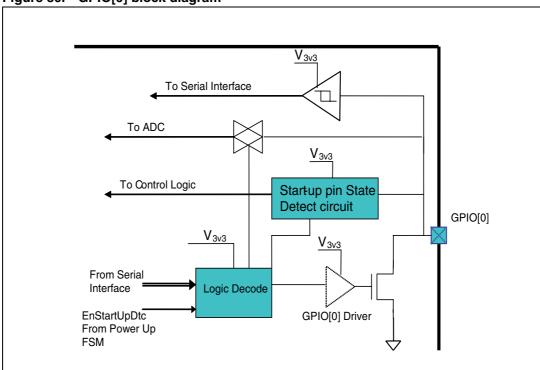

|    | 22.1   | GPIO[0]                                                                 |

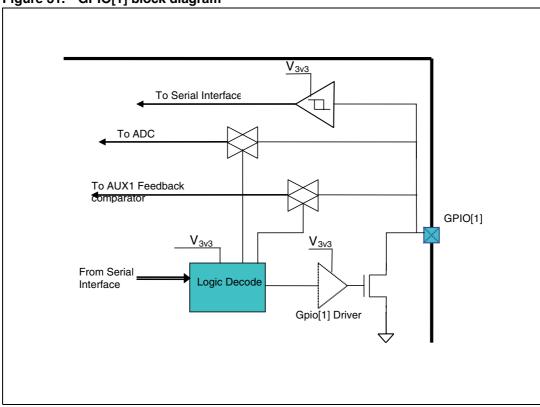

|    | 22.2   | GPIO[1] 101                                                             |

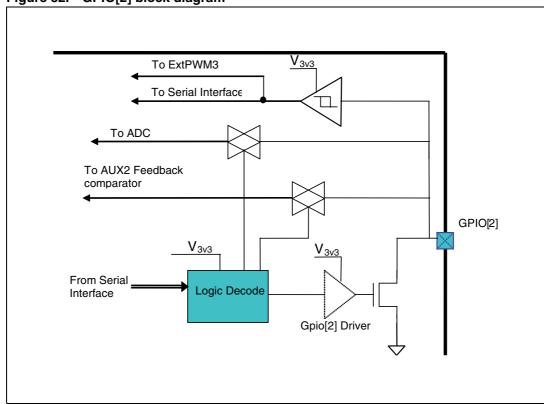

|    | 22.3   | GPIO[2] 103                                                             |

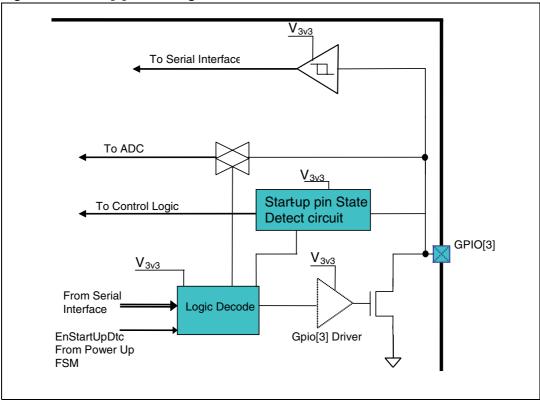

|    | 22.4   | GPIO[3] 105                                                             |

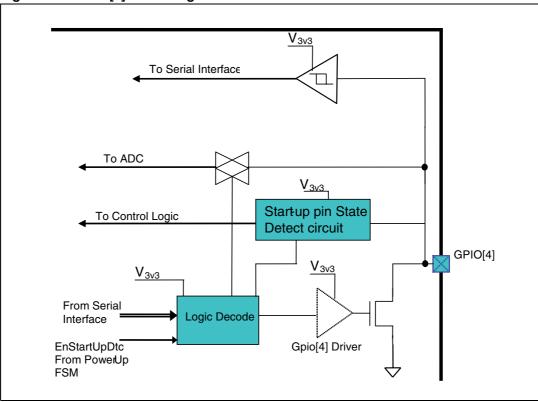

|    | 22.5   | GPIO[4] 107                                                             |

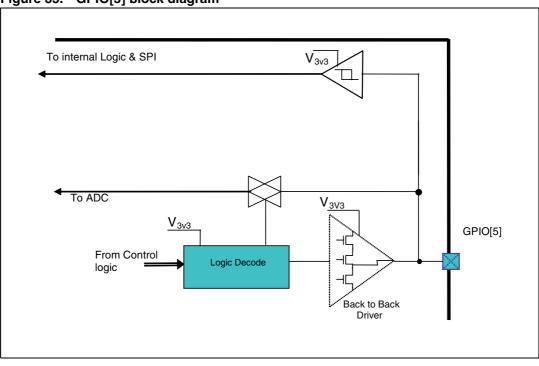

|    | 22.6   | GPIO[5] 109                                                             |

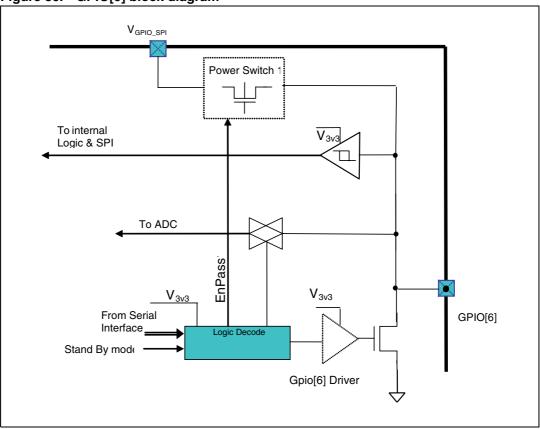

|    | 22.7   | GPIO[6] 111                                                             |

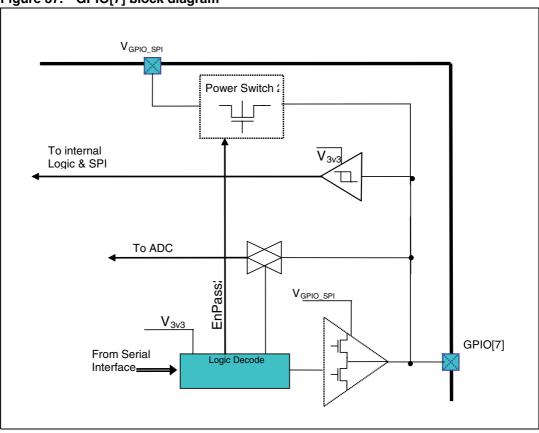

|    | 22.8   | GPIO[7] 113                                                             |

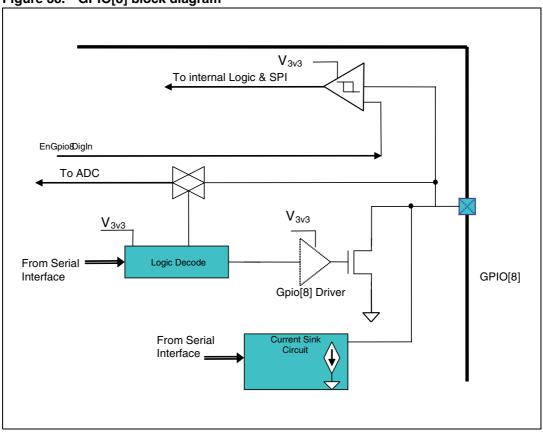

|    | 22.9   | GPIO[8] 115                                                             |

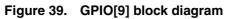

|    |        | GPIO[9] 117                                                             |

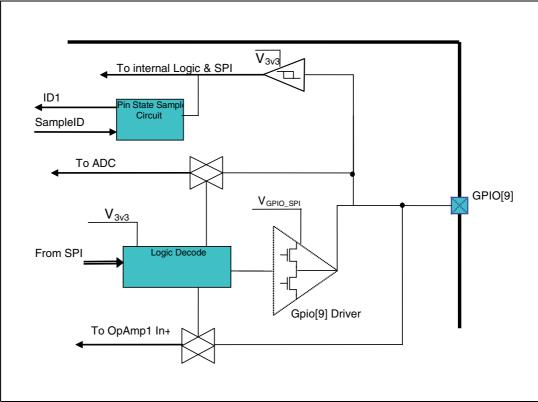

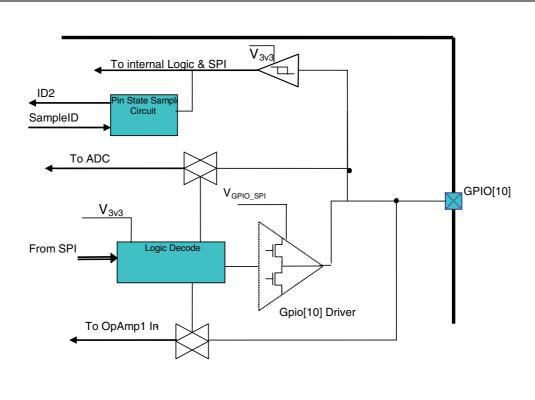

|    |        | GPIO[10] 119                                                            |

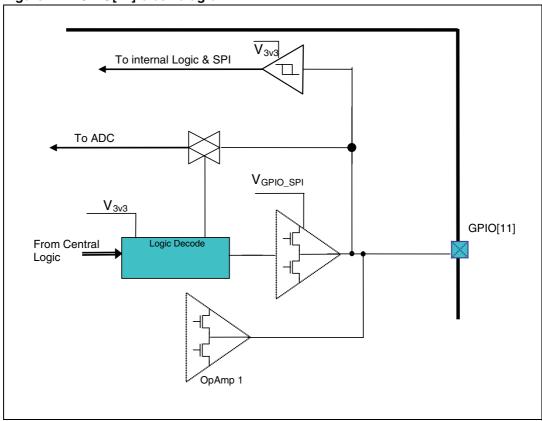

|    |        | GPIO[11] 121                                                            |

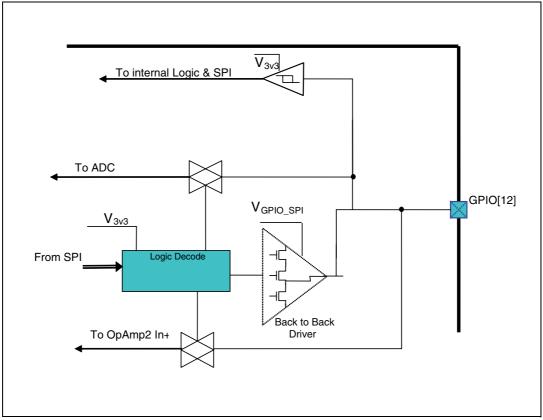

|    |        | GPIO[12] 123                                                            |

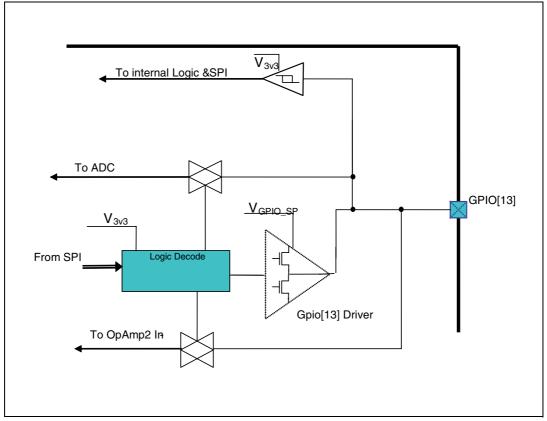

|    |        | GPIO[13] 125                                                            |

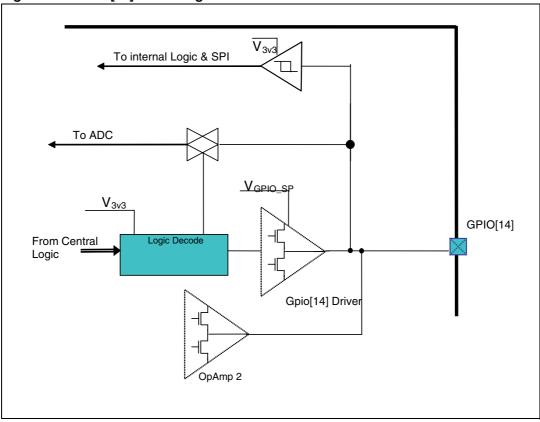

|    | 22.15  | GPIO[14] 127                                                            |

| 23 | Serial | l interface                                                             |

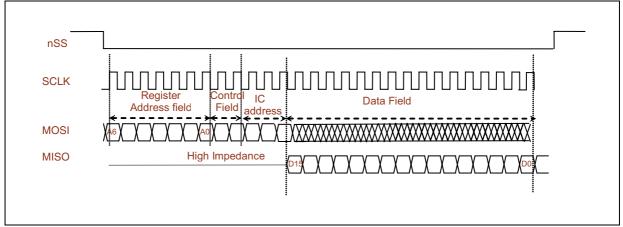

|    | 23.1   | Read transaction                                                        |

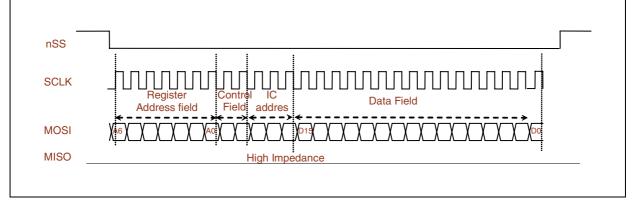

|    | 23.2   | Write transaction                                                       |

| 24 | Registers list          | 2 |

|----|-------------------------|---|

| 25 | Schematic examples 13   | 5 |

| 26 | Package mechanical data | 7 |

| 27 | Revision history        | 8 |

## List of tables

| Table 1.  | Device summary                                                 | . 1 |

|-----------|----------------------------------------------------------------|-----|

| Table 2.  | Pins configuration                                             | 12  |

| Table 3.  | Absolute maximum ratings                                       | 16  |

| Table 4.  | IC operating ratings                                           | 16  |

| Table 5.  | Electrical characteristics                                     | 17  |

| Table 6.  | Stretch time selection                                         | 33  |

| Table 7.  | Watchdog timeout specifications                                | 37  |

| Table 8.  | Possible start-up pins state symbol                            | 39  |

| Table 9.  | Start-up correspondence                                        | 40  |

| Table 10. | Main switching regulator PWM specification.                    | 51  |

| Table 11. | Main switching regulator current limit                         |     |

| Table 12. | Switching regulator controller PWM specification               | 53  |

| Table 13. | Switching regulator controller application: feedback reference | 54  |

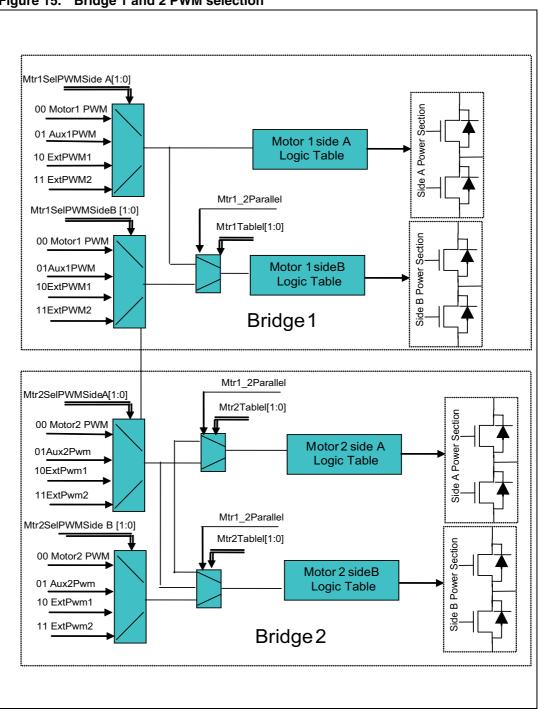

| Table 14. | PWM selection truth table for bridge 1 or 2                    | 57  |

| Table 15. | PWM selection truth table for bridge 3 or 4                    | 57  |

| Table 16. | Bridge selection                                               | 59  |

| Table 17. | Bridge 3 and 4 configuration.                                  | 59  |

| Table 18. | Full bridge truth table                                        | 60  |

| Table 19. | Half bridge truth table                                        | 62  |

| Table 20. | Switch truth table                                             | 63  |

| Table 21. | Sequencer driver                                               | 66  |

| Table 22. | Stepper driving mode                                           |     |

| Table 23. | Stepper sequencer direction                                    | 67  |

| Table 24. | DAC                                                            | 68  |

| Table 25. | Internal sequencer                                             | 69  |

| Table 26. | Stepper off time                                               | 71  |

| Table 27. | Stepper fast decay                                             | 73  |

| Table 28. | PWM specification                                              |     |

| Table 29. | Battery charger regulator controller PWM specification         | 79  |

| Table 30. | ADC truth table                                                | 81  |

| Table 31. | Channel addresses                                              |     |

| Table 32. | ADC sample times when working as a 8-bit ADC                   |     |

| Table 33. | ADC sample time when working as a 9-bit ADC.                   | 83  |

| Table 34. | Voltage divider specification                                  |     |

| Table 35. | Current DAC truth table                                        | 86  |

| Table 36. | Interrupt controller event                                     |     |

| Table 37. | Comparison type truth table                                    | 94  |

| Table 38. | DataX selection truth table                                    |     |

| Table 39. | GPIO functions description                                     |     |

| Table 40. | Abbreviations                                                  |     |

| Table 41. | GPIO[0] truth table                                            |     |

| Table 42. | GPIO[1] truth table                                            |     |

| Table 43. | GPIO[2] truth table                                            |     |

| Table 44. | GPIO[3] truth table                                            |     |

| Table 45. | GPIO[4] truth table                                            |     |

| Table 46. | GPIO[5] truth table                                            |     |

| Table 47. | GPIO[6] truth table                                            |     |

| Table 48. | GPIO[7] truth table                                            |     |

| Table 49. | GPIO[8] truth table                                            | 15  |

| Table 50. | GPIO[9] truth table       | 117 |

|-----------|---------------------------|-----|

| Table 51. | GPIO[10] truth table      | 119 |

| Table 52. | GPIO[11] truth table      | 121 |

|           | GPIO[12] truth table      |     |

|           | GPIO[13] truth table      |     |

| Table 55. | GPIO[14] truth table      | 127 |

| Table 56. | Register address map      | 132 |

| Table 57. | Document revision history | 138 |

# List of figures

| Figure 1.  | Block diagram                                                     | 10 |

|------------|-------------------------------------------------------------------|----|

| Figure 2.  | Pin connection                                                    | 11 |

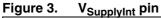

| Figure 3.  | V <sub>SupplyInt</sub> pin                                        | 30 |

| Figure 4.  | Charge pump block diagram.                                        |    |

| Figure 5.  | nReset generation circuit                                         | 34 |

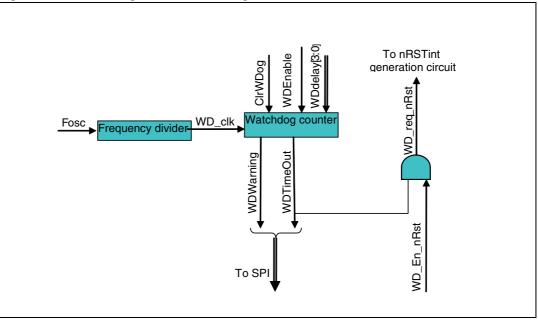

| Figure 6.  | Watchdog circuit block diagram                                    | 36 |

| Figure 7.  | Standby mode function description                                 | 45 |

| Figure 8.  | nAWAKE function block diagram                                     | 47 |

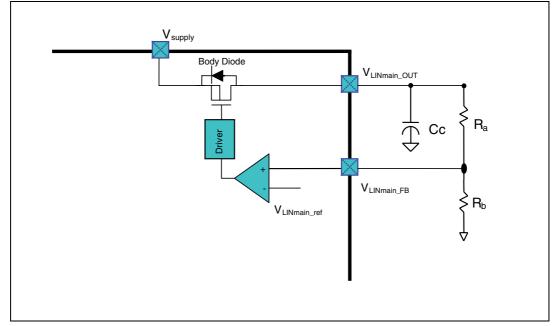

| Figure 9.  | Linear main regulator                                             | 48 |

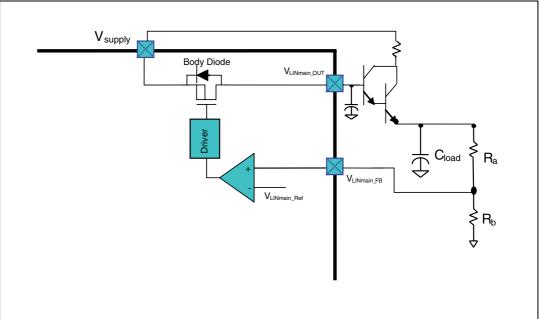

| Figure 10. | Linear main regulator with external bipolar for high current      | 49 |

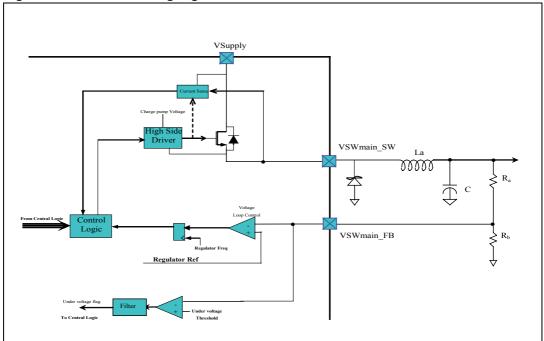

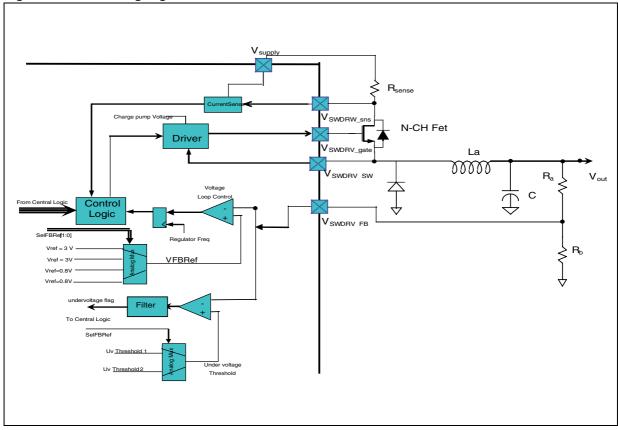

| Figure 11. | Main switching regulator functional blocks                        | 51 |

| Figure 12. | Switching regulator controller functional blocks                  | 53 |

| Figure 13. | Switching regulator controller output driving: equivalent circuit | 54 |

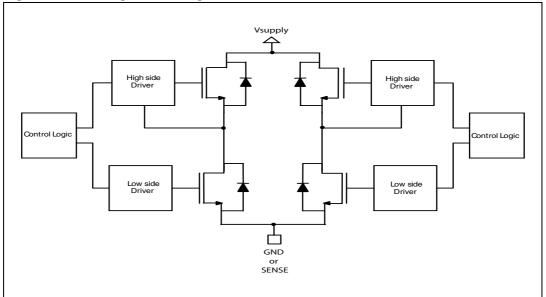

| Figure 14. | H Bridge block diagram                                            | 56 |

| Figure 15. | Bridge 1 and 2 PWM selection                                      |    |

| Figure 16. | Super bridge configuration                                        |    |

| Figure 17. | Half bridge configuration                                         | 62 |

| Figure 18. | Bipolar stepper configuration                                     | 65 |

| Figure 19. | Regulator block diagram                                           | 74 |

| Figure 20. | Internal comparator functional block diagram                      | 75 |

| Figure 21. | Battery charger control loop block diagram                        | 76 |

| Figure 22. | Li-ion battery charge profile                                     | 77 |

| Figure 23. | Simple buck regulator                                             |    |

| Figure 24. | A2D block diagram                                                 | 81 |

| Figure 25. | Current DAC block diagram                                         |    |

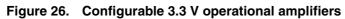

| Figure 26. | Configurable 3.3 V operational amplifiers                         | 87 |

| Figure 27. | Low power switch block diagram                                    | 89 |

| Figure 28. | Interrupt controller diagram                                      | 91 |

| Figure 29. | Digital comparator block diagram                                  | 94 |

| Figure 30. | GPIO[0] block diagram                                             |    |

| Figure 31. | GPIO[1] block diagram                                             |    |

| Figure 32. | GPIO[2] block diagram                                             |    |

| Figure 33. | GPIO[3] block diagram                                             | 06 |

| Figure 34. | GPIO[4] block diagram                                             |    |

| Figure 35. | GPIO[5] block diagram                                             |    |

| Figure 36. | GPIO[6] block diagram                                             |    |

| Figure 37. | GPIO[7] block diagram                                             |    |

| Figure 38. | GPIO[8] block diagram                                             |    |

| Figure 39. | GPIO[9] block diagram                                             |    |

| Figure 40. | GPIO[10] block diagram                                            |    |

| Figure 41. | GPIO[11] block diagram                                            |    |

| Figure 42. | GPIO[12] block diagram                                            | 24 |

| Figure 43. | GPIO[13] block diagram                                               | 126 |

|------------|----------------------------------------------------------------------|-----|

| Figure 44. | GPIO[14] block diagram                                               | 128 |

| Figure 45. | SPI read transaction                                                 | 130 |

| Figure 46. | SPI write transaction                                                | 130 |

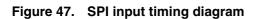

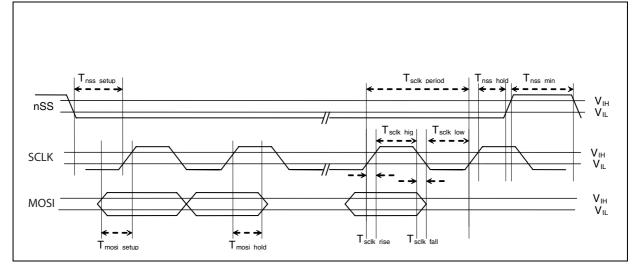

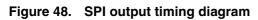

| Figure 47. | SPI input timing diagram                                             | 131 |

| Figure 48. | SPI output timing diagram                                            | 131 |

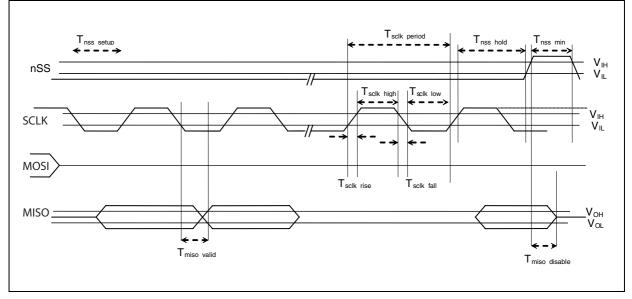

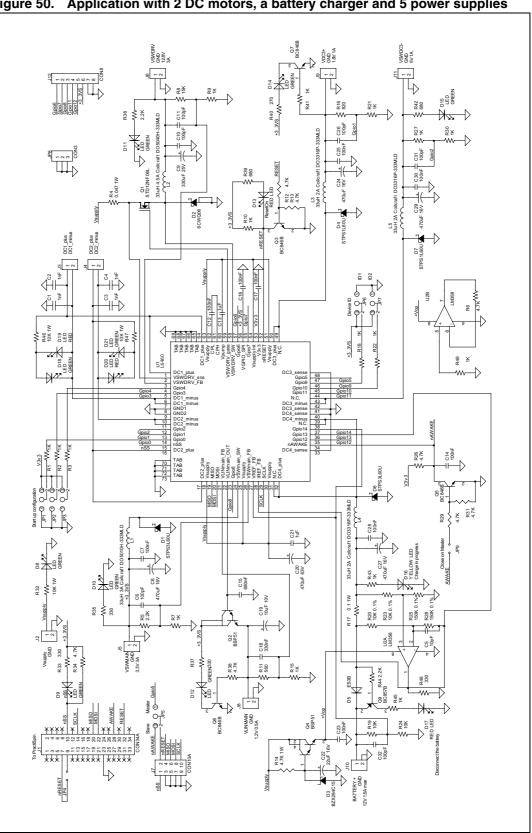

| Figure 49. | Application with 2 DC motors, 1 stepper motor and 3 power supplies   | 135 |

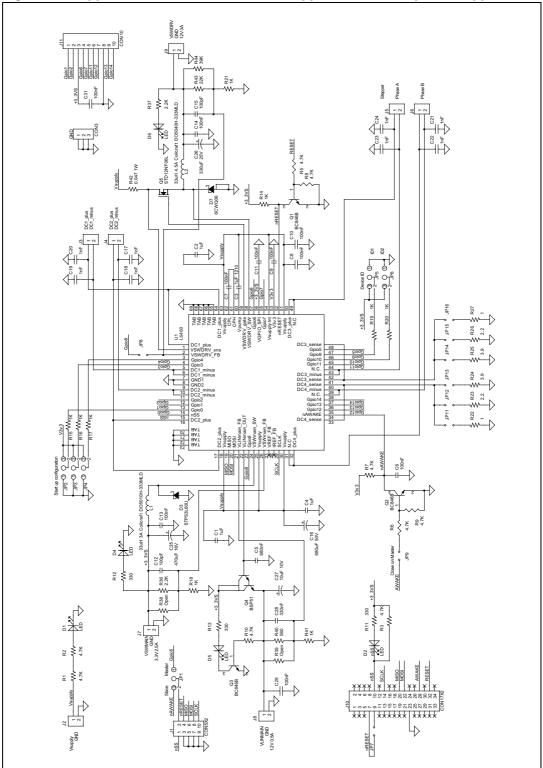

| Figure 50. | Application with 2 DC motors, a battery charger and 5 power supplies | 136 |

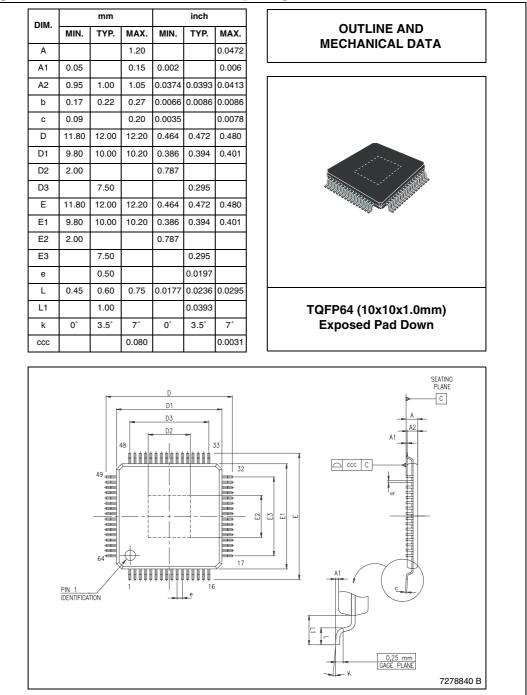

| Figure 51. | TQFP64 mechanical data an package dimensions                         | 137 |

### 1 General description

#### 1.1 Overview

L6460 offers the possibility to control and power multi motor systems, through the management of simultaneous driving of stepper and DC motor. A number of features can be configured through the digital interface (SPI), including 3 voltage regulators, 1 high precision A/D converter, 2 operational amplifiers and 14 configurable GPIOs.

The high flexibility allows the possibility to configure two, one full or half bridge to work as power stage featuring additional voltage buck regulators.

See following Chapter 2 for a detailed description of possible configurations.

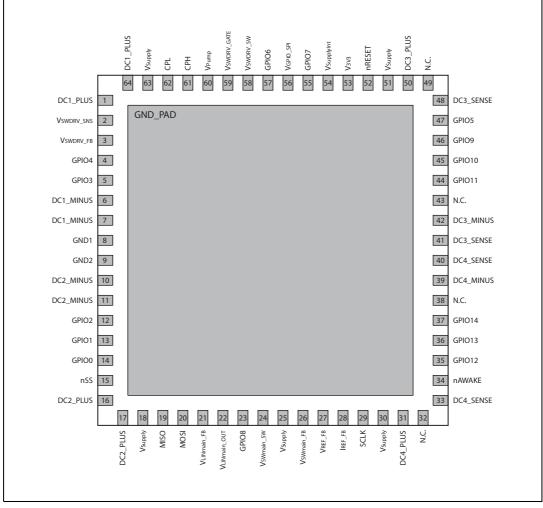

#### 1.2 Pin connection

### 1.3 Pin list

Table 2.Pins configuration

| Pin # | Pin name                 | Description                                 | Туре                        |

|-------|--------------------------|---------------------------------------------|-----------------------------|

| 1     | DC1_PLUS                 | Bridge 1 phase "plus" output                | Output                      |

| 2     | V <sub>SWDRV_SNS</sub>   | Switching regulator controller sense        | Analog input                |

| 3     | V <sub>SWDRV_FB</sub>    | Switching regulator controller feedback     | Analog input                |

| 4     | GPIO4                    | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 5     | GPIO3                    | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 6     | DC1_MINUS                | Bridge 1 phase "minus" output               | Output                      |

| 7     | DC1_MINUS                | Bridge 1 phase "minus" output               | Output                      |

| 8     | GND1                     | Ground pin for bridge1 <sup>(1)(2)(3)</sup> | Power/digital               |

| 9     | GND2                     | Ground pin for bridge2 <sup>(1)(2)(3)</sup> | Power/digital               |

| 10    | DC2_MINUS                | Bridge 2 phase "minus" output               | Output                      |

| 11    | DC2_MINUS                | Bridge 2 phase "minus" output               | Output                      |

| 12    | GPIO2                    | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 13    | GPIO1                    | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 14    | GPIO0                    | General purpose I/O                         | Analog Input - CMOS input   |

| 15    | nSS                      | SPI chip select pin                         | CMOS input                  |

| 16    | DC2_PLUS                 | Bridge 2 phase "plus" output                | Output                      |

| 17    | DC2_PLUS                 | Bridge 2 phase "plus" output                | Output                      |

| 18    | V <sub>Supply</sub>      | Main voltage supply                         | Power input                 |

| 19    | MISO                     | SPI serial data output                      | CMOS output                 |

| 20    | MOSI                     | SPI serial data input                       | CMOS input                  |

| 21    | V <sub>LINmain_FB</sub>  | Linear main regulator feedback              | Analog input                |

| 22    | V <sub>LINmain_OUT</sub> | Linear main regulator output                | Power output                |

| 23    | GPIO 8                   | General purpose I/O                         | Analog In/Out - CMOS bi-dir |

| 24    | V <sub>SWmain_SW</sub>   | Main switching regulator switching output   | Power output                |

| 25    | V <sub>Supply</sub>      | Main voltage supply                         | Power Input                 |

| 26    | V <sub>SWmain_FB</sub>   | Main switching regulator feedback pin       | Analog input                |

| 27    | V <sub>REF_FB</sub>      | Regulator voltage feedback                  | Analog input                |

| 28    | I <sub>REF_FB</sub>      | Regulator current feedback                  | Analog input                |

| 29    | SCLK                     | SPI input clock pin                         | CMOS input                  |

| 30    | V <sub>Supply</sub>      | Main voltage supply                         | Power input                 |

| 31    | DC4_PLUS                 | Bridge 4 phase "plus" output                | Output                      |

| 32    | N.C.                     | Not connected                               |                             |

| 33    | DC4_SENSE                | Bridge 4 sense output <sup>(4)</sup>        | Output                      |

| 34    | nAWAKE                   | Device wake up                              | CMOS input                  |

Doc ID 17713 Rev 1

| Table 2 | ble 2. Pins configuration (continued) |                                             |                             |  |  |

|---------|---------------------------------------|---------------------------------------------|-----------------------------|--|--|

| Pin #   | Pin name                              | Description                                 | Туре                        |  |  |

| 35      | GPIO12                                | General purpose I/O                         | Analog In/Out - CMOS bi-dir |  |  |

| 36      | GPIO13                                | General purpose I/O                         | Analog In/Out - CMOS bi-dir |  |  |

| 37      | GPIO14                                | General purpose I/O                         | Analog In/Out - CMOS bi-dir |  |  |

| 38      | N.C.                                  | Not connected                               |                             |  |  |

| 39      | DC4_MINUS                             | Bridge 4 phase "minus" output               | Output                      |  |  |

| 40      | DC4_SENSE                             | Bridge 4 sense output <sup>(4)</sup>        | Output                      |  |  |

| 41      | DC3_SENSE                             | Bridge 3 sense output <sup>(4)</sup>        | Output                      |  |  |

| 42      | DC3_MINUS                             | Bridge 3 phase "minus" output               | Output                      |  |  |

| 43      | N.C.                                  | Not connected                               |                             |  |  |

| 44      | GPIO11                                | General purpose I/O                         | Analog In/Out - CMOS bi-dir |  |  |

| 45      | GPIO10                                | General purpose I/O                         | Analog In/Out - CMOS bi-dir |  |  |

| 46      | GPIO9                                 | General purpose I/O                         | Analog In/Out - CMOS bi-dir |  |  |

| 47      | GPIO5                                 | General purpose I/O                         | Analog In/Out - CMOS bi-dir |  |  |

| 48      | DC3_SENSE                             | Bridge 3 sense output <sup>(4)</sup>        | Output                      |  |  |

| 49      | N.C.                                  | Not connected                               |                             |  |  |

| 50      | DC3_PLUS                              | Bridge 3 phase "plus" output                | Output                      |  |  |

| 51      | V <sub>Supply</sub>                   | Main voltage supply                         | Power input                 |  |  |

| 52      | nRESET                                | Open drain system reset pin                 | CMOS Input/output           |  |  |

| 53      | V <sub>3v3</sub>                      | Internal 3.3 volt regulator                 | Power Input/output          |  |  |

| 54      | V <sub>SupplyInt</sub>                | Internal voltage supply                     | Power Input                 |  |  |

| 55      | GPIO7                                 | General purpose I/O                         | Analog In/Out - CMOS bi-dir |  |  |

| 56      | V <sub>GPIO_SPI</sub>                 | Low voltage pins power supply               | Power input                 |  |  |

| 57      | GPIO6                                 | General purpose I/O                         | Analog In/Out - CMOS bi-dir |  |  |

| 58      | V <sub>SWDRV_SW</sub>                 | Switching regulator controller source input | Power input                 |  |  |

| 59      | V <sub>SWDRV_GATE</sub>               | Switching driver gate drive pin             | Analog output               |  |  |

| 60      | V <sub>Pump</sub>                     | Charge pump voltage                         | Power Input/output          |  |  |

| 61      | CPH                                   | Charge pump high switch pin                 | Power Input/output          |  |  |

| 62      | CPL                                   | Charge pump low switch pin                  | Power Input/output          |  |  |

| 63      | V <sub>Supply</sub>                   | Main voltage supply                         | Power input                 |  |  |

| 64      | DC1_plus                              | Bridge 1 phase "plus" output                | Output                      |  |  |

| E_Pad   | GND_PAD                               | (1)(2)(3)                                   |                             |  |  |

Table 2.

Pins configuration (continued)

1. These pins must be connected all together to a unique PCB ground.

2. Bridges1 and 2 have 2 ground pads: one is bonded to the relative ground pin (GND1 or GND2) and the other is connected to exposed pad (E\_Pad) ground ring. This makes the bond wires testing possible by forcing a current between E-Pad and GND1 or GND2 pins and using the other pin as sense pin to measure the resistance of E-Pad bonding. (N.B: grounds of two bridges are internally connected together).

3. The analog ground is connected to exposed pad E-Pad.

4. The pin must be tied to ground if bridge is not used as a stepper motor.

### 2 L6460's main features

L6460 includes the following circuits:

- Four widely configurable full bridges:

- Bridges 1 and 2:

- Diagonal  $R_{DSon}$ : 0.6  $\Omega$  typ.

- Max operative current = 2.5 A.

- Bridges 3 and 4:

- Diagonal  $R_{DSon}$ : 0.85  $\Omega$  typ.

- Max operative current = 1.5 A.

- Possible configurations for each bridge are the following:

- Bridge 1:

- DC motor driver.

- Super DC (bridge 1 and 2 paralleled form superbridge1).

- 2 independent half bridges.

- 1 super half bridge (bridge 1 side A and bridge 1 side B paralleled form superhalfbridge1).

- 2 independent switches (high or low side).

- 1 super switch (high or low side).

- Bridge 2 has the same configurations of bridge 1.

- Bridge 3 has the same configurations of bridge 1 (bridge 3 and 4 paralleled form superbridge2) plus the following:

- ½ stepper motor driver.

- 2 buck regulators (V<sub>AUX1\_SW</sub>, V<sub>AUX2\_SW</sub>).

- 1 Super buck regulator (V<sub>AUX1//2\_SW</sub>).

- Bridge 4 has the same configurations of bridge 1 plus the following:

- 1/2 stepper motor driver.

- 1 super buck regulator (V<sub>AUX3 SW</sub>).

- Battery charger.

- One buck type switching regulator (V<sub>SWmain</sub>) with:

- Output regulated voltage range: 1-5 Volts.

- Output load current: 3.0 A.

- Internal output power DMOS.

- Internal soft start sequence.

- Internal PWM generation.

- Switching frequency: ~250 kHz.

- Pulse skipping strategy control.

- One switching regulator controller (V<sub>SWDRV</sub>) with:

- Output regulated voltage range: 1-30 Volts.

- Selectable current limitation.

- Internal PWM generation.

- Pulse skipping strategy control.

- One linear regulator (V<sub>LINmain</sub>) that can be used to generate low current/low ripple

Doc ID 17713 Rev 1

voltages. This regulator can be used to drive an external bipolar pass transistor to generate high current/low ripple output voltages.

- One bidirectional serial interface with address detection so that different ICs can share the same data bus.

- Integrated power sequencing and supervisory functions with fault signaling through serial interface and external reset pin.

- Fourteen general purpose I/Os that can be used to drive/read internal/external analog/logic signals.

- One 8-bit/9-bit A/D converter (100 kS/s @ 9-bit, 200 kS/s @8-bit). It can be used to measure most of the internal signals, of the input pins and a voltage proportional to IC temperature.

- Current sink DAC:

- Three output current ranges: up to 0.64/6.4/64 mA.

- 64 (6-bit programmable) available current levels for each range.

- 5 V output tolerant.

- Two operational amplifiers:

- 3.3 V supply, rail to rail input compatibility, internally compensated.

- They can have all pins externally accessible or can be internally configured as a buffer o make internal reference voltages available outside of the chip.

- Unity gain bandwidth > 1 MHz.

- They can also be set as comparators with 3.3 V input compatibility and low offset.

- Two 3.3 V pass switches with 1 Ω R<sub>DSon</sub> and short circuit protected.

- Programmable watchdog function.

- Thermal shutdown protection with thermal warning capability.

- Very low power dissipation in "low power mode" (~35 mW)

L6460 is intended to maximize the use of its components, so when an internal circuit is not used it could be employed for other applications. Bridge 3, for example, can be used as a full bridge or to implement two switching regulators with synchronous rectification: to obtain this flexibility L6460 includes 2 separate regulation loops for these regulators; when the bridge is used as a motor driver, the 2 regulation loops can be redirected on general purpose I/Os to leave the possibility to assembly a switching regulator by only adding an external FET.

### 3 Electrical specifications

#### 3.1 Absolute maximum rating

The following specifications define the maximum range of voltages or currents for L6460.

Stresses above these absolute maximum specifications may cause permanent damage to the device. Exposure to absolute maximum ratings for extended periods may affect device reliability.

| Parameter             | Description                                   | Test<br>condition | Min  | Max                 | Unit |

|-----------------------|-----------------------------------------------|-------------------|------|---------------------|------|

| V <sub>Supply</sub>   | V <sub>Supply</sub> voltage                   |                   |      | 40                  | V    |

| V <sub>GPIO_SPI</sub> | V <sub>GPIO_SPI</sub> voltage                 |                   |      | 3.9                 | V    |

| V <sub>3V3pin</sub>   | V <sub>3V3</sub> voltage                      |                   | -0.3 | 3.9                 | V    |

| V <sub>SW</sub>       | Switching regulators output pin voltage range |                   | -1   | V <sub>Supply</sub> | V    |

| V <sub>SW_pulse</sub> | Switching regulators min pulsed voltage       | tpulse <<br>500ns | -3   |                     | V    |

| V <sub>Pump</sub>     | Charge pump voltage                           | (1)               |      | 15                  | V    |

| т                     | Junction temperature <sup>(2)</sup>           | Storage           | -40  | 190                 | °C   |

| TJ                    |                                               | Operating         | -40  | TSD                 | °C   |

Table 3. Absolute maximum ratings

This value is useful to define the voltage rating for external capacitor to be connected from V<sub>Pump</sub> to V<sub>Supply</sub>. V<sub>Pump</sub> is internally generated and can never be supplied by external voltage source nor is intended to provide voltage to external loads.

2. TSD is the thermal shut down temperature of the device.

### 3.2 Operating ratings specifications

#### Table 4. IC operating ratings

| Parameter                | Description                             | Test<br>condition | Min               | Max                 | Unit |

|--------------------------|-----------------------------------------|-------------------|-------------------|---------------------|------|

| V <sub>Supply</sub>      | V <sub>Supply</sub> voltage range       |                   | 13 <sup>(1)</sup> | 38                  | V    |

| I <sub>Supply</sub>      | V <sub>Supply</sub> operative current   | (2)               |                   | 15                  | mA   |

| I <sub>Shut_down</sub>   | $V_{Supply}$ shut down state current    |                   |                   | 1.5                 | mA   |

| V <sub>GPIO_SPI</sub>    | V <sub>GPIO_SPI</sub> voltage range     |                   | 2.4               | 3.6                 | V    |

| I <sub>VGPIO_SPI</sub>   | V <sub>GPIO_SPI</sub> operative current | (3)               |                   | 0.4                 | mA   |

| V <sub>3v3</sub>         | 3.3V input pin voltage range            |                   |                   | 3.6                 | V    |

| V <sub>LINmain_OUT</sub> | Output pin voltage range                | (4)               | 0                 | V <sub>Supply</sub> | V    |

| V <sub>LINmain_FB</sub>  | Feedback pin voltage range              |                   | 0                 | 3.6                 | V    |

| V <sub>SWmain_SW</sub>   | Output pin voltage range                | (4)               | -1                | V <sub>supply</sub> | V    |

| V <sub>SWDRV_SW</sub>    | V <sub>SWDRV_SW</sub> pin voltage range | (4)               | -1                | V <sub>Supply</sub> | V    |

| Parameter               | Description            | Test condition | Min                        | Max                 | Unit |

|-------------------------|------------------------|----------------|----------------------------|---------------------|------|

| V <sub>SWDRV_GATE</sub> | Gate drive pin voltage |                | 0                          | V <sub>Pump</sub>   | V    |

| V <sub>SWDRV_SNS</sub>  | Sense pin voltage      |                | V <sub>Supply</sub><br>-3V | V <sub>Supply</sub> | V    |

| TJ                      | Junction temperature   | Operating      | -40                        | 125                 | °C   |

Table 4.IC operating ratings

1. For V<sub>supply</sub> lower than 21 V an external resistor between V<sub>supply</sub> and V<sub>supply</sub> Int pins are required. For V<sub>supply</sub> lower than 15 V external diodes for charge pump are required.

2. Operating supply current is measured with system regulators operating but not loaded.

Operating V<sub>GPIO\_SPI</sub> current is measured with all circuits supplied by V<sub>GPIO\_SPI</sub> (GPIO's, operational amplifiers and pass switches) enabled but not loaded.

4. The external components connected to the pin must be chosen to avoid that the voltage exceeds this operative range.

#### 3.3 Electrical characteristics

#### Table 5.Electrical characteristics

| Parameter                      | Description                               | Test condition               | Min                           | Тур                          | Max                           | Unit |

|--------------------------------|-------------------------------------------|------------------------------|-------------------------------|------------------------------|-------------------------------|------|

| V <sub>SupplyInt</sub> regulat | tor                                       |                              |                               |                              |                               |      |

| V <sub>S_Int</sub>             | V <sub>SupplyInt</sub> output voltage     | (1)                          | 18                            | 19.5                         | 21                            | V    |

| I <sub>S_Int</sub>             | V <sub>SupplyInt</sub> operative current  | (2)                          |                               | 11                           |                               | mA   |

| Charge pump V <sub>F</sub>     | Pump                                      |                              |                               |                              |                               |      |

| V <sub>Pump</sub>              | Charge pump voltage                       | V <sub>Supply</sub> =32V     | V <sub>Supply</sub><br>+ 10.5 | V <sub>Supply</sub><br>+12.5 | V <sub>Supply</sub><br>+ 14.5 | V    |

| F <sub>Pump</sub>              | V <sub>Pump</sub> clock frequency         | F <sub>OSC</sub> = 16MHz typ |                               | F <sub>OSC</sub> /6          |                               | kHz  |

| V3V3 regulator                 |                                           |                              |                               |                              |                               |      |

| V <sub>3V3</sub>               | V <sub>3v3</sub> output voltage           | V <sub>Supply</sub> =32V     | 3.15                          | 3.3                          | 3.45                          | V    |

| Power on reset                 |                                           |                              |                               |                              |                               |      |

| V <sub>Supply_POR_valid</sub>  | V <sub>Supply</sub> voltage for POR valid | I <sub>nRESET</sub> = 1mA    | 4                             |                              |                               | V    |

| V <sub>Supply_POR_fall</sub>   | V <sub>Supply</sub> POR falling threshold | V <sub>Supply</sub> falling  | 6                             |                              | 8                             | V    |

| t <sub>Supply_POR_filt</sub>   | V <sub>Supply</sub> POR filter Time       |                              |                               | 3                            |                               | μs   |

| V <sub>3V3_POR_fall</sub>      | V <sub>3v3</sub> POR falling threshold    | V <sub>3V3</sub> falling     | 1.9                           | 2.2                          |                               | V    |

| V <sub>3V3_POR_rise</sub>      | V <sub>3v3</sub> POR rising threshold     | V <sub>3V3</sub> rising      |                               | 2.7                          |                               | V    |

| V <sub>3V3_POR_hys</sub>       | V <sub>3v3</sub> POR hysteresis           |                              |                               | 0.5                          |                               | V    |

| t <sub>3V3_POR_filt</sub>      | V <sub>3v3</sub> POR filter time          |                              |                               | 1.5                          |                               | μs   |

| nRESET circuit                 |                                           |                              |                               |                              |                               |      |

| V <sub>nRST_L</sub>            | nRESET low level output voltage           | I=10mA                       |                               |                              | 0.4                           | V    |

| Parameter                  | Description                              | Test condition                 | Min                          | Тур                                   | Max                          | Unit |

|----------------------------|------------------------------------------|--------------------------------|------------------------------|---------------------------------------|------------------------------|------|

| <sup>t</sup> nRST_fall     | nRESET fall time                         | l=1mA<br>C=50pF <sup>(3)</sup> |                              |                                       | 15                           | ns   |

| t <sub>nRST_del</sub>      | nRESET delay time                        | (4)                            |                              |                                       | 150                          | ns   |

| V <sub>Supply_UV_f</sub>   | V <sub>Supply</sub> falling threshold    |                                | 10.2                         | 11                                    | 11.8                         | V    |

| V <sub>Supply_UV_r</sub>   | V <sub>Supply</sub> rising threshold     |                                | 10.5                         | 11.5                                  | 12.5                         | V    |

| V <sub>Supply_UV_hys</sub> | V <sub>Supply</sub> hysteresis           |                                | 0.3                          | 0.5                                   | 0.7                          | V    |

| t <sub>Supply_UV</sub>     | V <sub>Supply</sub> UV filter time       |                                |                              | 3.5                                   |                              | μs   |

| V <sub>S_Int_UV_f</sub>    | V <sub>SupplyInt</sub> falling threshold |                                | 9.7                          | 10.7                                  | 11.7                         | V    |

| V <sub>S_Int_UV_r</sub>    | V <sub>SupplyInt</sub> rising threshold  |                                | 10.6                         | 11.4                                  | 12.2                         | V    |

| V <sub>S_Int_UV_hys</sub>  | V <sub>SupplyInt</sub> hysteresis        |                                | 0.4                          | 0.7                                   | 1                            | V    |

| t <sub>S_Int_UV</sub>      | V <sub>SupplyInt</sub> UV filter time    |                                |                              | 3.5                                   |                              | μs   |

| V <sub>Pump_UV_f</sub>     | V <sub>Pump</sub> falling threshold      |                                | V <sub>Supply</sub><br>+7    | V <sub>Supply</sub><br>+ 7.5          | V <sub>Supply</sub><br>+ 8   | V    |

| V <sub>Pump_UV_r</sub>     | V <sub>Pump</sub> rising threshold       |                                | V <sub>Supply</sub><br>+ 7.5 | V <sub>Supply</sub><br>+ 8            | V <sub>Supply</sub><br>+ 8.5 | V    |

| V <sub>Pump_UV_hys</sub>   | V <sub>Pump</sub> hysteresis             |                                | 0.3                          | 0.5                                   | 0.7                          | V    |

| t <sub>Pump_UV</sub>       | V <sub>Pump</sub> UV filter time         |                                |                              | 3.5                                   |                              | μs   |

| V <sub>GPIO_SPI_UV_f</sub> | V <sub>GPIO_SPI</sub> falling threshold  |                                | 1.8                          | 2                                     |                              | V    |

| V <sub>GPIO_SPI_UV_r</sub> | V <sub>GPIO_SPI</sub> rising threshold   |                                |                              | 2.2                                   | 2.4                          | V    |

| V <sub>GPIO_SPI_hys</sub>  | V <sub>GPIO_SPI</sub> hysteresis         |                                | 200                          | 250                                   | 300                          | mV   |

| t <sub>GPIO_SPI_UV</sub>   | V <sub>GPIO_SPI</sub> UV filter time     |                                |                              | 3.5                                   |                              | μs   |

| TSD circuit                |                                          |                                |                              |                                       |                              |      |

| T <sub>TSD</sub>           | Thermal shut down temperature            |                                |                              | 170                                   |                              | °C   |

| T <sub>WARM</sub>          | Warming temperature                      |                                |                              | 140                                   |                              | °C   |

| T <sub>DIFF</sub>          | Thermal shut down to warming difference  |                                |                              | 30                                    |                              | °C   |

| t <sub>TSD_FILT</sub>      | Thermal shut down filter time            |                                |                              | 8                                     |                              | μs   |

| t <sub>WARM_FILT</sub>     | Warming filter time                      |                                |                              | 8                                     |                              | μs   |

| Watchdog                   |                                          | I                              |                              |                                       |                              |      |

| WD_T <sub>clk</sub>        | Watchdog clock period                    |                                |                              | T <sub>osc</sub> *<br>2 <sup>22</sup> |                              | s    |

| Internal clock             |                                          |                                | <u>I</u>                     | <u>.</u>                              | <b>.</b>                     |      |

| F <sub>osc</sub>           | Oscillator frequency                     | V <sub>3V3</sub> = 3.3 V       | 14.1                         | 16                                    | 17.6                         | MHz  |

| nAWAKE functi              | on                                       |                                |                              |                                       |                              |      |

| V <sub>IL</sub>            | nAWAKE low logic level voltage           |                                |                              |                                       | 0.8                          | v    |

Table 5.

Electrical characteristics (continued)

57

| Parameter                            | Description                                   | Test condition                                                       | Min   | Тур  | Max   | Unit |

|--------------------------------------|-----------------------------------------------|----------------------------------------------------------------------|-------|------|-------|------|

| V <sub>IH</sub>                      | nAWAKE high logic level voltage               |                                                                      | 1.6   |      |       | V    |

| V <sub>HYS</sub>                     | nAWAKE input hysteresis                       |                                                                      |       | 0.25 |       | V    |

| I <sub>OUT</sub>                     | nAWAKE pin output current                     | nAWAKE=0V <sup>(5)</sup>                                             | -0.72 |      | -2    | mA   |

| I <sub>INP</sub>                     | nAWAKE pin input current                      | nAWAKE=0.8V <sup>(5)</sup>                                           | 0.2   |      | 0.4   | mA   |

| t <sub>AWAKEFILT</sub>               | Filter time                                   |                                                                      |       | 1.2  |       | μs   |

| Main linear regu                     | llator                                        | ·                                                                    |       |      |       |      |

| V <sub>drop</sub>                    | Drop out voltage                              | V <sub>drop</sub> =<br>V <sub>supply</sub> -V <sub>LINmain_OUT</sub> | 2     |      |       | V    |

| I <sub>PD</sub>                      | Internal switch pull down current             | Linear Main Regulator<br>disabled; V <sub>LINmain_OUT</sub> =1V      |       | 3    |       | mA   |

| V <sub>LINmain_Ref</sub>             | Feedback reference voltage                    |                                                                      | 0.776 | 0.8  | 0.824 | V    |

| I <sub>LINmain_Ref</sub>             | Feedback pin input current                    |                                                                      | -2    |      | 2     | μA   |

| I <sub>outLINMax</sub>               | Maximum output current                        | V <sub>LINmain_OUT</sub> = V <sub>supply</sub> -2V                   | 10    |      |       | mA   |

| I <sub>short</sub>                   | Output short<br>circuit current               | V <sub>LINmain_OUT</sub> =0V,<br>V <sub>LINmain_FB</sub> =0V         | 12    | 24   | 32    | mA   |

| $\Delta V_{out}/V_{o}$               | Load regulation                               | $0 \le I_{load} \le I_{outLINMax}^{(6)}$                             |       |      | 0.8   | %    |

| $\Delta V_{out} / \Delta V_{Supply}$ | Line regulation                               | I <sub>load</sub> =10mA <sup>(6)</sup>                               |       |      | 0.2   | %    |

| V <sub>loop_acc</sub>                | Loop voltage accuracy                         |                                                                      |       | ±2.5 |       | %    |

| V <sub>LIN_UV_f</sub>                | Undervoltage falling threshold                | (7)                                                                  | 84.5  | 87   | 89.5  | %    |

| V <sub>LIN_UV_r</sub>                | Undervoltage rising threshold                 | (7)                                                                  | 90.5  | 93   | 95.5  | %    |

| V <sub>LIN_UV_hys</sub>              | Undervoltage hysteresis                       |                                                                      |       | 6    |       | %    |

| t <sub>prim_uv</sub>                 | Under voltage deglitch filter                 |                                                                      |       | 5    |       | μs   |

| Main switching                       | regulator                                     |                                                                      |       |      |       |      |

|                                      |                                               | SelFBref = '00'                                                      | 0.776 | 0.8  | 0.824 | V    |

| M                                    | Main switching regulator                      | SelFBref = '01' <sup>(8)</sup>                                       | 0.97  | 1    | 1.03  | V    |

| V <sub>FBREF</sub>                   | feedback reference voltage                    | SelFBref = '10'                                                      | 2.425 | 2.5  | 2.575 | V    |

|                                      |                                               | SelFBref = '11'                                                      | 2.91  | 3    | 3.09  | V    |

| Ι <sub>Q</sub>                       | Output leakage current                        | T <sub>junction</sub> = 125°C                                        | -40   |      | +40   | μA   |

| I <sub>Q_LP</sub>                    | Output leakage current in<br>"low power mode" | V <sub>Supply</sub> = 36V<br>T <sub>junction</sub> = 125°C           | -15   |      | +15   | μA   |

| I <sub>SWmain_FB</sub>               | V <sub>SWmain_FB</sub> pin current            | T <sub>junction</sub> = 125°C                                        | -10   |      | +10   | μA   |

| V <sub>SWmain_OUT</sub>              | Output voltage range                          | (9)                                                                  | 0.8   |      | 5     | V    |

| I <sub>load</sub>                    | Maximum output load current                   | V <sub>Supply</sub> = 36V                                            | 0.002 |      | 3     | Α    |

| R <sub>DSonHS</sub>                  | Internal high side R <sub>DSon</sub>          | I <sub>load</sub> =1A<br>T <sub>junction</sub> = 125°C               |       | 0.33 | 0.95  | Ω    |

L6460

\_\_\_\_\_

| Parameter              | Description                                   | Test condition                                                             | Min        | Тур               | Max   | Unit   |

|------------------------|-----------------------------------------------|----------------------------------------------------------------------------|------------|-------------------|-------|--------|

| V <sub>loop</sub>      | Loop voltage accuracy                         |                                                                            |            | ±3%               |       |        |

| V <sub>SW_UV_f</sub>   | Under voltage falling threshold               | (10)                                                                       | 84.5       | 87                | 89.5  | %      |

| V <sub>SW_UV_r</sub>   | Under voltage rising threshold                | (10)                                                                       | 90.5       | 93                | 95.5  | %      |

| V <sub>SW_UV_hys</sub> | Under voltage hysteresis                      |                                                                            |            | 6                 |       | %      |

| t <sub>prim_uv</sub>   | Under voltage deglitch filter                 |                                                                            |            | 5                 |       | μs     |

| I <sub>limit</sub>     | Current limit protection                      | Selllimit ="0"<br>Selllimit ="1"                                           | 3.3<br>2.3 | 5<br>3.5          |       | A<br>A |

| t <sub>deglitch</sub>  | Current limit deglitch time                   |                                                                            | 50         |                   |       | ns     |

| t <sub>l_lim</sub>     | Current limit response time                   | Normal operating mode (no UV) <sup>(11)</sup>                              |            | 450               | 650   | ns     |

| t <sub>I_limUV</sub>   | Current limit response time in UV condition   | UV condition <sup>(12)</sup>                                               |            | 200               | 400   | ns     |

| t <sub>r</sub>         | Switching output rise time                    | $V_{Supply} = 36V,$<br>$R_{LOAD} = 422 \ \Omega^{(13)}$                    | 5          |                   | 30    | ns     |

| t <sub>f</sub>         | Switching output fall time                    | $V_{Supply} = 36V,$<br>$R_{LOAD} = 10 \ \Omega^{(13)}$                     | 5          |                   | 30    | ns     |

| F <sub>SW_PWM</sub>    | Operating frequency                           |                                                                            |            | Fosc/6<br>4       |       | kHz    |

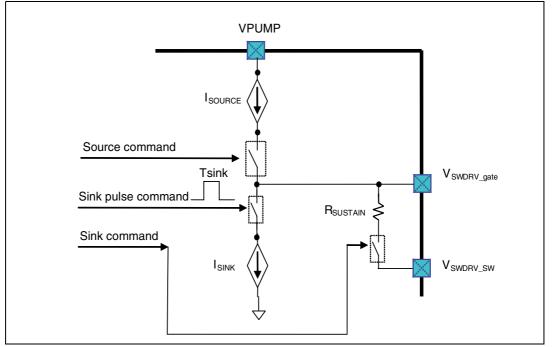

| witching regu          | lator controller                              |                                                                            |            |                   |       |        |

| V <sub>GS_ext</sub>    | Gate to source voltage for external FET       |                                                                            |            | V <sub>Pump</sub> |       | V      |

| ISOURCE                | Source current                                | V <sub>Pump</sub> =V <sub>Supply</sub> +12V<br>V <sub>SWCTR_GATE</sub> =0V | 25         |                   | 50    | mA     |

| I <sub>SINK</sub>      | Sink current                                  | V <sub>SWCTR_GATE</sub> = V <sub>Supply</sub>                              | 20         |                   |       | mA     |

| t <sub>SINK</sub>      | Sink discharge pulse time                     |                                                                            |            | 600               |       | ns     |

| R <sub>SUSTAIN</sub>   | Gate-source sustain resistance                | (V <sub>SWCTR_GATE</sub> -<br>V <sub>SWCTR_SRC</sub> ) = 0.2V              |            | 650               |       | Ω      |

| ۱ <sub>Q</sub>         | Output<br>leakage current                     | V <sub>Supply</sub> = 36V,<br>T <sub>junction</sub> = 125°C                | -40        |                   | +40   | μA     |

| I <sub>Q_LP</sub>      | Output leakage current in<br>"Low Power Mode" | V <sub>Supply</sub> = 36V,<br>T <sub>junction</sub> = 125°C                | -5         |                   | +5    | μA     |

|                        |                                               | SelFBref = '00' <sup>(8)</sup>                                             | 0.776      | 0.8               | 0.824 | V      |

| V                      | Switching regulator feedback                  | SelFBref = '01'                                                            | 0.97       | 1                 | 1.03  | V      |

| V <sub>FBREF</sub>     | controller feedback reference voltage         | SelFBref = '10'                                                            | 2.425      | 2.5               | 2.575 | V      |

|                        |                                               | SelFBref = '11'                                                            | 2.91       | 3                 | 3.09  | V      |

| I <sub>SWDRV_FB</sub>  | V <sub>SWDRV_FB</sub> pin current             | V <sub>Supply</sub> = 36V,<br>T <sub>junction</sub> = 125°C                | -10        |                   | +10   | μA     |

| V <sub>loop</sub>      | Loop voltage accuracy                         |                                                                            |            | ±3%               |       |        |

Table 5.

Electrical characteristics (continued)

L6460

| Parameter               | Description                                               | Test condition                                                 | Min  | Тур                  | Мах  | Unit |

|-------------------------|-----------------------------------------------------------|----------------------------------------------------------------|------|----------------------|------|------|

| V <sub>SWD_UV_f</sub>   | Under voltage falling threshold                           | (14)                                                           | 84.5 | 87                   | 89.5 | %    |

| V <sub>SWD_UV_r</sub>   | Under voltage rising threshold                            | (14)                                                           | 90.5 | 93                   | 95.5 | %    |

| V <sub>SWD_UV_hys</sub> | Under voltage hysteresis                                  |                                                                |      | 6                    |      | %    |

| t <sub>prim_uv</sub>    | Under voltage deglitch filter                             |                                                                |      | 5                    |      | μs   |

| V <sub>ovc</sub>        | Over current threshold voltage                            |                                                                | 250  | 300                  | 350  | mV   |

| t <sub>deglitch</sub>   | Current limit deglitch time                               |                                                                | 50   |                      |      | ns   |

| t <sub>l_lim</sub>      | Current limit response time                               | Normal operating mode (no UV) <sup>(11)</sup>                  |      | 500                  | 900  | ns   |

| t <sub>I_limUV</sub>    | Current Limit response time in UV condition.              | UV condition <sup>(12)</sup>                                   |      | 380                  | 550  | ns   |

| F <sub>SWD_PWM</sub>    | Operating frequency                                       |                                                                |      | F <sub>osc</sub> /64 |      | kHz  |

| Power bridges           |                                                           |                                                                |      |                      |      |      |

| R <sub>DSon1_2</sub>    | Bridge 1 and 2 diagonal R <sub>DSon</sub>                 | $I = 1.4A, V_{Supply} = 36V,$<br>T <sub>junction</sub> = 125°C |      | 0.6                  | 1.1  | Ω    |

| R <sub>DSon3_4</sub>    | Bridge 3 and 4 diagonal R <sub>DSon</sub>                 | I = 1A, $V_{Supply}$ = 36V,<br>T <sub>junction</sub> = 125°C   |      | 0.85                 | 1.65 | Ω    |

| I <sub>MAX1_2</sub>     | Bridge 1 and 2 operative rms current                      |                                                                |      |                      | 2.5  | A    |

| I <sub>MAX3_4</sub>     | Bridge 3 and 4 operative rms current                      |                                                                |      |                      | 1.5  | A    |

| I <sub>dss</sub>        | Output leakage current.                                   | T <sub>junction</sub> = 125°C                                  | -50  |                      | +50  | μA   |

| I <sub>Q_LP</sub>       | Output leakage current in "low power mode"                | V <sub>Supply</sub> = 36V,<br>T <sub>junction</sub> = 125°C    | -10  |                      | +10  | μΑ   |

|                         |                                                           | MtrXSideYILimSel[1:0]=00                                       | 0.6  | 1                    | 1.6  |      |

|                         | Low side current protection for                           | MtrXSideYILimSel[1:0]=01                                       | 1.4  | 2                    | 2.6  |      |

| I <sub>OC_LS1_2</sub>   | bridges 1 and $2^{(15)}$                                  | MtrXSideYILimSel[1:0]=10                                       | 2.4  | 3                    | 3.6  | A    |

|                         |                                                           | MtrXSideYILimSel[1:0]=11<br>(16)                               | 2.4  | 3                    | 3.6  |      |

|                         |                                                           | MtrXSideYILimSel[1:0]=00                                       | 0.7  | 1                    | 1.7  |      |

|                         |                                                           | MtrXSideYILimSel[1:0]=01                                       | 1.5  | 2                    | 2.7  |      |

| I <sub>OC_HS1_2</sub>   | High side current protection for bridges 1 and $2^{(15)}$ | MtrXSideYILimSel[1:0]=10                                       | 2.5  | 3                    | 3.7  | А    |

|                         |                                                           | MtrXSideYILimSel[1:0]=11 <sup>(1</sup>                         | 2.5  | 3                    | 3.7  |      |

| I <sub>OC_LS3_4</sub>   | Low side current protection for bridges 3 and $4^{(15)}$  | MtrXSideYILimSel[1:0]=11<br>(17)(18)                           | 1.55 |                      | 2.5  | А    |

| I <sub>OC_HS3_4</sub>   | High side current protection for bridges 3 and $4^{(15)}$ | MtrXSideYILimSel[1:0]=11 <sup>(1</sup><br><sup>7)(18)</sup>    | 1.6  |                      | 2.5  | А    |

| t <sub>filter</sub>     | Current limit filter time                                 |                                                                | 2    |                      | 5    | μs   |

Table 5.

Electrical characteristics (continued)

| Parameter              | Description                                   | Test condition                                                                                                               | Min          | Тур                       | Мах                 | Unit                 |

|------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------|---------------------|----------------------|

| t <sub>delay</sub>     | Current limit<br>delay time                   |                                                                                                                              |              | 5                         |                     | μs                   |

| t <sub>OC_off</sub>    | Over current Off time                         | MtrXIIimitOffTimeY[1:0]=00<br>MtrXIIimitOffTimeY[1:0]=01<br>MtrXIIimitOffTimeY[1:0]=10<br>MtrXIIimitOffTimeY[1:0]=11<br>(19) |              | 60<br>120<br>240<br>480   |                     | μs<br>μs<br>μs<br>μs |

| t <sub>r1_2</sub>      | Output rise time<br>bridges 1 and 2           | $V_{Supply} = 36V$ , resistive load<br>between outputs:<br>R= 25 $\Omega^{(20)}$                                             | 100          | 180                       | 250                 | ns                   |

| t <sub>r3_4</sub>      | Output rise time<br>bridges 3 and 4           | $V_{Supply} = 36V$ , resistive load<br>between outputs:<br>R= 36 $\Omega^{(20)}$                                             | 50           | 100                       | 200                 | ns                   |

| t <sub>f1_2</sub>      | Output fall time<br>bridges 1 and 2           | $V_{Supply} = 36V$ , resistive load<br>between outputs:<br>R= 25 $\Omega^{(20)}$                                             | 100          | 180                       | 250                 | ns                   |

| t <sub>f3_4</sub>      | Output fall time<br>bridges 3 and 4           | $V_{Supply} = 36V$ , resistive load<br>between outputs:<br>R= 36 $\Omega^{(20)}$                                             | 50           | 125                       | 250                 | ns                   |

| t <sub>deadRise</sub>  | Anti crossover rising dead time               |                                                                                                                              | 100          | 300                       | 450                 | ns                   |

| t <sub>dead</sub> Fall | Anti crossover falling dead time              |                                                                                                                              | 100          | 300                       | 450                 | ns                   |

| F <sub>PWM</sub>       | Operating frequency                           |                                                                                                                              |              | F <sub>osc</sub> /51<br>2 |                     | kHz                  |

| t <sub>resp</sub>      | Delay from PWM to output transition           |                                                                                                                              |              | 500                       |                     | ns                   |

| lipolar steppe         | r circuitry                                   |                                                                                                                              |              |                           |                     |                      |

| V <sub>STEPREF</sub>   | Reference voltage                             | SelStepRef =0<br>SelStepRef =1                                                                                               | 0.48<br>0.72 | 0.50<br>0.75              | 0.52<br>0.78        | V                    |

| V <sub>offset</sub>    | Sense comparator offset                       |                                                                                                                              | -12          |                           | 12                  | mV                   |

|                        |                                               | StepBlkTime = '00' <sup>(8)</sup>                                                                                            | 0.65         | 0.95                      | 1.25                | μs                   |

| t                      | Blanking time                                 | StepBlkTime = '01'                                                                                                           | 1            | 1.45                      | 1.9                 | μs                   |

| t <sub>blk</sub>       |                                               | StepBlkTime = '10'                                                                                                           | 1.5          | 2.25                      | 3                   | μs                   |

|                        |                                               | StepBlkTime = '11'                                                                                                           | 3            | 4.25                      | 5.5                 | μs                   |

| ynchronous b           | ouck regulator (bridge 3)                     |                                                                                                                              |              |                           |                     |                      |

| V <sub>AUX_SW</sub>    | Output pin voltage range (DC3x)               | (26)                                                                                                                         | -1           |                           | V <sub>Supply</sub> | V                    |

| ۱ <sub>Q</sub>         | Output leakage current                        | T <sub>junction</sub> = 125°C                                                                                                | -50          |                           | +50                 | μA                   |

| I <sub>QLP</sub>       | Output leakage current in "Low<br>Power Mode" | V <sub>Supply</sub> = 36V<br>T <sub>junction</sub> = 125°C                                                                   | -10          |                           | +10                 | μA                   |

Table 5. **Electrical characteristics (continued)**

| I. | 6460  |  |

|----|-------|--|

| _  | .0700 |  |

| Parameter               | Description                                  | Test condition                                          | Min   | Тур                  | Мах                 | Unit |

|-------------------------|----------------------------------------------|---------------------------------------------------------|-------|----------------------|---------------------|------|

|                         |                                              | SelFBRef = '00'                                         | 0.776 | 0.8                  | 0.824               | V    |

| V                       | Synchronous buck regulator                   | SelFBRef = '01' (21)                                    | 0.97  | 1                    | 1.03                | V    |

| V <sub>FBREF</sub>      | feedback reference voltage                   | SelFBRef = '10' <sup>(22)</sup>                         | 2.425 | 2.5                  | 2.575               | V    |

|                         |                                              | SelFBRef = '11'                                         | 2.91  | 3                    | 3.09                | V    |

| I <sub>GPIO_FB</sub>    | GPIO feedback pin current                    | T <sub>junction</sub> = 125°C<br>0V≤Feedback ≤ 3V       | -15   |                      | 15                  | μA   |

| V <sub>out</sub>        | Output voltage range                         | $V_{Supply} = 36V^{(23)}$                               | 0.8   |                      | 30                  | V    |

| I <sub>load</sub>       | Output load current                          | V <sub>Supply</sub> = 36V                               | 0.002 |                      | 1.5                 | Α    |

| R <sub>DSonHS</sub>     | Internal high/low side R <sub>DSon</sub>     | T <sub>junction</sub> = 125°C; I <sub>load</sub> =1A    |       | 0.6                  | 0.8                 | Ω    |

| V <sub>loop</sub>       | Loop voltage accuracy                        |                                                         |       | ±3%                  |                     |      |

| V <sub>REG_UV_f</sub>   | Under voltage falling threshold              | (24)                                                    | 84.5  | 87                   | 89.5                | %    |

| V <sub>REG_UV_r</sub>   | Under voltage rising threshold               | (24)                                                    | 90.5  | 93                   | 95.5                | %    |