# SN65DSI84 MIPI® DSI Bridge To FLATLINK™ LVDS Single Channel DSI to Dual-Link LVDS Bridge

#### 1 Features

- Implements MIPI® D-PHY version 1.00.00 physical layer front-end and display serial interface (DSI) version 1.02.00

- Single channel DSI receiver configurable for one, two, three, or four D-PHY data lanes per channel operating up to 1 Gbps per lane

- Supports 18 bpp and 24-bpp DSI video packets with RGB666 and RGB888 formats

- Suitable for 60-fps WUXGA 1920 × 1200 resolution at 18-bpp and 24-bpp color, 60 fps 1366 × 768 at 18 bpp and 24 bpp

- FlatLink™ output configurable for single-link or dual-link LVDS

- Supports single channel DSI to dual-link LVDS operating mode

- LVDS output clock range of 25 MHz to 154 MHz in dual-link or single-link modes

- LVDS pixel clock may be sourced from freerunning continuous D-PHY clock or external reference clock (REFCLK)

- 1.8-V main V<sub>CC</sub> power supply

- Low power features include shutdown mode, reduced LVDS output voltage swing, common mode, and MIPI ultra-low power state (ULPS) support

- LVDS channel swap, LVDS PIN order reverse feature for ease of PCB routing

- ESD rating ±2 kV (HBM)

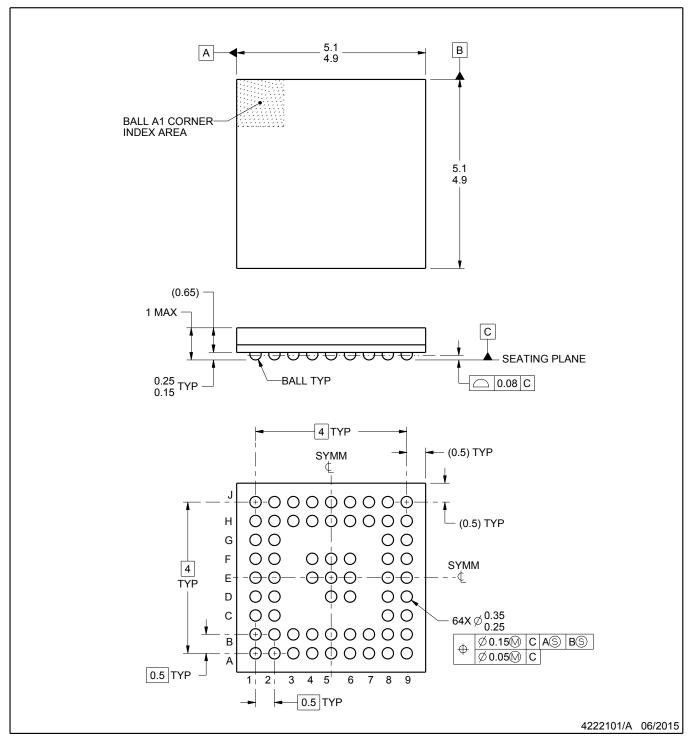

- Packaged in 64-pin 5-mm × 5-mm nFBGA (ZXH)

- Temperature range: -40°C to 85°C

## 2 Applications

- PC & notebooks

- **Tablets**

- Connected peripherals & printers

## 3 Description

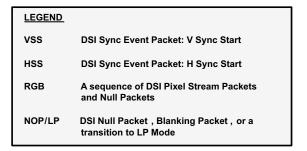

The SN65DSI84 DSI to FlatLink™ bridge features a single-channel MIPI® D-PHY receiver front-end configuration with 4 lanes per channel operating at 1 Gbps per lane; a maximum input bandwidth of 4 Gbps. The bridge decodes MIPI® DSI 18bpp RGB666 and 24 bpp RGB888 packets and converts the formatted video data stream to a FlatLink™ compatible LVDS output operating at pixel clocks operating from 25 MHz to 154 MHz, offering a Dual-Link LVDS, Single-Link LVDS interface with four data lanes per link.

The SN65DSI84 is well suited for WUXGA 1920 x 1200 at 60 frames per second, with up to 24 bits-perpixel. Partial line buffering is implemented to accommodate the data stream mismatch between the DSI and LVDS interfaces.

Designed with industry compliant technology, the SN65DSI84 is compatible with a wide range of micro-processors, and is designed with a range of power management features including lowswing LVDS outputs, and the MIPI® defined ultra-low power state (ULPS) support.

The SN65DSI84 is implemented in a small outline 5x5mm nFBGA at 0.5 mm pitch package, and operates across a temperature range from -40°C to 85°C.

### Device Information (1)

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| SN65DSI84   | nFBGA (64) | 5.00 mm × 5.00 mm |

For all available packages, see the orderable addendum at the end of the datasheet.

**Typical Application**

#### **Table of Contents**

| 1 Features                           | 1 7.4 Device Functional Modes | 14 |

|--------------------------------------|-------------------------------|----|

| 2 Applications                       | .1 7.5 Programming            | 22 |

| 3 Description                        |                               | 23 |

| 4 Revision History                   |                               |    |

| 5 Pin Configuration and Functions    |                               |    |

| 6 Specifications                     |                               |    |

| 6.1 Absolute Maximum Ratings         |                               |    |

| 6.2 EDS Ratings                      |                               |    |

| 6.3 Recommended Operating Conditions |                               |    |

| 6.4 Thermal Information              | 6 10 Layout                   | 41 |

| 6.5 Electrical Characteristics       |                               |    |

| 6.6 Switching Characteristics        |                               |    |

| 7 Detailed Description1              |                               |    |

| 7.1 Overview1                        |                               | 43 |

| 7.2 Functional Block Diagram1        | 12 11.2 Community Resources   | 43 |

| 7.3 Feature Description1             | <u> </u>                      |    |

| •                                    |                               |    |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes                | from    | Revision  | G (June | 2018) to | Revision  | H | October | 20201 |

|------------------------|---------|-----------|---------|----------|-----------|---|---------|-------|

| Ullallu <del>u</del> 5 | 11 0111 | VEAISIOII | GiJulie | 2010110  | V6A121011 | п | OCLUDE  | 20201 |

| Page |  |

|------|--|

|------|--|

| • | NOTE: The device in the MicroStar Jr. BGA packaging were redesigned using a laminate nFBGA packag                                                                                                               |      |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | This nFBGA package offers datasheet-equivalent electrical performance. It is also footprint equivalent to MicroStar Jr. BGA. The new package designator in place of the discontinued package designator will be | ıne  |

|   | updated throughout the datasheet                                                                                                                                                                                |      |

| • | Changed u*jr ZQE to nFBGA ZXH                                                                                                                                                                                   |      |

|   | Changed u*jr ZQE to nFBGA ZXH                                                                                                                                                                                   |      |

|   | Changed u*jr ZQE to nFBGA ZXH. Updated thermal information                                                                                                                                                      |      |

| • | Changed u*jr ZQE to nFBGA ZXH                                                                                                                                                                                   | 4    |

| С | hanges from Revision F (August 2015) to Revision G (June 2018)                                                                                                                                                  | Page |

| • | Deleted figure Shutdown and Reset Timing Definition While V <sub>CC</sub> Is High                                                                                                                               | 9    |

| • | Changed the paragraph following Figure 7-3                                                                                                                                                                      | 14   |

| • | Changed Recommended Initialization Sequence To: Initialization Sequence                                                                                                                                         | 1    |

| • | Changed Table 7-2                                                                                                                                                                                               | 14   |

| • | Changed item 3 in Video Stop and Restart Sequence From: Drive all DSI input lanes including DSI CLK la                                                                                                          | ane  |

## Changes from Revision E (October 2013) to Revision F (August 2015)

Page

Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device

Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout

section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information

section

to LP11. To: Drive all DSI data lanes to LP11, but keep the DSI CLK lanes in HS. ......33

- Changed ULPS Itemized List, item 3 from "Wait for the PLL\_LOCK bit (CSR 0x0A.7) to be set" to "Wait for a minimum of 3 ms."

- Changed Initialization Sequence Description for Init seq7 from "Wait for the PLL\_LOCK bit to be set (CSR 0x0A.7)" to "Wait for a minimum of 3 ms."

- Changed Table 7-6 Address 0x0A, Bit 7 description from "PLL\_LOCK" to "PLL\_EN\_STAT".....23

- Changed Address 0x18, Bits 3, 2, 1, and 0 Descriptions in Table 7-8 for clarification......23

|                                                  | f the Video STOP and Restart sequence from "Clear the PLL_EN bit to 0(CSR<br>I bit to 0 (CSR 0x0D.0)" |      |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|

| Changes from Revis                               | sion D (August 2013) to Revision E (October 2013)                                                     | Page |

| Added rows for Bit                               | s 7, and 6:5 to Table 7-7 CSR Bit Field Definition – DSI Registers                                    | 23   |

| Changes from Revis                               | sion C (December 2012) to Revision D (August 2013)                                                    | Page |

| Aligned package of                               | lescription throughout datasheet                                                                      | 1    |

| Changes from Revis                               | sion A (December 2012) to Revision B (December 2012)                                                  | Page |

| <ul> <li>Changed PGBA to</li> </ul>              | PBGA                                                                                                  | 1    |

| Changes from Revis                               | sion * (August 2012) to Revision A (December 2012)                                                    | Page |

| <ul> <li>Changed the value</li> </ul>            | e of V <sub>OH</sub> From: 1.3 MIN To: 1.25 MIN                                                       | 7    |

| <ul> <li>Changed the I<sub>CC</sub> T</li> </ul> | YP value From: 125 To: 106 and MAX value From: 200 To: 150                                            | 7    |

| <ul> <li>Added a TYP valu</li> </ul>             | e of 7.7 to I <sub>ULPS</sub>                                                                         | 7    |

| <ul> <li>Changed the I<sub>RST</sub></li> </ul>  | TYP value From: 0.05 To: 0.04 and MAX value From: 0.2 To: 0.06                                        | 7    |

| <ul> <li>changed the value</li> </ul>            | s of  VOD                                                                                             | 7    |

| <ul> <li>Changed the value</li> </ul>            | es of $V_{OC(SS)}$ for test conditions CSR 0x19.6 = 0 and, or CSR 0x19.4 = 0                          | 7    |

|                                                  | e 2                                                                                                   |      |

|                                                  | 3                                                                                                     |      |

| · Changed the SWI                                | TCHING CHARACTERISTICS table                                                                          | 9    |

| Changed the description                          | ription of CHA_LVDS_VOD_SWING                                                                         | 23   |

|                                                  | ription of CHB_LVDS_VOD_SWING                                                                         |      |

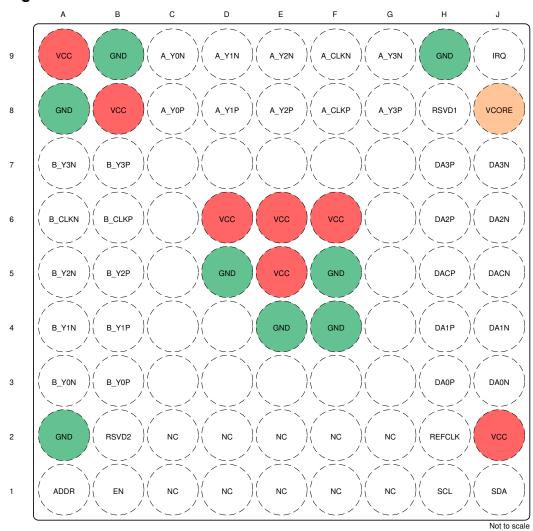

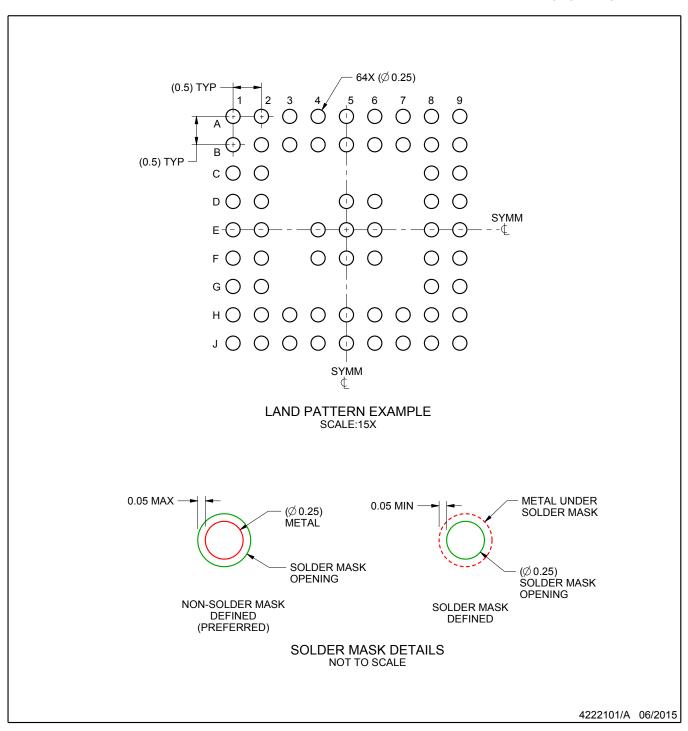

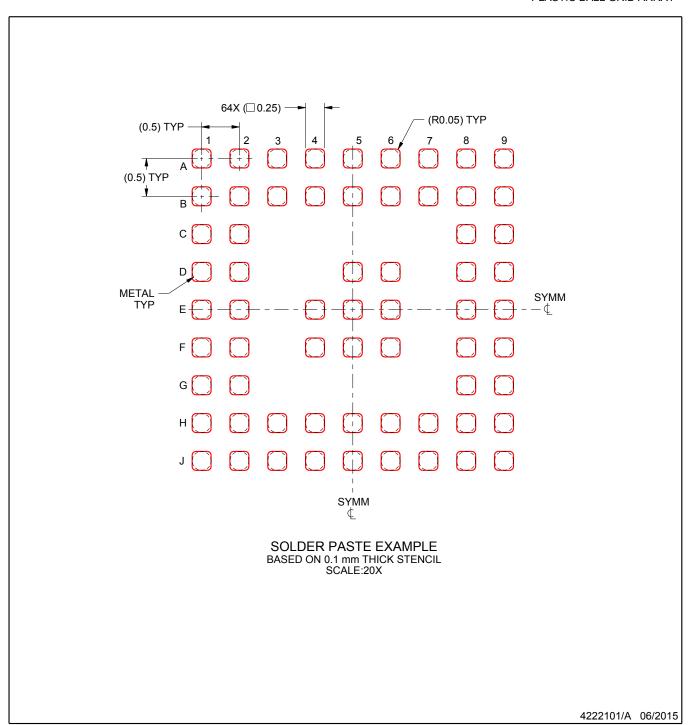

## **5 Pin Configuration and Functions**

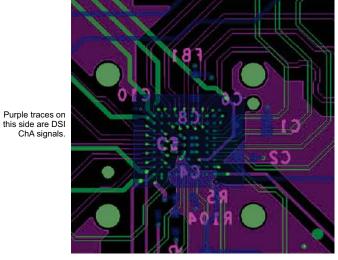

To minimize the power supply noise floor, provide good decoupling near the SN65DSI84 power pins. The use of four ceramic capacitors ( $2x \ 0.1 \ \mu F$  and  $2x \ 0.01 \ \mu F$ ) provides good performance. At the least, it is recommended to install one  $0.1 \ \mu F$  and one  $0.01 \ \mu F$  capacitor near the SN65DSI84. To avoid large current loops and trace inductance, the trace length between decoupling capacitor and device power inputs pins must be minimized. Placing the capacitor underneath the SN65DSI84 on the bottom of the PCB is often a good choice.

Figure 5-1. ZXH Package 64-Pin nFBGA Top View

Table 5-1. Pin Functions

|      | PIN |                 | DESCRIPTION                                                |

|------|-----|-----------------|------------------------------------------------------------|

| NAME | NO. | I/O             | DESCRIPTION                                                |

| DA0P | H3  |                 | MIPI® D-PHY Channel A Data Lane 0; data rate up to 1 Gbps. |

| DA0N | J3  |                 |                                                            |

| DA1P | H4  |                 | MIPI® D-PHY Channel A Data Lane 1; data rate up to 1 Gbps. |

| DA1N | J4  | LVDS Input (HS) |                                                            |

| DA2P | H6  | CMOS Input (LS) | MIPI® D-PHY Channel A Data Lane 2; data rate up to 1 Gbps. |

| DA2N | J6  | (Failsafe)      |                                                            |

| DA3P | H7  |                 | MIPI® D-PHY Channel A Data Lane 3; data rate up to 1 Gbps. |

| DA3N | J7  |                 |                                                            |

| DACP | H5  |                 | MIPI® D-PHY Channel A Clock Lane; operates up to 500 MHz.  |

| DACN | J5  |                 |                                                            |

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

## Table 5-1. Pin Functions (continued)

|        | Table 5-1. Pin Functions (continued) |                                        |                                                                                                                                                                                                                                                                                               |  |  |  |

|--------|--------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME   | PIN                                  | 1/0                                    | DESCRIPTION                                                                                                                                                                                                                                                                                   |  |  |  |

| NAME   | NO. C2, C1, D2, D1, F2,              | I/O                                    |                                                                                                                                                                                                                                                                                               |  |  |  |

| NC     | F1, G2, G1, E2, E1                   | No connects.                           | These pins should not be connected to any signal, power or ground.                                                                                                                                                                                                                            |  |  |  |

| A_Y0P  | C8                                   |                                        | FlatLink™ Channel A LVDS Data Output 0.                                                                                                                                                                                                                                                       |  |  |  |

| A_Y0N  | C9                                   |                                        |                                                                                                                                                                                                                                                                                               |  |  |  |

| A_Y1P  | D8                                   |                                        | FlatLink™ Channel A LVDS Data Output 1.                                                                                                                                                                                                                                                       |  |  |  |

| A_Y1N  | D9                                   |                                        |                                                                                                                                                                                                                                                                                               |  |  |  |

| A_Y2P  | E8                                   |                                        | FlatLink™ Channel A LVDS Data Output 2.                                                                                                                                                                                                                                                       |  |  |  |

| A_Y2N  | E9                                   |                                        |                                                                                                                                                                                                                                                                                               |  |  |  |

| A_Y3P  | G8                                   |                                        | FlatLink™ Channel A LVDS Data Output 3. A_Y3P and A_Y3N shall be left NC for 18 bpp panels.                                                                                                                                                                                                   |  |  |  |

| A_Y3N  | G9                                   |                                        |                                                                                                                                                                                                                                                                                               |  |  |  |

| A_CLKP | F8                                   |                                        | FlatLink™ Channel A LVDS Clock                                                                                                                                                                                                                                                                |  |  |  |

| A_CLKN | F9                                   | LVDS Output                            |                                                                                                                                                                                                                                                                                               |  |  |  |

| B_Y0P  | B3                                   |                                        | FlatLink™ Channel B LVDS Data Output 0.                                                                                                                                                                                                                                                       |  |  |  |

| B_Y0N  | A3                                   |                                        |                                                                                                                                                                                                                                                                                               |  |  |  |

| B_Y1P  | B4                                   |                                        | FlatLink™ Channel B LVDS Data Output 1.                                                                                                                                                                                                                                                       |  |  |  |

| B_Y1N  | A4                                   |                                        |                                                                                                                                                                                                                                                                                               |  |  |  |

| B_Y2P  | B5                                   |                                        | FlatLink™ Channel B LVDS Data Output 2.                                                                                                                                                                                                                                                       |  |  |  |

| B_Y2N  | A5                                   |                                        |                                                                                                                                                                                                                                                                                               |  |  |  |

| B_Y3P  | В7                                   |                                        | FlatLink™ Channel B LVDS Data Output 3. B_Y3P and B_Y3N shall be left NC for 18 bpp panels.                                                                                                                                                                                                   |  |  |  |

| B_Y3N  | A7                                   |                                        |                                                                                                                                                                                                                                                                                               |  |  |  |

| B_CLKP | B6                                   |                                        | FlatLink™ Channel B LVDS Clock.                                                                                                                                                                                                                                                               |  |  |  |

| B_CLKN | A6                                   |                                        |                                                                                                                                                                                                                                                                                               |  |  |  |

| RSVD1  | H8                                   | CMOS Input/Output with pulldown        | Reserved. This pin should be left unconnected for normal operation.                                                                                                                                                                                                                           |  |  |  |

| RSVD2  | B2                                   | CMOS Input with pulldown               | Reserved. This pin should be left unconnected for normal operation.                                                                                                                                                                                                                           |  |  |  |

| ADDR   | A1                                   | CMOS Input/Output                      | Local I <sup>2</sup> C Interface Target Address Select. See Table 7-4. In normal operation this pin is an input. When the ADDR pin is programmed high, it should be tied to the same 1.8 V power rails where the SN65DSI84 VCC 1.8 V power rail is connected.                                 |  |  |  |

| EN     | B1                                   | CMOS Input with pullup (Failsafe)      | Chip Enable and Reset. Device is reset (shutdown) when EN is low.                                                                                                                                                                                                                             |  |  |  |

| REFCLK | H2                                   | CMOS Input<br>(Failsafe)               | Optional External Reference Clock for LVDS Pixel Clock. If an External Reference Clock is not used, this pin should be pulled to GND with an external resistor. The source of the reference clock should be placed as close as possible with a series resistor near the source to reduce EMI. |  |  |  |

| SCL    | H1                                   |                                        | Local I <sup>2</sup> C Interface Clock.                                                                                                                                                                                                                                                       |  |  |  |

| SDA    | J1                                   | Open Drain Input/<br>Output (Failsafe) | Local I <sup>2</sup> C Interface Bi-directional Data Signal.                                                                                                                                                                                                                                  |  |  |  |

| IRQ    | J9                                   | CMOS Output                            | Interrupt Signal.                                                                                                                                                                                                                                                                             |  |  |  |

| GND    | A2, A8, B9, D5, E4,<br>F4, F5, H9    |                                        | Reference Ground.                                                                                                                                                                                                                                                                             |  |  |  |

| vcc    | A9, B8, D6, E5, E6,<br>F6, J2        | Power Supply                           | 1.8 V Power Supply.                                                                                                                                                                                                                                                                           |  |  |  |

| VCORE  | J8                                   |                                        | 1.1 V Output from Voltage Regulator. This pin must have a 1 µF external capacitor to GND.                                                                                                                                                                                                     |  |  |  |

## **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted) (1)

|                                      |                                          | MIN  | MAX   | UNIT |

|--------------------------------------|------------------------------------------|------|-------|------|

| Supply Voltage                       | V <sub>CC</sub>                          | -0.3 | 2.175 | V    |

| Input Valtage                        | CMOS Input Terminals                     | -0.5 | 2.175 | V    |

| Input Voltage                        | DSI Input Terminals (DA x P/N, DB x P/N) | -0.4 | 1.4   | V    |

| Storage Temperature T <sub>stg</sub> |                                          | -65  | 105   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 EDS Ratings

|                    |               |                                                                                          | VALUE | UNIT |

|--------------------|---------------|------------------------------------------------------------------------------------------|-------|------|

|                    | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±200  |      |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                      |                                                | MIN                         | NOM  | MAX  | UNIT              |

|----------------------|------------------------------------------------|-----------------------------|------|------|-------------------|

| V <sub>CC</sub>      | VCC Power supply                               | 165                         | 18   | 195  | V                 |

| V <sub>PSN</sub>     | Supply noise on any V <sub>CC</sub> pin        | f <sub>(noise)</sub> > 1MHz |      | 0.05 | V                 |

| T <sub>A</sub>       | Operating free-air temperature                 | -40                         |      | 85   | °C                |

| T <sub>CASE</sub>    | Case temperature                               |                             |      | 92.2 | °C                |

| V <sub>DSI_PIN</sub> | DSI input pin voltage range                    | -50                         |      | 1350 | mV                |

| f <sub>(I2C)</sub>   | Local I <sup>2</sup> C input frequency         |                             |      | 400  | kHz               |

| f <sub>HS_CLK</sub>  | DSI HS clock input frequency                   | 40                          |      | 500  | MHz               |

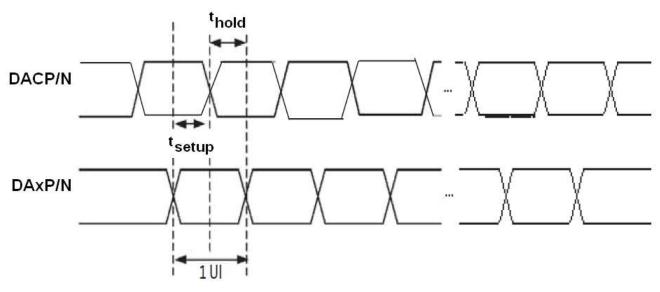

| t <sub>setup</sub>   | DSI HS data to clock setup time                |                             | 0.15 |      | UI <sup>(1)</sup> |

| t <sub>hold</sub>    | DSI HS data to clock hold time; see Figure 6-4 | 0.15                        |      |      | UI                |

| Z <sub>L</sub>       | LVDS output differential impedance             | 90                          |      | 132  | Ω                 |

<sup>(1)</sup> The unit interval (UI) is one half of the period of the HS clock; at 500 MHz the minimum setup and hold time is 150 ps.

## **6.4 Thermal Information**

|                       | THERMAL METRIC <sup>(1)</sup>                | SN65DSI84  ZXH (nFBGA)  64 PINS | UNIT |

|-----------------------|----------------------------------------------|---------------------------------|------|

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 55.1                            | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 30.6                            | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 31.0                            | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.8                             | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 30.8                            | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: SN65DSI84

## **6.5 Electrical Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                                                          | TEST CONDITIONS                                              | MIN       | TYP <sup>(1)</sup> | MAX       | UNIT |

|----------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------|--------------------|-----------|------|

| V <sub>IL</sub>      | Low-level control signal input voltage                                             |                                                              |           |                    | 0.3 x VCC | V    |

| V <sub>IH</sub>      | High-level control signal input voltage                                            |                                                              | 0.7 x VCC |                    |           | V    |

| V <sub>OH</sub>      | High-level output voltage                                                          | I <sub>OH</sub> = –4 mA                                      | 1.25      |                    |           | V    |

| V <sub>OL</sub>      | Low-level output voltage                                                           | I <sub>OL</sub> = 4 mA                                       |           |                    | 0.4       | V    |

| I <sub>LKG</sub>     | Input failsafe leakage current                                                     | V <sub>CC</sub> = 0; V <sub>CC(PIN)</sub> = 1.8 V            |           |                    | ±30       | μA   |

| I <sub>IH</sub>      | High level input current                                                           | Any input terminal                                           |           |                    | ±30       | μA   |

| I <sub>IL</sub>      | Low level input current                                                            | Any input terminal                                           |           |                    | ±30       | μA   |

| l <sub>oz</sub>      | High-impedance output current                                                      | Any output terminal                                          |           |                    | ±10       | μA   |

| Ios                  | Short-circuit output current                                                       | Any output driving GND short                                 |           |                    | ±20       | mA   |

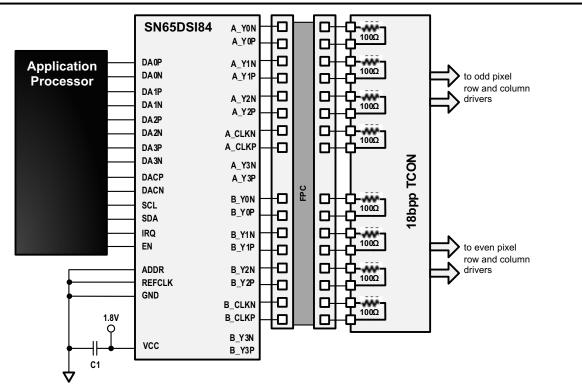

| I <sub>cc</sub>      | Device active current                                                              | see <sup>(2)</sup>                                           |           | 106                | 150       | mA   |

| I <sub>ULPS</sub>    | Device standby current                                                             | All data and clock lanes are in ultra-low power state (ULPS) |           | 7.7                | 10        | mA   |

| I <sub>RST</sub>     | Shutdown current                                                                   | EN = 0                                                       |           | 0.04               | 0.06      | mA   |

| R <sub>EN</sub>      | EN control input resistor                                                          |                                                              |           | 200                |           | kΩ   |

| MIPI DSI IN          | TERFACE                                                                            |                                                              |           |                    |           |      |

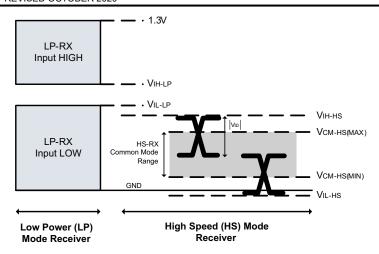

| V <sub>IH-LP</sub>   | LP receiver input high threshold                                                   | See Figure 6-1                                               | 880       |                    |           | mV   |

| V <sub>IL-LP</sub>   | LP receiver input low threshold                                                    | See Figure 6-1                                               |           |                    | 550       | mV   |

| V <sub>ID</sub>      | HS differential input voltage                                                      |                                                              | 70        |                    | 270       | mV   |

| V <sub>IDT</sub>     | HS differential input voltage threshold                                            |                                                              |           |                    | 50        | mV   |

| V <sub>IL-ULPS</sub> | LP receiver input low threshold; ultra-low power state (ULPS)                      |                                                              |           |                    | 300       | mV   |

| V <sub>CM-HS</sub>   | HS common mode voltage; steady-state                                               |                                                              | 70        |                    | 330       | mV   |

| ΔV <sub>CM-HS</sub>  | HS common mode peak-to-peak variation including symbol delta and interference      |                                                              |           |                    | 100       | mV   |

| V <sub>IH-HS</sub>   | HS single-ended input high voltage                                                 | See Figure 6-1                                               |           |                    | 460       | mV   |

| V <sub>IL-HS</sub>   | HS single-ended input low voltage                                                  | See Figure 6-1                                               | -40       |                    |           | mV   |

| V <sub>TERM-EN</sub> | HS termination enable; single-ended input voltage (both Dp AND Dn apply to enable) | Termination is switched simultaneous for Dn and Dp           |           |                    | 450       | mV   |

| R <sub>DIFF-HS</sub> | HS mode differential input impedance                                               |                                                              | 80        |                    | 125       | Ω    |

over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                                                                         | TEST CONDITIONS                                                                                    | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |  |

|--------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|--------------------|------|------|--|

| LATLINK            | LVDS OUTPUT                                                                       |                                                                                                    |      |                    |      |      |  |

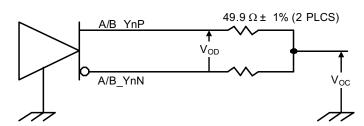

|                    |                                                                                   | CSR 0x19.3:2=00 and, or CSR 0x19.1:0=00; 100 Ω near end termination                                | 180  | 245                | 313  |      |  |

|                    |                                                                                   | CSR 0x19.3:2=01 and/or CSR 0x19.1:0=01; 100 Ω near end termination                                 | 215  | 293                | 372  |      |  |

|                    |                                                                                   | CSR 0x19.3:2=10 and, or CSR 0x19.1:0=10; 100 Ω near end termination                                | 250  | 341                | 430  |      |  |

|                    | Steady-state differential output voltage for                                      | CSR 0x19.3:2=11 and/or CSR 0x19.1:0=11; 100 Ω near end termination                                 | 290  | 389                | 488  | mV   |  |

|                    | A_Y x P/N and B_Y x P/N                                                           | CSR 0x19.3:2=00 and, or CSR 0x19.1:0=00; 200 Ω near end termination                                | 150  | 204                | 261  | IIIV |  |

| IV <sub>OD</sub> I |                                                                                   | CSR 0x19.3:2=01 and, or CSR 0x19.1:0=01; 200 Ω near end termination                                | 200  | 271                | 346  |      |  |

|                    |                                                                                   | CSR 0x19.3:2=10 and, or CSR 0x19.1:0=10; 200 Ω near end termination                                | 250  | 337                | 428  |      |  |

|                    |                                                                                   | CSR 0x19.3:2=11 and, or CSR 0x19.1:0=11; 200 Ω near end termination                                | 300  | 402                | 511  |      |  |

|                    | Steady-state differential output voltage for                                      | CSR 0x19.3:2=00 and, or CSR 0x19.1:0=00 100 Ω near end termination                                 | 140  | 191                | 244  | mV   |  |

|                    |                                                                                   | CSR 0x19.3:2=01 and, or CSR 0x19.1:0=01 100 $\Omega$ near end termination                          | 168  | 229                | 290  |      |  |

|                    |                                                                                   | CSR 0x19.3:2=10 and, or CSR 0x19.1:0=10 100 $\Omega$ near end termination                          | 195  | 266                | 335  |      |  |

|                    |                                                                                   | CSR 0x19.3:2=11 and, or CSR 0x19.1:0=11 100 Ω near end termination                                 | 226  | 303                | 381  |      |  |

|                    | A_CLKP/N and B_CLKP/N                                                             | CSR 0x19.3:2=00 and, or CSR 0x19.1:0=00 200 $\Omega$ near end termination                          | 117  | 159                | 204  |      |  |

|                    |                                                                                   | CSR 0x19.3:2=01 and, or CSR 0x19.1:0=01 200 $\Omega$ near end termination                          | 156  | 211                | 270  |      |  |

|                    |                                                                                   | CSR 0x19.3:2=10 and, or CSR 0x19.1:0=10 200 Ω near end termination                                 | 195  | 263                | 334  |      |  |

|                    |                                                                                   | CSR 0x19.3:2=11 and, or CSR 0x19.1:0=11 200 Ω near end termination                                 | 234  | 314                | 399  |      |  |

| V <sub>OD</sub>    | Change in steady-state differential output voltage between opposite binary states | RL = 100 Ω                                                                                         |      |                    | 35   | mV   |  |

| OC(SS)             | Steady state common-mode output voltage <sup>(3)</sup>                            | CSR 0x19.6 = 1 and CSR 0x1B.6 = 1;<br>and, or CSR 0x19.4 = 1 and<br>CSR 0x1B.4 = 1; see Figure 6-2 | 0.8  | 0.9                | 1    | V    |  |

| . ·                | voitage                                                                           | CSR 0x19.6 = 0 and, or CSR 0x19.4 = 0;<br>see Figure 6-2                                           | 1.15 | 1.25               | 1.35 |      |  |

| OC(PP)             | Peak-to-peak common-mode output voltage                                           | see Figure 6-2                                                                                     |      |                    | 35   | mV   |  |

| LVDS DIS           | Pull-down resistance for disabled LVDS outputs                                    |                                                                                                    |      | 1                  |      | kΩ   |  |

- (1) All typical values are at  $V_{CC}$  = 1.8 V and  $T_A$  = 25°C

- (2) SN65DSI84: SINGLE Channel DSI to DUAL Channel LVDS, 1440 x 900

- a. number of LVDS lanes = 2 x (3 data lanes + 1 CLK lane)

- b. number of DSI lanes = 2 data lanes + 1 CLK lane

- c. LVDS CLK OUT = 53.25 M

- d. DSI CLK = 500 M

- e. RGB888, LVDS18bpp

Maximum values are at  $V_{CC}$  = 1.95 V and  $T_A$  = 85°C

(3) Tested at  $V_{CC}$  = 1.8 V ,  $T_A$  = -40°C for MIN,  $T_A$  = 25°C for TYP,  $T_A$  = 85°C for MAX.

## 6.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                                               | TEST CONDITIONS                                                   | MIN                       | TYP <sup>(1)</sup> | MAX                       | UNIT |

|---------------------------------|---------------------------------------------------------|-------------------------------------------------------------------|---------------------------|--------------------|---------------------------|------|

| DSI                             |                                                         |                                                                   |                           |                    |                           |      |

| t <sub>GS</sub>                 | DSI LP glitch suppression pulse width                   |                                                                   |                           |                    | 300                       | ps   |

| LVDS                            |                                                         |                                                                   |                           |                    |                           |      |

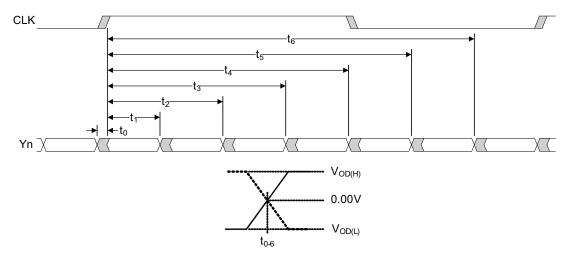

| t <sub>c</sub>                  | Output clock period                                     |                                                                   | 6.49                      |                    | 40                        | ns   |

| t <sub>w</sub>                  | High-level output clock (CLK) pulse duration            |                                                                   |                           | 4/7 tc             |                           | ns   |

| t <sub>0</sub>                  | Delay time, CLK↑ to 1st serial bit position             |                                                                   | -0.15                     | 0.15               |                           | ns   |

| t <sub>1</sub>                  | Delay time, CLK↑ to 2nd serial bit position             |                                                                   | 1/7 t <sub>c</sub> - 0.15 |                    | ns                        |      |

| t <sub>2</sub>                  | Delay time, CLK↑ to 3rd serial bit position             |                                                                   | 2/7 t <sub>c</sub> - 0.15 |                    | 2/7 t <sub>c</sub> + 0.15 | ns   |

| t <sub>3</sub>                  | Delay time, CLK↑ to 4th serial bit position             | t <sub>c</sub> = 6.49ns;<br>Input clock jitter < 25ps<br>(REFCLK) |                           |                    |                           |      |

| t <sub>4</sub>                  | Delay time, CLK↑ to 5th serial bit position             |                                                                   | 4/7 t <sub>c</sub> – 0.15 |                    | 4/7 t <sub>c</sub> + 0.15 | ns   |

| t <sub>5</sub>                  | Delay time, CLK↑ to 6th serial bit position             |                                                                   | 5/7 t <sub>c</sub> – 0.15 |                    | 5/7 t <sub>c</sub> + 0.15 | ns   |

| t <sub>6</sub>                  | Delay time, CLK↑ to 7th serial bit position             |                                                                   | 6/7 t <sub>c</sub> - 0.15 |                    | 6/7 t <sub>c</sub> + 0.15 | ns   |

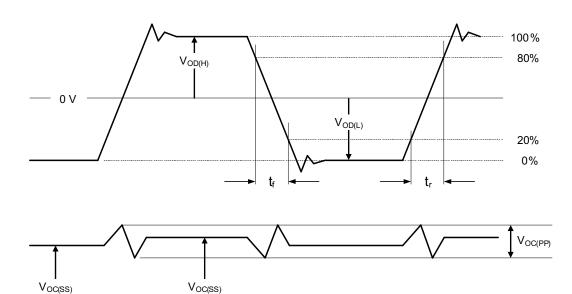

| t <sub>r</sub>                  | Differential output rise-time                           | See Figure 6-5                                                    | 180                       |                    | 500                       | ps   |

| t <sub>f</sub>                  | Differential output fall-time                           |                                                                   |                           |                    |                           |      |

| EN, ULPS, RE                    | SET                                                     |                                                                   |                           |                    |                           |      |

| t <sub>en</sub>                 | Enable time from EN or ULPS                             | -t <sub>c(o)</sub> = 12.9 ns                                      |                           |                    | 1                         | ms   |

| t <sub>dis</sub>                | Disable time to standby                                 | t <sub>c(0)</sub> = 12.9 119                                      |                           |                    | 0.1                       | 1115 |

| t <sub>reset</sub>              | Reset time                                              |                                                                   | 10                        |                    |                           | ms   |

| R <sub>EFCLK</sub>              |                                                         |                                                                   |                           |                    |                           |      |

| F <sub>REFCLK</sub>             | REFCLK Frequency. Supported frequencies: 25 MHz-154 MHz |                                                                   | 25                        |                    | 154                       | MHz  |

| t <sub>r</sub> , t <sub>f</sub> | REFCLK rise and fall time                               |                                                                   | 100 ps                    |                    | 1ns                       | s    |

| t <sub>pj</sub>                 | REFCLK Peak-to-Peak Phase Jitter                        |                                                                   |                           |                    | 50                        | ps   |

| Duty                            | REFCLK Duty Cycle                                       |                                                                   | 40%                       | 50%                | 60%                       |      |

| REFCLK or DS                    | SI CLK (DACP/N, DBCP/N)                                 |                                                                   |                           |                    |                           |      |

| SSC_CLKIN                       | SSC enabled Input CLK center spread depth (2)           |                                                                   | 0.5%                      | 1%                 | 2%                        |      |

| _                               | Modulation Frequency Range                              |                                                                   | 30                        |                    | 60                        | KHz  |

<sup>(1)</sup> All typical values are at  $V_{CC} = 1.8 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$

<sup>(2)</sup> For EMI reduction purpose, SN65DSI84 supports the center spreading of the LVDS CLK output through the REFCLK or DSI CLK input. The center spread CLK input to the REFCLK or DSI CLK is passed through to the LVDS CLK output A\_CLKP/N and/or B\_CLKP/N.

Figure 6-1. DSI Receiver Voltage Definitions

Figure 6-2. Test Load and Voltage Definitions for Flatlink Outputs

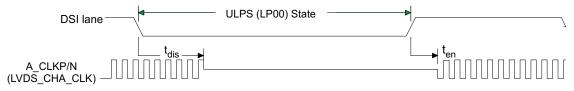

A. See the ULPS section of the data sheet for the ULPS entry and exit sequence.

B. ULPS entry and exit protocol and timing requirements must be met per MIPI® DPHY specification.

## Figure 6-3. ULPS Timing Definition

Figure 6-4. DSI HS Mode Receiver Timing Definitions

Figure 6-5. SN65DSI84 Flatlink Timing Definitions

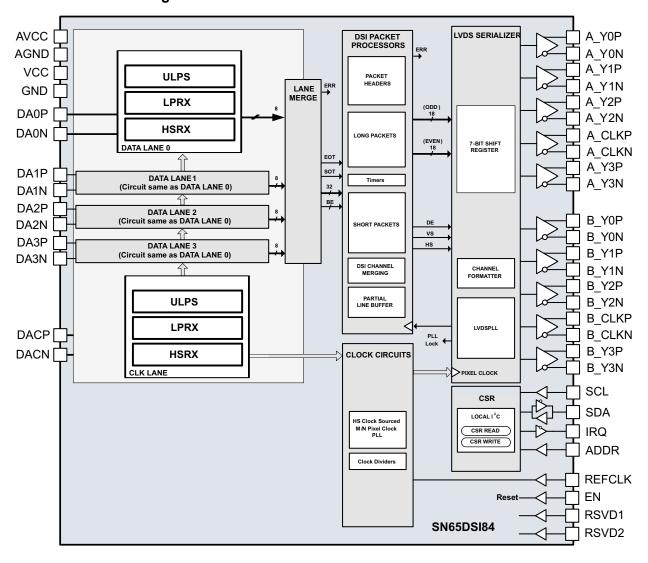

## 7 Detailed Description

## 7.1 Overview

The SN65DSI84 DSI to FlatLink bridge features a single0channel MIPI D-PHY receiver front-end configuration with 4 lanes per channel operating at 1 Gbps per lane; a maximum input bandwidth of 4 Gbps. The bridge decodes MIPI DSI 18bpp RGB666 and 240bpp RG888 packets and converts the formatted video data stream to a FlatLink compatible LVDS output operating at pixel clocks operating from 25 MHx to 154 MHz, offering a Dual-Link LVDS, Single-Link LVDS interface with four data lanes per link.

## 7.2 Functional Block Diagram

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

### 7.3 Feature Description

### 7.3.1 Clock Configurations and Multipliers

The FlatLink™ LVDS clock may be derived from the DSI channel A clock, or from an external reference clock source. When the MIPI® D-PHY channel A HS clock is used as the LVDS clock source, the D-PHY clock lane must operate in HS free-running (continuous) mode; this feature eliminates the need for an external reference clock reducing system costs

The reference clock source is selected by HS\_CLK\_SRC (CSR 0x0A.0) programmed through the local I<sup>2</sup>C interface. If an external reference clock is selected, it is multiplied by the factor in REFCLK\_MULTIPLIER (CSR 0x0B.1:0) to generate the FlatLink™ LVDS output clock. When an external reference clock is selected, it must be between 25 MHz and 154 MHz. If the DSI channel A clock is selected, it is divided by the factor in DSI\_CLK\_DIVIDER (CSR 0x0B.7:3) to generate the FlatLink™ LVDS output clock. Additionally, LVDS\_CLK\_RANGE (CSR 0x0A.3:1) and CH\_DSI\_CLK\_RANGE(CSR 0x12) must be set to the frequency range of the FlatLink™ LVDS output clock for and DSI Channel A input clock respectively the internal PLL to operate correctly. After these settings are programmed, PLL\_EN (CSR 0x0D.0) must be set to enable the internal PLL.

## 7.3.2 ULPS

The SN65DSI84 supports the MIPI defined ultra-low power state (ULPS). While the device is in the ULPS, the CSR registers are accessible via I2C interface. ULPS sequence should be issued to all active DSI CLK and/or DSI data lanes of the enabled DSI Channels for the SN65DSI84 enter the ULPS. The Following sequence should be followed to enter and exit the ULPS.

- 1. Host issues a ULPS entry sequence to all DSI CLK and data lanes enabled.

- 2. When host is ready to exit the ULPS mode, host issues a ULPS exit sequence to all DSI CLK and data lanes that need to be active in normal operation.

- 3. Wait for a minimum of 3 ms.

- 4. Set the SOFT\_RESET bit (CSR 0x09.0).

- 5. Device resumes normal operation. (i.e video streaming resumes on the panel).

## 7.3.3 LVDS Pattern Generation

The SN65DSI84 supports a pattern generation feature on LVDS Channels. This feature can be used to test the LVDS output path and LVDS panels in a system platform. The pattern generation feature can be enabled by setting the CHA\_TEST\_PATTERN bit at address 0x3C. No DSI data is received while the pattern generation feature is enabled.

There are three modes available for LVDS test pattern generation. The mode of test pattern generation is determined by register configuration as shown in Table 7-1.

Table 7-1. Video Registers

| Addr. bit | Register Name                  |

|-----------|--------------------------------|

| 0x20.7:0  | CHA_ACTIVE_LINE_LENGTH_LOW     |

| 0x21.3:0  | CHA_ACTIVE_LINE_LENGTH_HIGH    |

| 0x24.7:0  | CHA_VERTICAL_DISPLAY_SIZE_LOW  |

| 0x25.3:0  | CHA_VERTICAL_DISPLAY_SIZE_HIGH |

| 0x2C.7:0  | CHA_HSYNC_PULSE_WIDTH_LOW      |

| 0x2D.1:0  | CHA_HSYNC_PULSE_WIDTH_HIGH     |

| 0x30.7:0  | CHA_VSYNC_PULSE_WIDTH_LOW      |

| 0x31.1:0  | CHA_VSYNC_PULSE_WIDTH_HIGH     |

| 0x34.7:0  | CHA_HORIZONTAL_BACK_PORCH      |

| 0x36.7:0  | CHA_VERTICAL_BACK_PORCH        |

| 0x38.7:0  | CHA_HORIZONTAL_FRONT_PORCH     |

| 0x3A.7:0  | CHA_VERTICAL_FRONT_PORCH       |

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

#### 7.4 Device Functional Modes

### 7.4.1 Reset Implementation

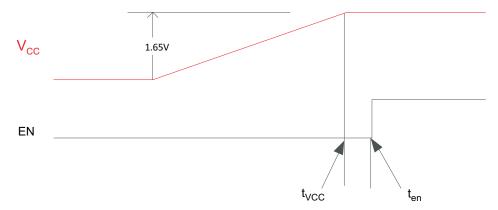

When EN is de-asserted (low), the SN65DSI84 is in SHUTDOWN or RESET state. In this state, CMOS inputs are ignored, the MIPI® D-PHY inputs are disabled and outputs are high impedance. It is critical to transition the EN input from a low to a high level after the  $V_{CC}$  supply has reached the minimum operating voltage as shown in Figure 7-1. This is achieved by a control signal to the EN input, or by an external capacitor connected between EN and GND.

Figure 7-1. Cold Start V<sub>CC</sub> Ramp up to EN

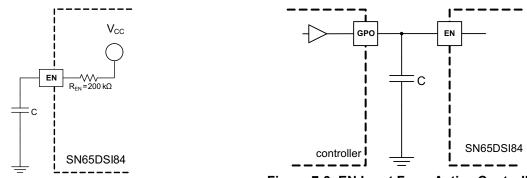

When implementing the external capacitor, the size of the external capacitor depends on the power up ramp of the  $V_{CC}$  supply, where a slower ramp-up results in a larger value external capacitor. See the latest reference schematic for the SN65DSI84 device and, or consider approximately 200 nF capacitor as a reasonable first estimate for the size of the external capacitor.

Both EN implementations are shown in Figure 7-2 and Figure 7-3.

Figure 7-2. External Capacitor Controlled EN

Figure 7-3. EN Input From Active Controller

### 7.4.2

When the SN65DSI84 is reset while  $V_{CC}$  is high, the EN pin must be held low for at least 10 ms before being asserted high as described in Table 7-2 to be sure that the device is properly reset. The DSI CLK lane MUST be in HS and the DSI data lanes MUST be driven to LP11 while the device is in reset before the EN pin is asserted per the timing described in Table 7-2.

#### 7.4.3 Initialization Sequence

Use the following initialization sequence to setup the SN65DSI84. This sequence is required for proper operation of the device. Steps 9 through 11 in the sequence are optional.

Also see to Figure 7-1.

### Table 7-2. Initialization Sequence

| INITIALIZATION<br>SEQUENCE<br>NUMBER | INITIALIZATION SEQUENCE DESCRIPTION                                                                                                                            |  |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Init seq 1                           | Power on                                                                                                                                                       |  |  |  |  |  |

| Init seq 2                           | After power is applied and stable, the DSI CLK lanes MUST be in HS state and the DSI data lanes MUST be driven to LP11 state                                   |  |  |  |  |  |

| Init seq 3                           | Set EN pin to Low                                                                                                                                              |  |  |  |  |  |

| Wait 10 ms <sup>(1)</sup>            | Wait 10 ms <sup>(1)</sup>                                                                                                                                      |  |  |  |  |  |

| Init seq 4                           | Tie EN pin to High                                                                                                                                             |  |  |  |  |  |

| Wait 10 ms <sup>(1)</sup>            |                                                                                                                                                                |  |  |  |  |  |

| Init seq 5                           | Initialize all CSR registers to their appropriate values based on the implementation (The SN65DSI8x is not functional until the CSR registers are initialized) |  |  |  |  |  |

| Init seq 6                           | Set the PLL_EN bit (CSR 0x0D.0)                                                                                                                                |  |  |  |  |  |

| Wait 10 ms <sup>(1)</sup>            |                                                                                                                                                                |  |  |  |  |  |

| Init seq 7                           | Set the SOFT_RESET bit (CSR 0x09.0)                                                                                                                            |  |  |  |  |  |

| Wait 10 ms <sup>(1)</sup>            |                                                                                                                                                                |  |  |  |  |  |

| Init seq 8                           | Change DSI data lanes to HS state and start DSI video stream                                                                                                   |  |  |  |  |  |

| Wait 5 ms <sup>(1)</sup>             |                                                                                                                                                                |  |  |  |  |  |

| Init seq 9                           | Read back all resisters and confirm they were correctly written                                                                                                |  |  |  |  |  |

| Init seq 10                          | Write 0xFF to CSR 0xE5 to clear the error registers                                                                                                            |  |  |  |  |  |

| Wait 1 ms <sup>(1)</sup>             |                                                                                                                                                                |  |  |  |  |  |

| Init seq 11                          | Read CSR 0xE5. If CSR 0xE5!= 0x00, then go back to step #2 and re-initialize                                                                                   |  |  |  |  |  |

<sup>(1)</sup> Minimum recommended delay. It is fine to exceed these.

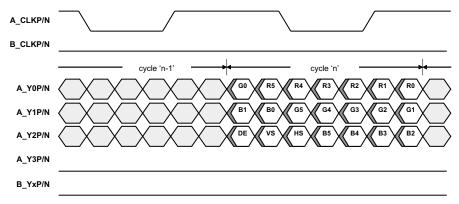

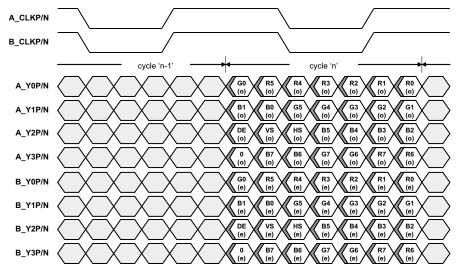

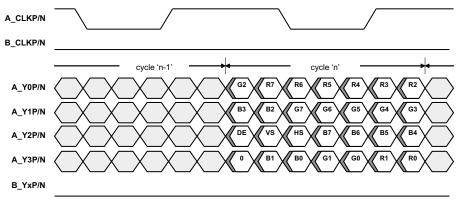

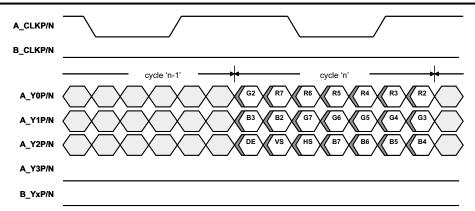

## 7.4.4 LVDS Output Formats

The SN65DSI84 processes DSI packets and produces video data driven to the FlatLink™ LVDS interface in an industry standard format. Single-Link LVDS and Dual-Link LVDS are supported by the SN65DSI84; when the FlatLink™ output is implemented in a Dual-Link configuration, channel A carries the odd pixel data, and channel B carries the even pixel data. During conditions such as the default condition, and some video synchronization periods, where no video stream data is passing from the DSI input to the LVDS output, the SN65DSI84 transmits zero value pixel data on the LVDS outputs while maintaining transmission of the vertical sync and horizontal sync status.

Figure 7-4 illustrates a Single-Link LVDS 18bpp application.

Figure 7-5 illustrates a Dual-Link 24 bpp application using Format 2, controlled by CHA\_24BPP\_FORMAT1 (CSR 0x18.1) and CHB\_24BPP\_FORMAT1 (CSR 0x18.0). In data Format 2, the two MSB per color are transferred on the Y3P/N LVDS lane.

Figure 7-6 illustrates a 24 bpp Single-Link application using Format 1. In data Format 1, the two LSB per color are transferred on the Y3P/N LVDS lane.

Figure 7-7 illustrates a Single-Link LVDS application where 24 bpp data is received from DSI and converted to 18 bpp data for transmission to an 18 bpp panel. This application is configured by setting CHA\_24BPP\_FORMAT1 (CSR 0x18.1) to '1' and CHA\_24BPP\_MODE (CSR 0x18.3) to '0'. In this configuration, the SN65DSI84 will not transmit the 2 LSB per color since the Y3P/N LVDS lane is disabled.

#### Note

Note: Figure 7-4, Figure 7-5, Figure 7-6, and Figure 7-7 only illustrate a few example applications for the SN65DSI84. Other applications are also supported.

DE = Data Enable; Channel B Clock, Channel B Data, and A\_Y3P/N are Output Low

Figure 7-4. Flatlink Output Data; Single-Link 18 Bpp

DE = Data Enable; (o) = Odd Pixels; (e) = Even Pixels

Figure 7-5. Flatlink Output Data (Format 2); Dual-Link 24 Bpp

DE = Data Enable; Channel B Clock and Data are Output Low

Figure 7-6. Flatlink Output Data (Format 1); Single-Link 24 Bpp

DE = Data Enable; Channel B Clock, Channel B Data, and A\_Y3P/N a re Output Low; Channel B Clock, Channel B Data, and A\_Y3P/N are Output Low

Figure 7-7. Flatlink Output Data (Format 1); 24-Bpp to Single-Link 18-Bpp Conversion

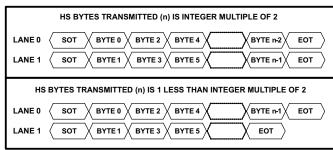

### 7.4.5 DSI Lane Merging

The SN65DSI84 supports four DSI data lanes per input channel, and may be configured to support one, two, or three DSI data lanes per channel. Unused DSI input pins on the SN65DSI84 should be left unconnected or driven to LP11 state. The bytes received from the data lanes are merged in HS mode to form packets that carry the video stream. DSI data lanes are bit and byte aligned.

Figure 7-8 illustrates the lane merging function for each channel; 4-Lane, 3-Lane, and 2-Lane modes are illustrated

4 DSI Data Lane Configuration (default)

3 DSI Data Lane Configuration

2 DSI Data Lane Configuration

Figure 7-8. SN65DSI84 DSI Lane Merging Illustration

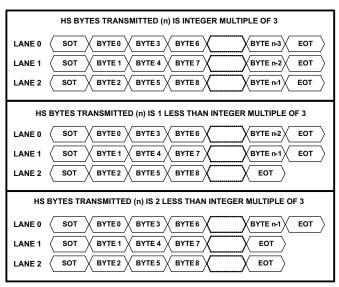

#### 7.4.6 DSI Pixel Stream Packets

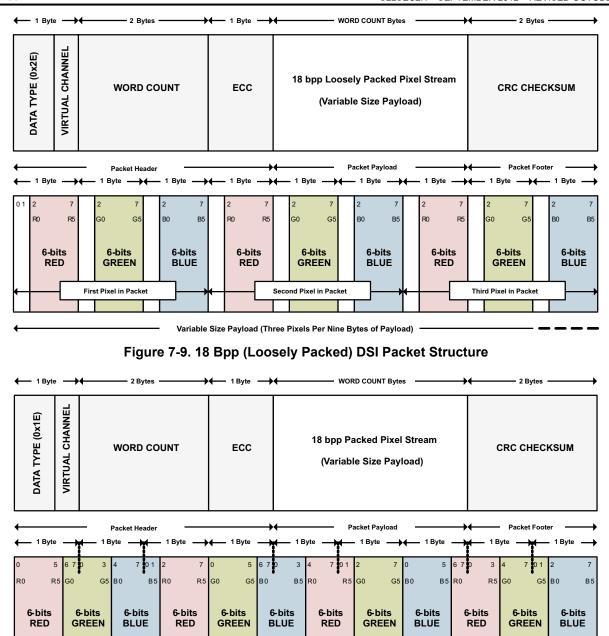

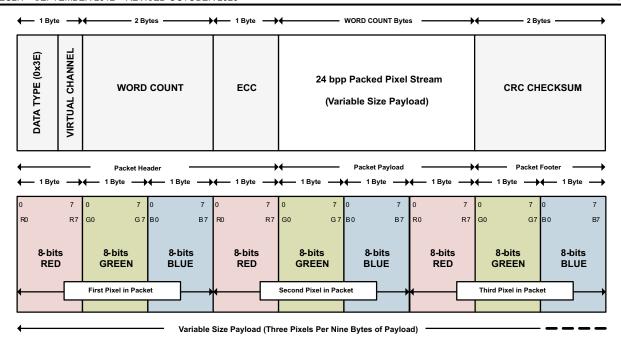

The SN65DSI84 processes 18bpp (RGB666) and 24 bpp (RGB888) DSI packets on each channel as shown in Figure 7-9, Figure 7-10, and Figure 7-11.

Submit Document Feedback

Figure 7-10. 18-Bpp (Tightly Packed) DSI Packet Structure

Variable Size Payload (Four Pixels Per Nine Bytes of Payload)

Third Pixel in Packet

Second Pixel in Packet

First Pixel in Packet

Fourth Pixel in Packet

Figure 7-11. 24-Bpp DSI Packet Structure

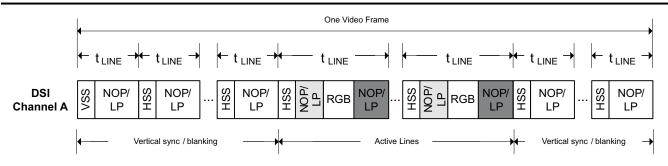

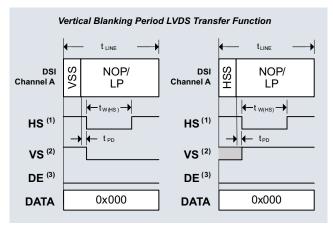

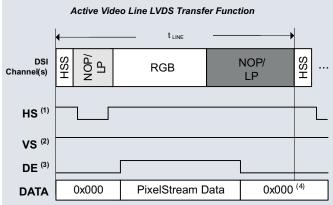

### 7.4.7 DSI Video Transmission Specifications

The SN65DSI84 supports burst video mode and non-burst video mode with sync events or with sync pulses packet transmission as described in the DSI specification. The burst mode supports time-compressed pixel stream packets that leave added time per scan line for power savings LP mode. The SN65DSI84 requires a transition to LP mode once per frame to enable PHY synchronization with the DSI host processor; however, for a robust and low-power implementation, the transition to LP mode is recommended on every video line.

Figure 7-12 illustrates the DSI video transmission applied to SN65DSI84 applications. In all applications, the LVDS output rate must be less than or equal to the DSI input rate. The first line of a video frame shall start with a VSS packet, and all other lines start with VSE or HSS. The position of the synchronization packets in time is of utmost importance since this has a direct impact on the visual performance of the display panel; that is, these packets generate the HS and VS (horizontal and vertical sync) signals on the LVDS interface after the delay programmed into CHA SYNC DELAY LOW/HIGH (CSR 0x28.7:0 and 0x29.3:0).

As required in the DSI specification, the SN65DSI84 requires that pixel stream packets contain an integer number of pixels (i.e. end on a pixel boundary); it is recommended to transmit an entire scan line on one pixel stream packet. When a scan line is broken in to multiple packets, inter-packet latency shall be considered such that the video pipeline (ie. pixel queue or partial line buffer) does not run empty (i.e. under-run); during scan line processing, if the pixel queue runs empty, the SN65DSI84 transmits zero data (18'b0 or 24'b0) on the LVDS interface.

#### Note

When the HS clock is used as a source for the LVDS pixel clock, the LP mode transitions apply only to the data lanes, and the DSI clock lane remains in the HS mode during the entire video transmission.

The DSI84 does not support the DSI Virtual Channel capability or reverse direction (peripheral to processor) transmissions.

<sup>\*</sup> VSS and HSS packets are required for DSI Channel B, although LVDS video sync signals are derived from DSI Channel A VSS and HSS packets

- (1) The assertion of HS is delayed  $(t_{PD})$  by a programmable number of pixel clocks from the last bit of VSS/HSS packet received on DSI. The HS pulse width  $(t_{W(HS)})$  is also programmable The illustration shows HS active low.

- (2) VS is signaled for a programmable number of lines  $(t_{LINE})$  and is asserted when HS is asserted for the first line of the frame . VS is de -asserted when HS is asserted after the number of lines programmed has been reached. The illustration shows VS active low

- (3) DE is asserted when active pixel data is transmitted on LVDS, and polarity is set independent to HS/VS. The illustration shows DE active high

- (4) After the last pixel in an active line is output to LVDS, the LVDS data is output zero

Figure 7-12. DSI Channel Transmission and Transfer Function

## 7.4.8 Operating Modes

The SN65DSI84 can be configured for several different operating modes via LVDS\_LINK\_CFG (CSR 0x18.4), LEFT\_RIGHT\_PIXELS (CSR 0x10.7), and DSI\_CHANNEL\_MODE (CSR 0x10.6:5). These modes are summarized in Table 7-3. In each of the modes, video data can be 18 bpp or 24 bpp.

Table 7-3. SN65DSI84 Operating Modes

| MODE                                 | CSR 0x18.4    | DESCRIPTION                                                                                                       |  |  |

|--------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| WODE                                 | LVDS_LINK_CFG | DESCRIPTION                                                                                                       |  |  |

| Single DSI Input to Single-Link LVDS | 1             | Single DSI Input on Channel A to Single-Link LVDS output on Channel A.                                            |  |  |

| Single DSI Input to Dual-Link LVDS   | 0             | Single DSI Input on Channel A to Dual-Link LVDS output with Odd pixels on Channel A and Even pixels on Channel B. |  |  |

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

## 7.5 Programming

## 7.5.1 Local I<sup>2</sup>C Interface Overview

The SN65DSI84 local I<sup>2</sup>C interface is enabled when EN is input high, access to the CSR registers is supported during ultra-low power state (ULPS). The SCL and SDA terminals are used for I<sup>2</sup>C clock and I<sup>2</sup>C data respectively. The SN65DSI84 I<sup>2</sup>C interface conforms to the two-wire serial interface defined by the I<sup>2</sup>C Bus Specification, Version 2.1 (January 2000), and supports fast mode transfers up to 400 kbps.

The device address byte is the first byte received following the START condition from the master device. The 7 bit device address for SN65DSI84 is factory preset to 010110X with the least significant bit being determined by the ADDR control input. Table 7-4 clarifies the SN65DSI84 target address.

Table 7-4. SN65DSI84 I<sup>2</sup>C Target Address Description (1) (2)

| SN65DSI84 I2C TARGET ADDRESS |       |       |       |       |       |       |             |

|------------------------------|-------|-------|-------|-------|-------|-------|-------------|

| BIT 7 (MSB)                  | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 (W/R) |

| 0                            | 1     | 0     | 1     | 1     | 0     | ADDR  | 0/1         |

- (1) When ADDR=1, Address Cycle is 0x5A (Write) and 0x5B (Read)

- (2) When ADDR=0, Address Cycle is 0x58 (Write) and 0x59 (Read)

The following procedure is followed to write to the SN65DSI84 I<sup>2</sup>C registers.

- 1. The master initiates a write operation by generating a start condition (S), followed by the SN65DSI84 7-bit address and a zero-value "W/R" bit to indicate a write cycle.

- 2. The SN65DSI84 acknowledges the address cycle.

- 3. The master presents the sub-address (I2C register within SN65DSI84) to be written, consisting of one byte of data. MSB-first.

- 4. The SN65DSI84 acknowledges the sub-address cycle.

- 5. The master presents the first byte of data to be written to the I<sup>2</sup>C register.

- 6. The SN65DSI84 acknowledges the byte transfer.

- 7. The master may continue presenting additional bytes of data to be written, with each byte transfer completing with an acknowledge from the SN65DSI84.

- 8. The master terminates the write operation by generating a stop condition (P).

The following procedure is followed to read the SN65DSI84 I<sup>2</sup>C registers:

- 1. The master initiates a read operation by generating a start condition (S), followed by the SN65DSI84 7-bit address and a one-value "W/R" bit to indicate a read cycle.

- 2. The SN65DSI84 acknowledges the address cycle.

- 3. The SN65DSI84 transmit the contents of the memory registers MSB-first starting at register 00h. If a write to the SN65DSI84 I2C register occurred prior to the read, then the SN65DSI84 will start at the sub-address specified in the write.

- 4. The SN65DSI84 will wait for either an acknowledge (ACK) or a not-acknowledge (NACK) from the master after each byte transfer; the I2C master acknowledges reception of each data byte transfer.

- 5. If an ACK is received, the SN65DSI84 transmits the next byte of data.

- 6. The master terminates the read operation by generating a stop condition (P).

The following procedure is followed for setting a starting sub-address for I<sup>2</sup>C reads:

- 1. The master initiates a write operation by generating a start condition (S), followed by the SN65DSI84 7-bit address and a zero-value "W/R" bit to indicate a write cycle

- 2. The SN65DSI84 acknowledges the address cycle.

- 3. The master presents the sub-address (I<sup>2</sup>C register within SN65DSI84) to be written, consisting of one byte of data, MSB-first.

- 4. The SN65DSI84 acknowledges the sub-address cycle.

- 5. The master terminates the write operation by generating a stop condition (P).

Product Folder Links: SN65DSI84

## 7.6 Register Maps

## 7.6.1 Control and Status Registers Overview

Many of the SN65DSI84 functions are controlled by the Control and Status Registers (CSR). All CSR registers are accessible through the local  $I^2C$  interface.

See the following tables for the SN65DSI84 CSR descriptions. Reserved or undefined bit fields should not be modified. Otherwise, the device may operate incorrectly.

Table 7-5. CSR Bit Field Definitions - ID Registers

|             |        | <b>-</b>                                                                                   |          |                       |  |

|-------------|--------|--------------------------------------------------------------------------------------------|----------|-----------------------|--|

| ADDRESS     | BIT(S) | DESCRIPTION                                                                                | DEFAULT  | ACCESS <sup>(1)</sup> |  |

| 0x00 – 0x08 | 7:0    | Reserved<br>Addresses 0x08 - 0x00 = {0x01, 0x20, 0x20, 0x20, 0x44, 0x53, 0x49, 0x38, 0x35} | Reserved | RO                    |  |

(1) RO = Read Only; RW = Read/Write; RW1C = Read/Write '1' to Clear; WO = Write Only (reads return undetermined values)

Table 7-6. CSR Bit Field Definitions – Reset and Clock Registers

| ADDRESS | BIT(S) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DEFAULT | ACCESS (1) |