## UDP UPPI CARD USER'S GUIDE

## 1. Introduction

The UPPI-series evaluation cards are the engine of an MCU-based system, containing an MCU, optional radio, and minimal support circuitry.

These cards are designed around either a C8051F96xMCU or a Si102x/3x Wireless MCU. Only placement-critical items, such as bypass capacitors, crystals, dc-dc inductor, and RF front end circuitry are included. All other circuits reside on the hosting platform.

These cards are compatible with Silicon Labs Unified Development Platform MCU cards (UDP-F960-MCU series). They may also be used as prototyping modules, as they fit on a 2 mm-center prototyping board.

Figure 1. UPPI Cards with and without Radio

## 2. Description

The UPPI cards contain the MCU device and a minimal number of supporting components. Most of the core device pins are connected directly to headers, allowing signal mapping to be defined by the host board, typically a UDP MCU card. (See "2.3. Compatibility" for more information.)

Each board design varies in schematic and features. Refer to the board design files available from www.silabs.com for specifics.

### 2.1. Features

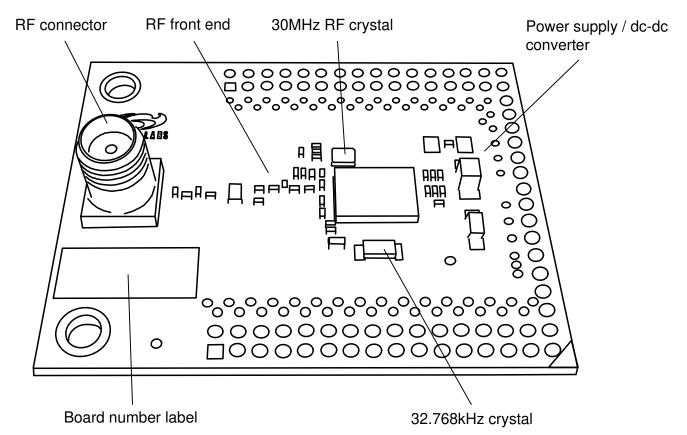

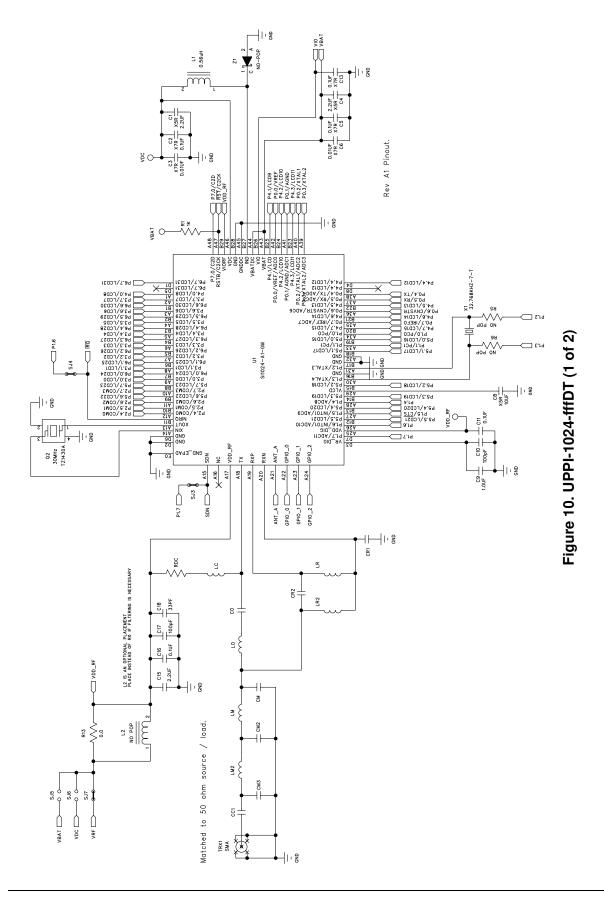

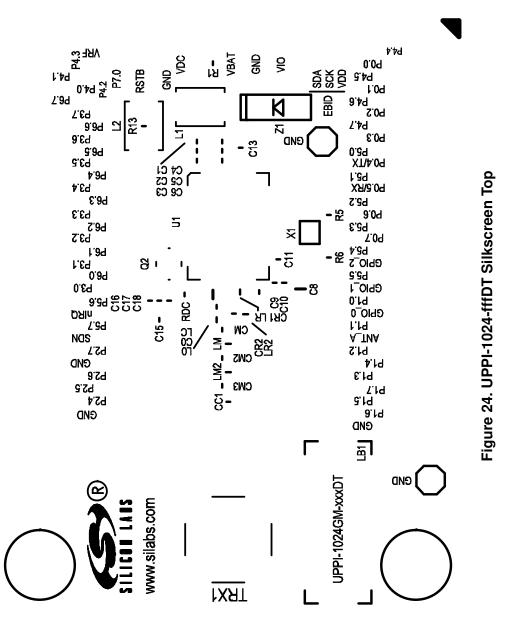

Figure 2. Top View: UPPI-10xx-fffTR and UPPI-10xx-fffDT Wireless MCU Boards

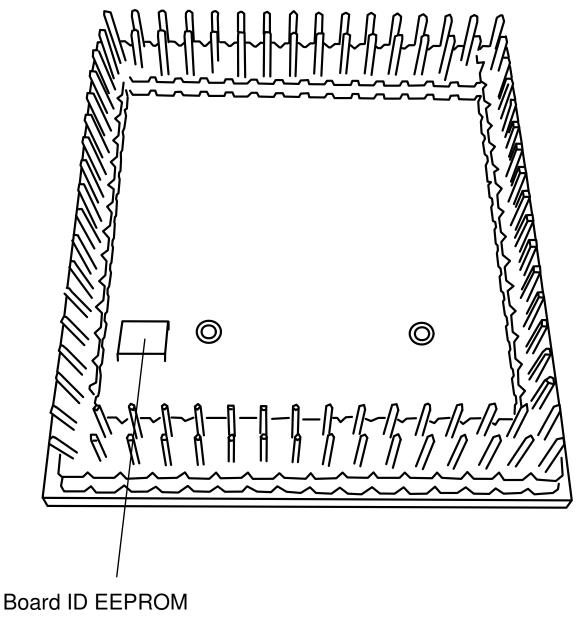

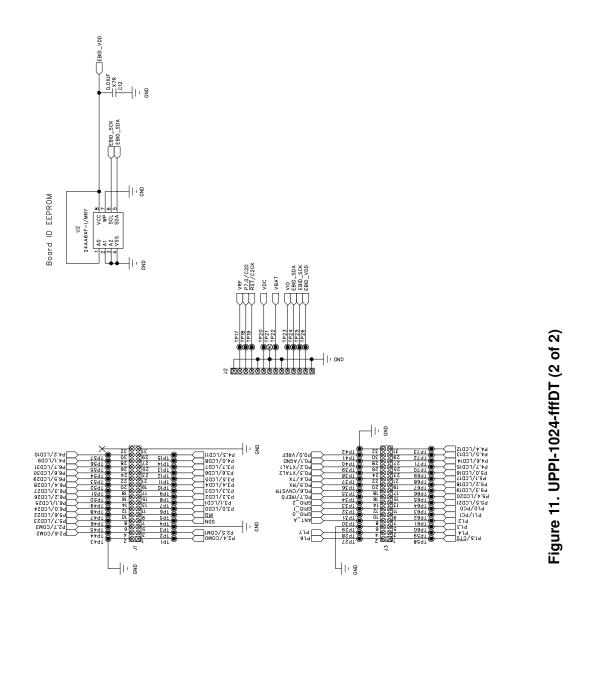

Board ID EEPROM

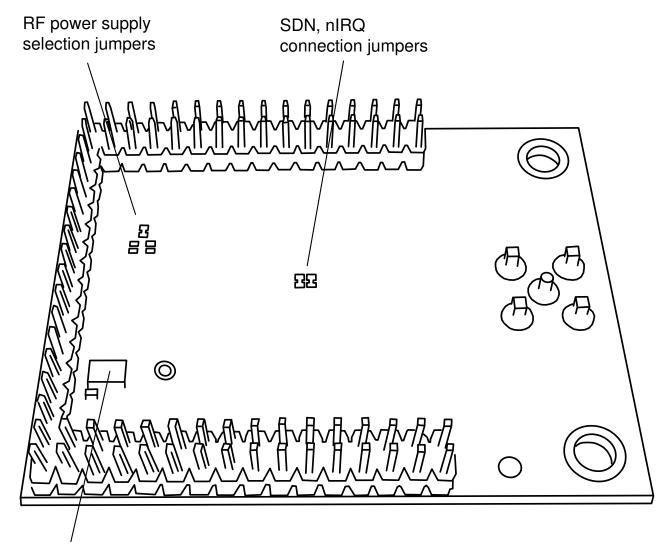

Figure 3. Bottom View: UPPI-10xx-fffTR and UPPI-10xx-fffDT Wireless MCU Boards

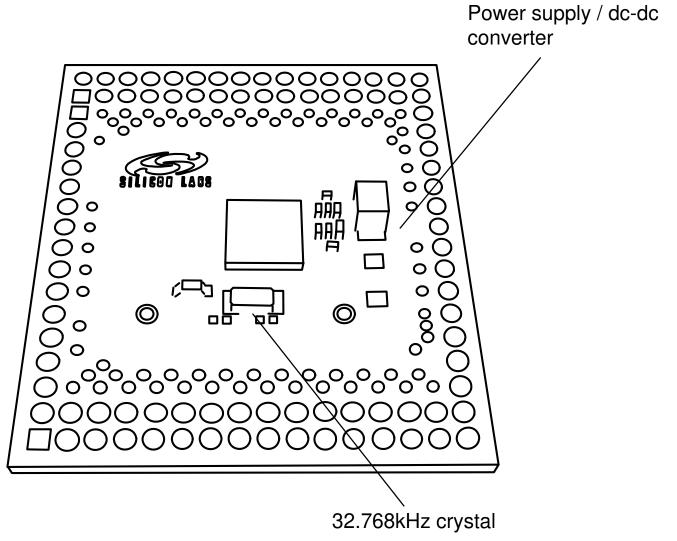

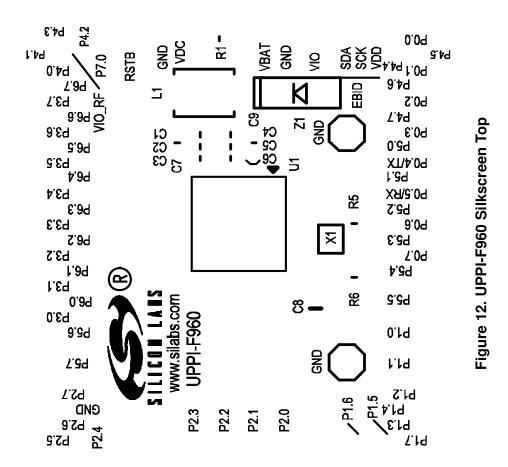

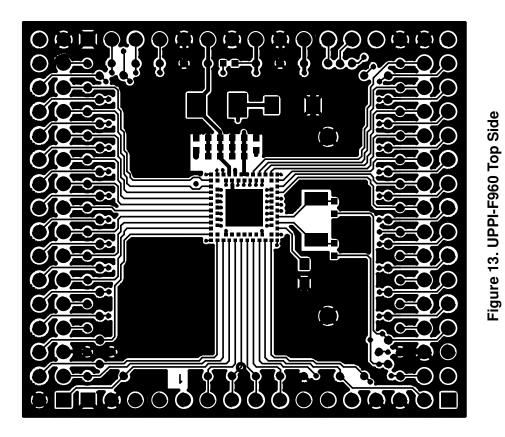

Figure 4. Top View: UPPI-F960

The UPPI cards contain the following functions:

#### Power Supply

The device's VBAT and VDC pins are connected to external pins. The dc-dc inductor, optional diode, and bypass capacitors are all included on the UPPI board as recommended in the data sheet.

The VIO connection is routed to a pin and must be connected on the host board.

The VIO\_RF pin (if applicable) is connected to the VRF net and routed to a pin. This net supplies both the radio section power and the VIO\_RF I/O voltage . The source is set on the host board, but may be optionally hard-wired via solder jumpers on the back of the board.

#### Crystal Oscillators

The MCU has a 32.768kHz crystal connected to the XTAL 3/4 pins. Devices with a radio have a 30 MHz crystal connected to the radio's XOUT/XIN pins. These nets are not connected to pins.

### RF Front End

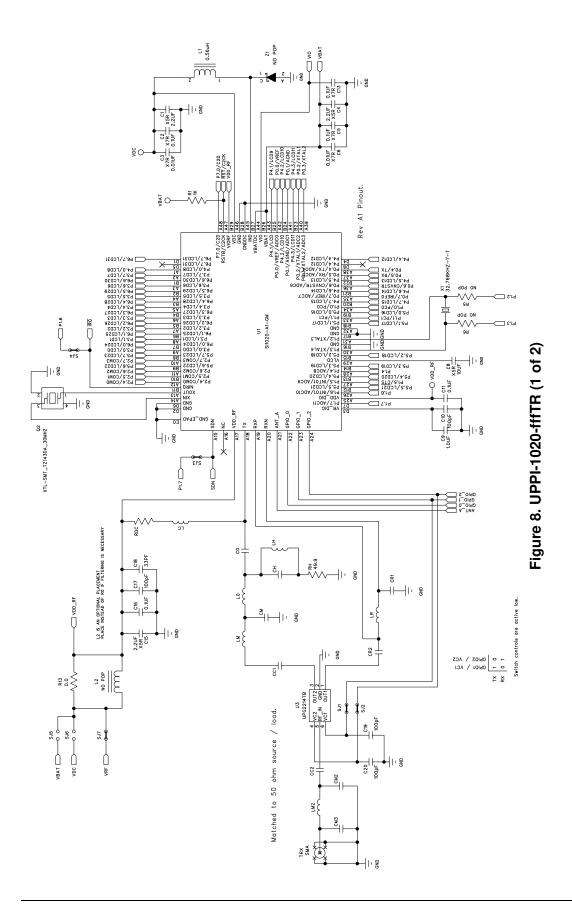

All RF matching circuitry is on-board. The transmitter and receiver pins are both matched to a 50  $\Omega$  SMA connector. This connector may be used with test equipment or an appropriate antenna.

The matching is based on either a T/R switch or a Direct Tie topology. The T/R switch topology uses a TX/RX switch device to share the RF port between TX and RX paths. T/R is used with high power (+20dBm) devices. The Direct Tie topology passively sums TX and RX paths and is suitable for low-power (+13dBm) devices.

Both matching topologies are discussed in detail in the following application notes:

- AN427: EZRadioPRO<sup>™</sup> Si433X & Si443X RX LNA Matching (+20dBm, T/R switch)

- AN435: Si4032/4432 PA Matching (+20 dBm, T/R switch)

- AN436: Si4030/4031/4430/4431 PA Matching (+13 dBm, Direct Tie)

#### RF GPIO Signals

The radio's GPIO\_0 - GPIO\_2 and ANT\_A nets are connected to pins. GPIO\_1 and GPIO\_2 are also connected on-board to the RF transmit/receive switch on high power ("TR" version) boards.

#### RF to MCU Interface Signals

The radio and MCU are interconnected within the Si102x/3x device. Two external signals, shutdown (SDN) and the interrupt (nIRQ) are connected to MCU port pins on the board. These signals may be disconnected by cutting jumpers on the back of the board.

### Port Pins

Most port pins are connected directly to the module's pins. Exceptions include

- Pins dedicated to the on-board radio interface

- P1.2 / P1.3, as these pins are used for the 32.768kHz crystal. These may be connected by adding 0-ohm resistors.

#### Programming/Debugging

C2CK/RSTB and C2D are connected to the module header. C2CK/RSTB has an on-board pullup resistor to VBAT.

#### Unified Development Platform Support

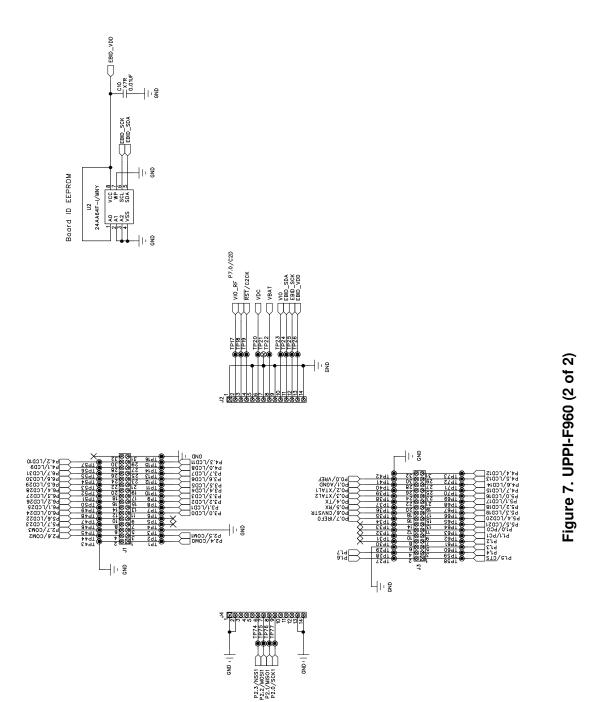

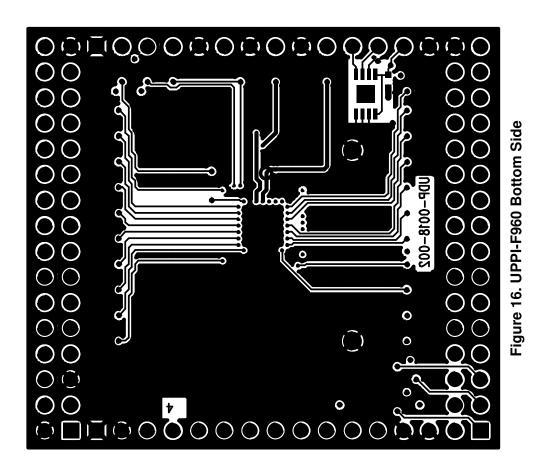

An EEPROM is included on the back side of the board to identify board information to the UDP system. This EEPROM is electrically isolated from the rest of the board except for a common ground.

The UPPI boards are based on 2mm-center headers. The footprint fits any C8051F96x- or Si102x/3x compatible Unified Development Platform MCU card. The UPPI boards may also be used for prototyping, using a 2mm-center perforated prototyping board.

The UPPI boards should be fastened to the base board using two 4-40 screws and 6.5mm standoffs to resist twisting moments from the antenna or RF cabling.

## 2.2. Ordering Information

A variety of UPPI boards are available, each tailored to a specific RF frequency band, transmitter power, and RF front end configuration. Refer to www.silabs.com for specific ordering information.

|                 | Device    | Description                                                      | Frequency | Tx Power<br>(Max) | Rf Front End |

|-----------------|-----------|------------------------------------------------------------------|-----------|-------------------|--------------|

| MCU Only        |           |                                                                  |           |                   |              |

| UPPI-F960       | C8051F960 | 'F960 microcontroller only                                       | _         | _                 | _            |

| Wireless MCU    |           |                                                                  |           |                   |              |

| UPPI-1020-fffTR | Si1020    | Si1020 Wireless MCU<br>with T/R switch (+20 dBm)                 | fff MHz   | +20 dBm max       | T/R switch   |

| UPPI-1024-fffDT | Si1024    | Si1023 Wireless MCU<br>with Direct Tie RF front end<br>(+13 dBm) | fff MHz   | +13 dBm max       | Direct Tie   |

### Table 1. Ordering Information

## 2.3. Compatibility

These boards are compatible with the following UDP MCU cards:

- UDP F960 MCU card with Multiplexed LCD (UPMP-F960-MLCD)

- UDP F960 MCU card with EMIF (UPMP-F960-EMIF)

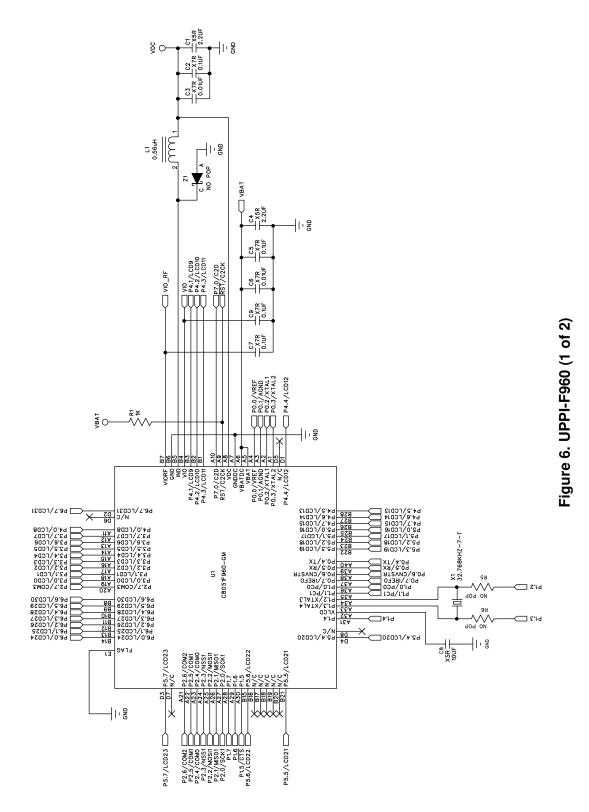

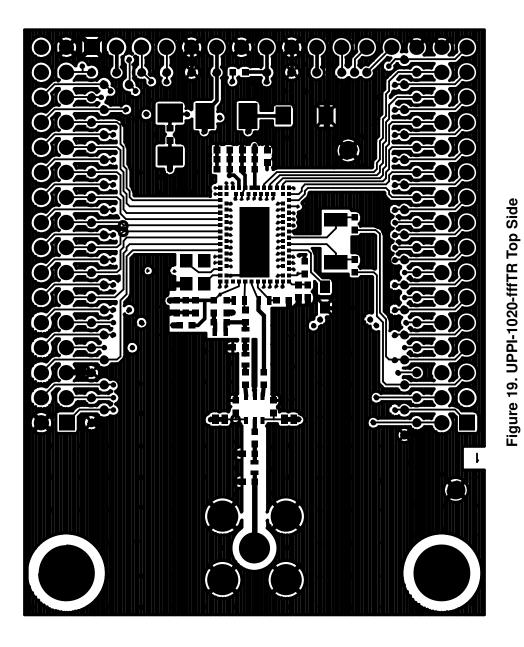

### 2.4. Schematics

These schematics show circuit topologies of the various cards. Refer to the latest schematics, available from www.silabs.com, for actual values.

© TP78

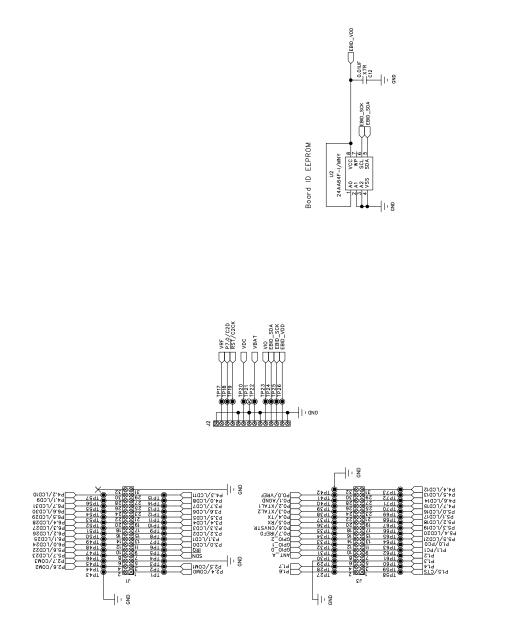

Figure 9. UPPI-1020-fffTR (2 of 2)

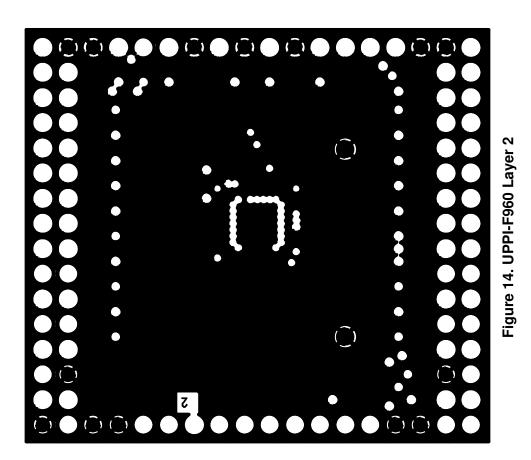

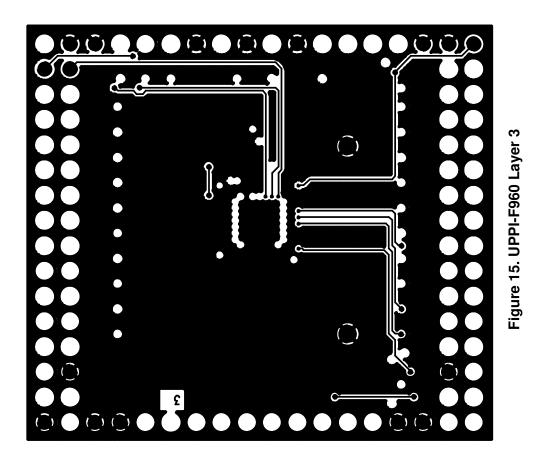

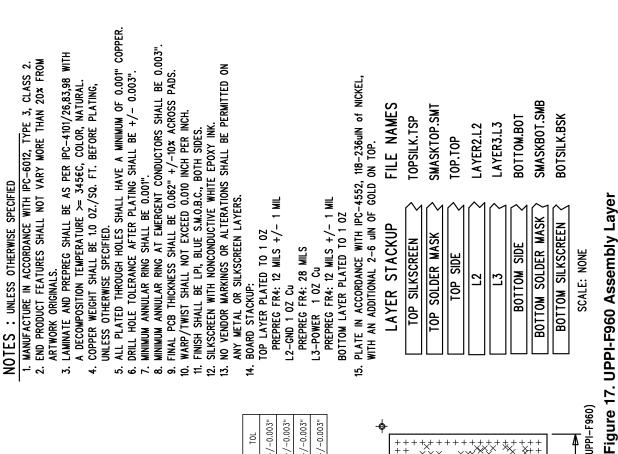

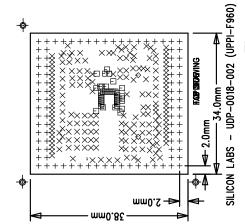

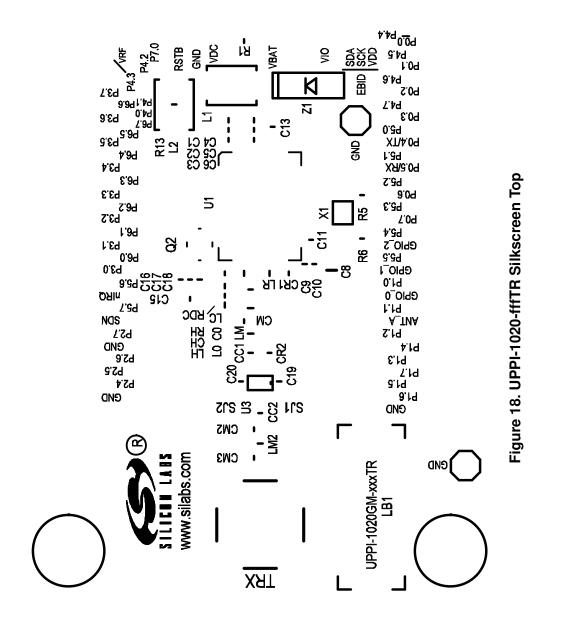

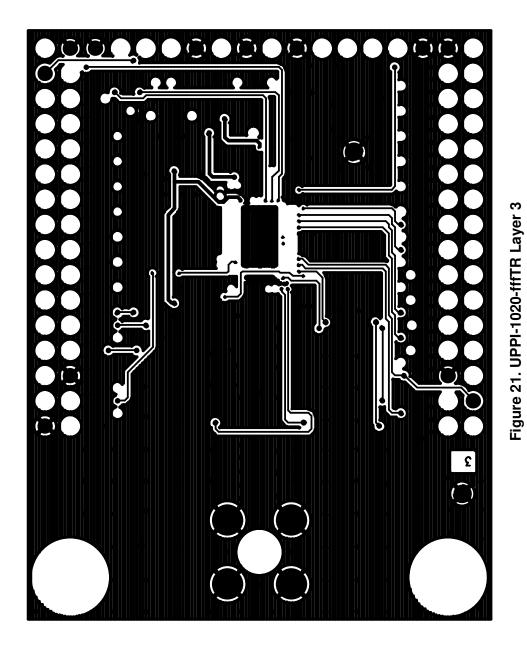

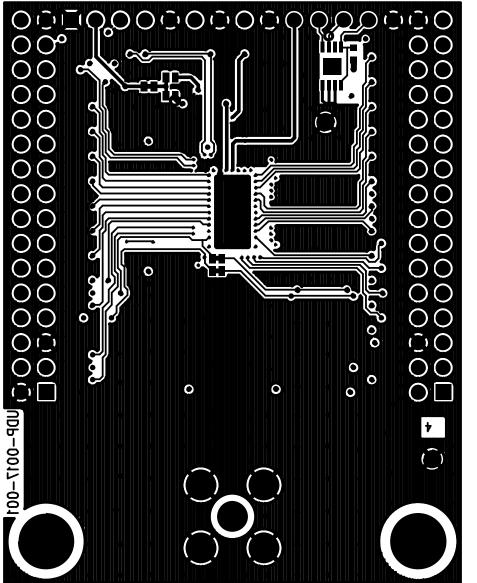

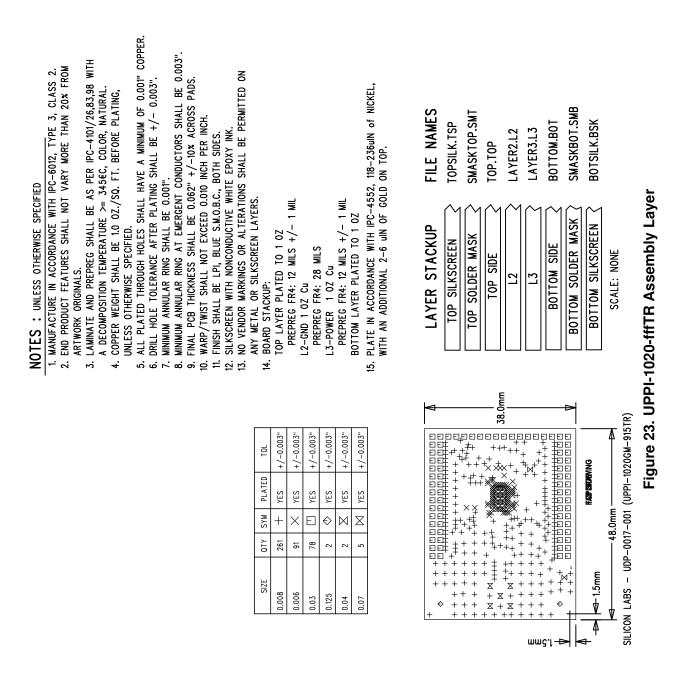

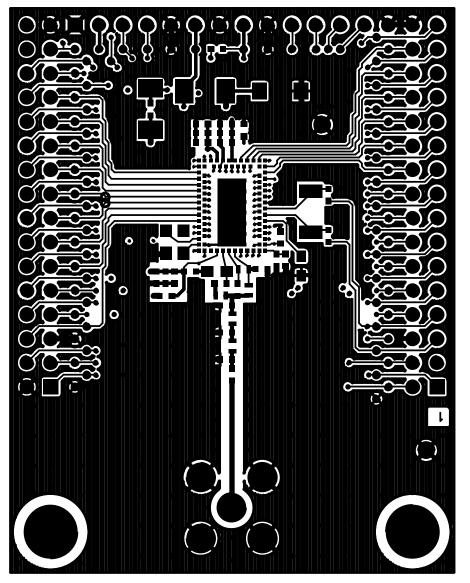

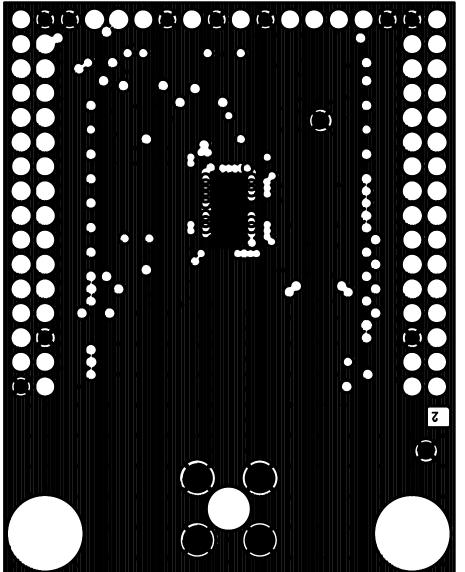

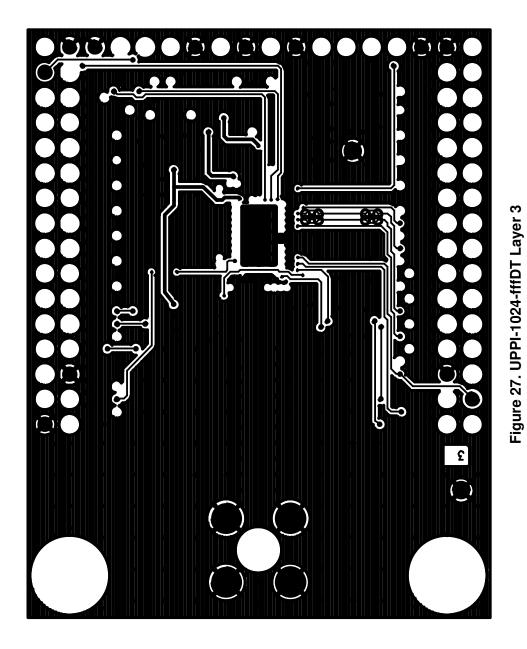

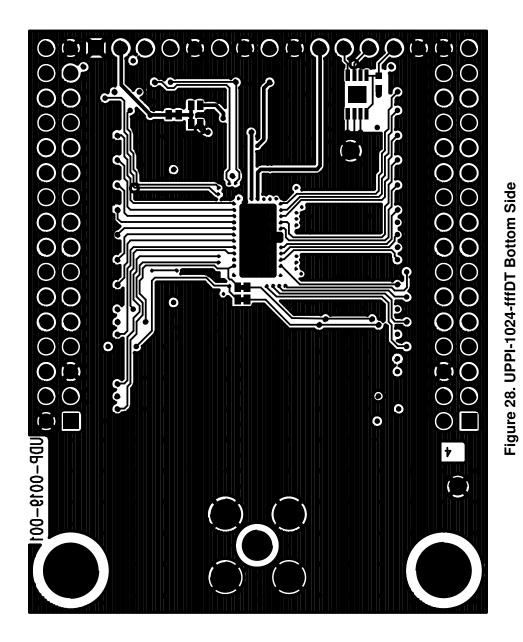

### 2.5. PCB Layouts

| SIZE | QTΥ | SΥM            | PLATED | 101      |

|------|-----|----------------|--------|----------|

| 30   | 92  | +              | YES    | 200.0-/+ |

| 8    | 194 | $\times$       | YES    | 200'0-/+ |

| 6    | 39  | Ð              | YES    | 200'0-/+ |

| 40   | 2   | $\diamondsuit$ | YES    | 200.0-/+ |

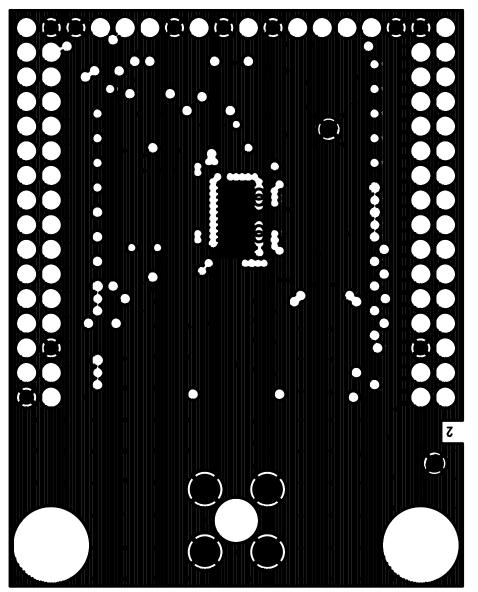

Figure 20. UPPI-1020-ftfTR Layer 2

Figure 22. UPPI-1020-fffTR Bottom Side

Figure 25. UPPI-1024-fffDT Top Side

SILICON LABS

աաց լ

NOTES : UNLESS OTHERWISE SPECIFIED

31

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products not be used in weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

## http://www.silabs.com