# 0.2 GHz to 8 GHz, GaAs, HBT MMIC, Divide by 8 Prescaler

### **Enhanced Product**

## HMC434-EP

### FEATURES

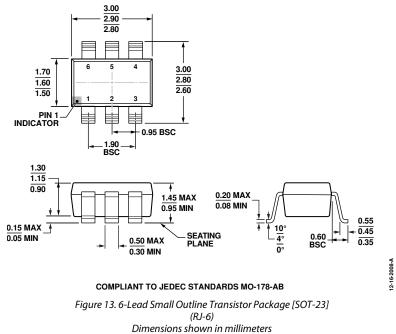

Ultralow SSB phase noise: –150 dBc/Hz typical Single-ended input/outputs RF output power: –2 dBm typical Single-supply operation: 3 V Ultrasmall, surface-mount, 2.90 mm × 2.80 mm, 6-lead SOT-23 package

### **ENHANCED PRODUCT FEATURES**

Supports defense and aerospace applications (AQEC standard) Extended industrial temperature range: -55°C to +105°C Controlled manufacturing baseline 1 assembly/test site 1 fabrication site Product change notification Qualification data available upon request

#### **APPLICATIONS**

DC to C band PLL prescalers Very small aperture terminal (VSAT) radios Unlicensed national information infrastructure (UNII) and point to point radios IEEE 802.11a and high performance radio local area network (HiperLAN) WLAN Fiber optics Cellular/3G infrastructure

### **GENERAL DESCRIPTION**

The HMC434-EP is a low noise, static, divide by 8 prescaler monolithic microwave integrated circuit (MMIC) utilizing indium gallium phosphide/gallium arsenide (InGaP/GaAs) heterojunction bipolar transistor (HBT) technology in an ultrasmall surface-mount 6-lead SOT-23 package.

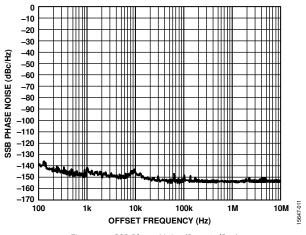

The HMC434-EP operates from near dc (square wave) or 0.2 GHz (sine wave) to 8 GHz input frequency with a single 3 V dc supply.

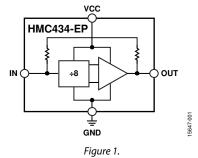

FUNCTIONAL BLOCK DIAGRAM

The HMC434-EP features single-ended inputs and outputs for reduced component count and cost. The low additive single sideband (SSB) phase noise of -150 dBc/Hz at 100 kHz offset helps the user maintain optimal system noise performance.

Additional application and technical information can be found in the HMC434 data sheet.

Rev. B

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2017–2019 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

### TABLE OF CONTENTS

| Features                  | 1 |

|---------------------------|---|

| Enhanced Product Features | 1 |

| Applications              | 1 |

| Functional Block Diagram  | 1 |

| General Description       | 1 |

| Revision History          | 2 |

| Specifications            | 3 |

| Absolute Maximum Ratings  | 4 |

### **REVISION HISTORY**

| 3/2019—Rev. A to Rev. B |   |

|-------------------------|---|

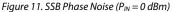

| Changes to Figure 11    | 6 |

| 8/2017—Rev. 0 to Rev. A                                       |   |

|---------------------------------------------------------------|---|

| Changes to Features Section and General Description Section 1 |   |

| Added Endnote 2 to Table 1                                    | 5 |

### 3/2017—Revision 0: Initial Version

| Thermal Resistance                          | 4 |

|---------------------------------------------|---|

| ESD Caution                                 | 4 |

| Pin Configuration and Function Descriptions | 5 |

| Interface Schematics                        | 5 |

| Typical Performance Characteristics         | 6 |

| Outline Dimensions                          | 7 |

| Ordering Guide                              | 7 |

### **SPECIFICATIONS**

$V_{CC}$  = 3 V,  $T_A$  = 25°C, 50  $\Omega$  system, unless otherwise noted. P<sub>IN</sub> is input power.

#### Table 1.

| Parameter                  | Min  | Тур  | Max  | Unit   | Test Conditions / Comments                                             |

|----------------------------|------|------|------|--------|------------------------------------------------------------------------|

| RADIO FREQUENCY (RF) INPUT |      |      |      |        |                                                                        |

| Frequency <sup>1, 2</sup>  | 0.2  |      | 8    | GHz    | Sine wave input                                                        |

| Power                      | -10  | 0    | +10  | dBm    | $f_{IN} = 1.0 \text{ GHz}$ to 3.0 GHz                                  |

|                            | 0    | 0    | 10   | dBm    | $f_{IN} = 3.0 \text{ GHz}$ to 8.0 GHz                                  |

| RF OUTPUT                  |      |      |      |        |                                                                        |

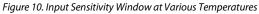

| SSB Phase Noise            |      | -150 |      | dBc/Hz | 100 kHz offset, $P_{IN} = 0 \text{ dBm}$ , $f_{IN} = 4.0 \text{ GHz}$  |

| Power                      | -5   | -2   |      | dBm    | $f_{IN} = 1.0 \text{ GHz}$ to 8.0 GHz                                  |

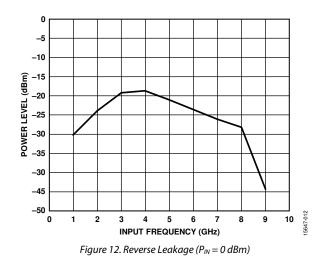

| REVERSE LEAKAGE            |      | -25  |      | dBm    | $P_{IN} = 0 \text{ dBm}, f_{IN} = 4.0 \text{ GHz}$ , output terminated |

| SUPPLY                     |      |      |      |        |                                                                        |

| Voltage (V <sub>cc</sub> ) | 2.85 | 3    | 3.15 | V      |                                                                        |

| Current (Icc)              |      | 62   | 83   | mA     |                                                                        |

<sup>1</sup> Below 200 MHz, a square wave input is required. <sup>2</sup> For stable operation without an input signal, refer to the AN-1463 Application Note, Frequency Divider Operation and Compensation with No Input Signal.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                         | Rating           |  |  |

|-----------------------------------|------------------|--|--|

| Supply Voltage (V <sub>CC</sub> ) | –0.3 V to +3.5 V |  |  |

| RF Input Power ( $V_{CC} = 3 V$ ) | 13 dBm           |  |  |

| Temperature                       |                  |  |  |

| Operating                         | -55°C to +105°C  |  |  |

| Storage                           | –65°C to +125°C  |  |  |

| Junction, T <sub>J</sub>          | 135°C            |  |  |

| Nominal ( $T_A = 105^{\circ}C$ )  | 119°C            |  |  |

| Reflow                            | 260°C            |  |  |

| ESD Sensitivity                   |                  |  |  |

| Human Body Model (HBM)            | Class 0          |  |  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

#### Table 3. Thermal Resistance

| Package Type | $\theta_{JA}{}^1$ | θ <sub>JC</sub> <sup>2</sup> | Unit |

|--------------|-------------------|------------------------------|------|

| RJ-6         | 359               | 70                           | °C/W |

<sup>1</sup> Simulated values per JEDEC JESD51-12 standards.

<sup>2</sup> Junction to GND package pin.

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### HMC434-EP

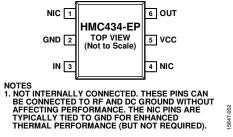

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. Pin Configuration

#### **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                             |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4    | NIC      | Not Internally Connected. These pins can be connected to RF and dc ground without affecting performance.<br>The NIC pins are typically tied to GND for enhanced thermal performance (but not required). |

| 2       | GND      | Ground. This pin must be connected to both RF and dc ground.                                                                                                                                            |

| 3       | IN       | RF Input. This pin must be dc blocked.                                                                                                                                                                  |

| 5       | VCC      | Supply Voltage (3 V).                                                                                                                                                                                   |

| 6       | OUT      | RF Output. This pin must be dc blocked.                                                                                                                                                                 |

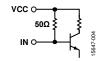

#### **INTERFACE SCHEMATICS**

Figure 3. GND Interface Schematic

Figure 4. IN Interface Schematic

Figure 5. OUT Interface Schematic

Figure 6. VCC Interface Schematic

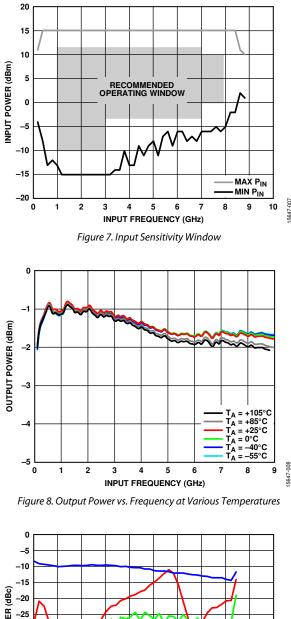

### **TYPICAL PERFORMANCE CHARACTERISTICS**

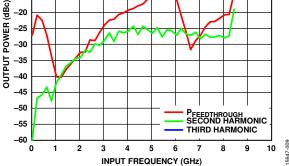

In Figure 9,  $P_{\text{FEEDTHROUGH}}$  is the power of the output spectrum at the input frequency.

Figure 9. Output Harmonic Content ( $P_{IN} = 0 dBm$ )

### **OUTLINE DIMENSIONS**

**ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                              | Package Option | Marking Code |

|--------------------|-------------------|--------------------------------------------------|----------------|--------------|

| HMC434SRJZ-EP-PT   | –55°C to +105°C   | 6-Lead Small Outline Transistor Package [SOT-23] | RJ-6           | 34P          |

| HMC434SRJZ-EP-R7   | –55°C to +105°C   | 6-Lead Small Outline Transistor Package [SOT-23] | RJ-6           | 34P          |

$^{1}$  Z = RoHs Compliant Part.

©2017–2019 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D15647-0-3/19(B)

www.analog.com

Rev. B | Page 7 of 7