### HSDL-3208-S21

Ultra Small Profile Package

IrDA® Data Compliant Low Power

115.2 kbit/s Infrared Transceiver

### Data Sheet

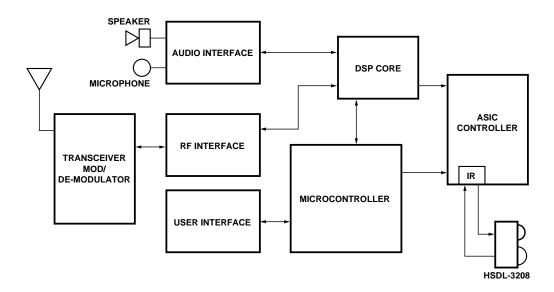

The HSDL-3208 is an ultra-small low cost infrared transceiver module that provides the interface between logic and infrared (IR) signals for through air, serial, half-duplex IR data link. The module is compliant to IrDA Physical Layer Specifications version 1.4 Low Power from 9.6 kbit/s to 115.2 kbit/s with extended link distance and it is IEC 825-Class 1 eye safe.

The HSDL-3208 can be shut down completely to achieve very low power consumption. In the shutdown mode, the PIN diode will be inactive and thus producing very little photocurrent even under very bright ambient light. Such features are ideal for battery operated handheld products.

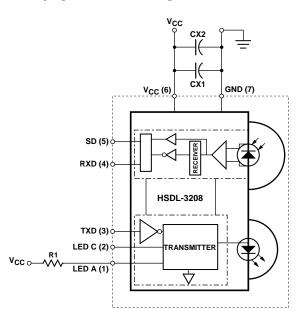

Figure 1. Functional block diagram of HSDL-3208.

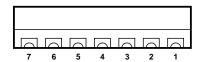

Figure 2. Rear view diagram with pinout.

### **Features**

- Fully compliant to IrDA 1.4 low power specification from 9.6 kbit/s to 115.2 kbit/s

- Miniature package

- Height: 1.60 mm

- Width: 7.00 mm

- Depth: 2.8 mm

- · Miniature package (with shield)

- Height: 1.80 mm

- Width: 7.4 mm

- Depth: 2.90 mm

- Guaranteed temperature performance, -25 to +70°C

- Critical parameters are guaranteed over temperature and supply voltage

- · Low power consumption

- Low shutdown current (1 nA typical)

- Complete shutdown of TXD, RXD, and PIN diode

- Withstands > 100 mVp-p power supply ripple typically

- · Excellent EMI performance without shield

- · Vcc supply 2.4 to 3.6 volts

- · LED stuck-high protection

- Designed to accommodate light loss with cosmetic windows

- · IEC 825-class 1 eye safe

### **Applications**

- IRFM

- M obile telecom

- Cellular phones

- Pagers

- Smart phones

- Data communication

- PDAs

- Portable printers

- · Digital imaging

- Digital cameras

- Photo-imaging printers

# Application Support Information

The Application Engineering group in Avago Technologies is available to assist you with the technical understanding associated with HSDL-3208 infrared transceiver module. You can contact them through your local Avago sales representatives for additional details.

### **Order Information**

| Part Number   | Packaging Type | Package    | Quantity |

|---------------|----------------|------------|----------|

| HSDL-3208-021 | Tape and Reel  | Front View | 2500     |

| HSDL-3208-S21 | Tape and Reel  | Front View | 2500     |

### **Marketing Information**

The unit is marked with yww on the back of the PCB. y=year ww=work week

### I/O Pins Configuration Table

| Pin | Symbol          | Description    | I/O Type           | Notes |  |

|-----|-----------------|----------------|--------------------|-------|--|

| 1   | LED A           | LED Anode      | Input              | 1     |  |

| 2   | LED C           | LED Cathode    |                    | 2     |  |

| 3   | TXD             | Transmit Data  | Input, Active High | 3     |  |

| 4   | RXD             | Receive Data   | Output, Active Low | 4     |  |

| 5   | SD/Mode         | Shutdown       | Input, Active High | 5     |  |

| 6   | V <sub>CC</sub> | Supply Voltage | Supply Voltage     | 6     |  |

| 7   | GND             | Ground         | Ground             | 7     |  |

### Notes:

- 1. This pin can be connected directly to  $V_{CC}$  (i.e. without series resistor) at less than 3 V.

- 2. Internally connected to the LED driver.

- 3. This pin is used to transmit serial data when SD pin is low. Do not float the pin. This pin has an internal 500 kΩ pulldown with a typical input capacitance of 2 pF.

- 4. This pin is capable of driving a standard CMOS or TTL load. No external pull-up or pull down resistor is required. It is in tri-state mode when the transceiver is in shutdown mode. This pin tristates with a weak  $500~\mathrm{k}\Omega$  pullup resistor.

- 5. The transceiver is in shutdown mode if this pin is high. Do not float the pin.

- 6. Regulated, 2.4 to 3.6 volts.

- 7. Connect to system ground.

### **Recommended Application Circuit Components**

| Component | Recommended Value                                                   | Notes |

|-----------|---------------------------------------------------------------------|-------|

| R1        | 30 $\Omega$ $\pm$ 5%, 0.25 Watt for 2.4 <= V <sub>CC</sub> <= 3.6 V |       |

| CX1       | 0.47 μF± 20%, X7R Ceramic                                           | 8     |

| CX2       | 6.8 μF±20%, Tantalum                                                | 9     |

#### Notes:

- 8. CX1 must be placed within 0.7 cm of the HSDL-3208 to obtain optimum noise immunity.

- 9. In environments with noisy power supplies, supply rejection performance can be enhanced by including CX2, as shown in "Figure 1: HSDL-3208 Functional Block Diagram" in Page 1.

CAUTIONS: The BiCMOS inherent to the design of this component increases the component's susceptibility to damage from the electrostatic discharge (ESD). It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

### **Absolute Maximum Ratings**

For implementations where case to ambient thermal resistance is  $\leq 50^{\circ}$  C/W.

| Parameter                   | Symbol                | Min. | Max. | Units | Notes |

|-----------------------------|-----------------------|------|------|-------|-------|

| Storage Temperature         | T <sub>S</sub>        | -40  | +100 | °C    |       |

| Operating Temperature       | T <sub>A</sub>        | -25  | +85  | °C    |       |

| LED Anode Voltage           | V <sub>LEDA</sub>     | 0    | 6.5  | V     |       |

| Supply Voltage              | Vcc                   | 0    | 6.5  | V     |       |

| Input Voltage: TXD, SD/Mode | VI                    | 0    | 6.5  | V     |       |

| Output Voltage: RXD         | Vo                    | 0    | 6.5  | V     |       |

| DC LED Transmit Current     | I <sub>LED</sub> (DC) |      | 50   | mA    |       |

| Peak LED Transmit Current   | I <sub>LED</sub> (PK) |      | 250  | mA    | 10    |

#### Note:

10.  $\leq$  20% duty cycle,  $\leq$  90  $\mu$ s pulse width.

## **Recommended Operating Conditions**

| Parameter                               |            | Symbol            | Min.                | Тур. | Max.                | Units              | Conditions                                              |

|-----------------------------------------|------------|-------------------|---------------------|------|---------------------|--------------------|---------------------------------------------------------|

| Operating Temperat                      | ure        | T <sub>A</sub>    | -25                 |      | 70                  | °C                 |                                                         |

| Supply Voltage                          |            | Vcc               | 2.4                 |      | 3.6                 | V                  |                                                         |

| Logic Input Voltage                     | Logic High | V <sub>IH</sub>   | 2/3 V <sub>CC</sub> |      | V <sub>CC</sub>     | V                  |                                                         |

| for TXD, SD/Mode                        | Logic Low  | VIL               | 0                   |      | 1/3 V <sub>CC</sub> | V                  |                                                         |

| Receiver Input                          | Logic High | ElH               | 0.0081              |      | 500                 | mW/cm <sup>2</sup> | For in-band signals $\leq 115.2$ kbit/s <sup>[11]</sup> |

| Irradiance                              | Logic Low  | ElL               |                     |      | 1                   | μW/cm <sup>2</sup> | For in-band signals <sup>[11]</sup>                     |

| LED (Logic High) Cur<br>Pulse Amplitude | rrent      | I <sub>LEDA</sub> |                     | 50   |                     | mA                 |                                                         |

| Receiver Data Rate                      |            |                   | 9.6                 |      | 115.2               | kbit/s             |                                                         |

#### Note

11. An in-band optical signal is a pulse/sequence where the peak wavelength, λp, is defined as 850 ≤ λp ≤ 900 nm, and the pulse characteristics are compliant with the IrDA Serial Infrared Physical Layer Link Specification v1.4.

### **Electrical & Optical Specifications**

Specifications (Min. & Max. values) hold over the recommended operating conditions unless otherwise noted. Unspecified test conditions may be anywhere in their operating range. All typical values (Typ.) are at 25°C with  $V_{\rm CC}$  set to 3.0 V unless otherwise noted.

| Parameter                  |                    | Symbol                          | Min.                 | Тур.  | Max. | Units | Conditions                                                                                     |

|----------------------------|--------------------|---------------------------------|----------------------|-------|------|-------|------------------------------------------------------------------------------------------------|

| Receiver                   |                    |                                 |                      |       |      |       |                                                                                                |

| Viewing Angle              |                    | 2θ                              | 30                   |       |      | 0     |                                                                                                |

| Peak Sensitivity Wa        | velength           | λρ                              |                      | 880   |      | nm    |                                                                                                |

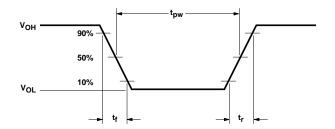

| RXD Output                 | Logic High         | V <sub>OH</sub>                 | V <sub>CC</sub> -0.2 |       | Vcc  | V     | $I_{OH}$ = -200 $\mu$ A, EI $\leq$ 1 $\mu$ W/cm <sup>2</sup>                                   |

| Voltage                    | Logic Low          | V <sub>OL</sub>                 | 0                    |       | 0.4  | V     | $I_{OL} = 200 \mu\text{A},  \text{El} \ge 8.1 \mu\text{W/cm}^2$                                |

| RXD Pulse Width (S         | IR)                | t <sub>PW</sub> (SIR)           | 1                    |       | 4.0  | μs    | $\theta \le 15^{\circ}$ , $C_L = 12 pF$                                                        |

| RXD Rise and Fall T        | imes               | t <sub>r</sub> , t <sub>f</sub> |                      | 50    |      | ns    | C <sub>L</sub> =12 pF                                                                          |

| Receiver Latency Ti        | me                 | t∟                              |                      | 70    |      | μs    |                                                                                                |

| Receiver Wake Up           | Time               | tw                              |                      | 90    |      | μs    |                                                                                                |

| Transmitter                |                    |                                 |                      |       |      |       |                                                                                                |

| Radiant Intensity          |                    | IEH                             | 4                    | 8     |      | mW/sr | $I_{LEDA} = 50 \text{ mA}, \ \theta \le 15^{\circ}, \ V_{TXD} \ge V_{IH}$<br>$T = 25^{\circ}C$ |

| Viewing Angle              |                    | 2θ                              | 30                   |       | 60   | 0     |                                                                                                |

| Peak Wavelength            |                    | λρ                              |                      | 875   |      | nm    |                                                                                                |

| Spectral Line Half V       | Vidth              | Δλ                              |                      | 35    |      | nm    |                                                                                                |

| TXD Input Current          | High               | lH                              |                      | 0.02  | 10   | μΑ    | $V_I \ge V_{IH}$                                                                               |

|                            | Low                | IL                              | -10                  | -0.02 | 10   | μΑ    | 0 ≤ V <sub>I</sub> _≤ V <sub>IL</sub>                                                          |

| LED Current                | On                 | I <sub>VLED</sub>               |                      | 50    |      | mA    | $V_{I}(TXD) \ge V_{IH}, V_{I}(SD) \le V_{IL}$                                                  |

|                            | Shutdown           | I <sub>VLED</sub>               |                      | 20    | 100  | nA    | $V_{I}$ (SD) $\geq V_{IH}$                                                                     |

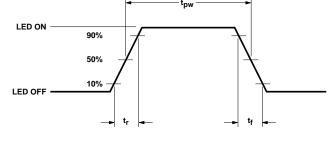

| Optical Pulse Width        | (SIR)              | t <sub>PW</sub> (SIR)           | 1.5                  | 1.6   | 1.8  | μs    | t <sub>PW</sub> (TXD) = 1.6 μs at 115.2 kbit/s                                                 |

| Maximum Optical P          | W                  | tpw(max.)                       |                      | 25    | 100  | μs    |                                                                                                |

| TXD Rise and Fall Ti       | ime (Optical)      | t <sub>r</sub> , t <sub>f</sub> |                      |       | 600  | ns    | tpw (TXD) = 1.6 μs                                                                             |

| LED Anode on State Voltage |                    | V <sub>ON</sub> (LEDA           | ۸)                   | 1.7   | 1.8  | V     | $I_{LEDA} = 50 \text{ mA}, \ V_I(TXD) \geq V_{IH}$                                             |

| Transceiver                |                    |                                 |                      |       |      |       |                                                                                                |

| Supply Current             | Shutdown           | I <sub>CC1</sub>                |                      | 0.001 | 1    | μΑ    | $V_{SD} \ge V_{CC}$ -0.5, $T_A = 25^{\circ}C$                                                  |

|                            | Idle               | I <sub>CC2</sub>                |                      | 100   | 200  | μΑ    | $V_{I}$ (TXD) $\leq V_{IL}$ , $EI = 0$                                                         |

|                            | Active<br>Receiver | I <sub>CC3</sub>                |                      | 0.8   | 3.1  | mA    | $V_{CC} = 3.6 \text{ V}, V_1(TXD) \le 1/3 V_{CC}^{[12]}$                                       |

### Notes:

<sup>12.</sup> Typical value is at EI =  $10 \text{ mW/cm}^2$ , maximum value is at EI =  $500 \text{ mW/cm}^2$ .

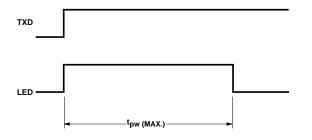

Figure 3. RXD output waveform.

Figure 4. LED optical waveform.

Figure 5. TXD "stuck on" protection waveform.

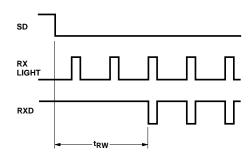

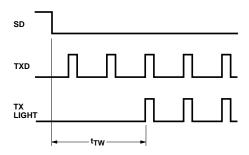

Figure 6. Receiver wakeup time waveform.

Figure 7. TXD wakeup time waveform.

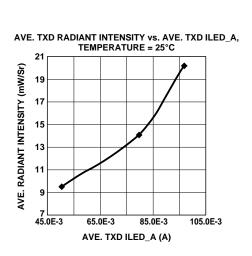

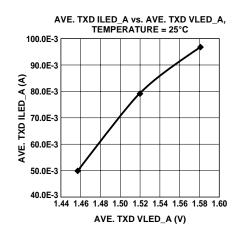

Figure 8. LOP vs. I<sub>LED</sub>.

Figure 9.  $\rm V_{\rm LED}$  vs.  $\rm I_{\rm LED}.$

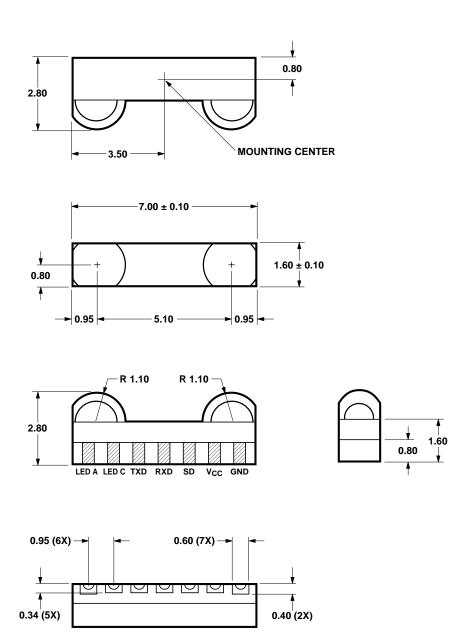

# HSDL-3208 (Unshielded) Package Dimensions

Figure 10. Package outline dimensions.

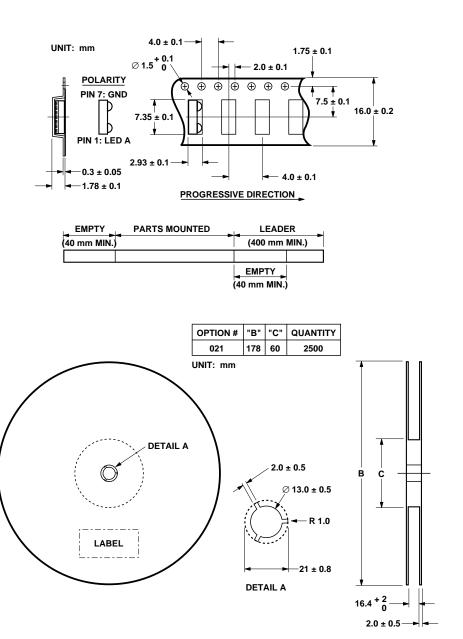

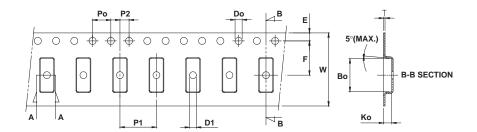

### HSDL-3208 (Unshielded) Tape and Reel Dimensions

Figure 11. Tape and reel dimensions.

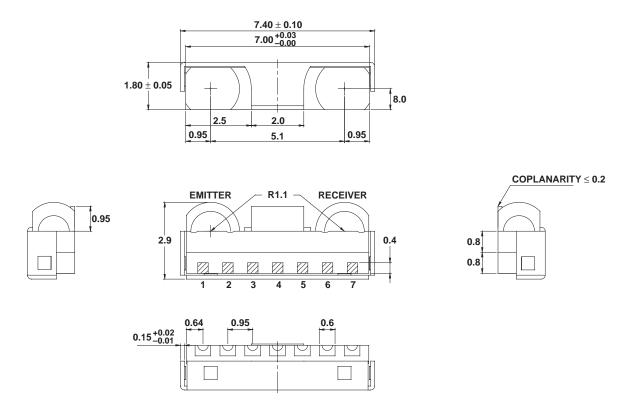

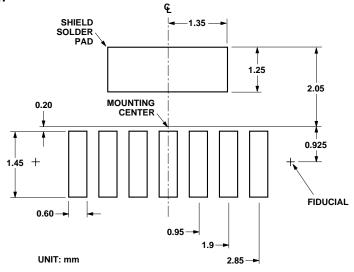

# **HSDL-3208 (Shielded) Package Dimensions**

1. Unless otherwise stated, dimension tolerance :  $^{\circ}\,\text{0.2}$  mm

Figure 12. Package outline dimensions.

### HSDL-3208 (Shielded) Tape Dimensions

|        |             |             |             |             |             |             | UNIT: mm    |

|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| SYMBOL | Ao          | Во          | Ко          | Ро          | P1          | P2          | Т           |

| SPEC   | 3.15 ± 0.10 | 7.75 ± 0.10 | 2.05 ± 0.10 | 4.0 ± 0.10  | 8.0 ± 0.10  | 2.0 ± 0.10  | 0.30 ± 0.10 |

| SYMBOL | E           | F           | Do          | D1          | w           | 10Po        |             |

| SPEC   | 1.75 ± 0.10 | 7.50 ± 0.10 | 1.55 ± 0.05 | 1.50 ± 0.10 | 16.0 ± 0.30 | 40.0 ± 0.20 |             |

#### NOTICE:

- 1. 10 SPROCKET HOLE PITCH CUMULATIVE TOLERANCE IS  $\pm 0.20$  mm.

- 2. CARRIER CAMBER SHALL BE NOT MORE THAN 1 mm PER 100 mm THROUGH A LENGTH OF 250 mm.

- 3. Ao & Bo MEASURED ON A PLACE 0.30 mm ABOVE THE BOTTOM OF THE POCKET.

- 4. K0 MEASURED FROM A PLACE ON THE INSIDE BOTTOM OF THE POCKET TO TOP SURFACE OF CARRIER.

- 5. POCKET POSITION RELATIVE TO SPROCKET HOLE MEASURED AS TRUE POSITION OF POCKET, NOT POCKET HOLE.

Figure 13. Tape dimensions.

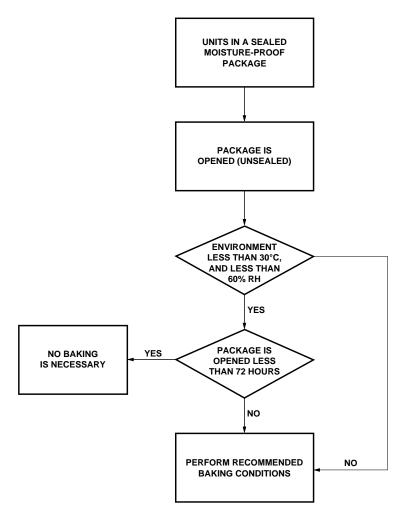

### **Moisture Proof Packaging**

All HSDL-3208 options are shipped in moisture proof package. Once opened, moisture absorption begins.

This part is compliant to JEDEC Level 4.

Figure 14. Baking conditions chart.

### **Baking Conditions**

If the parts are not stored in dry conditions, they must be baked before reflow to prevent damage to the parts.

| Package  | Temp. | Time       |

|----------|-------|------------|

| In reels | 60°C  | ≥ 48 hours |

| In bulk  | 100°C | ≥ 4 hours  |

|          | 125°C | ≥ 2 hours  |

|          | 150°C | ≥ 1 hour   |

Baking should only be done once.

# Recommended Storage Conditions

| Storage<br>Temperature | 10°C to 30°C |

|------------------------|--------------|

| Relative<br>Humidity   | below 60% RH |

# Time from Unsealing to Soldering

After removal from the bag, the parts should be soldered within three days if stored at the recommended storage conditions. If times longer than 72 hours are needed, the parts must be stored in a dry box.

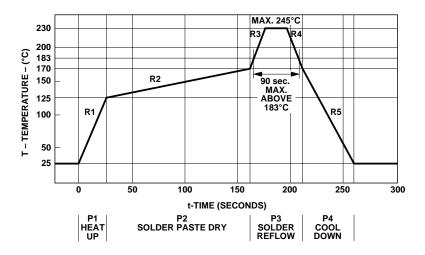

#### **Recommended Reflow Profile**

Figure 15. Reflow graph.

| Process Zone     | Symbol | ΔΤ                                        | Maximum $\Delta T/\Delta time$ |

|------------------|--------|-------------------------------------------|--------------------------------|

| Heat Up          | P1, R1 | 25°C to 160°C                             | 4°C/s                          |

| Solder Paste Dry | P2, R2 | 160°C to 200°C                            | 0.5°C/s                        |

| Solder Reflow    | P3, R3 | 200°C to 255°C (260°C at 10 seconds max.) | 4°C/s                          |

|                  | P3, R4 | 255°C to 200°C                            | -6°C/s                         |

| Cool Down        | P4, R5 | 200°C to 25°C                             | −6°C/s                         |

The reflow profile is a straight-line representation of a nominal temperature profile for a convective reflow solder process. The temperature profile is divided into four process zones, each with different  $\Delta T/\Delta time$  temperature change rates. The  $\Delta T/\Delta time$  rates are detailed in the above table. The temperatures are measured at the component to printed circuit board connections.

In process zone P1, the PC board and HSDL-3208 castellation pins are heated to a temperature of 160°C to activate the flux in the solder paste. The temperature ramp up rate, R1, is limited to 4°C per second to allow for even heating of both the PC board and HSDL-3208 castellations.

Process zone P2 should be of sufficient time duration (60 to 120 seconds) to dry the solder paste. The temperature is raised to a level just below the liquidus point of the solder, usually 200°C (392°F).

Process zone P3 is the solder reflow zone. In zone P3, the temperature is quickly raised above the liquidus point of solder to 255°C (491°F) for optimum results. The dwell time above the liquidus point of solder should be between 20 and 60 seconds. It usually takes about 20 seconds to assure proper coalescing of the solder balls into liquid solder and the formation of good solder connections. Beyond a dwell time of 60 seconds, the intermetallic growth within the solder

connections becomes excessive, resulting in the formation of weak and unreliable connections. The temperature is then rapidly reduced to a point below the solidus temperature of the solder, usually 200°C (392°F), to allow the solder within the connections to freeze solid.

Process zone P4 is the cool down after solder freeze. The cool down rate, R5, from the liquidus point of the solder to 25°C (77°F) should not exceed 6°C per second maximum. This limitation is necessary to allow the PC board and HSDL-3208 castellations to change dimensions evenly, putting minimal stresses on the HSDL-3208 transceiver.

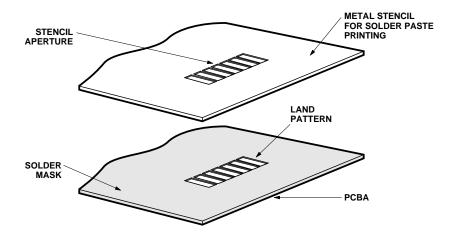

# Appendix A: SMT Assembly Application Note HSDL-3208 (Unshielded)

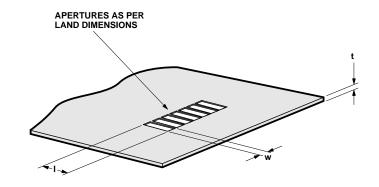

## 1.0 Solder Pad, Mask and Metal Stencil Aperture

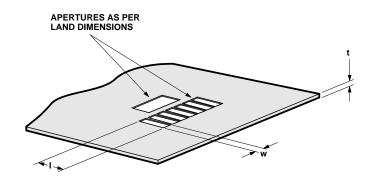

Figure 16. Stencil and PCBA.

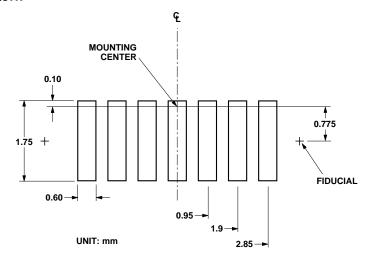

# 1.1 Recommended Land Pattern

Figure 17. Stencil and PCBA.

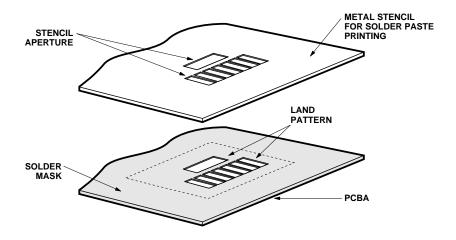

# 1.2 Recommended Metal Solder Stencil Aperture

It is recommended that only a 0.152 mm (0.006 inches) or a 0.127 mm (0.005 inches) thick stencil be used for solder paste printing. This is to ensure adequate printed solder paste volume and no shorting. See the table below the drawing for combinations of metal stencil aperture and metal stencil thickness that should be used.

Aperture opening for shield pad is  $2.7~\mathrm{mm}~\mathrm{x}~1.25~\mathrm{mm}$  as per land pattern.

Figure 18. Solder stencil aperture.

|                           | Aperture size(mm) |                 |  |

|---------------------------|-------------------|-----------------|--|

| Stencil thickness, t (mm) | length, I         | width, w        |  |

| 0.152 mm                  | $2.60 \pm 0.05$   | $0.55 \pm 0.05$ |  |

| 0.127 mm                  | $3.00 \pm 0.05$   | $0.55 \pm 0.05$ |  |

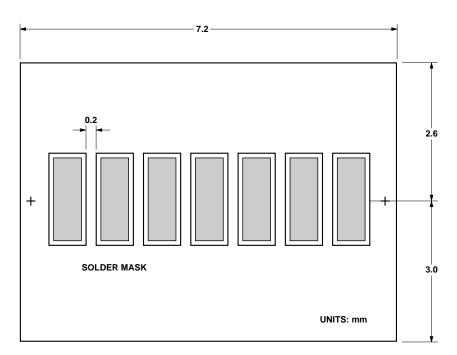

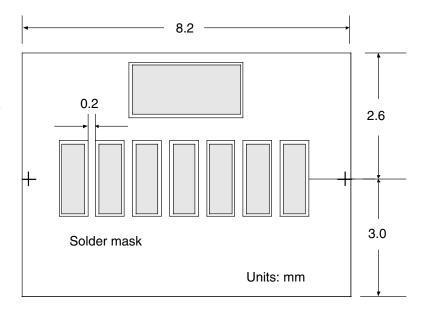

# 1.3 Adjacent Land Keepout and Solder Mask Areas

Adjacent land keep-out is the maximum space occupied by the unit relative to the land pattern. There should be no other SMD components within this area.

The minimum solder resist strip width required to avoid solder bridging adjacent pads is 0.2 mm. It is recommended that two fiducial crosses be placed at mid-length of the pads for unit alignment.

Note: Wet/Liquid Photo-Imageable solder resist/mask is recommended.

Figure 19. Adjacent land keepout and solder mask areas.

# Appendix A: SMT Assembly Application Note HSDL-3208 (Shielded)

## 2.0 Solder Pad, Mask and Metal Stencil Aperture

Figure 20. Stencil and PCBA.

# 2.1 Recommended Land Pattern

Figure 21. Land Pattern.

# 2.2 Recommended Metal Solder Stencil Aperture

It is recommended that only a 0.152 mm (0.006 inches) or a 0.127 mm (0.005 inches) thick stencil be used for solder paste printing. This is to ensure adequate printed solder paste volume and no shorting. See the table below the drawing for combinations of metal stencil aperture and metal stencil thickness that should be used.

Aperture opening for shield pad is 2.7 mm x 1.25 mm as per land pattern.

Figure 22. Solder stencil aperture.

|                           | Aperture size(  | mm)         |

|---------------------------|-----------------|-------------|

| Stencil thickness, t (mm) | length, I       | width, w    |

| 0.152 mm                  | $1.45 \pm 0.05$ | 0.55 ± 0.05 |

| 0.127 mm                  | 1.45 ± 0.05     | 0.55 ± 0.05 |

# 2.3 Adjacent Land Keepout and Solder Mask Areas

Adjacent land keep-out is the maximum space occupied by the unit relative to the land pattern. There should be no other SMD components within this area.

The minimum solder resist strip width required to avoid solder bridging adjacent pads is 0.2 mm. It is recommended that two fiducial crosses be placed at mid-length of the pads for unit alignment.

Note: Wet/Liquid Photo-Imageable solder resist/mask is recommended.

Figure 23. Adjacent land keepout and solder mask areas.

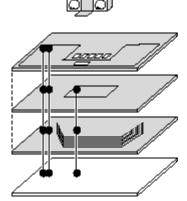

### Appendix B: **PCB Layout Suggestion**

The HSDL-3208 is a shieldless part and hence does not contain a shield trace, unlike the other transceivers. The following PCB layout guidelines should be followed to obtain a good PSRR and EM immunity, resulting in good electrical performance. Things to note:

- 1. The AGND pin should be connected to the ground plane.

- 2. C1 and C2 are optional supply filter capacitors; they may be left out if a clean power supply is used.

- 3. VLED can be connected to either unfiltered or unregulated power supply. If VLED and V<sub>CC</sub> share the same power supply and C1 is used, the connection should be before the current limiting resistor R2. In a noisy environment, including capacitor C2 can enhance supply rejection. C1 is generally a ceramic capacitor of low inductance providing a wide frequency response while C2 is a tantalum capacitor of big volume and fast frequency response. The use of a tantalum capacitor is more critical on the V<sub>LED</sub> line, which carries a high current.

- 4. Preferably a multi-layered board should be used to provide sufficient ground plane. Use the layer underneath and near the transceiver module as V<sub>CC</sub>, and sandwich that layer between

ground connected board layers. Refer to the diagram below for an example of a 4-layer board.

The area underneath the module at the second layer, and 3 cm in all directions around the module, is defined as the critical ground plane zone. The ground plane should be maximized in this zone. Refer to application note AN1114 or the Avago IrDA Data Link Design Guide for details. The layout below is based on a 2-layer PCB.

CONNECT THE METAL SHIELD AND MODULE GROUND PIN TO BOTTOM GROUND LAYER

LAYER 2

CRITICAL GROUND PLANE ZONE. DO NOT CONNECT DIRECTLY TO THE MODULE

KEEP DATA BUS AWAY FROM CRITICAL GROUND PLANE ZONE

BOTTOM LAYER (GND)

Top View

**Bottom View**

Figure 24. PCB layout suggestion.

# Appendix C: General Application Guide for the HSDL-3208 Infrared IrDA<sup>®</sup> Compliant 115.2 kb/s Transceiver

### Description

The HSDL-3208 is an ultra-small low-cost infrared transceiver module that provides the interface between logic and infrared (IR) signals for through air, serial, half-duplex IR data link. The device is designed to address the mobile computing market such as PDAs, as well as small embedded mobile products such as digital

cameras and cellular phones. It is fully compliant to IrDA 1.4 low power specification from 9.6 kb/s to 115.2 kb/s, and supports HP-SIR and TV Remote modes. The design of the HSDL-3208 also includes the following unique features:

- Low passive component count

- Shutdown mode for low power consumption requirement

#### Selection of Resistor R1

Resistor R1 should be selected to provide the appropriate peak pulse LED current over different ranges of  $V_{\rm CC}$  as shown in the table below.

# Interface to Recommended I/O Chips

The HSDL-3208's TXD data input is buffered to allow for CMOS drive levels. No peaking circuit or capacitor is required.

Data rate from 9.6 kb/s up to 115.2 kb/s is available at the RXD pin.

The diagram below shows how the IR port fits into the mobile phone platform and PDA platform.

| Recommended R1 | Vcc   | Intensity | Minimum Peak Pulse<br>LED Current |

|----------------|-------|-----------|-----------------------------------|

| 30 Ω           | 3.3 V | 9 mW/Sr   | 50 mA                             |

Figure 25: IR layout in mobile phone platform.

Figure 26: IR layout in PDA platform.

The link distance testing is done using typical HSDL-3208 units with National Semiconductor's PC87109 3V Super I/O Controller and SMC's FDC37C669 and FDC37N769 Super I/O controllers. An 115.2 kb/s datarate IR link distance of up to 40 cm has been demonstrated.

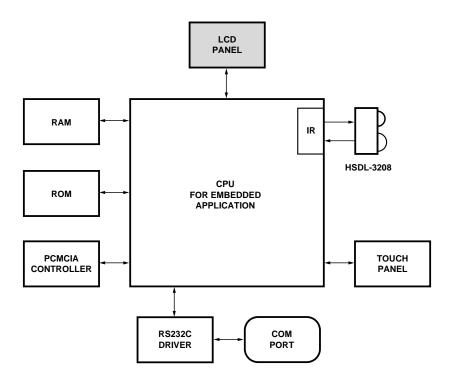

## Appendix D: Window Designs for HSDL-3208

# Optical port dimensions for HSDL-3208:

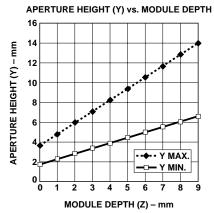

To ensure IrDA compliance, some constraints on the height and width of the window exist. The minimum dimensions ensure that the IrDA cone angles are met without vignetting. The maximum dimensions minimize the effects of stray light. The minimum size corresponds to a cone angle of 30° and the maximum size corresponds to a cone angle of 60°.

In the figure below, X is the width of the window, Y is the height of the window and Z is the distance from the HSDL-3208 to the back of the window. The distance from the center of the LED lens to the center of the photodiode lens, K, is 5.1 mm. The equations for computing the window dimensions are as follows:

$$X = K + 2*(Z + D)*tanA$$

$$Y = 2*(Z + D)*tanA$$

The above equations assume that the thickness of the window is negligible compared to the distance of the module from the back of the window (Z). If they are comparable, Z' replaces Z in the above equation. Z' is defined as

$$Z' = Z + t/n$$

where 't' is the thickness of the window and 'n' is the refractive index of the window material.

The depth of the LED image inside the HSDL-3208, D, is 3.17 mm. 'A' is the required half angle for viewing. For IrDA compliance, the minimum is 150 and the maximum is 300. Assuming the thickness of the window to be negligible, the equations result in the following tables and graphs:

Figure 27. Window design diagram.

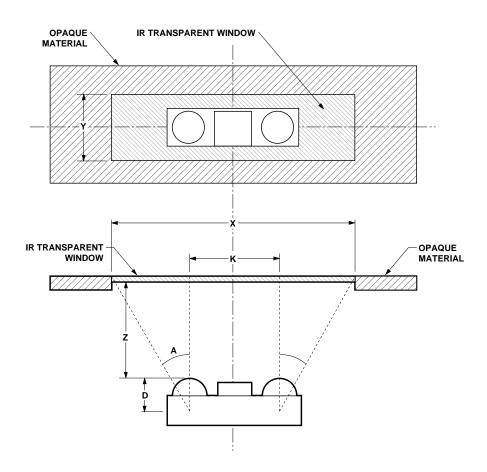

| Module Depth | Aperture | Aperture Width (x, mm) |       | Aperture Height (y, mm) |  |

|--------------|----------|------------------------|-------|-------------------------|--|

| (z) mm       | Max.     | Min.                   | Max.  | Min.                    |  |

| 0            | 8.76     | 6.80                   | 3.66  | 1.70                    |  |

| 1            | 9.92     | 7.33                   | 4.82  | 2.33                    |  |

| 2            | 11.07    | 7.87                   | 5.97  | 2.77                    |  |

| 3            | 12.22    | 8.41                   | 7.12  | 3.31                    |  |

| 4            | 13.38    | 8.94                   | 8.28  | 3.84                    |  |

| 5            | 14.53    | 9.48                   | 9.43  | 4.38                    |  |

| 6            | 15.69    | 10.01                  | 10.59 | 4.91                    |  |

| 7            | 16.84    | 10.55                  | 11.74 | 5.45                    |  |

| 8            | 18.00    | 11.09                  | 12.90 | 5.99                    |  |

| 9            | 19.15    | 11.62                  | 14.05 | 6.52                    |  |

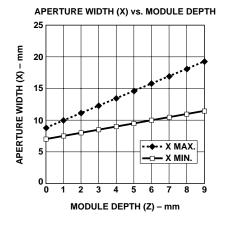

Figure 28. Aperture width (X) vs. module depth.

Figure 29. Aperture height (Y) vs. module depth.

#### Window Material

Almost any plastic material will work as a window material. Polycarbonate is recommended. The surface finish of the plastic should be smooth, without any texture. An IR filter dye may be used in the window to make it look black to the eye, but the total optical loss of the window should be 10% or less for best optical performance. Light loss should be measured at 875 nm.

The recommended plastic materials for use as a cosmetic window are available from General Electric Plastics.

### Shape of the Window

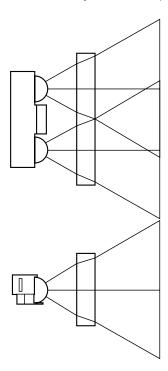

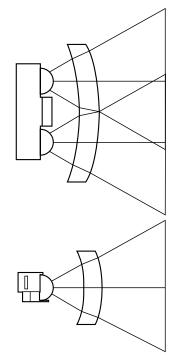

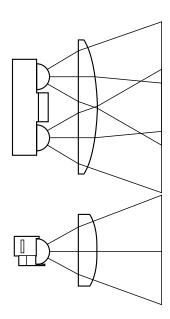

From an optics standpoint, the window should be flat. This ensures that the window will not alter either the radiation pattern of the LED, or the receive pattern of the photodiode.

If the window must be curved for mechanical or industrial design reasons, place the same curve on the back side of the window that has an identical radius as the front side. While this will not completely eliminate the lens effect of the front curved surface, it will significantly reduce the effects. The amount of change in the radiation pattern is dependent

upon the material chosen for the window, the radius of the front and back curves, and the distance from the back surface to the transceiver. Once these items are known, a lens design can be made which will eliminate the effect of the front surface curve.

The following drawings show the effects of a curved window on the radiation pattern. In all cases, the center thickness of the window is 1.5 mm, the window is made of polycarbonate plastic, and the distance from the transceiver to the back surface of the window is 3 mm.

#### **Recommended Plastic Materials**

| Material<br>Number | Light<br>Transmission | Haze | Refractive<br>Index |

|--------------------|-----------------------|------|---------------------|

| Lexan 141L         | 88%                   | 1%   | 1.586               |

| Lexan 920A         | 85%                   | 1%   | 1.586               |

| Lexan 940A         | 85%                   | 1%   | 1.586               |

Note: 920A and 940A are more flame retardant than 141L. Recommended Dye: Violet #21051 (IR transmissant above 625 nm).

Flat Window (First Choice)

Figure 30. Shape of windows.

Curved Front and Back (Second Choice)

Curved Front, Flat Back (Do Not Use)

For product information and a complete list of distributors, please go to our website: www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies Limited in the United States and other countries.

Data subject to change. Copyright © 2006 Avago Technologies Limited. All rights reserved. Cosoletes 5988-8481EN

TECHNOLOGY

TECHN