### **General Description**

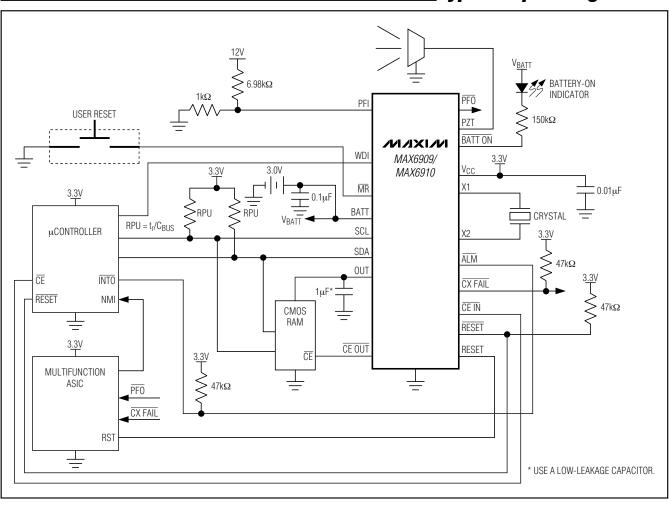

The MAX6909/MAX6910 are I<sup>2</sup>C-compatible real-time clocks (RTCs) with a microprocessor supervisor, optional trickle charger (MAX6910 only), backup power source, and NV RAM controller. The MAX6909/ MAX6910 provide alarm outputs to indicate a crystal failure, a switchover to battery power, and time and date indication. The NV RAM is 31 bytes of static RAM that are available for scratchpad storage. The MAX6909/ MAX6910 are controlled through a 2-wire serial bus.

The real-time clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The date is automatically adjusted for months with fewer than 31 days, including corrections for leap year up to the year 2100. The clock operates in either the 24-hour or 12-hour format with an AM/PM indicator. A time/date-programmable ALARM output completes the features list for the real-time clock section of the MAX6909/MAX6910. The alarm function can also be used in a polled mode by periodically reading the alarm out status bit in the minutes register. A crystal fail output, CX FAIL, indicates loss of accurate timekeeping due to crystal problems.

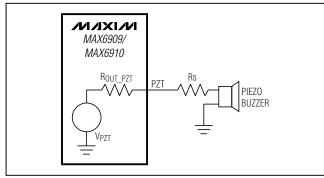

A built-in µP supervisor with an open-drain reset ensures the µP powers up in a known state. A reset threshold is available for 3V or 3.3V supplies. The piezo transducer output, PZT, is register selectable for one of four frequencies, can be turned on and off through a register bit, or selected to go on when the ALM, alarm output, goes active.

The MAX6909/MAX6910 are available in a 20-pin QSOP package and operate over the -40°C to +85°C temperature range.

### **Applications**

Point-of-Sale Equipment Programmable Logic Controller Handheld Instruments Medical Instrumentation

#### **Features**

- ♦ RTC Counts Seconds, Minutes, Hours, Date of the Month, Month, Day of the Week, and Year, with **Leap Year Compensation Valid Up to 2100**

- ♦ 31 Bytes of RAM for Scratchpad Data Storage

- ♦ Uses Standard 32.768kHz, 6pF Load, Watch Crystal

- ♦ Programmable Time/Date, Open-Drain ALARM **Output (Status Can also Be Polled)**

- ♦ Chip Enable Gating (Control of CE with Reset and Power Valid)

- ♦ OUT Pin for SRAM Power

- ♦ µP Reset Output

- Watchdog Input

- ♦ Manual Reset Input with Push-Button Switch **Debounce**

- ♦ Independent Power-Fail and Reset Comparators

- ♦ 400kHz 2-Wire Interface

- ♦ Single-Byte or Multiple-Byte (Burst Mode) Data Transfer for Read or Write of Clock Registers or RAM

- ♦ Bus Timeout to Prevent Lockup of Malfunctioning **Bus Interface**

- ♦ Dual Power-Supply Pins for Primary and Backup **Power**

- ♦ Programmable Trickle Charger (MAX6910)

- ♦ Uses Less than 1µA Timekeeping Current at 3.0V

- Operating Voltages of 3V and 3.3V

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX6909EO30 | -40°C to +85°C | 20 QSOP     |

| MAX6909EO33 | -40°C to +85°C | 20 QSOP     |

| MAX6910EO30 | -40°C to +85°C | 20 QSOP     |

| MAX6910EO33 | -40°C to +85°C | 20 QSOP     |

Pin Configuration/Selector Guide/Typical Operating Circuit appear at end of data sheet.

### **ABSOLUTE MAXIMUM RATINGS**

| All Voltages (with respect to G<br>BATT or V <sub>CC</sub> OUT, ALM, SCL, SDA, CX FAIL | 0.3V to +6.0V                                                                                                               | Output Current OUT Continuous All Other Outputs                        |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| All Other Pins                                                                         | 0.3V to +6.0V<br>0.3V to (V <sub>SUP</sub> + 0.3V)<br>v <sub>SUP</sub> is greater of V <sub>BATT</sub> or V <sub>CC</sub> ) | Continuous Power Dissi<br>20-Pin QSOP (derate<br>Operating Temperature |

| Input Current VCC                                                                      | 500mA                                                                                                                       | Junction Temperature<br>Storage Temperature Ra                         |

|                                                                                        | 100mA<br>20mA                                                                                                               | Lead Temperature (sold                                                 |

| Output Current                                        |                |

|-------------------------------------------------------|----------------|

| OUT Continuous                                        | 450mA          |

| All Other Outputs                                     | 20mA           |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| 20-Pin QSOP (derate 9.1mW/°C above +7                 | '0°C)727mW     |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = V_{CC(MIN)})$  to  $V_{CC(MAX)}$ ,  $T_A = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Notes 1, 2)

| PARAMETER                                         | SYMBOL            | CO                                                                    | ONDITIONS                                        | MIN                      | TYP                      | MAX  | UNITS |

|---------------------------------------------------|-------------------|-----------------------------------------------------------------------|--------------------------------------------------|--------------------------|--------------------------|------|-------|

| Operating Voltage Penge                           | Voc               | MAX69EO30 (Note 3)                                                    |                                                  | 2.7                      |                          | 3.3  | V     |

| Operating Voltage Range                           | Vcc               | MAX69EO33 (N                                                          | ote 3)                                           | 3.0                      |                          | 3.6  | V     |

| On exeting Veltage Denge DATT                     | \/                | MAX69EO30 (N                                                          | lote 4)                                          | 2.0                      |                          | 3.6  | V     |

| Operating Voltage Range BATT                      | V <sub>BATT</sub> | MAX69EO33 (N                                                          | lote 4)                                          | 2.0                      |                          | 3.6  | V     |

|                                                   |                   | 0                                                                     | VBATT = 2V, VCC = 0V                             |                          |                          | 0.75 |       |

| BATT Current (Note 5)                             | I <sub>BATT</sub> | Crystal fail-<br>circuit disabled                                     | V <sub>BATT</sub> = 3V, V <sub>CC</sub> = 0V     |                          |                          | 0.95 | μΑ    |

|                                                   |                   | Circuit disabled                                                      | V <sub>BATT</sub> = 3.6V, V <sub>CC</sub> = 0V   |                          |                          | 1.1  |       |

|                                                   |                   |                                                                       | V <sub>BATT</sub> = 2V, V <sub>CC</sub> = 0V     |                          |                          | 0.9  |       |

| Timekeeping Current (Note 5)                      | I <sub>BATT</sub> | Crystal fail-<br>circuit enabled                                      | VBATT = 3V, VCC = 0V                             |                          |                          | 4    | μΑ    |

|                                                   |                   | Circuit eriableu                                                      | $V_{BATT} = 3.6V, V_{CC} = 0V$                   |                          |                          | 9    |       |

| Active County Courset (Nets C)                    | ICCA              | PZT disabled,<br>crystal-disabled                                     | V <sub>C</sub> C = 3.3V, V <sub>BATT</sub> = 0V  |                          |                          | 0.14 | mA    |

| Active Supply Current (Note 6)                    |                   |                                                                       | V <sub>C</sub> C = 3.6V, V <sub>B</sub> ATT = 0V |                          |                          | 0.15 |       |

| Ohara allari Origina ant (NI-ta E)                | Iccs              | PZT disabled, crystal-disabled                                        | V <sub>C</sub> C = 3.3V, V <sub>BATT</sub> = 0V  |                          |                          | 7    | μΑ    |

| Standby Current (Note 5)                          |                   |                                                                       | V <sub>C</sub> C = 3.6V, V <sub>B</sub> ATT = 0V |                          |                          | 7    |       |

| Otana dia a Orania at (Nata 5)                    | Iccs              | Crystal fail-<br>circuit enabled                                      | V <sub>C</sub> C = 3.3V, V <sub>BATT</sub> = 0V  |                          |                          | 18   | μΑ    |

| Standby Current (Note 5)                          |                   |                                                                       | V <sub>C</sub> C = 3.6V, V <sub>B</sub> ATT = 0V |                          |                          | 25   |       |

| Trickle-Charge Diode Voltage<br>Drop (Two Diodes) |                   |                                                                       |                                                  |                          | 1.2                      |      | ٧     |

|                                                   | R1                |                                                                       |                                                  |                          | 1.7                      |      |       |

| Trickle Charge Resistors                          | R2                |                                                                       |                                                  |                          | 2.8                      |      | kΩ    |

| _                                                 | R3                |                                                                       |                                                  |                          | 5.0                      |      |       |

| OUT                                               |                   |                                                                       |                                                  |                          |                          |      |       |

| OUT in Battery-Backup Mode<br>(Note 4)            |                   | VBATT = 3.0V, VCC = 0V, IOUT = 20mA                                   |                                                  | V <sub>BATT</sub> - 0.15 | V <sub>BATT</sub> - 0.1  |      | M     |

|                                                   | Vout              | V <sub>BATT</sub> = 2.0V, V <sub>CC</sub> = 0V, I <sub>OUT</sub> 10mA |                                                  | V <sub>BATT</sub> - 0.1  | V <sub>BATT</sub> - 0.05 |      | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{CC(MIN)})$  to  $V_{CC(MAX)}$ ,  $T_A = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Notes 1, 2)

| PARAMETER                                                                      | SYMBOL           | CONDITIONS                                                                                                                                                                                                              | MIN                        | TYP                         | MAX                      | UNITS |

|--------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|--------------------------|-------|

| OLIT in Voc Mode (Note 4)                                                      | Volum            | V <sub>CC</sub> = 3.0V, V <sub>BATT</sub> = 0V, I <sub>OUT</sub> = 100mA                                                                                                                                                | V <sub>CC</sub> - 0.15     | V <sub>CC</sub> - 0.1       |                          | V     |

| OUT in V <sub>CC</sub> Mode (Note 4)                                           | Vout             | V <sub>CC</sub> = 2.7V, V <sub>BATT</sub> = 0V, I <sub>OUT</sub> = 50mA                                                                                                                                                 | V <sub>CC</sub> – 0.1      | V <sub>CC</sub> -<br>0.05   |                          | V     |

| V <sub>BATT</sub> to V <sub>CC</sub> Switchover<br>Threshold                   | V <sub>TRU</sub> | Power-up (V <sub>CC</sub> < V <sub>RST</sub> ) switch from V <sub>BATT</sub> to V <sub>CC</sub> (Note 7)                                                                                                                |                            | V <sub>BATT</sub><br>+ 0.05 |                          | V     |

| V <sub>CC</sub> to V <sub>BATT</sub> Switchover<br>Threshold                   | V <sub>TRD</sub> | Power-down ( $V_{CC} < V_{RST}$ ) switch from $V_{CC}$ to $V_{BATT}$ (Note 7)                                                                                                                                           |                            | V <sub>BATT</sub><br>- 0.05 |                          | V     |

| CEIN AND CEOUT                                                                 |                  |                                                                                                                                                                                                                         |                            |                             |                          |       |

| CE IN Leakage Current                                                          |                  | Disabled, V <sub>CC</sub> < V <sub>RST</sub> , V <sub>CE IN</sub> = V <sub>CC</sub> or GND                                                                                                                              | -1                         |                             | +1                       | μA    |

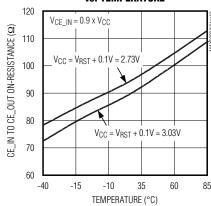

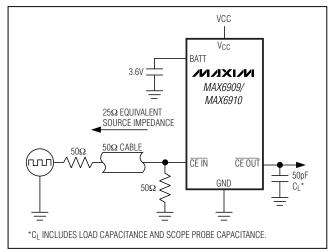

| CE IN to CE OUT Resistance                                                     |                  | $V_{CC} = V_{CC(min)}$ , $V_{IH} = 0.9V_{CC}$ , $V_{IL} = 0.1V_{CC}$                                                                                                                                                    |                            | 70                          | 140                      | Ω     |

| CE IN to CE OUT Propagation Delay                                              |                  | $50\Omega$ source impedance driver,<br>CLOAD = 10pF, VCC = VCC(MIN),<br>VIH = 0.9VCC, VIL = 0.1 VCC (Note 8),<br>measured from 50% point on $\overline{\text{CE IN}}$ to the<br>50% point on $\overline{\text{CE OUT}}$ |                            | 5                           | 15                       | ns    |

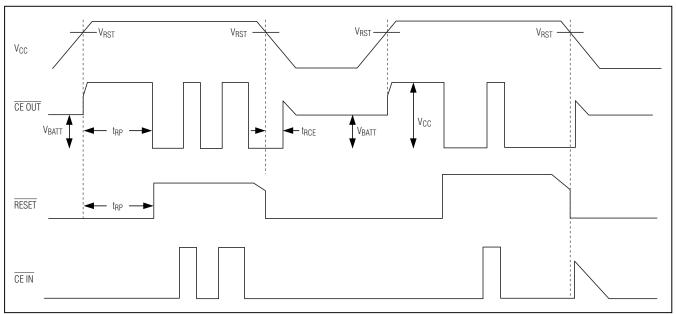

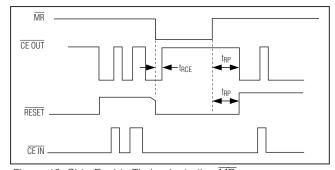

| RESET (or RESET) Active to CE OUT disabled and pulled to Vout Delay            | tRCE             | $\overline{\rm MR}$ low to high, V <sub>CC(MIN)</sub> < V <sub>CC</sub> < V <sub>CC(MAX)</sub>                                                                                                                          | 2                          | 10                          | 50                       | μs    |

| CE OUT Enabled and Connected to CE IN After V <sub>CC</sub> > V <sub>RST</sub> | t <sub>RP</sub>  |                                                                                                                                                                                                                         | 140                        | 200                         | 280                      | ms    |

| CE OUT High (RESET or RESET Active)                                            | V <sub>OH</sub>  | V <sub>CC</sub> = 0V, I <sub>OUT</sub> = -100μA, V <sub>BATT</sub> = 2V                                                                                                                                                 | 0.95 x<br>V <sub>OUT</sub> |                             |                          | V     |

| MANUAL RESET INPUT                                                             | •                |                                                                                                                                                                                                                         |                            |                             |                          |       |

| MR Input Threshold                                                             | VIL              |                                                                                                                                                                                                                         |                            |                             | 0.3 ×<br>V <sub>CC</sub> | V     |

| ININ III PUL III I ESTIOIU                                                     | VIH              |                                                                                                                                                                                                                         | 0.7 ×<br>VCC               |                             |                          | V     |

| MR Internal Pullup Resistance                                                  |                  |                                                                                                                                                                                                                         |                            | 50                          |                          | kΩ    |

| MR Minimum Pulse Width                                                         |                  |                                                                                                                                                                                                                         | 1                          |                             |                          | μs    |

| MR Glitch Immunity                                                             |                  | (Note 8)                                                                                                                                                                                                                |                            |                             | 50                       | ns    |

| MR to Reset Delay                                                              |                  | (Note 8)                                                                                                                                                                                                                |                            | 200                         | 350                      | ns    |

| POWER-FAIL INPUT AND POWE                                                      | R-FAIL OUTI      | PUT                                                                                                                                                                                                                     |                            |                             |                          |       |

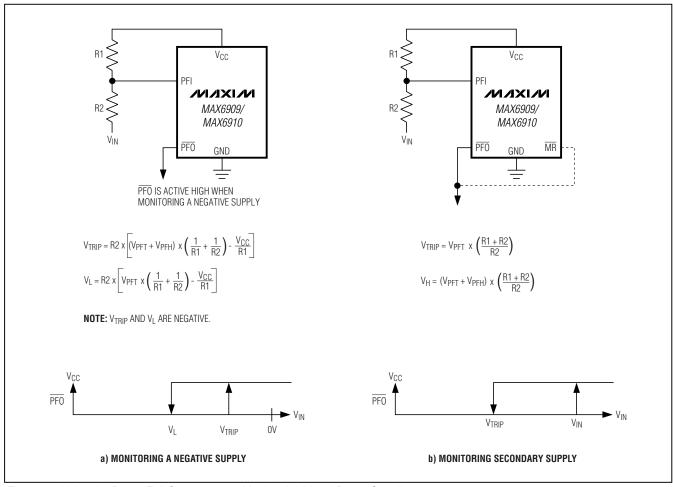

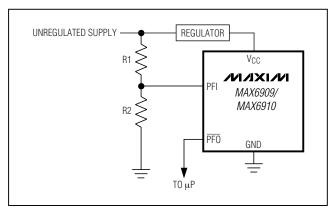

| PFI Input Threshold                                                            | VPFT             | VCC = VCC(MIN)                                                                                                                                                                                                          | 1.19                       | 1.27                        | 1.31                     | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{CC(MIN)})$  to  $V_{CC(MAX)}$ ,  $T_A = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Notes 1, 2)

| PARAMETER                                                            | SYMBOL            | C                                       | ONDITIONS                             | MIN                      | TYP  | MAX          | UNITS        |  |  |

|----------------------------------------------------------------------|-------------------|-----------------------------------------|---------------------------------------|--------------------------|------|--------------|--------------|--|--|

| PFI Input Current                                                    |                   |                                         |                                       | -100                     | +2   | +100         | nA           |  |  |

| DELta DEO Dalay                                                      |                   | (1)                                     | PFI rising                            | 0.06                     | 0.2  | 2.2          |              |  |  |

| PFI to PFO Delay                                                     |                   | (Note 8)                                | PFI falling                           | 2.4                      | 5    | 12           | μs           |  |  |

| PFI Hysteresis                                                       | VPFH              | PFI rising                              |                                       |                          | 30   |              | mV           |  |  |

| PFO Output Voltage High                                              | VoH               | ISOURCE = 200µ                          | A, PFI = $V_{CC} = V_{CC}(MIN)$       | 0.9 ×<br>V <sub>CC</sub> |      |              | V            |  |  |

| PFO Output Voltage Low                                               | V <sub>OL</sub>   | ISINK = 1.2mA, V                        | BATT = 2V, PFI = V <sub>CC</sub> = 0V |                          |      | 0.2          | V            |  |  |

| WATCHDOG INPUT                                                       |                   |                                         |                                       |                          |      |              |              |  |  |

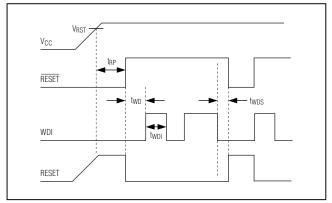

| Watchdog Timeout Period Initial                                      | twD               | Before first WDI                        | edge, after reset timeout             | 1.00                     | 1.6  | 2.25         | S            |  |  |

| Watchdog Timeout Period                                              | twD               | Register select—                        | -long                                 | 1.00                     | 1.6  | 2.25         | S            |  |  |

| Watchdog Timeout Feriod                                              | twds              | Register select—                        | -short                                | 140                      | 200  | 280          | ms           |  |  |

| Minimum WDI Input Pulse Width                                        | twDI              |                                         |                                       | 100                      |      |              | ns           |  |  |

| WELL THE LAND                                                        | VIL               |                                         |                                       |                          |      | 0.3 ×<br>VCC | .,           |  |  |

| WDI Input Threshold                                                  | VIH               |                                         |                                       | 0.7 ×<br>VCC             |      |              | V            |  |  |

| WDI Input Current                                                    | I <sub>I</sub> L  | V <sub>WDI</sub> = V <sub>CC</sub> or G | iND                                   | -100                     |      | +100         | nA           |  |  |

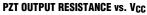

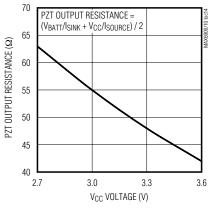

| PZT OUTPUT                                                           |                   |                                         |                                       |                          |      |              |              |  |  |

| D77 0 1 101 10: 10                                                   |                   | MAX69EO30                               | Sink current                          | 5                        |      | 18           |              |  |  |

| PZT Output Short-Circuit Current (VCC Must Be > V <sub>RST</sub> for | I <sub>PZT</sub>  | 1417 (7.03E000                          | Source current                        | 5                        |      | 20           | - mA         |  |  |

| PZT to Be Active)                                                    |                   | MAX69EO33                               | Sink current                          | 6                        |      | 20           |              |  |  |

| ŕ                                                                    |                   |                                         | Source current                        | 6.5                      |      | 25           |              |  |  |

| PZT Frequency 1                                                      | PZT <sub>f1</sub> |                                         |                                       |                          | 1024 |              | Hz           |  |  |

| PZT Frequency 2                                                      | PZT <sub>f2</sub> |                                         |                                       |                          | 2048 |              | Hz           |  |  |

| PZT Frequency 3                                                      | PZT <sub>f3</sub> |                                         |                                       |                          | 4096 |              | Hz           |  |  |

| PZT Frequency 4                                                      | PZT <sub>f4</sub> |                                         |                                       |                          | 8192 |              | Hz           |  |  |

| PZT Off-Leakage Current                                              | lolkg             |                                         |                                       | -1                       |      | +1           | μΑ           |  |  |

| CRYSTAL-FAIL OUTPUT                                                  | Т                 | 1                                       |                                       | ı                        |      |              |              |  |  |

| CX FAIL Output Low Voltage                                           | VOI               |                                         | $_{CC} = 0V, I_{OL} = 3mA$            |                          | 0.1  | 0.2          | <sub>V</sub> |  |  |

| · · · · · · · · · · · · · · · · · · ·                                | 02                | $V_{CC} = 2.7V, I_{OL}$                 | = 5mA, V <sub>BATT</sub> = 0V         |                          |      | 0.25         |              |  |  |

| CX FAIL Off-Leakage Current                                          | lolkg             |                                         |                                       | -1                       |      | +1           | μΑ           |  |  |

| ALARM OUTPUT                                                         | T                 | T                                       |                                       | T                        |      |              |              |  |  |

| ALM Output Low Voltage                                               | V <sub>OL</sub>   |                                         | $T = 2.0V, V_{CC} = 0V$               |                          |      | 0.2          | <u> </u>     |  |  |

|                                                                      |                   | $I_{OL} = 5mA, V_{CC}$                  | = 2.7V, V <sub>BATT</sub> = 0V        |                          |      | 0.25         |              |  |  |

| ALM Off-Leakage Current                                              | lolkg             |                                         |                                       | -1                       |      | +1           | μΑ           |  |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{CC(MIN)})$  to  $V_{CC(MAX)}$ ,  $T_A = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Notes 1, 2)

| PARAMETER                           | SYMBOL             | C                                                                                                                                                                     | ONDITIONS                                                                     | MIN                       | TYP                       | MAX                      | UNITS |  |

|-------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------|---------------------------|--------------------------|-------|--|

| BATTERY ON OUTPUT                   | •                  |                                                                                                                                                                       |                                                                               |                           |                           |                          | •     |  |

| DATT ON Code at Law Valtage         | M                  | $V_{BATT} = 2.0V, I_{OL}$                                                                                                                                             | _ = 3mA, V <sub>CC</sub> = 0V                                                 |                           |                           | 0.2                      | V     |  |

| BATT ON Output Low Voltage          | VoL                | V <sub>BATT</sub> = 2.7V, I <sub>OL</sub>                                                                                                                             | _ = 5mA, V <sub>CC</sub> = 0V                                                 |                           |                           | 0.25                     | j v   |  |

| BATT ON Off-Leakage Current         | lolkg              |                                                                                                                                                                       |                                                                               | -1                        |                           | +1                       | μΑ    |  |

| RESET FUNCTION                      |                    |                                                                                                                                                                       |                                                                               |                           |                           |                          |       |  |

| Reset Threshold                     | \/por              | MAX69EO33                                                                                                                                                             |                                                                               | 2.80                      | 2.93                      | 3.00                     | V     |  |

| Reset ITITESHOID                    | V <sub>RST</sub>   | MAX69EO30                                                                                                                                                             |                                                                               | 2.50                      | 2.63                      | 2.70                     | V     |  |

| V <sub>RST</sub> Hysteresis         | V <sub>H</sub> YST |                                                                                                                                                                       |                                                                               |                           | 10                        |                          | mV    |  |

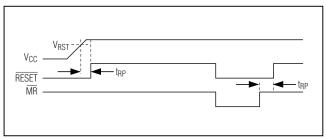

| V <sub>CC</sub> Falling Reset Delay |                    | V <sub>CC</sub> falling from V <sub>RST(MAX)</sub> to V <sub>RST(MIN)</sub> at 10V/ms, measured from the beginning of V <sub>CC</sub> falling to RESET asserting high |                                                                               |                           | 10                        | 50                       | μs    |  |

| Reset Active Timeout Period         | t <sub>RP</sub>    |                                                                                                                                                                       |                                                                               | 140                       | 200                       | 280                      | ms    |  |

| RESET Output Low Voltage            | VoL                | Reset asserted                                                                                                                                                        | I <sub>OL</sub> = 1.6mA,<br>V <sub>BATT</sub> = 2.0V,<br>V <sub>CC</sub> = 0V |                           |                           | 0.2                      | V     |  |

| RESET Off-Leakage Current           | ILKG               |                                                                                                                                                                       | •                                                                             | -1                        |                           | +1                       | μΑ    |  |

| RESET Output High Voltage           |                    | Reset asserted                                                                                                                                                        | I <sub>OH</sub> = 50μA, V <sub>CC</sub> = 1.0V,<br>V <sub>BATT</sub> = 0V     | 0.8 ×<br>V <sub>C</sub> C |                           |                          | - v   |  |

| neser Output riigh voltage          | Voh                | neset asserted                                                                                                                                                        | $I_{OH} = 1mA$ , $V_{CC} = 2V$ , $V_{BATT} = 0V$                              | 0.9 ×<br>V <sub>CC</sub>  |                           |                          |       |  |

| RESET Output Low Voltage            | V <sub>OL</sub>    | $V_{CC} = V_{CC(MIN)}$                                                                                                                                                |                                                                               |                           | 0.032                     | 0.1                      | V     |  |

| 2-WIRE DIGITAL INPUTS (SCL,         | SDA) (VCC(MI       | V) < VCC < VCC(MA                                                                                                                                                     | X))                                                                           |                           |                           |                          |       |  |

| Input High Voltage                  | VIH                |                                                                                                                                                                       |                                                                               | 0.7 ×<br>VCC              |                           |                          | V     |  |

| Input Low Voltage                   | VIL                |                                                                                                                                                                       |                                                                               |                           |                           | 0.3 ×<br>V <sub>CC</sub> | V     |  |

| Input Hysteresis                    | VHYS               |                                                                                                                                                                       |                                                                               |                           | 0.05 ×<br>V <sub>CC</sub> |                          | V     |  |

| Input Leakage Current               |                    | V <sub>IN</sub> = GND or V <sub>CC</sub>                                                                                                                              |                                                                               | -1                        |                           | +1                       | μΑ    |  |

| Input Capacitance                   |                    | (Note 8)                                                                                                                                                              |                                                                               |                           |                           | 10                       | рF    |  |

| Output Low Voltage                  | V <sub>OL</sub>    | I <sub>OL</sub> = 4mA, V <sub>CC</sub> =                                                                                                                              | = VCC(MIN)                                                                    |                           |                           | 0.4                      | V     |  |

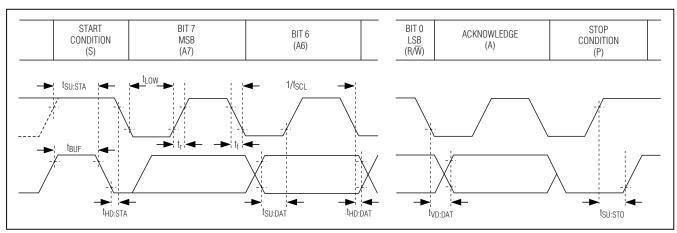

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC(MIN)} < V_{CC} < V_{CC(MAX)}, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                                                                                            | SYMBOL         | CONDITIONS     | MIN TYP                      | MAX    | UNITS |

|------------------------------------------------------------------------------------------------------|----------------|----------------|------------------------------|--------|-------|

| 2-WIRE BUS TIMING                                                                                    |                |                |                              |        |       |

| SCL Clock Frequency                                                                                  | fscl           | (Note 9)       | 0.32                         | 400.00 | kHz   |

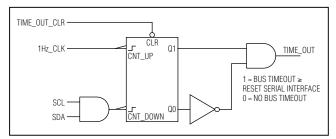

| Bus Timeout                                                                                          | ttimeout       |                | 1                            | 2      | S     |

| Bus Free Time Between STOP and START Condition                                                       | tBUF           |                | 1.3                          |        | μs    |

| Hold Time After (Repeated)<br>START Condition; After This<br>Period, the First Clock Is<br>Generated | tHD:STA        |                | 0.6                          |        | μs    |

| Repeated START Condition<br>Setup Time                                                               | tsu:sta        |                | 0.6                          |        | μs    |

| STOP Condition Setup Time                                                                            | tsu:sto        |                | 0.6                          |        | μs    |

| Data Hold Time                                                                                       | thd:dat        | (Notes 10, 11) | 0                            | 0.9    | μs    |

| Data Setup Time                                                                                      | tsu:dat        |                | 100                          |        | ns    |

| SCL Low to Data Out Valid                                                                            | tvd:dat        | (Note 8)       | 50                           |        | ns    |

| SCL Low Period                                                                                       | tLOW           |                | 1.3                          |        | μs    |

| SCL High Period                                                                                      | thigh          |                | 0.6                          |        | μs    |

| SCL/SDA Rise Time                                                                                    | t <sub>R</sub> | (Note 12)      | 20 + 0.1<br>x C <sub>B</sub> | 300    | ns    |

| SCL/SDA Fall Time (Receiving)                                                                        | tϝ             | (Notes 12, 13) | 20 + 0.1<br>x C <sub>B</sub> | 300    | ns    |

| SCL/SDA Fall Time (Transmitting)                                                                     | t⊨             | (Notes 12, 13) | 20 + 0.1<br>x C <sub>B</sub> | 250    | ns    |

| Pulse Width of Spike Suppressed                                                                      | tsp            | (Note 8)       |                              | 50     | ns    |

| Capacitive Load of Each Bus<br>Line                                                                  | СВ             |                |                              | 400    | рF    |

- **Note 1:**  $V_{RST}$  is the reset threshold for  $V_{CC}$ . See the *Ordering Information*.

- **Note 2:** All parameters are 100% tested at  $T_A = +85$ °C. Limits over temperature are guaranteed by design and not production tested.

- **Note 3:** 2-wire serial interface is operational for  $V_{CC} > V_{RST}$ .

- Note 4: See the Detailed Description section (BATT function).

- Note 5: IBATT and ICCS are specified with SDA and SCLK pulled high, OUT floating, and CE OUT floating.

- **Note 6:** 2-wire serial interface operating at 400kHz, SDA pulled high.

- Note 7: For OUT switch over to BATT, V<sub>CC</sub> must fall below V<sub>RST</sub> and V<sub>BATT</sub>. For OUT switchover to V<sub>CC</sub>, V<sub>CC</sub> must be above V<sub>RST</sub> or above V<sub>BATT</sub>.

- Note 8: Guaranteed by design. Not production tested.

- **Note 9:** Due to the 2-wire bus timeout feature, there is a minimum specification on the SCL clock frequency based on a 31-byte burst-mode transaction to RAM. See the *Timeout Feature* section.

- **Note 10:** A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IH min</sub> of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

- Note 11: The maximum tho:DAT only has to be met if the device does not stretch the LOW period (tLOW) of the SCL signal.

- **Note 12:**  $C_B$  = total capacitance of one bus line in pF.

- Note 13: The maximum t<sub>F</sub> for the SDA and SCL bus lines is specified at 300ns. The maximum fall time for the SDA output stage t<sub>F</sub> is specified at 250ns. This allows series protection resistors to be connected between the SDA/SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>F</sub>.

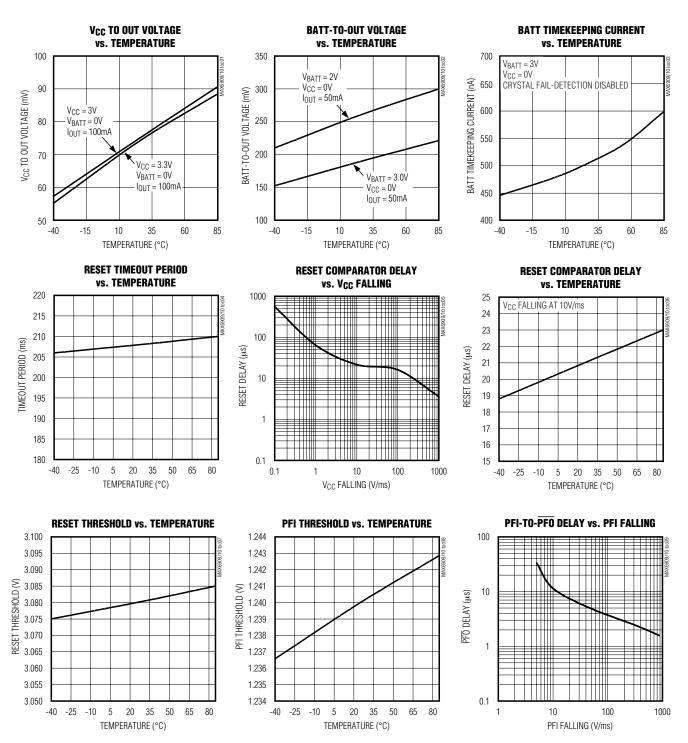

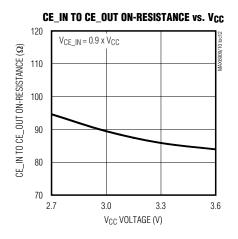

**Typical Operating Characteristics**

(VCC = 3.3V, VBATT = 3V, TA = +25°C, unless otherwise noted.)

# $I^2C$ -Compatible Real-Time Clocks with $\mu P$ Supervisor and NV RAM Controller

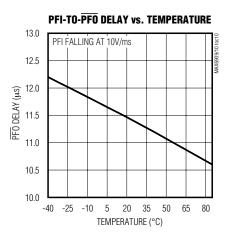

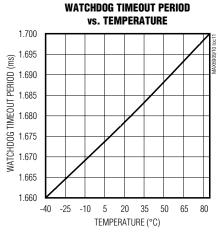

### Typical Operating Characteristics (continued)

(VCC = 3.3V, VBATT = 3V, TA = +25°C, unless otherwise noted.)

### CE\_IN TO CE\_OUT ON-RESISTANCE vs. Temperature

### PZT OUTPUT RESISTANCE vs. TEMPERATURE

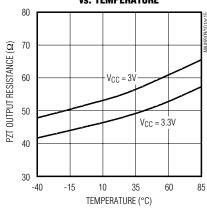

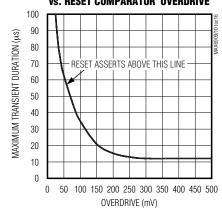

### MAXIMUM TRANSIENT DURATION vs. RESET COMPARATOR OVERDRIVE

### **Pin Description**

|     | T       |                                                                                                                                                                     |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | NAME    | FUNCTION                                                                                                                                                            |

| 1   | BATT    | Backup Battery Input. When $V_{CC}$ falls below the reset threshold and $V_{BATT}$ , OUT connects to BATT. Connect BATT to GND if no backup battery supply is used. |

| 2   | OUT     | Supply Output for CMOS RAM or Other ICs Requiring Use of Backup Battery Power. Bypass to GND with at least a 0.1µF capacitor.                                       |

| 3   | BATT ON | Logic Output Open Drain. BATT ON is low when the MAX6909/MAX6910 are powered from BATT.                                                                             |

| 4   | CEIN    | Chip-Enable Input. Input to the chip-enable switch used for external RAM. Connect to VCC if unused.                                                                 |

| 5   | PFI     | Power-Fail Comparator Input. For monitoring external power supplies.                                                                                                |

| 6   | MR      | Manual Reset Input. The active-low input has an internal pullup resistor. Internal debouncing circuitry ensures noise immunity. Leave open if unused.               |

| 7   | WDI     | Watchdog Input                                                                                                                                                      |

| 8   | GND     | Ground                                                                                                                                                              |

| 9   | X1      | 32.768kHz Crystal Pin; Oscillator Input                                                                                                                             |

| 10  | X2      | 32.768kHz Crystal Pin; Oscillator Output                                                                                                                            |

| 11  | CX FAIL | Crystal Fail Output. Open drain, active low.                                                                                                                        |

| 12  | SDA     | Serial Data Line. Data input/output connection for the 2-wire serial interface.                                                                                     |

| 13  | SCL     | Serial Clock Line. Clock input connection for the 2-wire serial interface.                                                                                          |

| 14  | ALM     | Alarm Output. Open drain, active low.                                                                                                                               |

| 15  | PZT     | Piezo Transducer Output. Push-pull Piezo transducer output.                                                                                                         |

| 16  | PFO     | Power-Fail Comparator Output. Push-pull active low.                                                                                                                 |

| 17  | CE OUT  | Chip-Enable Output. For controlling external RAM.                                                                                                                   |

| 18  | RESET   | Open-Drain, Active-Low Reset Output                                                                                                                                 |

| 19  | RESET   | Push-Pull, Active-High Reset Output. Complement of RESET.                                                                                                           |

| 20  | Vcc     | Main Supply Input. Bypass to GND with at least a 0.01µF capacitor.                                                                                                  |

### **Detailed Description**

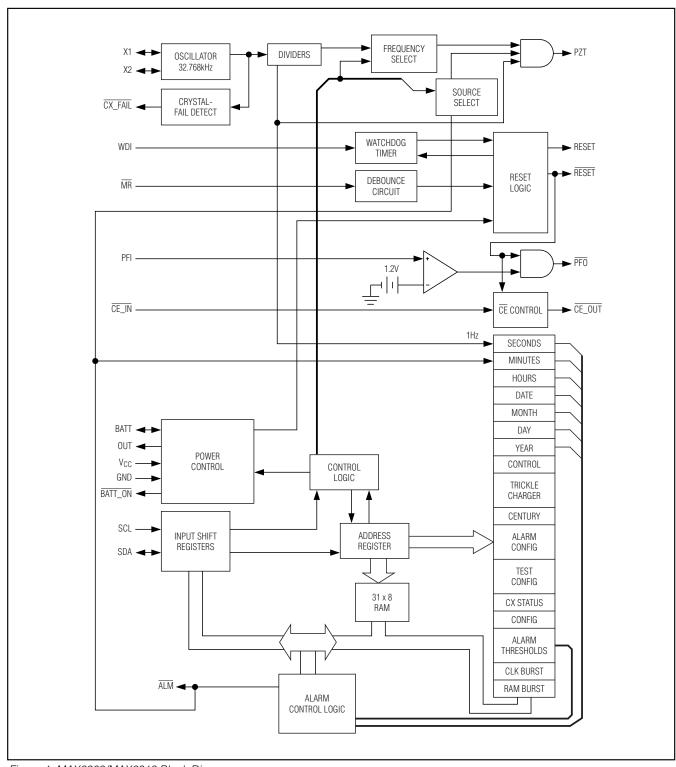

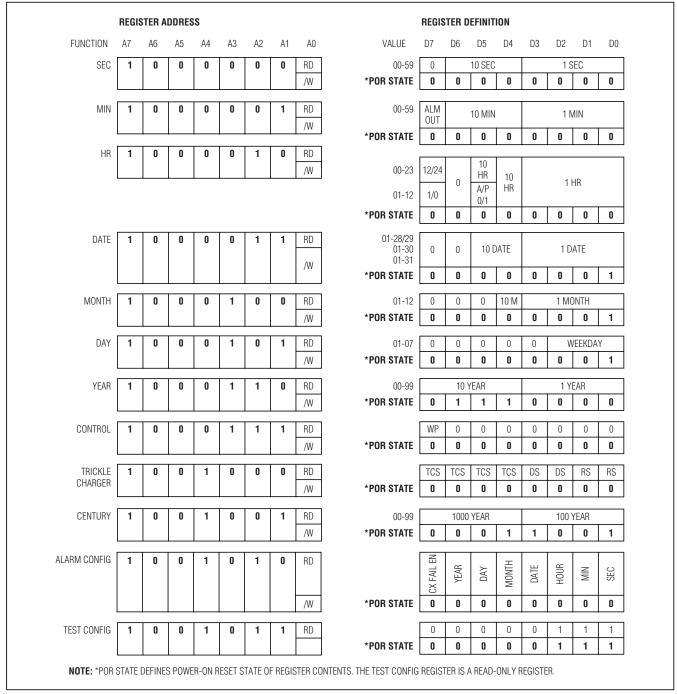

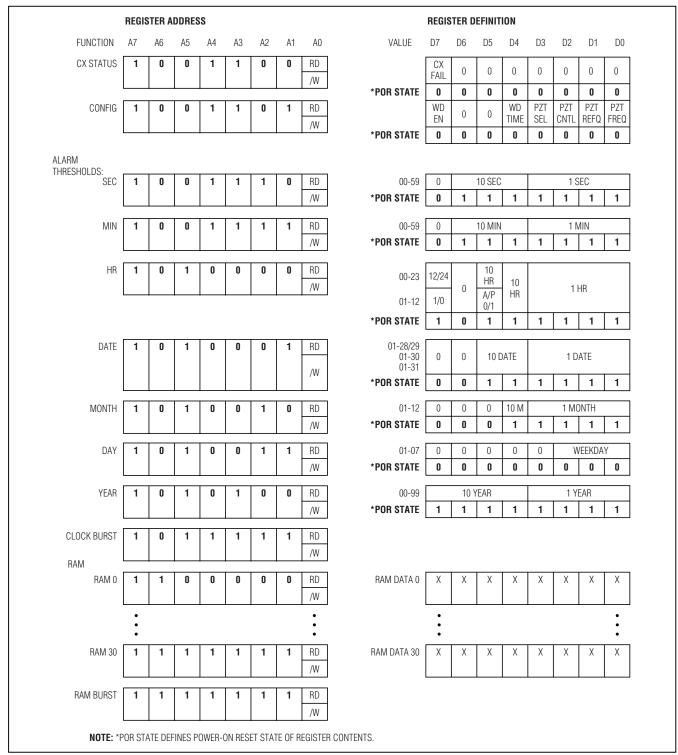

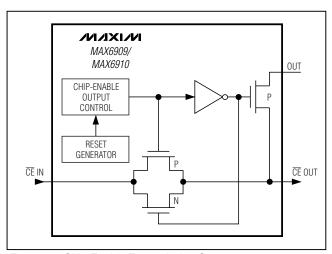

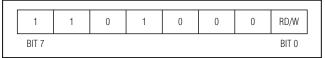

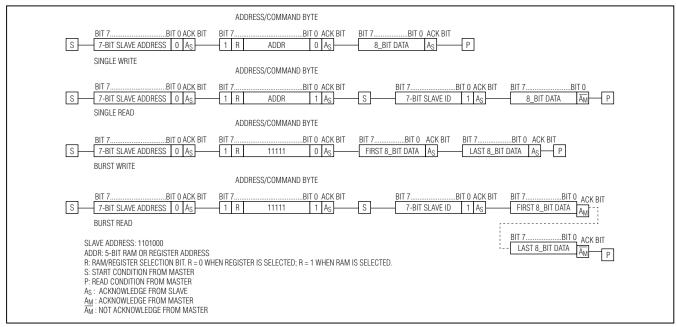

The MAX6909/MAX6910 contain eight 8-bit timekeeping registers, two burst address registers, a trickle charge register, a control register, a configuration register, an alarm configuration register, and seven alarm threshold registers, all controlled through a 2-wire serial interface. Figure 1 is the MAX6909/MAX6910 block diagram.

The OUT pin supplies voltage for CMOS RAM or other ICs requiring the use of backup battery power. When V<sub>CC</sub> rises above the reset threshold (V<sub>RST</sub>) or above V<sub>BATT</sub>, OUT is connected to V<sub>CC</sub>. When V<sub>CC</sub> falls below V<sub>RST</sub> and V<sub>BATT</sub>, BATT is connected to OUT. If enabled, an on-board trickle charger charges BATT from V<sub>CC</sub>. BATT can act as a backup supply from either a battery or SuperCap<sup>TM</sup>. When operating from BATT, the battery-on output (BATT ON) is pulled low and can be used as an indicator of operation in battery backup mode.

SuperCap is a trademark of Baknor Industries.

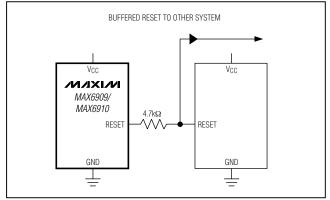

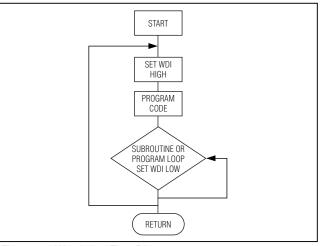

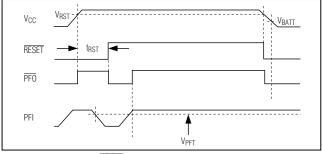

There are two reset outputs, RESET and RESET. They become active while V<sub>CC</sub> is below the reset threshold (V<sub>RST</sub>) or while manual reset (MR) is held low, and for t<sub>RP</sub> after MR goes high, V<sub>CC</sub> rises above the reset threshold, or a WDI pulse is not received when the watchdog function is enabled. Reset thresholds are available for 3V and 3.3V applications. See the *Ordering Information* for specifics. MR is internally pulled high and contains debounce circuitry to accommodate a manual pushbutton reset switch. The WDI, when enabled, keeps RESET and RESET from becoming active if it is strobed once every twDs or twD. The watchdog timeout is selectable in the configuration register.

Other features include internal chip-enable gating logic, which accepts a valid  $\overline{\text{CE IN}}$  from a microprocessor and only gates it through as valid to  $\overline{\text{CE OUT}}$  when the MAX6909/MAX6910 are not in a reset state. This can be used for disabling CMOS RAM to limit current consumption when OUT is switched to BATT.

Figure 1. MAX6909/MAX6910 Block Diagram

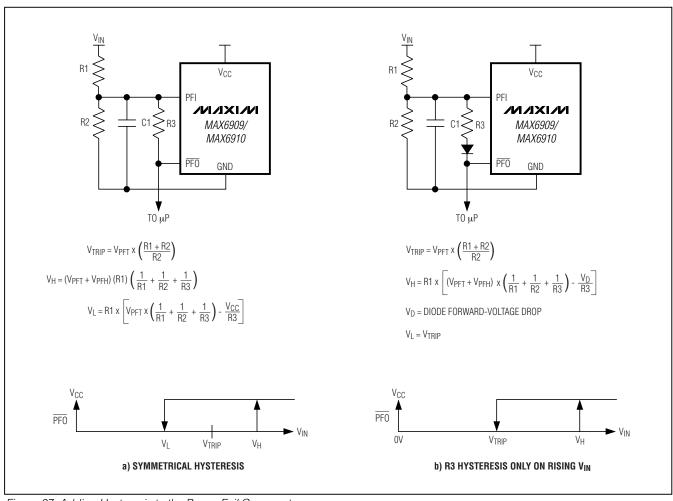

A power-fail comparator is available to monitor other system voltages through PFI and report the status through PFO. If the MAX6909/MAX6910 are in reset, PFO is low; otherwise, it is high as long as PFI is greater than 1.27V (typ).

The piezo transducer drive output (PZT) has register-selectable frequencies of 1.024kHz, 2.048kHz, 4.096kHz, or 8.192kHz. This output can be selected to become active when the alarm is triggered or can be independently controlled through the configuration register. When activated, the PZT outputs a frequency with an attention-getting 1Hz duty cycle of 50% on and 50% off.

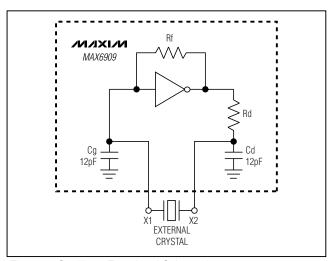

An on-chip crystal oscillator maintaining circuit, for use with a 32.768kHz crystal, provides the <u>clock for</u> time-keeping functions. A crystal fail output (CX FAIL) alerts the user when the 32.768kHz crystal oscillator has failed for 30 cycles (typ), resulting in conditions that produce invalid timekeeping data. The crystal fail function can also be polled by reading the status bit in the CX status register.

#### **Crystal Selection**

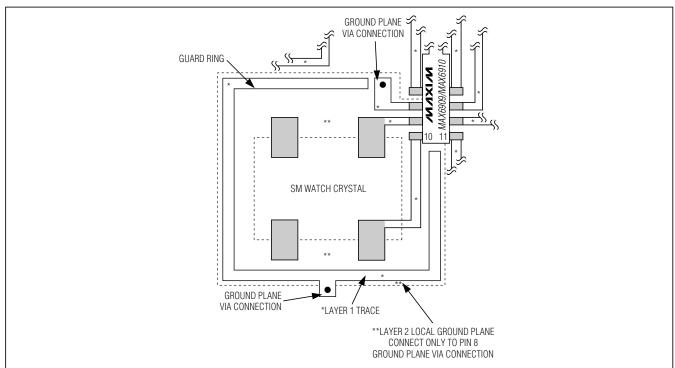

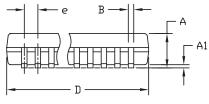

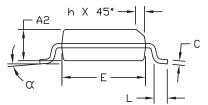

A 32.768kHz crystal is connected to the MAX6909/MAX6910 through pins 9 and 10 (X1 and X2). The crystal selected for use should have a specified load capac-

itance (CL) of 6pF where the capacitive load is included in the MAX6909/MAX6910. When designing the PC board, keep the crystal as close to the X1 and X2 pins as possible. Keep the trace lengths short and small and place a guard ring around the crystal and connect the ring to GND to reduce capacitive loading and prevent unwanted noise pickup. Keep all signals out from beneath the crystal and the X1 and X2 pins to prevent noise coupling. Finally, an additional local ground plane on an adjacent PC board layer can be added under the crystal to shield it from unwanted pickup from traces on other layers of the board. This plane should be isolated from the regular PC board ground plane, should be no larger than the perimeter of the guard ring, and connected to the GND pin of the MAX6909/MAX6910. Ensure that this ground plane does not contribute to significant capacitance between signal line and ground on the connections that run from X1 and X2 to the crystal. Figure 2 shows the recommended crystal layout.

Some crystal manufacturers and part numbers for their SMT, 32.768kHz watch crystals that require 6pF loads are listed in Table 1. In addition, these manufacturers offer other package options depending upon the specific application considerations.

Figure 2. Recommended Crystal Layout

Table 1. Crystal Manufacturers and Part Numbers

| MANUFACTURER          | PART                                | TEMP<br>RANGE (°C) | C <sub>L</sub><br>(pF) | +25°C FREQUENCY<br>TOLERANCE (ppm) |

|-----------------------|-------------------------------------|--------------------|------------------------|------------------------------------|

| Caliber Electronics   | AWS2A-32.768KHz,<br>AWS2B-32.768KHz | -20 to +70         | 6                      | ±20                                |

| ECS INC International | ECS327-6.0-17                       | -10 to +60         | 6                      | ±20                                |

| Fox Electronics       | FSM327                              | -40 to +85         | 6                      | ±20                                |

| M-tron                | SX2010/ SX2020                      | -20 to +75         | 6                      | ±20                                |

| Raltron               | RSE-32.768-6-C-T                    | -10 to +60         | 6                      | ±20                                |

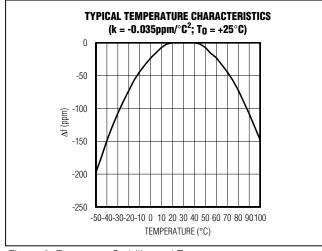

Timekeeping accuracy of the MAX6909/MAX6910 is dependent on the frequency stability of the external crystal. To determine frequency stability, use the parabolic curve of Figure 3 and the following equations:

$$\Delta f = f \times k \times (T_0 - T)^2$$

where:

$\Delta f$  = change in frequency from +25°C (Hz)

f = nominal crystal frequency (Hz)

k = parabolic curvature constant (-0.035 ±0.005ppm/°C<sup>2</sup> for 32.768kHz watch crystals)

$T_0$  = turnover temperature (+25°C ±5°C for 32.768kHz watch crystals)

T = temperature of interest (°C)

For example: What is the worst-case change in oscillator frequency from +25°C ambient to +45°C ambient?

$$\Delta f_{drift} = 32,768$$

Hz  $\times (-0.04$ ppm/°C)<sup>2</sup>  $\times (20$ °C  $-45$ °C)<sup>2</sup> =  $-0.8192$ Hz

What is the worst-case timekeeping error per second?

1) Error due to temperature drift:

2) Error due to +25°C initial crystal tolerance of ±20ppm:

$$\begin{split} & \Delta f_{initial} = 32,768 \text{Hz} \times (\text{-20ppm}) = \text{-0.65536Hz} \\ & \Delta t_{initial} = \left\{ \left[ 1 \, / \, \left[ \left( f + \Delta f_{initial} \right) \, / \, 32,768 \right] \right] \text{--} 1 \right\} \, / \, 1s \\ & \Delta t_{initial} = \left\{ \left[ 1 \, / \, \left[ 32,768 \, \text{--} \, 0.65536 \, / \, 32,768 \right] \right] \text{--} 1 \right\} \, / \\ & 1s = 0.000020s \, / \, s \end{split}$$

3) Total timekeeping error per second:

$$\Delta t_{total} = \Delta t_{drift} + t_{initial}$$

$$\Delta t_{total} = 0.000025 \text{s/s} + 0.000020 \text{s/s} = 0.000045 \text{s/s}$$

Figure 3. Frequency Stability and Temperature

Figure 4. Oscillator Functional Schematic

Table 2. Acceptable Quartz Crystal Parameters

| PARAMETER                          | SYMBOL | MIN    | TYP    | MAX | UNITS |

|------------------------------------|--------|--------|--------|-----|-------|

| Frequency                          | f      |        | 32.768 |     | kHz   |

| Equivalent series resistance (ESR) | Rs     |        |        | 60  | kΩ    |

| Parallel load capacitance          | CL     |        | 6      |     | pF    |

| Q factor                           | Q      | 40,000 |        |     |       |

After 1 month that translates to:

$$\Delta t = (31 \text{day}) \times \left(24 \frac{\text{hr}}{\text{day}}\right) \times \left(60 \frac{\text{min}}{\text{hr}}\right) \times \left(60 \frac{\text{s}}{\text{min}}\right) \times \left(0.000045 \text{s/s}\right) = 120.158 \text{s}$$

Total worst-case timekeeping error at the end of 1 month at +45°C is approximately 120s or 2min (assumes negligible parasitic layout capacitance). Figure 5 shows the register address definition. Table 3 is the hex register address/description.

#### **Control Register (Write Protect Bit)**

Bit 7 of the control register is the write protect bit. The lower 7 bits (bits 0–6) are forced to zero and always read a zero when read. Before any write operation to the clock or RAM, bit 7 must be zero. When high, the write protect bit prevents a write operation to any other register.

#### Hours Register (AM-PM/12-24 Mode)

Bit 7 of the hours register is defined as the 12-hour or 24-hour mode select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the AM/PM bit with logic high being PM. In the 24-hour mode, bit 5 is the second 10-hour bit (20h–23h).

#### **Clock Burst**

Addressing the clock burst register specifies burst mode operation. In this mode, the first seven clock/calendar registers and the control register can be consecutively read or written starting with bit 7 of address BEh for a write and BFh for a read. If the write protect bit is set high when a write clock/calendar burst mode is specified, no data transfer occurs to any of the seven clock/calendar registers or the control register. When writing to the clock registers in the burst mode, all eight registers must be written in order for the data to be transferred. In addition, the WP bit in the control register must be set to zero prior to a clock burst write.

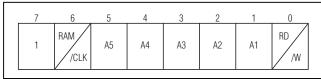

#### RΔM

The static RAM is 31 bytes addressed consecutively in the RAM address space. Even address/commands (C0h–FCh) are used for writes, and odd address/commands (C1h–FDh) are used for reads. The contents of the RAM are static and remain valid for V<sub>OUT</sub> down to 1.5V (typ).

#### **RAM Burst**

Addressing the RAM burst register specifies burst mode operation. In this mode, the 31 RAM registers can be consecutively read or written starting with bit 7 of address FEh for a write and FFh for a read. When writing to RAM in burst mode, it is not necessary to write all 31 bytes for the data to transfer. Each byte that is written to is transferred to RAM regardless of whether all 31 bytes are written.

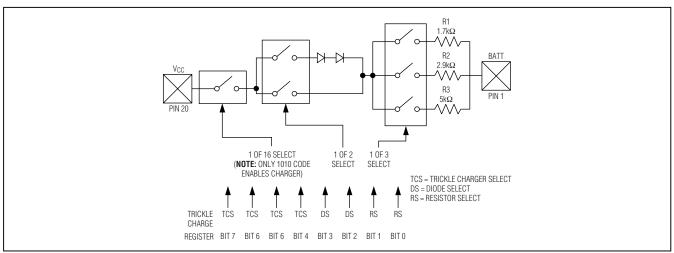

#### Trickle Charge Register (MAX6910)

The trickle charge register controls the trickle charger characteristics of the MAX6910. The trickle charger functional schematic (Figure 6) shows the basic components of the trickle charger. Table 4 details the bit settings for trickle charger control. Trickle charge selection (TCS) bits D7-D4 control the selection of the trickle charger. In order to prevent accidental enabling, only a pattern of 1010 enables the trickle charger. All other patterns disable the trickle charger. The MAX6910 powers up with the trickle charger disabled. The diode select (DS) bits (D3-D2) select whether two diodes or no diodes are connected between VCC and BATT. If DS is 10, no diode is selected; if DS is 01, two diodes are selected. If DS is 00 or 11, the trickle charger is disabled independent of the state of the TCS bits. The RS bits (D1-D0) select the resistor that is connected between V<sub>CC</sub> and BATT. If both RS bits are set to zero, the trickle charger is disabled, regardless of any other bit states in the trickle charger register. RS bits set to 10 select a 1.7K, 01 selects 2.9K, and 11 select 5K.

Figure 5. Register Address Definition (Sheet 1 of 2)

Figure 5. Register Address Definition (Sheet 2 of 2)

Table 3. Hex Register Address/Description

| WRITE (HEX) | READ (HEX) | DESCRIPTION             | POR CONTENTS (HEX) | POR CONTENTS (BCD) |

|-------------|------------|-------------------------|--------------------|--------------------|

| 80          | 81         | Seconds                 | 00                 | 00                 |

| 82          | 83         | Minutes                 | 00                 | 00                 |

| 84          | 85         | Hours                   | 00                 | 00                 |

| 86          | 87         | Date                    | 01                 | 01                 |

| 88          | 89         | Month                   | 01                 | 01                 |

| 8A          | 8B         | Day                     | 01                 | 01                 |

| 8C          | 8D         | Year                    | 70                 | 70                 |

| 8E          | 8F         | Control                 | 00                 | 00                 |

| 90          | 91         | Trickle charger         | 00                 | 00                 |

| 92          | 93         | Century                 | 19                 | 19                 |

| 94          | 95         | Alarm configuration     | 00                 | 00                 |

| _           | 97         | Test configuration*     | 07                 | 07                 |

| 98          | 99         | CX status               | 00                 | 00                 |

| 9A          | 9B         | Configuration           | 00                 | 00                 |

| 9C          | 9D         | Seconds alarm threshold | 7F                 | 7F                 |

| 9E          | 9F         | Minutes alarm threshold | 7F                 | 7F                 |

| A0          | A1         | Hours alarm threshold   | BF                 | BF                 |

| A2          | A3         | Date alarm threshold    | 3F                 | 3F                 |

| A4          | A5         | Month alarm threshold   | 1F                 | 1F                 |

| A6          | A7         | Day alarm threshold     | 00                 | 00                 |

| A8          | A9         | Year alarm threshold    | FF                 | FF                 |

| BE          | BF         | Clock burst             | N/A                | N/A                |

| C0          | C1         | RAM 0                   | Indeterminate      | Indeterminate      |

| C2          | C3         | RAM 1                   | Indeterminate      | Indeterminate      |

| C4          | C5         | RAM 2                   | Indeterminate      | Indeterminate      |

| C6          | C7         | RAM 3                   | Indeterminate      | Indeterminate      |

| C8          | C9         | RAM 4                   | Indeterminate      | Indeterminate      |

| CA          | СВ         | RAM 5                   | Indeterminate      | Indeterminate      |

| CC          | CD         | RAM 6                   | Indeterminate      | Indeterminate      |

| CE          | CF         | RAM 7                   | Indeterminate      | Indeterminate      |

| D0          | D1         | RAM 8                   | Indeterminate      | Indeterminate      |

| D2          | D3         | RAM 9                   | Indeterminate      | Indeterminate      |

| D4          | D5         | RAM 10                  | Indeterminate      | Indeterminate      |

| D6          | D7         | RAM 11                  | Indeterminate      | Indeterminate      |

| D8          | D9         | RAM 12                  | Indeterminate      | Indeterminate      |

| DA          | DB         | RAM 13                  | Indeterminate      | Indeterminate      |

| DC          | DD         | RAM 14                  | Indeterminate      | Indeterminate      |

| DE          | DF         | RAM 15                  | Indeterminate      | Indeterminate      |

| E0          | E1         | RAM 16                  | Indeterminate      | Indeterminate      |

| E2          | E3         | RAM 17                  | Indeterminate      | Indeterminate      |

<sup>\*</sup>This is a read-only register.

Table 3. Hex Register Address/Description (continued)

| WRITE (HEX) | READ (HEX) | DESCRIPTION | POR CONTENTS (HEX) | POR CONTENTS (BCD) |

|-------------|------------|-------------|--------------------|--------------------|

| E4          | E5         | RAM 18      | Indeterminate      | Indeterminate      |

| E6          | E7         | RAM 19      | Indeterminate      | Indeterminate      |

| E8          | E9         | RAM 20      | Indeterminate      | Indeterminate      |

| EA          | EB         | RAM 21      | Indeterminate      | Indeterminate      |

| EC          | ED         | RAM 22      | Indeterminate      | Indeterminate      |

| EE          | EF         | RAM 23      | Indeterminate      | Indeterminate      |

| F0          | F1         | RAM 24      | Indeterminate      | Indeterminate      |

| F2          | F3         | RAM 25      | Indeterminate      | Indeterminate      |

| F4          | F5         | RAM 26      | Indeterminate      | Indeterminate      |

| F6          | F7         | RAM 27      | Indeterminate      | Indeterminate      |

| F8          | F9         | RAM 28      | Indeterminate      | Indeterminate      |

| FA          | FB         | RAM 29      | Indeterminate      | Indeterminate      |

| FC          | FD         | RAM 30      | Indeterminate      | Indeterminate      |

| FE          | FF         | RAM Burst   | N/A                | N/A                |

Diode and resistor selection is determined by the user, according to the maximum current desired for the battery or SuperCap charging. The maximum charging current can be calculated as shown in the following example. Assume that a system power supply of 3V is applied to  $V_{\rm CC}$  and a SuperCap is connected to BATT. Also assume that the trickle charger has been enabled with no diode and resistor R1 between  $V_{\rm CC}$  and BATT. The maximum current  $I_{\rm MAX}$  would therefore be calculated as follows:

$$I_{MAX} = \frac{3.0V}{R1} \approx \frac{3.0V}{1.7k\Omega} \approx 1.76mA$$

As the SuperCap charges, the voltage difference between VCC and VBATT decreases, and therefore the charge current decreases. The MAX6909 does not feature a trickle charger.

### Power Control, Trickle Charger, and Battery Switchover

BATT provides power as a battery backup. V<sub>CC</sub> provides the primary power in dual-supply systems where BATT is connected as a backup source to maintain the timekeeping function and RAM + register contents. When V<sub>CC</sub> rises above the reset threshold, V<sub>RST</sub>, V<sub>CC</sub> powers the MAX6909/MAX6910. When V<sub>CC</sub> falls below the reset

threshold, VRST, and is less than V<sub>TPD</sub>, BATT powers the MAX6909/MAX6910. If V<sub>CC</sub> falls below the reset threshold, V<sub>RST</sub>, and is more than V<sub>TPD</sub>, V<sub>CC</sub> powers the MAX6909/MAX6910. When RESET and RESET are active, all inputs (MR, WDI, CE IN, and the 2-wire interface) are disabled. In addition, when operating from BATT, the outputs RESET, RESET, and PFO remain in the active state, PZT is high impedance and CE OUT is pulled to OUT. The timekeeping function remains active, together with the alarm function and crystal fail function if enabled. To minimize power consumption when operating from BATT, some functions are disabled; see Table 5. MAX6909/MAX6910 functional blocks remain active when powered from V<sub>CC</sub> or BATT.

A battery can be connected prior to application of VCC with no current being drawn from the battery and the MAX6909/MAX6910 remaining inactive. This is the freshness seal mode of operation. On the very first application of VCC to the MAX6909/MAX6910, VCC must rise above the reset threshold. The battery should only be changed with VCC applied in order to maintain timekeeping functions.

The trickle charger can be enabled and disabled through software control but is automatically disabled whenever V<sub>CC</sub> falls below V<sub>BATT</sub>.

Table 4. Trickle-Charger Register Control

| D7  | D6  | D5  | D4  | D3 | D2 | D1 | D0 | ACTION                             |

|-----|-----|-----|-----|----|----|----|----|------------------------------------|

| TCS | TCS | TCS | TCS | DS | DS | RS | RS | ACTION                             |

| X   | Χ   | Χ   | Χ   | 0  | 0  | Χ  | X  | Trickle charger disabled           |

| X   | Χ   | Χ   | Χ   | 1  | 1  | Χ  | Χ  | Trickle charger disabled           |

| X   | Χ   | Χ   | Χ   | Χ  | Χ  | 0  | 0  | Trickle charger disabled           |

| 1   | 0   | 1   | 0   | 1  | 0  | 1  | 0  | No diode selected; 1.7K selected   |

| 1   | 0   | 1   | 0   | 1  | 0  | 0  | 1  | No diode selected; 2.9K selected   |

| 1   | 0   | 1   | 0   | 1  | 0  | 1  | 1  | No diode selected; 5K selected     |

| 1   | 0   | 1   | 0   | 0  | 1  | 1  | 0  | Two diodes selected; 1.7K selected |

| 1   | 0   | 1   | 0   | 0  | 1  | 0  | 1  | Two diodes selected; 2.9K selected |

| 1   | 0   | 1   | 0   | 0  | 1  | 1  | 1  | Two diodes selected; 5K selected   |

Figure 6. Trickle-Charger Functional Schematic

#### **OUT Function**

OUT is an output supply voltage for external devices. When  $V_{CC}$  rises above the reset threshold or is greater than  $V_{BATT}$ , OUT connects to  $V_{CC}$ . When  $V_{CC}$  falls below  $V_{RST}$  and  $V_{BATT}$ , OUT connects to BATT. There is a typical  $V_{TRU}$  -  $V_{TRD}$  hysteresis associated with the switching between  $V_{CC}$  and BATT if BATT <  $V_{RST}$  and typically  $V_{HYST}$  of hysteresis if BATT >  $V_{RST}$ . Connect at least a 0.1 $\mu$ F capacitor from OUT to ground (GND). Switching from  $V_{CC}$  to BATT uses a break-before-make switch; a capacitor from OUT to GND prevents loss of power needed for clock data and RAM during switchover.

#### **Oscillator Start Time**

The MAX6909/MAX6910 oscillator typically takes 100ms to settle to its optimum operating power level after start-up. To ensure the oscillator is operating, the system software should validate this by reading the seconds register. Any reading with more than 0s, from the POR value of 0s, is a validation that the oscillator is operating.

#### **Power-On Reset (POR)**

The MAX6909/MAX6910 contain an integral POR circuit that ensures all registers are reset to a known state on power-up. On initial power-up, once Vout rises above 0.75V (typ), the POR circuit releases the registers for normal operation. Should Vout dip to less than 1.5V (typ), the contents of the MAX6909/MAX6910 registers can no longer be guaranteed.

Table 5. MAX6910 I/O and IC Sections Powered from Vcc and BATT

| DESCRIPTION                                                                 | PIN     | PIN NAME     | POWER = VCC | V <sub>CC</sub> <<br>V <sub>RST</sub> | V <sub>CC</sub> < V <sub>RST</sub><br>COMMENTS | COMMENTS                 |

|-----------------------------------------------------------------------------|---------|--------------|-------------|---------------------------------------|------------------------------------------------|--------------------------|

| Crystal Oscillator I/O                                                      | 9       | X1           | Enabled     | Enabled                               |                                                |                          |

| Crystal Oscillator I/O                                                      | 10      | X2           | Enabled     | Enabled                               |                                                |                          |

| Backup Power-Supply Input                                                   | 1       | BATT         | N/A         | N/A                                   |                                                | Power pin                |

| OUT (> of V <sub>CC</sub> or BATT if V <sub>CC</sub> < V <sub>RESET</sub> ) | 2       | OUT          | N/A         | N/A                                   |                                                | Power output<br>pin      |

| Manual Reset Input                                                          | 6       | MR           | Enabled     | Disabled                              | Input ignored                                  |                          |

| Battery-On Output                                                           | 3       | BATT ON      | Enabled     | Enabled                               |                                                |                          |

| Watchdog Input                                                              | 7       | WDI          | Enabled     | Disabled                              | Input ignored                                  |                          |

| Chip-Enable Input                                                           | 4       | <u>CE IN</u> | Enabled     | Disabled                              | Input ignored                                  |                          |

| Power-Fail Input                                                            | 5       | PFI          | Enabled     | Disabled                              | Input ignored                                  |                          |

| Ground                                                                      | 8       | GND          | N/A         | N/A                                   |                                                | Power pin                |

| Active Low, Open-Drain Reset Output (-OD)                                   | 18      | RESET        | Enabled     | Enabled                               | Pulled low                                     |                          |

| Active High, Push/Pull Reset Output                                         | 19      | RESET        | Enabled     | Enabled                               | Pulled to V <sub>CC</sub>                      |                          |

| Chip-Enable Output                                                          | 17      | CE OUT       | Enabled     | Disabled                              | Pulled to OUT                                  |                          |

| Power-Fail Output                                                           | 16      | PFO          | Enabled     | Enabled                               | Pulled low                                     |                          |

| Alarm Output                                                                | 14      | ĀLM          | Enabled     | Enabled                               |                                                |                          |

| Piezo Output                                                                | 15      | PZT          | Enabled     | Disabled                              | High impedance                                 |                          |

| Crystal-Fail Output                                                         | 11      | CX FAIL      | Enabled     | Enabled                               |                                                |                          |

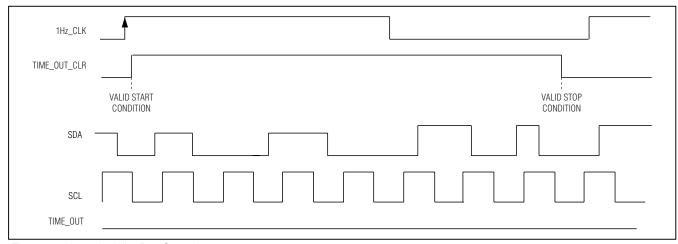

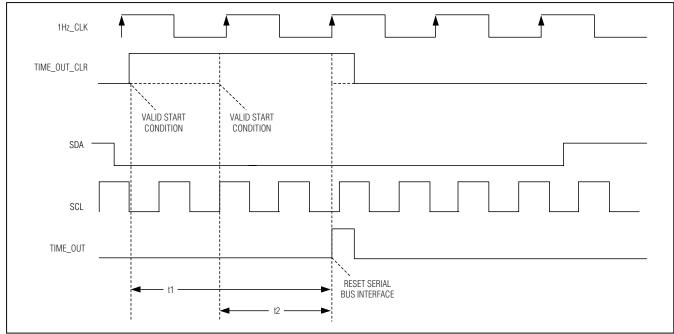

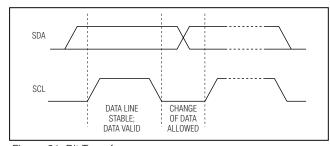

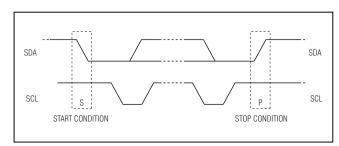

| 2-Wire Bus Data I/O                                                         | 12      | SDA          | Enabled     | Disabled                              |                                                |                          |