# STF202-22T1G

# USB Filter with ESD Protection

This device is designed for applications requiring **Line Termination**, **EMI Filtering** and **ESD Protection**. It is intended for use in upstream USB ports, Cellular phones, Wireless equipment and computer applications. This device offers an integrated solution in a small package (TSOP–6, Case 318G) reducing PCB space and cost.

#### Features:

- Provides USB Line Termination, Filtering and ESD Protection

- Single IC Offers Cost Savings by Replacing 3 Resistors,

2 Capacitors, and 5 TVs diodes

- Bi-directional EMI Filtering Prevents Noise from Entering/Leaving the System

- IEC61000-4-2 ESD Protection for USB Port

- Flexible Pull-down or Pull-up Line Termination to Meet USB 1.1

Low Speed and High Speed Specification

- ESD Ratings: Machine Model = C Human Body Model = 3B

- This is a Pb-Free Device

#### Benefits:

- TSOP-6 Package Minimizes PCB Space

- Integrated Circuit Increases System Reliability versus Discrete Component Implementation

- TVs Devices Provide ESD Protection That is Better than a Discrete Implementation because the Small IC minimizes Parasitic Inductances

#### **Typical Applications:**

- USB Hubs

- Computer Peripherals Using USB

#### MAXIMUM RATINGS (T<sub>A</sub> = 25°C)

| Rating                                          | Symbol              | Value       | Unit |

|-------------------------------------------------|---------------------|-------------|------|

| Steady State Power                              | $P_{D}$             | 225         | mW   |

| Maximum Junction Temperature                    | T <sub>J(max)</sub> | 125         | °C   |

| Operating Temperature Range                     | $T_J$               | -55 to +125 | °C   |

| Storage Temperature Range                       | T <sub>stg</sub>    | -55 to +125 | °C   |

| Lead Solder Temperature<br>(10 second duration) | TL                  | 260         | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

### ON Semiconductor®

http://onsemi.com

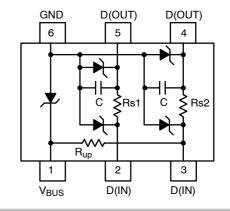

#### **CIRCUIT DESCRIPTION**

TSOP-6 CASE 318G STYLE 8

#### **MARKING DIAGRAM**

S22 = Specific Device Code

M = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

| Device       | Device Package      |                  |

|--------------|---------------------|------------------|

| STF202-22T1G | TSOP-6<br>(Pb-Free) | 3000/Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

#### STF202-22T1G

#### **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25°C)

|              |                   |                             | 1 n | Max I <sub>R</sub> @ V <sub>RWM</sub> = 5.25 V V <sub>BUS</sub> to |             | Max I <sub>R</sub><br>@ V <sub>RWM</sub><br>= 3.3 V | Typical Line<br>Capacitance  |     | es Resi<br>Ω) (Not |     |      | up Res<br>R <sub>up</sub> (kΩ |      |

|--------------|-------------------|-----------------------------|-----|--------------------------------------------------------------------|-------------|-----------------------------------------------------|------------------------------|-----|--------------------|-----|------|-------------------------------|------|

| Device       | Device<br>Marking | V <sub>RWM</sub><br>(Volts) | Min | Max                                                                | GND<br>(μA) | l/O Pin<br>(μA)                                     | ( <b>pF)</b><br>(Notes 2, 3) | Min | Nom                | Max | Min  | Nom                           | Max  |

| STF202-22T1G | S22               | 5.25                        | 6.0 | 8.0                                                                | 5.0         | 1.0                                                 | 68                           | 20  | 22                 | 24  | 1.35 | 1.5                           | 1.65 |

- 1. For other  $R_S$  values (i.e.  $R_S$  = 30  $\Omega$ ) contact your local ON Semiconductor sales representative. 2. Measured at 25°C,  $V_R$  = 0 V, f = 1 MHz, Pins 2, 3, 4 or 5 to GND with Pin 1 also grounded. 3. For other capacitance values contact your local ON Semiconductor sales representative.

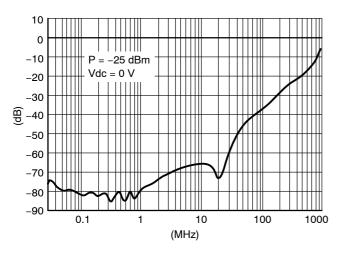

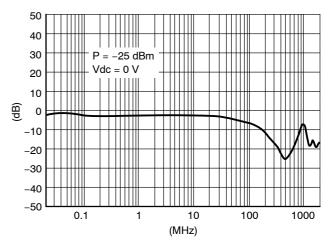

#### **TYPICAL CHARACTERISTICS**

Figure 1. Analog Cross-talk (D+ to D-)

Figure 2. Insertion Loss Characteristics

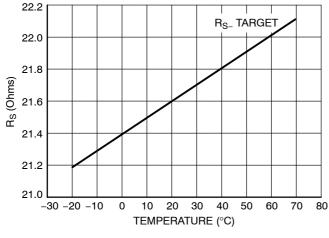

Figure 3. R<sub>S</sub> versus Temperature

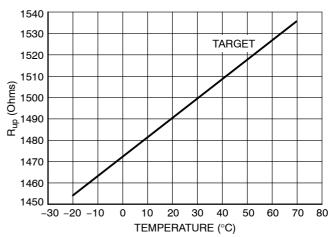

Figure 4. R<sub>up</sub> versus Temperature

#### STF202-22T1G

#### APPLICATIONS BACKGROUND

#### What Is USB?

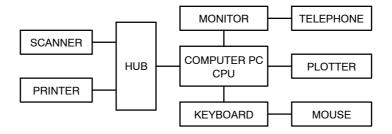

The USB is not a serial port, it is a serial bus, a fact that enables a single port on the computer to be a link for a myriad of devices, (up to 127 devices in a USB system). We can easily chain one device to another and use one port as a connecting point of many devices by using a hub. All these enables us to look at the USB system as a small network of devices.

The Universal Serial Bus (USB) makes connecting devices to your computer faster, easier and virtually limitless. High-Speed USB devices are capable of communicating at speeds up to 12 megabits without shutting down and without having to open your computer.

Figure 5. Typical USB System

Typically the USB system consists of one host, hubs and devices.

The Host in the USB system, is responsible to the whole complexity of the protocol (simplifies the designing of USB devices). The host controls the media access, therefore, no one can access the bus unless it got an approval required from the host.

The Hub provides an interconnect point, which enables many devices to connect to a single USB port. The logical topology of the USB is a star structure, all the devices are connected (logically) directly to the host. It is totally transparent to the device what is its hub tier (the number of hubs the data has to flow through). The hub is connected to the USB host in the upstream direction (data flows "up" to the host) and is connected to the USB device in the downstream direction (data flows "down" from the host to the device). The hub's main functionality is the responsibility of detecting an attachment and detachment of devices, handling the power management for devices that are bus-powered (get power from the bus), and responsibility for bus error detection and recovery. Another important role of the hub is to manage both full and low speed devices. When a device is attached to the system the hub detects the speed, which the device operates in, and through the whole communication on the bus prevents from full speed traffic to reach low speed device and vice versa – prevent from low speed traffic to reach full speed device.

**The Device** is defined as everything in the USB system, which is not a host (including hubs). A device provides one

or more USB functions. Most of the devices provide only one function but there may be some, which provides more than one and called compound devices. We refer to two kinds of devices – self powered or bus powered devices. A device that gets its power from the bus is called bus powered and on the other hand a device which supplies its own power is called self powered. There are two kinds of devices:

Full-speed devices - operates in 12 Mb/s

Low-speed devices that work in 1.5 Mb/s

#### **STF202 Device Information**

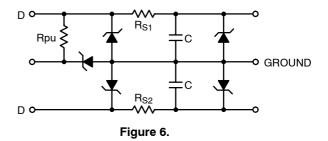

The Universal Serial Bus (USB) specification revision 1.1 requires EMI Filtering and line termination for the USB I/O lines. **The STF202** device from ON Semiconductor provides upstream termination, EMI Filtering and ESD Protection to IEC61000–4–2 (Level 4) in an integrated solution placed in a small and single package (TSOP–6, Case 318G). The equivalent circuit of this device is shown in the Figure 6.

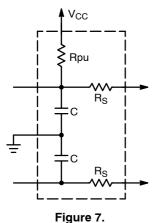

As previously mentioned, there are two types of configurations for the USB port which are upstream and downstream. If your port connects to the host either in a direct way or through a hub, you are upstream (data flows "up" to the host) and in the other hand, if you are the host or your port provides access to the host then you are downstream (data flows "down" from the host to the device). In the case of the STF202 device, it provides upstream termination. The Figure 7 represents the termination for an upstream USB port.

The USB Line termination is reached through the series

resistors placed in the D+ and D- lines. These resistors insure the proper termination to maintain the integrity of the signal. The Pull up Resistor of 1.5 k $\Omega$  on either the D+ or D- data lines is used to identify the equipment as either full-speed or low-speed device.

# Connection for Full-Speed and Low-Speed Devices

As mentioned before, there are two kinds of port devices:

Full-Speed devices - operates in 12 Mb/s

Low-Speed devices that work in 1.5 Mb/s

The STF202 device can be shaped to be used for either Full-Speed or Low-Speed devices which is achieved as described below:

#### **Full-Speed Devices**

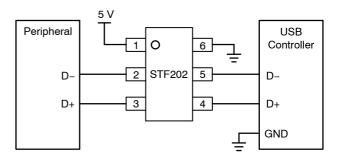

The Pull up resistor (Rpu) is connected to the D+ Line. The terminal 1 is connected to the Voltage Supply Line ( $V_{BUS}$ ) while the terminal 6 is connected to ground. The input of the D+ line is connected in the terminal 3 which outputs from the terminal 4. Finally, the input of the D- line is connected in the terminal 2 which outputs from the terminal 5. The Figure 8 shows the connections of the STF202 device for "Full–Speed devices".

Figure 8.

#### Low-Speed Devices

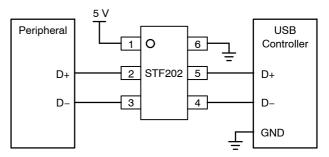

The Pull up resistor (Rpu) is connected to the D– Line. The terminal 1 is connected to the Voltage Supply Line ( $V_{BUS}$ ) while the terminal 6 is connected to ground. The input of the D– line is connected in the terminal 3 which outputs from the terminal 4. Finally, the input of the D+ line is connected in the terminal 2 which outputs from the terminal 5. The Figure 9 shows the connections of the STF202 device for "Low–Speed devices".

Figure 9.

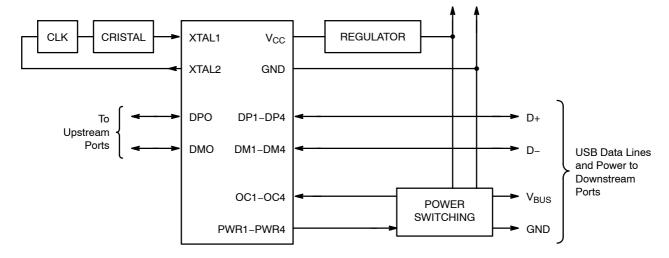

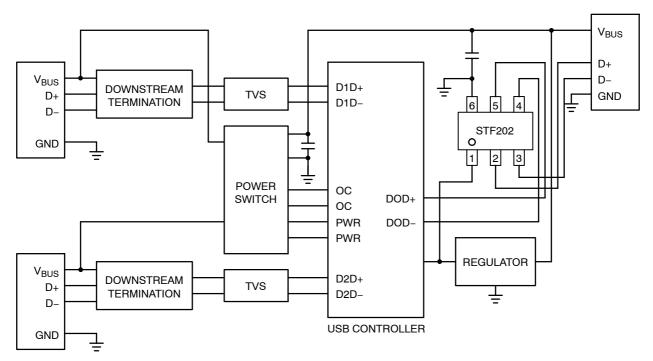

The Figure 10 describes in a simplified way what the USB port components are. As shown in this diagram, there are signals for upstream and downstream ports which must be provided with Line Termination and EMI Filtering to meet the requirements of the USB specification revision 1.1. In

addition to the Line termination and EMI Filtering, it is also needed to protect the USB I/O Lines against ESD conditions, so TVS devices must be added for these purposes.

Figure 10.

As mentioned before, **the ON Semiconductor STF202 device** provides "upstream termination", EMI Filtering and ESD Protection to IEC61000-4-2 in an integrated solution

placed in a small and single package (TSOP-6, Case 318G). The typical application for the STF202 device is shown in the Figure 11.

Figure 11.

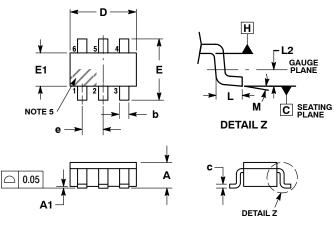

#### TSOP-6 CASE 318G-02 ISSUE V

**DATE 12 JUN 2012**

STYLE 6: PIN 1. COLLECTOR 2. COLLECTOR

3. BASE 4. EMITTER 5. COLLECTOR 6. COLLECTOR

STYLE 12: PIN 1. I/O 2. GROUND 3. I/O 4. I/O 5. VCC 6. I/O

#### NOTES:

- OTLO.

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM

- 3. MAXIMUM LEAD I HICKNESS INCLUDES LEAD FINISH, MINIMUM LEAD FILICKNESS OF BASE MATERIAL.

4. DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS, MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSIONS D AND E1 ARE DETERMINED AT DATUM H.

5. PIN ONE INDICATOR MUST BE LOCATED IN THE INDICATED ZONE.

|     | MILLIMETERS |      |      |  |  |  |

|-----|-------------|------|------|--|--|--|

| DIM | MIN         | NOM  | MAX  |  |  |  |

| Α   | 0.90        | 1.00 | 1.10 |  |  |  |

| A1  | 0.01        | 0.06 | 0.10 |  |  |  |

| b   | 0.25        | 0.38 | 0.50 |  |  |  |

| С   | 0.10        | 0.18 | 0.26 |  |  |  |

| D   | 2.90        | 3.00 | 3.10 |  |  |  |

| Е   | 2.50        | 2.75 | 3.00 |  |  |  |

| E1  | 1.30        | 1.50 | 1.70 |  |  |  |

| е   | 0.85        | 0.95 | 1.05 |  |  |  |

| L   | 0.20        | 0.40 | 0.60 |  |  |  |

| L2  | 0.25 BSC    |      |      |  |  |  |

| М   | Uo.         |      | 10°  |  |  |  |

| STYLE 1:<br>PIN 1. DRAIN<br>2. DRAIN<br>3. GATE<br>4. SOURCE<br>5. DRAIN<br>6. DRAIN            | STYLE 2:<br>PIN 1. EMITTER 2<br>2. BASE 1<br>3. COLLECTOR 1<br>4. EMITTER 1<br>5. BASE 2<br>6. COLLECTOR 2 | STYLE 3: PIN 1. ENABLE 2. N/C 3. R BOOST 4. Vz 5. V in 6. V out                            | STYLE 4:<br>PIN 1. N/C<br>2. V in<br>3. NOT USED<br>4. GROUND<br>5. ENABLE<br>6. LOAD    | STYLE 5: PIN 1. EMITTER 2 2. BASE 2 3. COLLECTOR 1 4. EMITTER 1 5. BASE 1 6. COLLECTOR 2 |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| STYLE 7:<br>PIN 1. COLLECTOR<br>2. COLLECTOR<br>3. BASE<br>4. N/C<br>5. COLLECTOR<br>6. EMITTER | STYLE 8: PIN 1. Vbus 2. D(in) 3. D(in)+ 4. D(out)+ 5. D(out) 6. GND                                        | STYLE 9: PIN 1. LOW VOLTAGE GATE 2. DRAIN 3. SOURCE 4. DRAIN 5. DRAIN 6. HIGH VOLTAGE GATE | STYLE 10:<br>PIN 1. D(OUT)+<br>2. GND<br>3. D(OUT)-<br>4. D(IN)-<br>5. VBUS<br>6. D(IN)+ | STYLE 11: PIN 1. SOURCE 1 2. DRAIN 2 3. DRAIN 2 4. SOURCE 2 5. GATE 1 6. DRAIN 1/GATE 2  |

| CTVLE 10:                                                                                       | CTVLE 14:                                                                                                  | CTVLE 15. CTVL                                                                             | E 16.                                                                                    | OTVLE 17.                                                                                |

| 6. EMITTER                                                                      | 6. GND                                                                                      | 6. HIGH VOLTAC                                                                        | GE GATE 6. D(IN)+                                                                  | 6. DRAIN 1/GATE 2                                                                  |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| STYLE 13: PIN 1. GATE 1 2. SOURCE 2 3. GATE 2 4. DRAIN 2 5. SOURCE 1 6. DRAIN 1 | STYLE 14: PIN 1. ANODE 2. SOURCE 3. GATE 4. CATHODE/DRAIN 5. CATHODE/DRAIN 6. CATHODE/DRAIN | STYLE 15:<br>PIN 1. ANODE<br>2. SOURCE<br>3. GATE<br>4. DRAIN<br>5. N/C<br>6. CATHODE | STYLE 16: PIN 1. ANODE/CATHODE 2. BASE 3. EMITTER 4. COLLECTOR 5. ANODE 6. CATHODE | STYLE 17: PIN 1. EMITTER 2. BASE 3. ANODE/CATHODE 4. ANODE 5. CATHODE 6. COLLECTOR |

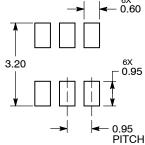

## **RECOMMENDED SOLDERING FOOTPRINT\***

**DIMENSIONS: MILLIMETERS**

# **GENERIC MARKING DIAGRAM\***

XXX = Specific Device Code

= Pb-Free Package

= Date Code

XXX = Specific Device Code =Assembly Location Α

Υ = Year

= Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

M

| DOCUMENT NUMBER: | 98ASB14888C | Electronic versions are uncontrolled except when accessed directly from the Document Repos<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | TSOP-6      |                                                                                                                                                                               | PAGE 1 OF 1 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales