© 1995 National Semiconductor Corporation TL/H/5118

RRD-B30M115/Printed in U. S. A.

| Absolute Maxim                    | num Ratings                                                    |                                                     |                 |

|-----------------------------------|----------------------------------------------------------------|-----------------------------------------------------|-----------------|

| , ,                               | pecified devices are required,<br>lational Semiconductor Sales | Operating Temperature Range<br>(Ambient)            | -25°C to +125°C |

| Office/Distributors for a         | vailability and specifications.                                | Storage Temperature Range                           |                 |

| V <sub>CC</sub> Relative to GND   | 7V                                                             | (Ambient)                                           | -65°C to +150°C |

| Voltage at Any Input<br>or Output | $V_{CC}$ + 0.3V to GND -0.3V                                   | Maximum Lead Temperature<br>(Soldering, 10 seconds) | 300°C           |

|                                   |                                                                | ESD rating to be determined.                        |                 |

# **DC Electrical Characteristics**

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{CC} = 5.0V \pm 5\%$ ;  $T_A = 0^\circ C$  to  $+70^\circ C$  by correlation with 100% electrical testing at  $T_A = 25^\circ C$ . All other limits are assured by correlation with other production tests and/ or product design and characterization. Typicals specified at  $V_{CC} = 5.0V$ ,  $T_A = 25^\circ C$ .

| Parameter                    | Conditions                                         | Min   | Тур | Max | Units |

|------------------------------|----------------------------------------------------|-------|-----|-----|-------|

| Input Voltage Levels         |                                                    |       |     |     |       |

| V <sub>IH</sub> , Logic High |                                                    | 2.0   |     |     | V     |

| V <sub>IL</sub> , Logic Low  |                                                    |       |     | 0.7 | V     |

| Input Currents               |                                                    |       |     |     |       |

| All Inputs Except MODE       | $V_{IL} < V_{IN} < V_{IH}$                         | - 1   |     | 1   | μA    |

| MODE                         | $V_{IN} = 0V$                                      | - 100 |     |     | μA    |

| Output Voltage Levels        |                                                    |       |     |     |       |

| V <sub>OH</sub> , Logic High | $FS_X$ and $FS_R$ Outputs, $I_{OH} = 3 \text{ mA}$ | 2.4   |     |     | V     |

| V <sub>OL</sub> , Logic Low  | $FS_X$ and $FS_R$ Outputs, $I_{OL} = 5 \text{ mA}$ |       |     | 0.4 | V     |

|                              | $TS_X Output, I_{OL} = 5 mA$                       |       |     | 0.4 | V     |

| Power Dissipation            | BCLK = 2.048 MHz,                                  |       | 1   | 1.5 | mA    |

| Operating Current            | All Outputs Open-Circuit                           |       |     |     |       |

# **Timing Specifications**

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for V<sub>CC</sub> = 5.0V ±5%, T<sub>A</sub> = 0°C to +70°C by correlation with 100% electrical testing at T<sub>A</sub> = 25°C. All other limits are assured by correlation with other production tests and/ or product design and characterization. Typicals specified at V<sub>CC</sub> = 5.0V, T<sub>A</sub> = 25°C. All timing parameters are measured at V<sub>OH</sub> = 2.0V and V<sub>OL</sub> = 0.7V.

See Definitions and Timing Conventions section for test methods information.

| Symbol                            | Parameter                                                        | Conditions                    | Min | Max | Units |

|-----------------------------------|------------------------------------------------------------------|-------------------------------|-----|-----|-------|

| t <sub>PC</sub>                   | Period of Clock                                                  | BCLK, CLK <sub>C</sub>        | 480 |     | ns    |

| twcH                              | Width of Clock High                                              | BCLK, CLK <sub>C</sub>        | 160 |     | ns    |

| t <sub>WCL</sub>                  | Width of Clock Low                                               | BCLK, CLK <sub>C</sub>        | 160 |     | ns    |

| t <sub>SDC</sub>                  | Set-Up Time from $D_C$ to $CLK_C$                                |                               | 50  |     | ns    |

| t <sub>HCD</sub>                  | Hold Time from $CLK_C$ to $D_C$                                  |                               | 50  |     | ns    |

| t <sub>SCC</sub>                  | Set-Up Time from $\overline{CS}$ to $CLK_C$                      |                               | 30  |     | ns    |

| tHCC                              | Hold Time from $CLK_C$ to $\overline{CS}$                        |                               | 100 |     | ns    |

| t <sub>SCHC</sub>                 | Set-Up Time from Channel Select to $CLK_C$                       |                               | 50  |     | ns    |

| t <sub>HCHC</sub>                 | Hold Time from Channel Select to CLK <sub>C</sub>                |                               | 50  |     | ns    |

| t <sub>DBF</sub>                  | Delay Time from BCLK Low to FS <sub>X/R</sub> 0–3<br>High or Low | $C_L = 50  pF$                |     | 100 | ns    |

| t <sub>HSYNC</sub>                | Hold Time from BCLK to Frame Sync                                |                               | 50  |     | ns    |

| tSSYNC                            | Set-Up Time from Frame Sync to BCLK                              |                               | 100 |     | ns    |

| t <sub>DTL</sub>                  | Delay to TS <sub>X</sub> Low                                     | $C_L = 50 \text{ pF}$         |     | 140 | ns    |

| t <sub>DTH</sub>                  | Delay to TS <sub>X</sub> High                                    | $R_L = 1k \text{ to } V_{CC}$ | 30  | 140 | ns    |

| t <sub>RC</sub> , t <sub>FC</sub> | Rise and Fall Time of Clock                                      | BCLK, CLK <sub>C</sub>        |     | 50  | ns    |

## **Functional Description**

### **OPERATING MODES**

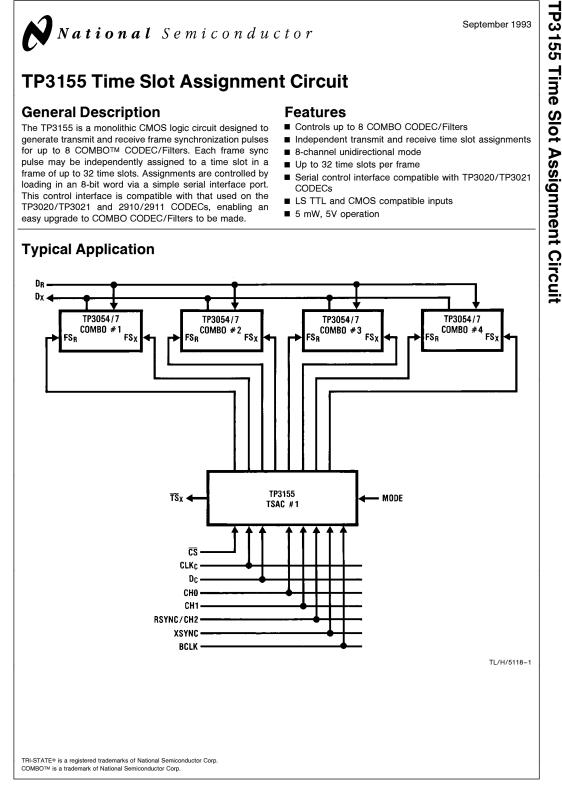

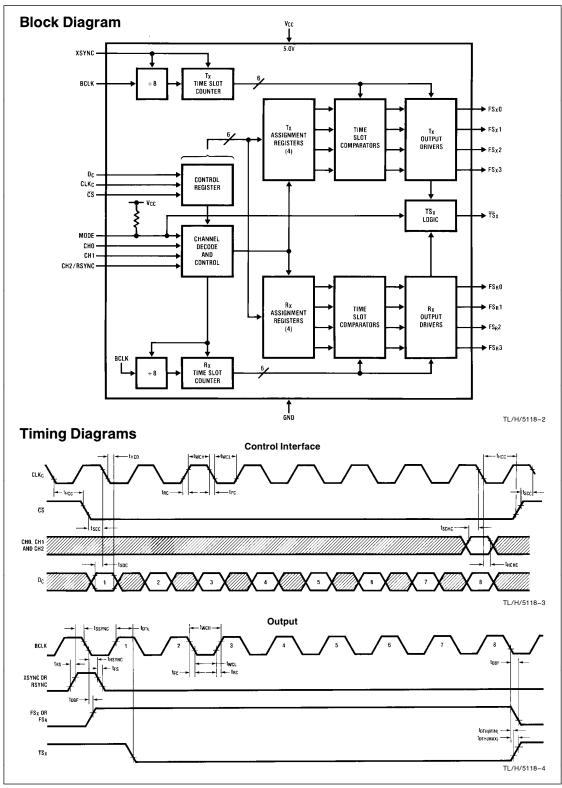

The TP3155 control interface requires an 8-bit serial control word which is compatible with the TP3020/TP3021 and 2910/2911 CODECs. Two bits,  $\overline{X}$  and  $\overline{R}$ , define which of the two groups of frame sync outputs,  $FS_X0$  to  $FS_R3$ , is affected by the control word, and a 6-bit assignment field specifies the selected time slot, from 0 to 31. A frame sync output is active-high for one time slot, which is always 8 cycles of BCLK. A frame may consist of any number of time slots up to 32. If a timeslot is assigned which is beyond the number of time slots in a frame, the FS\_R or FS\_R

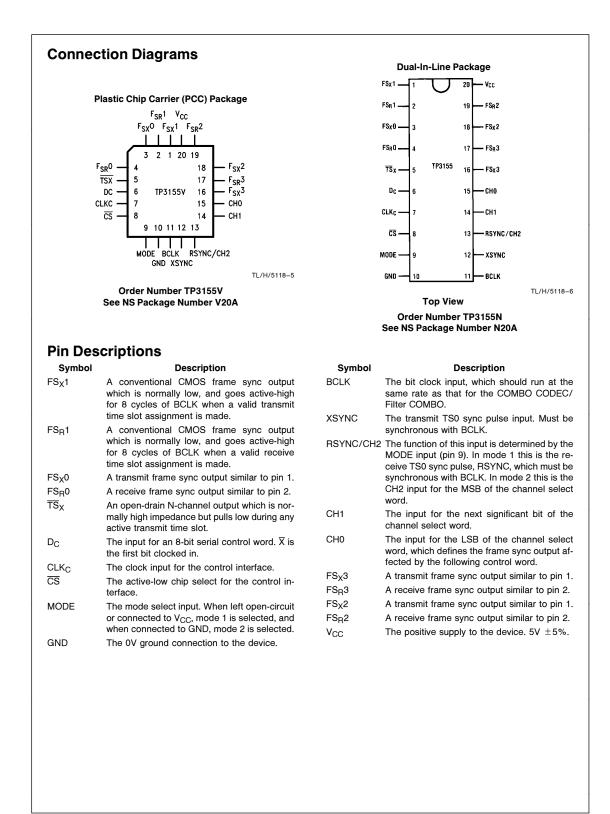

Two modes of operation are available. Mode 1 is for systems requiring different time slot assignments for the transmit and receive direction of each channel. Mode 1 is selected by leaving pin 9 (MODE) open-circuit or connecting it to V<sub>CC</sub>. In this case, Pin 13 is the RSYNC input which defines the start of each receive frame, and the four outputs, FS<sub>R</sub>0–FS<sub>R</sub>3, are assigned with respect to RSYNC. The XSYNC input defines the start of each transmit frame and outputs FS<sub>X</sub>0–FS<sub>X</sub>3 are assigned with respect to XSYNC. XSYNC may have any phase relationship with RSYNC. Inputs CH0 and CH1 select the channel, from 0 to 3 (see Table Ia).

Mode 2 provides the option of assigning all 8 frame sync outputs with respect to the XSYNC input. Mode 2 is selected by connecting pin 9 (MODE) to GND. This makes the TP3155 TSAC useful for either an 8-channel undirectional controller or for systems in which the transmit and receive directions of each channel are always assigned to the same time slot as the other, i.e., the FS<sub>X</sub> and FS<sub>R</sub> inputs on the COMBO CODEC/Filter are hard-wired together. In this case, logical selection of the channel to be assigned is made via inputs CH0, CH1 and CH2 (see Table Ib).

#### **POWER-UP INITIALIZATION**

During power-up, all frame sync outputs,  $FS_X0-FS_X3$  and  $FS_R0-FS_R3$ , are inhibited and held low. No outputs will go active until a valid time slot assignment is made.

### LOADING CONTROL DATA

During the loading of control data, the binary code for the selected channel must be set on inputs CH0 and CH1 (and CH2 in mode 2), see Tables Ia and Ib.

Control data is clocked into the  $\mathsf{D}_C$  input on the falling edges of  $\mathsf{CLK}_C$  while  $\overline{\mathsf{CS}}$  is low.

A new time slot assignment is transferred to the selected assignment register on the high going transition of  $\overline{\text{CS}}$ . The new assignment is re-synchronized to the system clock such that the new FS output pulses will start at the next complete valid time slot after the rising edge of  $\overline{\text{CS}}$ .

### TIME SLOT COUNTER OPERATION

At the start of TS0 of each transmit frame, defined by the first falling edge of BCLK after XSYNC goes high, the transmit time slot counter is reset to 000000 and begins to increment once every 8 cycles of BCLK. Each count is compared with the 4 transmit assignment registers and, on finding a match, a frame sync pulse is generated at that FS<sub>X</sub> output. Similarly, the first falling edge of BCLK after RSYNC goes high defines the start of receive TS0, and outputs FS<sub>R</sub>0–FS<sub>R</sub>3 are generated with respect to TS0 when the receive time slot counter matches the appropriate receive assignment register.

### TS<sub>X</sub> OUTPUT

In mode 1 (separate transmit and receive assignments), this output pulls low whenever any FS<sub>X</sub> output pulse is being generated. In mode 2, this output pulls low whenever any FS<sub>X</sub> or FS<sub>R</sub> output is being generated. At all other times it is open-circuit, allowing the TS<sub>X</sub> outputs of a number of TSACS to be wire-ANDed together with a common pull-up resistor. This signal can be used to control the TRI-STATE® enable input of a line driver to buffer the transmit PCM bus from the CODEC/Filters to the backplane.

|         |         |        | (     | TABL      | E la. C<br>)/TP30               |        |      |                     | e)                 |                   |

|---------|---------|--------|-------|-----------|---------------------------------|--------|------|---------------------|--------------------|-------------------|

| X       |         | R      |       | T5        | T4                              | Т3     |      | T2                  | T1                 | T0                |

| X is th | ne firs | st bil | t clo | cked into | the D <sub>C</sub> i<br>ntrol D |        | ori  | nat                 |                    |                   |

| Т5      | ;       | T      | 4     | Т3        | T2                              | T      | 1    | то                  | Time               | e Slot            |

| 0       |         | 0      |       | 0         | 0                               | 0      |      | 0                   |                    | 0                 |

| 0       |         | 0      |       | 0         | 0                               | 0      |      | 1                   |                    | 1                 |

| 0       |         | 0      |       | 0         | 0                               | 1      |      | 0                   |                    | 2                 |

|         |         |        |       |           |                                 |        |      |                     |                    | :                 |

| 0       |         | 1      |       | 1         | 1                               | 1      |      | 0                   | 3                  | 30                |

| 0       |         | 1      | 1     | 1         | 1                               | 1      |      | 1                   |                    | 31                |

| 1       |         | Х      |       | Х         | Х                               | X      |      | Х                   | (No                | te 1)             |

| c       | H1      |        |       | СНО       |                                 | С      | haı  | nnel Se             | lected             |                   |

|         | 0       |        |       | 0         | A                               | ssign  | to   | FS <sub>x</sub> 0 a | nd/or F            | S <sub>R</sub> 0  |

|         | 0       |        |       | 1         | A                               | ssign  | to   | FS <sub>x</sub> 1 a | nd/or F            | S <sub>R</sub> 1  |

|         | 1       |        |       | 0         | A                               | ssign  | to   | FS <sub>x</sub> 2 a | nd/or F            | S <sub>R</sub> 2  |

|         | 1       |        |       | 1         | A                               | ssign  | to   | FS <sub>x</sub> 3 a | nd/or F            | S <sub>R</sub> 3  |

| X       | R       |        |       |           |                                 | Ac     | tio  | n                   |                    |                   |

| 0       | 0       |        | As    | sign tim  | e slot t                        | o bot  | h s  | elected             | FS <sub>X</sub> an | d FS <sub>R</sub> |

| 0       | 1       |        | As    | sign tim  | e slot t                        | o sele | ecte | ed FS <sub>X</sub>  | only               |                   |

| 1       | 0       |        | As    | sign tim  | e slot t                        | o sele | ecte | ed FS <sub>R</sub>  | only               |                   |

| 1       | 1       |        | Dis   | sable bo  | th sele                         | cted   | FS   | <sub>X</sub> and F  | S <sub>R</sub>     |                   |

|         |         |        |       | TABL      | E Ib. C                         | ontro  | ol N | lode 2              |                    |                   |

| с       | H2      |        |       | CH1       | СН                              | 10     |      | Chann               | el Sele            | cted              |

|         | 0       |        |       | 0         | 0                               |        |      | Assic               | n to FS            | ×0                |

|         | 0       |        |       | 0         | 1                               |        |      |                     | n to FS            | ~                 |

|         | 0       |        |       | 1         | 0                               |        |      | -                   | n to FS            |                   |

|         | 0       |        |       | 1         | 1                               |        |      | -                   | ,<br>gn to FS      |                   |

|         | 1       |        |       | 0         | 0                               |        |      | Assig               | ,<br>In to FS      | R0                |

|         | 1       |        |       | 0         | 1                               |        |      | Assic               | n to FS            | в1                |

| x | R |   | 4 | Action                      |

|---|---|---|---|-----------------------------|

|   |   |   |   |                             |

| 1 |   | 1 | 1 | Assign to FS <sub>R</sub> 3 |

| 1 |   | 1 | 0 | Assign to FS <sub>R</sub> 2 |

| 1 |   | 0 | 1 | Assign to FS <sub>R</sub> 1 |

| 1 |   | 0 | 0 | Assign to FS <sub>R</sub> 0 |

| 0 |   | 1 | 1 | Assign to FS <sub>X</sub> 3 |

| 0 |   | 1 | 0 | Assign to FS <sub>X</sub> 2 |

|   |   |   |   |                             |

| 0 | 0 | 1                                   |

|---|---|-------------------------------------|

| 0 | 1 | Assign time slot to selected output |

| 1 | 0 | J                                   |

| 1 | 1 | Disable selected output             |

Note 1: When T5 = 1, then the appropriate  $FS_X$  or  $FS_R$  output is inactive.

| al test at reduced clock speeds and<br>nominal timing, (i.e. not minimum setup<br>and hold times or output strobes), with<br>the high level of all driving signals set<br>to V <sub>IH</sub> and maximum supply voltages<br>applied to the device.VILVIL is the d.c. input level below which<br>an input level is guaranteed to appear<br>as a logical zero to the device. This pa-<br>rameter is measured in the same man-<br>ner as V <sub>IH</sub> but with all driving signal low<br>levels set to V <sub>IL</sub> and minimum supply<br>voltages applied to the device.VOHVOH<br>woltages applied to the device.VOHVOH is the minimum d.c. output level to<br>which an output placed in a logical one<br>state will converge when loaded at the<br>maximum specified load current.VOLVOL<br>woltages between VIL<br>and VIL.VILThe threshold region is the range of in-<br>put voltages between VIL<br>and VIH.Valid SignalA signal is Valid if it is in one of the valid<br>logic states.Invalid SignalA signal is Invalid if it is not in a valid                                                                                                                                                                                                                                                                                                                                                                                     | all Time<br>Pulse Width High<br>Pulse Width Low<br>Setup Time | $t_{WZZH}$ , where zz represents the minimum of the input or output signs whose pulse width is being specifier High pulse widths are measured from $V_{IH}$ to $V_{IH}$ .<br>The low pulse width is designated at $t_{WZZL}$ , where zz represents the minimum of the input or output signs whose pulse width is being specified. Low pulse width are measured from $V_{IL}$ to $V_{IL}$ .<br>Setup times are designated as $t_{SWWX}$ where ww represents the minimum of the input or output signs whose input represented by minimum is being specified relative to a clock of strobe input represented by minimum X. Setup times are designated as $t_{HXWW}$ where we represents the minimum from the ww Valid to xx Invalid.<br>Hold times are designated as $t_{HXWW}$ where we represent the minimum of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| be measured by performing a function-<br>al test at reduced clock speeds and<br>nominal timing, (i.e. not minimum setup<br>and hold times or output strobes), with<br>the high level of all driving signals set<br>to VIH and maximum supply voltages<br>applied to the device.VILVIL is the d.c. input level below which<br>an input level is guaranteed to appear<br>as a logical zero to the device. This pa-<br>rameter is measured in the same man-<br>ner as VIH but with all driving signal low<br>levels set to VIL and minimum supply<br>voltages applied to the device.VOHVOH is the minimum d.c. output level to<br>which an output placed in a logical one<br>state will converge when loaded at the<br>maximum specified load current.VOLVOL is the maximum d.c. output level to<br>which an output placed in a logical zero<br>state will converge when loaded at the<br>maximum specified load current.VOLVOL is the maximum d.c. output level to<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pulse Width High<br>Pulse Width Low                           | Fall times are designated as $t_{FY}$ where yy represents a mnemonic of the signal whose fall time is being specified. $t_{FYY}$ is measured from $V_{IH}$ to $V_{IL}$ .<br>The high pulse width is designated at $t_{WZZH}$ , where zz represents the mnemonic of the input or output signal whose pulse width is being specified. High pulse widths are measured from $V_{IH}$ to $V_{IH}$ .<br>The low pulse width is designated at $t_{WZZL}$ , where zz represents the mnemonic of the input or output signal whose pulse width is being specified. Low pulse width is being specified. Low pulse widths are measured from $V_{IL}$ to $V_{IL}$ .<br>Setup times are designated as $t_{SWXX}$ where ww represents the mnemonic of the input signal whose setup time is being specified relative to a clock of strobe input represented by mnemonix x. Setup times are designated as $t_{HXXW}$ where ww represents the mnemonic of the input signal whose hold time is being specified relative to a clock of strobe input represents the mnemonic of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative t                                                                     |

| to V <sub>IH</sub> and maximum supply voltages<br>applied to the device.VILVIL is the d.c. input level below which<br>an input level is guaranteed to appear<br>as a logical zero to the device. This pa-<br>rameter is measured in the same man-<br>ner as VIH but with all driving signal low<br>levels set to VIL and minimum supply<br>voltages applied to the device.VOHVOH is the minimum d.c. output level to<br>which an output placed in a logical one<br>state will converge when loaded at the<br>maximum specified load current.VOLVOL is the maximum d.c. output level to<br>which an output placed in a logical zero<br>state will converge when loaded at the<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pulse Width Low                                               | <ul> <li>The high pulse width is designated at t<sub>WZZH</sub>, where zz represents the moment of the input or output signated at t<sub>WZZH</sub>, where zz represents the moment of the input or output signated at t<sub>WZZL</sub>, where zz represents the moment of the input or output signated at t<sub>WZZL</sub>, where zz represents the moment of the input or output signated as t<sub>WZZL</sub>, where zz represents the moment of the input or output signated as t<sub>WZZL</sub>. Setup times are designated as t<sub>SWWX</sub> where ww represents the moment of the input signal whose setup time is being specified relative to a clock of strobe input represented by mnemoni xx. Setup times are designated as t<sub>HXXW</sub> where ww represents the moment of the input signal whose hold time is being specified relative to a clock of strobe input represents the moment of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is being specified relative to a clock of the input signal whose hold time is be</li></ul> |

| an input level is guaranteed to appear<br>as a logical zero to the device. This pa-<br>rameter is measured in the same man-<br>ner as $V_{IH}$ but with all driving signal low<br>levels set to $V_{IL}$ and minimum supply<br>voltages applied to the device.<br>$V_{OH}$ $V_{OH}$ is the minimum d.c. output level to<br>which an output placed in a logical one<br>state will converge when loaded at the<br>maximum specified load current.<br>$V_{OL}$ $V_{OL}$ is the maximum d.c. output level to<br>which an output placed in a logical zero<br>state will converge when loaded at the<br>maximum specified load current.<br>Threshold Region The threshold region is the range of in-<br>put voltages between $V_{IL}$ and $V_{IH}$ . He<br>Valid Signal A signal is Valid if it is in one of the valid<br>logic states, (i.e. above $V_{IH}$ or below<br>$V_{IL}$ ). In timing specifications, a signal is<br>deemed valid at the instant it enters a<br>valid state.<br>Invalid Signal A signal is Invalid if it is not in a valid<br>logic state, i.e. when it is in the thresh-<br>old region between $V_{IL}$ and $V_{IH}$ . In tim-<br>ing specifications, a signal is deemed<br>Invalid at the instant it enters the<br>threshold region.<br><b>TIMING CONVENTIONS</b><br>For the purposes of this timing specification the following<br>conventions apply:                                                                  | Setup Time                                                    | <ul> <li>whose pulse width is being specified High pulse widths are measured from VIH to VIH.</li> <li>The low pulse width is designated at t<sub>WzzL</sub>, where zz represents the mmonic of the input or output sign whose pulse width is being specified. Low pulse widths are measured from VIL to VIL.</li> <li>Setup times are designated as t<sub>Swwx</sub> where ww represents the mmemonic of the input signal whose setup time is being specified relative to a clock of strobe input represents the mmemonic of the input signal whose hold time is the input signal whose hold time is being specified relative to a clock of strobe input represents the mmemonic of the input signal whose hold time is the input signal whose hold time is being specified relative to a clock of strobe input represents the mmemonic of the input signal whose hold time is being specified relative to a clock of strobe input represented by mmemon xx. Hold times are measured from the input signal whose hold time is being specified relative to a clock of strobe input represented by mmemon xx. Hold times are measured from the input signal whose hold time is being specified relative to a clock of strobe input represented by mmemon xx. Hold times are measured from the input signal whose hold time is being specified relative to a clock of strobe input represented by mmemon the input signal whose hold time is being specified relative to a clock of strobe input represented by mmemon the input signal whose hold time is being specified relative to a clock of strobe input represented by mmemon the input signal whose hold time is being specified relative to a clock of strobe input represented by mmemon the input signal whose hold time is being specified relative to a clock of strobe input represented by mmemon the input signal whose hold time is being specified relative to a clock of strobe input represented by mmemon the input signal whose hold time is being specified relative to a clock of strobe input represented by mmemon the input signal whose hold time is being specified r</li></ul>                                                   |

| ner as V <sub>IH</sub> but with all driving signal low<br>levels set to V <sub>IL</sub> and minimum supply<br>voltages applied to the device.VOHV <sub>OH</sub> is the minimum d.c. output level to<br>which an output placed in a logical one<br>state will converge when loaded at the<br>maximum specified load current.VOLV <sub>OL</sub> is the maximum d.c. output level to<br>which an output placed in a logical zero<br>state will converge when loaded at the<br>maximum specified load current.VOLV <sub>OL</sub> is the maximum d.c. output level to<br>which an output placed in a logical zero<br>state will converge when loaded at the<br>maximum specified load current.Threshold RegionThe threshold region is the range of in-<br>put voltages between V <sub>IL</sub> and V <sub>IH</sub> .Valid SignalA signal is Valid if it is in one of the valid<br>logic states, (i.e. above V <sub>IH</sub> or below<br>V <sub>IL</sub> ). In timing specifications, a signal is<br>deemed valid at the instant it enters a<br>valid state.Invalid SignalA signal is Invalid if it is not in a valid<br>logic state, i.e. when it is in the thresh-<br>old region between V <sub>IL</sub> and V <sub>IH</sub> . In tim-<br>ing specifications, a signal is deemed<br>Invalid at the instant it enters the<br>threshold region.TIMING CONVENTIONSFor the purposes of this timing specification the following<br>conventions apply: | Setup Time                                                    | $t_{WzzL}$ , where zz represents the mn<br>monic of the input or output sign<br>whose pulse width is being specifie<br>Low pulse widths are measured fro<br>$V_{IL}$ to $V_{IL}$ .<br>Setup times are designated as $t_{Swww}$<br>where ww represents the mnemonic<br>the input signal whose setup time is b<br>ing specified relative to a clock<br>strobe input represented by mnemon<br>xx. Setup times are measured from th<br>ww Valid to xx Invalid.<br>Hold times are designated as $t_{Hxxw}$<br>where ww represents the mnemonic<br>the input signal whose hold time is b<br>ing specified relative to a clock<br>strobe input represented by mnemon<br>xx. Hold times are measured from xx.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>which an output placed in a logical one state will converge when loaded at the maximum specified load current.</li> <li>V<sub>OL</sub> V<sub>OL</sub> is the maximum d.c. output level to which an output placed in a logical zero state will converge when loaded at the maximum specified load current.</li> <li>Threshold Region The threshold region is the range of input voltages between V<sub>IL</sub> and V<sub>IH</sub>.</li> <li>Valid Signal A signal is Valid if it is in one of the valid logic states, (i.e. above V<sub>I</sub> or below V<sub>IL</sub>). In timing specifications, a signal is deemed valid at the instant it enters a valid state.</li> <li>Invalid Signal A signal is Invalid if it is not in a valid logic state, i.e. when it is in the threshold region between V<sub>IL</sub> and V<sub>IH</sub>. In timing specifications, a signal is deemed logic state, i.e. when it is not the threshold region.</li> <li>TIMING CONVENTIONS</li> <li>For the purposes of this timing specification the following conventions apply:</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |                                                               | $V_{IL}$ to $V_{IL}$ .<br>Setup times are designated as $t_{Swwx}$<br>where ww represents the mnemonic of<br>the input signal whose setup time is bi-<br>ing specified relative to a clock of<br>strobe input represented by mnemon<br>xx. Setup times are measured from the<br>ww Valid to xx Invalid.<br>Hold times are designated as $t_{Hxxw}$<br>where ww represents the mnemonic of<br>the input signal whose hold time is bi-<br>ing specified relative to a clock of<br>strobe input represented by mnemon<br>xx. Hold times are measured from x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VOL       V <sub>OL</sub> is the maximum d.c. output level to which an output placed in a logical zero state will converge when loaded at the maximum specified load current.         Threshold Region       The threshold region is the range of input voltages between V <sub>IL</sub> and V <sub>IH</sub> .         Valid Signal       A signal is Valid if it is in one of the valid logic states, (i.e. above V <sub>IH</sub> or below V <sub>IL</sub> ). In timing specifications, a signal is deemed valid at the instant it enters a valid state.         Invalid Signal       A signal is Invalid if it is not in a valid logic state, i.e. when it is in the threshold region between V <sub>IL</sub> and V <sub>IH</sub> . In timing specifications, a signal is deemed lnvalid at the instant it enters the threshold region.         TIMING CONVENTIONS         For the purposes of this timing specification the following conventions apply:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | lold Time                                                     | the input signal whose setup time is being specified relative to a clock strobe input represented by mnemon xx. Setup times are measured from the ww Valid to xx Invalid.<br>Hold times are designated as t <sub>Hxxw</sub> , where ww represents the mnemonic the input signal whose hold time is being specified relative to a clock strobe input represented by mnemon xx. Hold times are measured from xx.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| put voltages between V <sub>IL</sub> and V <sub>IH</sub> .       H         Valid Signal       A signal is Valid if it is in one of the valid logic states, (i.e. above V <sub>IH</sub> or below V <sub>IL</sub> ). In timing specifications, a signal is deemed valid at the instant it enters a valid state.         Invalid Signal       A signal is Invalid if it is not in a valid logic state, i.e. when it is in the threshold region between V <sub>IL</sub> and V <sub>IH</sub> . In timing specifications, a signal is deemed Invalid at the instant it enters the threshold region.         TIMING CONVENTIONS         For the purposes of this timing specification the following conventions apply:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | łold Time                                                     | Hold times are designated as t <sub>Hxxw</sub><br>where ww represents the mnemonic<br>the input signal whose hold time is b<br>ing specified relative to a clock<br>strobe input represented by mnemon<br>xx. Hold times are measured from x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| logic states, (i.e. above V <sub>IH</sub> or below V <sub>IL</sub> ). In timing specifications, a signal is deemed valid at the instant it enters a valid state.         nvalid Signal       A signal is Invalid if it is not in a valid logic state, i.e. when it is in the threshold region between V <sub>IL</sub> and V <sub>IH</sub> . In timing specifications, a signal is deemed Invalid at the instant it enters the threshold region.         TIMING CONVENTIONS         For the purposes of this timing specification the following conventions apply:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                               | the input signal whose hold time is b<br>ing specified relative to a clock<br>strobe input represented by mnemor<br>xx. Hold times are measured from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| logic state, i.e. when it is in the thresh-<br>old region between V <sub>IL</sub> and V <sub>IH</sub> . In tim-<br>ing specifications, a signal is deemed<br>Invalid at the instant it enters the<br>threshold region.<br><b>TIMING CONVENTIONS</b><br>For the purposes of this timing specification the following<br>conventions apply:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| For the purposes of this timing specification the following conventions apply:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Delay Time                                                    | Valid to ww Invalid.<br>Delay times are designated a<br>t <sub>Dxxyy[  H L]</sub> , where xx represents th<br>mnemonic of the input reference sign<br>and yy represents the mnemonic of th<br>output signal whose timing is beir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| conventions apply:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                               | specified relative to xx. The mnemon<br>may optionally be terminated by an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                               | or L to specify the high going or lo<br>going transition of the output signa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| as: $V_L = 0.4V$ , $V_H = 2.4V$ , $t_R < 10$ ns, $t_F < 10$ ns.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                               | Maximum delay times are measure<br>from xx Valid to yy Valid. Minimum d<br>lay times are measured from xx Valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Period The period of clock signal is designated as $t_{Pxx}$ where xx represents the mnemonic of the clock signal being specified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                               | yy Invalid. This parameter is tested u<br>der the load conditions specified in th<br>Conditions column of the Timing Spec<br>fications section of this data sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

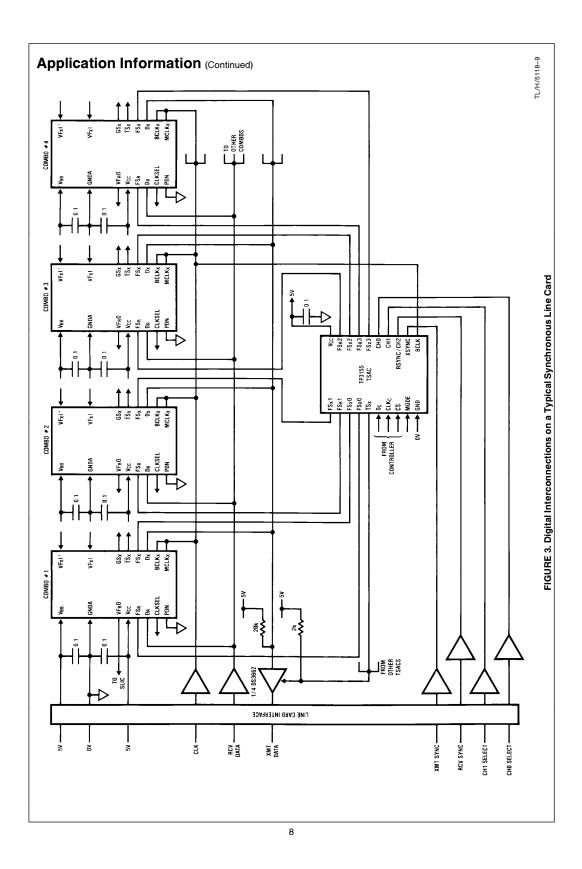

# **Applications Information**

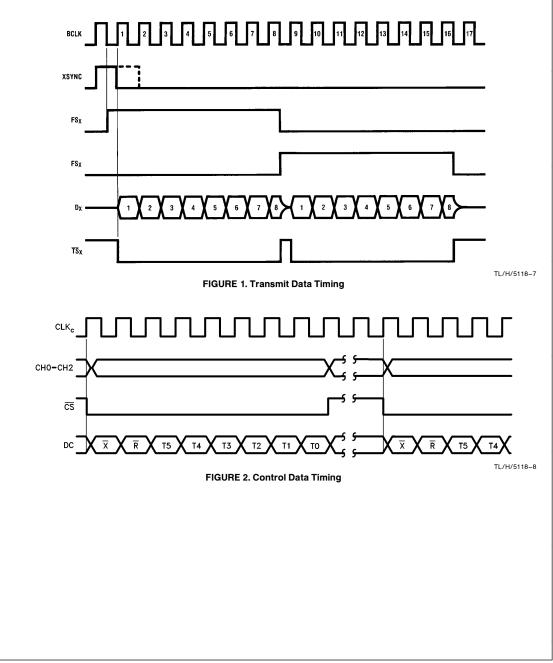

A combination of the TP3155 TSAC and any CODEC/Filter COMBO from the TP3052/3/4/7 or TP3064/7 series will result in data timing as shown in *Figure 1*. Although the FS<sub>x</sub> output pulse goes high before BCLK goes high, the D<sub>x</sub> output of the combo remains in the TRI-STATE mode until both are high. The eight bit period is shortened to prevent a bus clash, just as it is on the TP3020/1 CODECs.

Alternatively, eight full-length bits can be obtained by inverting the BCLK to the combo devices, thereby aligning rising edges of BCLK and  ${\sf FS}_{X/R}.$

*Figure 2* shows typical timing for the control data interface. *Figure 3* shows the digital interconnections of a typical line card application.

7

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications