# 500 kSPS, 8-Channel, Software-Selectable, True Bipolar Input, 12-Bit Plus Sign ADC

Enhanced Product AD7327-EP

#### **FEATURES**

12-bit plus sign SAR ADC

True bipolar input ranges

Software-selectable input ranges

±10 V, ±5 V, ±2.5 V, 0 V to +10 V

500 kSPS throughput rate

8 analog input channels with channel sequencer

Single-ended, true differential, and pseudo differential analog input capability

High analog input impedance

Low power: 18 mW

Temperature indicator

Full power signal bandwidth: 22 MHz Internal 2.5 V reference High speed serial interface Power-down modes 20-lead TSSOP package iCMOS process technology

#### **ENHANCED PRODUCT FEATURES**

Supports defense and aerospace applications (AQEC standard)

Military temperature range: -55°C to +125°C

Controlled manufacturing baseline

One assembly/test site

One fabrication site

Product change notification

Qualification data available on request

#### **GENERAL DESCRIPTION**

The AD7327-EP<sup>1</sup> is an 8-channel, 12-bit plus sign successive approximation ADC designed on the *i*CMOS<sup>®</sup> (industrial CMOS) process. It enables the development of a wide range of high performance analog ICs capable of 33 V operation in a footprint that no previous generation of high voltage devices achieved. Unlike analog ICs using conventional CMOS processes, *i*CMOS components can accept bipolar input signals while providing increased performance, dramatically reduced power consumption, and reduced package size.

The AD7327-EP can accept true bipolar analog input signals, software-selectable from  $\pm 10$  V,  $\pm 5$  V,  $\pm 2.5$  V, and 0 V to  $\pm 10$  V. Each analog input channel can be independently programmed to one of the four input ranges. The analog input channels on the AD7327-EP can be programmed to be single-ended, true differential, or pseudo differential.

# Rev. C Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

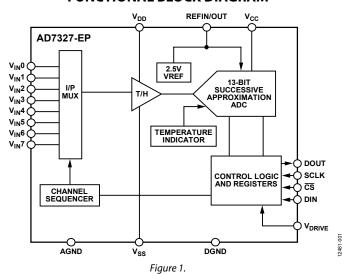

#### **FUNCTIONAL BLOCK DIAGRAM**

The ADC contains a 2.5 V internal reference. The AD7327-EP also allows external reference operation. If a 3 V reference is applied to the REFIN/OUT pin, the AD7327-EP can accept a true bipolar  $\pm 12$  V analog input. Minimum  $\pm 12$  V  $V_{DD}$  and  $V_{SS}$  supplies are required for the  $\pm 12$  V input range. The ADC has a high speed serial interface that can operate at throughput rates up to 500 kSPS.

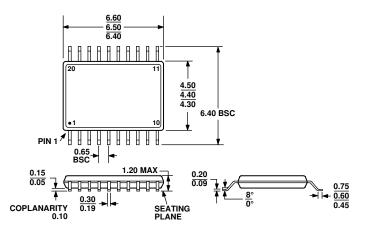

The AD7327-EP is housed in a 20-lead TSSOP with operation specified from -55°C to +125°C. Additional application and technical information can be found in the AD7327 data sheet.

#### **PRODUCT HIGHLIGHTS**

- 1. The AD7327-EP can accept true bipolar analog input signals,  $\pm 10$  V,  $\pm 5$  V,  $\pm 2.5$  V, and 0 V to  $\pm 10$  V (unipolar).

- The eight analog inputs can be configured as eight singleended inputs, four true differential inputs, four pseudo differential inputs, or seven pseudo differential inputs.

- 500 kSPS serial interface. SPI®-/QSPI™-/DSP-/MICROWIRE™compatible interface.

- Low power, 18 mW, at a maximum throughput rate of 500 kSPS.

- 5. Channel sequencer.

<sup>&</sup>lt;sup>1</sup> Protected by U.S. Patent No. 6,731,232.

## **TABLE OF CONTENTS**

| Features                                | Absolute Maximum Ratings8                        |

|-----------------------------------------|--------------------------------------------------|

| Enhanced Product Features               | ESD Caution8                                     |

| General Description                     | Pin Configuration and Function Descriptions9     |

| Functional Block Diagram                | Typical Performance Characteristics              |

| Product Highlights                      | Outline Dimensions                               |

| Revision History                        | Ordering Guide14                                 |

| Specifications                          |                                                  |

| Timing Specifications                   |                                                  |

| REVISION HISTORY                        |                                                  |

| 4/2018—Rev. B to Rev. C                 | 10/2014—Rev. 0 to Rev. A                         |

| Changes to Features Section             | Changes to Operating Temperature Range, Table 38 |

| Changes to Ordering Guide               |                                                  |

|                                         | 9/2014—Revision 0: Initial Version               |

| 9/2015—Rev. A to Rev. B                 |                                                  |

| Added Enhanced Product Features Section |                                                  |

## **SPECIFICATIONS**

$V_{DD} = 12 \text{ V to } 16.5 \text{ V}, V_{SS} = -12 \text{ V to } -16.5 \text{ V}, V_{CC} = 2.7 \text{ V to } 5.25 \text{ V}, V_{DRIVE} = 2.7 \text{ V to } 5.25 \text{ V}, V_{REF} = 2.5 \text{ V to } 3.0 \text{ V internal/external, } f_{SCLK} = 10 \text{ MHz, } f_S = 500 \text{ kSPS, } T_A = T_{MAX} \text{ to } T_{MIN} \text{, unless otherwise noted.}$

Table 1.

| Parameter <sup>1</sup>                                 | Min  | Тур             | Max   | Unit | Test Conditions/Comments                                                                                                                                    |

|--------------------------------------------------------|------|-----------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                                    |      | <del>-</del>    |       |      | f <sub>IN</sub> = 50 kHz sine wave                                                                                                                          |

| Signal-to-Noise Ratio (SNR) <sup>2</sup>               | 76   |                 |       | dB   | Differential mode, $V_{CC} = 4.75 \text{ V}$ to $5.25 \text{ V}$                                                                                            |

|                                                        | 75.5 |                 |       | dB   | Differential mode, V <sub>CC</sub> < 4.75 V                                                                                                                 |

|                                                        | 72   |                 |       | dB   | Single-ended/pseudo differential mode; $\pm 10 \text{ V}$ , $\pm 2.5 \text{ V}$ and $\pm 5 \text{ V}$ ranges, $V_{CC} = 4.75 \text{ V}$ to $5.25 \text{ V}$ |

|                                                        | 71.7 |                 |       | dB   | Single-ended/pseudo differential mode; 0 V to 10 V $V_{CC} = 4.75$ V to 5.25 V and all ranges at $V_{CC} < 4.75$ V                                          |

| Signal-to-Noise + Distortion (SINAD) <sup>2</sup>      | 75   |                 |       | dB   | Differential mode; ±2.5 V and ±5 V ranges                                                                                                                   |

|                                                        | 74   |                 |       | dB   | Differential mode; 0 V to 10 V                                                                                                                              |

|                                                        |      | 76              |       | dB   | Differential mode; ±10 V range                                                                                                                              |

|                                                        | 70.7 |                 |       | dB   | Single-ended/pseudo differential mode; ±2.5 V and ±5 V ranges                                                                                               |

|                                                        |      | 72.5            |       | dB   | Single-ended/pseudo differential mode; $0 \text{ V}$ to $+10 \text{ V}$ and $\pm 10 \text{ V}$ ranges                                                       |

| Total Harmonic Distortion (THD) <sup>2</sup>           |      |                 | -79.3 | dB   | Differential mode; ±2.5 V and ±5 V ranges                                                                                                                   |

|                                                        |      |                 | -78.8 | dB   | Differential mode; 0 V to 10 V ranges                                                                                                                       |

|                                                        |      | -82             |       | dB   | Differential mode; ±10 V range                                                                                                                              |

|                                                        |      |                 | -76   | dB   | Single-ended/pseudo differential mode; ±5 V range                                                                                                           |

|                                                        |      |                 | -77.3 | dB   | Single-ended/pseudo differential mode; ±2.5 V range                                                                                                         |

|                                                        |      | -80             |       | dB   | Single-ended/pseudo differential mode; $0 \text{ V}$ to $+10 \text{ V}$ and $\pm 10 \text{ V}$ ranges                                                       |

| Peak Harmonic or Spurious<br>Noise (SFDR) <sup>2</sup> |      |                 | -80   | dB   | Differential mode; ±2.5 V and ±5 V ranges                                                                                                                   |

|                                                        |      |                 | -80   | dB   | Differential mode; 0 V to 10 V ranges                                                                                                                       |

|                                                        |      | -82             |       | dB   | Differential mode; ±10 V ranges                                                                                                                             |

|                                                        |      |                 | -77.2 | dB   | Single-ended/pseudo differential mode; ±5 V range                                                                                                           |

|                                                        |      |                 | -78.9 | dB   | Single-ended/pseudo differential mode; ±2.5 V range                                                                                                         |

|                                                        |      | <del>-</del> 79 |       | dB   | Single-ended/pseudo differential mode; $0 \text{ V to } +10 \text{ V}$ and $\pm 10 \text{ V}$ ranges                                                        |

| Intermodulation Distortion (IMD) <sup>2</sup>          |      |                 |       |      | $f_A = 50 \text{ kHz}, f_B = 30 \text{ kHz}$                                                                                                                |

| Second-Order Terms                                     |      | -88             |       | dB   |                                                                                                                                                             |

| Third-Order Terms                                      |      | -90             |       | dB   |                                                                                                                                                             |

| Aperture Delay <sup>3</sup>                            |      | 7               |       | ns   |                                                                                                                                                             |

| Aperture Jitter <sup>3</sup>                           |      | 50              |       | ps   |                                                                                                                                                             |

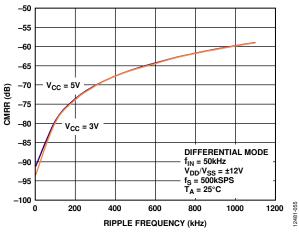

| Common-Mode Rejection (CMRR) <sup>2</sup>              |      | <del>-</del> 79 |       | dB   | Up to 100 kHz ripple frequency; see Figure 17                                                                                                               |

| Channel-to-Channel Isolation <sup>2</sup>              |      | -72             |       | dB   | $f_{\text{IN}}$ on unselected channels up to 100 kHz; see Figure 14                                                                                         |

| Full Power Bandwidth                                   |      | 22              |       | MHz  | At 3 dB                                                                                                                                                     |

|                                                        |      | 5               |       | MHz  | At 0.1 dB                                                                                                                                                   |

| Parameter <sup>1</sup>                         | Min                 | Тур             | Max        | Unit | Test Conditions/Comments                                                                                                                                                                                    |

|------------------------------------------------|---------------------|-----------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC ACCURACY <sup>4</sup>                       |                     |                 |            |      | Single-ended/pseudo differential mode 1 LSB =                                                                                                                                                               |

|                                                |                     |                 |            |      | FSR/4096, unless otherwise noted; differential mode                                                                                                                                                         |

|                                                |                     |                 |            |      | 1 LSB = FSR/8192, unless otherwise noted                                                                                                                                                                    |

| Resolution                                     | 13                  |                 |            | Bits |                                                                                                                                                                                                             |

| No Missing Codes                               | 12-bit              |                 |            | Bits | Differential mode                                                                                                                                                                                           |

|                                                | plus sign           |                 |            |      |                                                                                                                                                                                                             |

|                                                | (13 bits)           |                 |            |      |                                                                                                                                                                                                             |

|                                                | 11-bit<br>plus sign |                 |            | Bits | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                | (12 bits)           |                 |            |      |                                                                                                                                                                                                             |

| Integral Nonlinearity <sup>2</sup>             | (12 5.05)           |                 | ±1.25      | LSB  | Differential mode; $V_{CC} = 3 \text{ V to } 5.25 \text{ V, typical for } V_{CC} =$                                                                                                                         |

|                                                |                     |                 | 0          |      | 2.7 V                                                                                                                                                                                                       |

|                                                |                     |                 | ±1.2       | LSB  | Single-ended/pseudo differential mode, $V_{CC} = 3 \text{ V}$ to                                                                                                                                            |

|                                                |                     |                 |            |      | $5.25 \text{ V}$ , typical for $V_{CC} = 2.7 \text{ V}$                                                                                                                                                     |

|                                                |                     | -0.7/+1.2       |            | LSB  | Single-ended/pseudo differential mode (LSB =                                                                                                                                                                |

|                                                |                     |                 |            |      | FSR/8192)                                                                                                                                                                                                   |

| Differential Nonlinearity <sup>2</sup>         |                     |                 | -0.99/+1.2 | LSB  | Differential mode; guaranteed no missing codes to                                                                                                                                                           |

|                                                |                     |                 | . 0.00     | LCD  | 13 bits                                                                                                                                                                                                     |

|                                                |                     |                 | ±0.99      | LSB  | Single-ended mode; guaranteed no missing codes to 12 bits                                                                                                                                                   |

|                                                |                     | -0.7/+1         |            | LSB  | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                |                     | 0.7711          |            | LSD  | (LSB = FSR/8192)                                                                                                                                                                                            |

| Offset Error <sup>2, 5</sup>                   |                     |                 | -6/+10     | LSB  | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                |                     |                 | -7/+11     | LSB  | Differential mode                                                                                                                                                                                           |

| Offset Error Match <sup>2, 5</sup>             |                     |                 | ±0.8       | LSB  | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                |                     |                 | ±0.5       | LSB  | Differential mode                                                                                                                                                                                           |

| Gain Error <sup>2, 5</sup>                     |                     |                 | ±8         | LSB  | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                |                     |                 | ±15        | LSB  | Differential mode                                                                                                                                                                                           |

| Gain Error Match <sup>2, 5</sup>               |                     |                 | ±0.5       | LSB  | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                |                     |                 | ±0.5       | LSB  | Differential mode                                                                                                                                                                                           |

| Positive Full-Scale Error <sup>2, 6</sup>      |                     |                 | ±4         | LSB  | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                |                     |                 | ±8         | LSB  | Differential mode                                                                                                                                                                                           |

| Positive Full-Scale Error Match <sup>2,6</sup> |                     |                 | ±0.5       | LSB  | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                |                     |                 | ±0.5       | LSB  | Differential mode                                                                                                                                                                                           |

| Bipolar Zero Error <sup>2, 6</sup>             |                     |                 | ±9         | LSB  | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                |                     |                 | ±8         | LSB  | Differential mode                                                                                                                                                                                           |

| Bipolar Zero Error Match <sup>2, 6</sup>       |                     |                 | ±0.5       | LSB  | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                |                     |                 | ±0.5       | LSB  | Differential mode                                                                                                                                                                                           |

| Negative Full-Scale Error <sup>2, 6</sup>      |                     |                 | ±4         | LSB  | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                |                     |                 | ±7         | LSB  | Differential mode                                                                                                                                                                                           |

| Negative Full-Scale Error Match <sup>2,6</sup> |                     |                 | ±0.5       | LSB  | Single-ended/pseudo differential mode                                                                                                                                                                       |

|                                                |                     |                 | ±0.5       | LSB  | Differential mode                                                                                                                                                                                           |

| ANALOG INPUT                                   |                     |                 |            |      |                                                                                                                                                                                                             |

| Input Voltage Ranges <sup>2</sup>              |                     |                 |            | l    | Reference = 2.5 V                                                                                                                                                                                           |

| (Programmed via Range<br>Registers)            |                     | ±10             |            | V    | $V_{DD} = +10 \text{ V min}, V_{SS} = -10 \text{ V min}, V_{CC} = +2.7 \text{ V to } +5.25 \text{ V}$                                                                                                       |

| negisters)                                     |                     | ±5              |            | V    | $V_{DD} = +5 \text{ V min}, V_{SS} = -5 \text{ V min}, V_{CC} = +2.7 \text{ V to } +5.25 \text{ V}$                                                                                                         |

|                                                |                     | ±2.5            |            | V    | $V_{DD} = +5 \text{ V min}, V_{SS} = -5 \text{ V min}, V_{CC} = +2.7 \text{ V to } +5.25 \text{ V}$<br>$V_{DD} = +5 \text{ V min}, V_{SS} = -5 \text{ V min}, V_{CC} = +2.7 \text{ V to } +5.25 \text{ V}$  |

|                                                |                     | ±2.5<br>0 to 10 |            | V    | $V_{DD} = +10 \text{ V min}, V_{SS} = -3 \text{ V min}, V_{CC} = +2.7 \text{ V to } +5.25 \text{ V}$<br>$V_{DD} = +10 \text{ V min}, V_{SS} = \text{AGND min}, V_{CC} = +2.7 \text{ V to } +5.25 \text{ V}$ |

| Pseudo Differential V <sub>IN</sub> (–)        |                     | 0 10 10         |            | , v  | $V_{DD} = +16.5 \text{ V}, V_{SS} = AGND \text{ min}, V_{CC} = +2.7 \text{ V} \text{ to } +5.25 \text{ V}$<br>$V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}, V_{CC} = +5 \text{ V}$                   |

| Input Range <sup>2</sup>                       |                     |                 |            |      | νυυ - +10.5 v, v5510.5 v, vcc - +5 v                                                                                                                                                                        |

| ,                                              |                     | ±3.5            |            | V    | Reference = 2.5 V; range = ±10 V                                                                                                                                                                            |

|                                                |                     | ±6              |            | V    | Reference = $2.5 \text{ V}$ ; range = $\pm 5 \text{ V}$                                                                                                                                                     |

|                                                |                     | ±5              |            | V    | Reference = $2.5 \text{ V}$ ; range = $\pm 2.5 \text{ V}$                                                                                                                                                   |

|                                                |                     | +3/-5           |            | V    | Reference = 2.5 V; range = 0 V to +10 V                                                                                                                                                                     |

|                                                | I .                 | . 5, 5          |            | L •  | 213 V/Tallige OV to 110 V                                                                                                                                                                                   |

| Parameter <sup>1</sup>                             | Min                        | Тур        | Max   | Unit                                    | Test Conditions/Comments                                                |

|----------------------------------------------------|----------------------------|------------|-------|-----------------------------------------|-------------------------------------------------------------------------|

| DC Leakage Current                                 |                            |            | ±80   | nA                                      | $V_{IN} = V_{DD}$ or $V_{SS}$                                           |

|                                                    |                            | 3          |       | nA                                      | Per input channel, $V_{IN} = V_{DD}$ or $V_{SS}$                        |

| Input Capacitance <sup>3</sup>                     |                            | 13.5       |       | рF                                      | When in track, ±10 V range                                              |

|                                                    |                            | 16.5       |       | рF                                      | When in track, ±5 V and 0 V to +10 V ranges                             |

|                                                    |                            | 21.5       |       | pF                                      | When in track, ±2.5 V range                                             |

|                                                    |                            | 3          |       | pF                                      | When in hold, all ranges                                                |

| REFERENCE INPUT/OUTPUT                             |                            |            |       |                                         | -                                                                       |

| Input Voltage Range                                | 2.5                        |            | 3     | V                                       |                                                                         |

| Input DC Leakage Current                           |                            |            | ±1    | μΑ                                      |                                                                         |

| Input Capacitance                                  |                            | 10         |       | pF                                      |                                                                         |

| Reference Output Voltage                           |                            | 2.5        |       | V                                       |                                                                         |

| Reference Output Voltage Error<br>at 25°C          |                            |            | ±5    | mV                                      |                                                                         |

| Reference Output Voltage $T_{MIN}$ to $T_{MAX}$    |                            |            | ±10   | mV                                      |                                                                         |

| Reference Temperature<br>Coefficient               |                            |            | 25    | ppm/°C                                  |                                                                         |

|                                                    |                            | 3          |       | ppm/°C                                  |                                                                         |

| Reference Output Impedance                         |                            | 7          |       | Ω                                       |                                                                         |

| LOGIC INPUTS                                       |                            |            |       |                                         |                                                                         |

| Input High Voltage, V <sub>INH</sub>               | 2.4                        |            |       | V                                       |                                                                         |

| Input Low Voltage, V <sub>INL</sub>                |                            |            | 0.8   | V                                       | $V_{CC} = 4.75 \text{ V to } 5.25 \text{ V}$                            |

|                                                    |                            |            | 0.4   | V                                       | $V_{CC} = 2.7 \text{ to } 3.6 \text{ V}$                                |

| Input Current, I <sub>IN</sub>                     |                            |            | ±1    | μΑ                                      | $V_{IN} = 0 \text{ V or } V_{DRIVE}$                                    |

| Input Capacitance, C <sub>IN</sub> <sup>3</sup>    |                            | 10         |       | pF                                      |                                                                         |

| LOGIC OUTPUTS                                      |                            |            |       |                                         |                                                                         |

| Output High Voltage, V <sub>OH</sub>               | V <sub>DRIVE</sub> – 0.2 V |            |       | V                                       | Isource = 200 μA                                                        |

| Output Low Voltage, Vol                            |                            |            | 0.4   | V                                       | $I_{SINK} = 200 \mu\text{A}$                                            |

| Floating-State Leakage Current                     |                            |            | ±1    | μΑ                                      |                                                                         |

| Floating-State Output<br>Capacitance <sup>3</sup>  |                            | 5          |       | pF                                      |                                                                         |

| Output Coding                                      |                            | aight natu | -     |                                         | Coding bit set to 1 in control register                                 |

|                                                    | Twos complement            |            |       | Coding bit set to 0 in control register |                                                                         |

| CONVERSION RATE                                    |                            |            |       |                                         |                                                                         |

| Conversion Time                                    |                            |            | 1.6   | μs                                      | 16 SCLK cycles with SCLK = 10 MHz                                       |

| Track-and-Hold Acquisition<br>Time <sup>2, 3</sup> |                            |            | 305   | ns                                      | Full-scale step input                                                   |

| Throughput Rate                                    |                            |            | 500   | kSPS                                    |                                                                         |

| POWER REQUIREMENTS                                 |                            |            |       |                                         | Digital inputs = $0 \text{ V}$ or $V_{DRIVE}$                           |

| $V_{DD}^2$                                         | 12                         |            | 16.5  | V                                       |                                                                         |

| V <sub>SS</sub> <sup>2</sup>                       | -12                        |            | -16.5 | V                                       |                                                                         |

| $V_{CC}^2$                                         | 2.7                        |            | 5.25  | V                                       |                                                                         |

| $V_{DRIVE}$                                        | 2.7                        |            | 5.25  | V                                       |                                                                         |

| Normal Mode (Static)                               |                            | 0.9        |       | mA                                      | $V_{DD}/V_{SS} = \pm 16.5 \text{ V}, V_{CC}/V_{DRIVE} = 5.25 \text{ V}$ |

| Normal Mode (Operational)                          |                            |            |       |                                         | $f_{SAMPLE} = 500 \text{ kSPS}$                                         |

| $I_{DD}$                                           |                            |            | 195   | μΑ                                      | $V_{DD} = 16.5 \text{ V}$                                               |

| Iss                                                |                            |            | 215   | μΑ                                      | $V_{SS} = -16.5 \text{ V}$                                              |

| Icc and Idrive                                     |                            |            | 2.3   | mA                                      | $V_{CC}/V_{DRIVE} = 5.25 V$                                             |

| Autostandby Mode (Dynamic)                         |                            |            |       |                                         | $f_{SAMPLE} = 250 \text{ kSPS}$                                         |

| $I_{DD}$                                           |                            |            | 100   | μΑ                                      | $V_{DD} = 16.5 V$                                                       |

| Iss                                                |                            |            | 110   | μΑ                                      | $V_{SS} = -16.5 \text{ V}$                                              |

| Icc and Idrive                                     |                            |            | 0.87  | mA                                      | $V_{CC}/V_{DRIVE} = 5.25 \text{ V}$                                     |

| Parameter <sup>1</sup>     | Min | Тур | Max   | Unit | Test Conditions/Comments                                                       |

|----------------------------|-----|-----|-------|------|--------------------------------------------------------------------------------|

| Autoshutdown Mode (Static) |     |     |       |      | SCLK on or off                                                                 |

| I <sub>DD</sub>            |     |     | 1     | μΑ   | $V_{DD} = 16.5 \text{ V}$                                                      |

| Iss                        |     |     | 1     | μΑ   | $V_{SS} = -16.5 \text{ V}$                                                     |

| Icc and Idrive             |     |     | 1     | μΑ   | $V_{CC}/V_{DRIVE} = 5.25 V$                                                    |

| Full Shutdown Mode         |     |     |       |      | SCLK on or off                                                                 |

| I <sub>DD</sub>            |     |     | 1     | μΑ   | $V_{DD} = 16.5 \text{ V}$                                                      |

| Iss                        |     |     | 1     | μΑ   | $V_{SS} = -16.5 \text{ V}$                                                     |

| Icc and Idrive             |     |     | 1     | μΑ   | $V_{CC}/V_{DRIVE} = 5.25 \text{ V}$                                            |

| POWER DISSIPATION          |     |     |       |      |                                                                                |

| Normal Mode (Operational)  |     |     | 19    | mW   | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}, V_{CC} = +5.25 \text{ V}$ |

| Full Shutdown Mode         |     |     | 38.25 | μW   | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}, V_{CC} = +5.25 \text{ V}$ |

<sup>&</sup>lt;sup>1</sup> Temperature range is -55°C to +125°C.

<sup>2</sup> See the terminology section of the AD7327 data sheet.

<sup>3</sup> Sample tested during initial release to ensure compliance.

<sup>4</sup> For dc accuracy specifications, the LSB size for differential mode is FSR/8192. For single-ended mode/pseudo differential mode, the LSB size is FSR/4096, unless otherwise noted.

<sup>5</sup> University OVES 10 Versity OVES 10 Versity of the property of the

<sup>&</sup>lt;sup>5</sup> Unipolar 0 V to 10 V range with straight binary output coding. <sup>6</sup> Bipolar range with twos complement output coding.

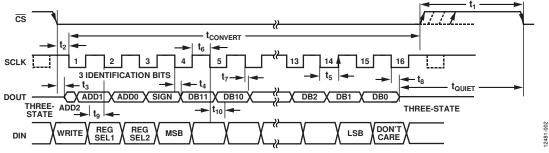

### **TIMING SPECIFICATIONS**

$V_{DD} = 12~V$  to 16.5~V,  $V_{SS} = -12~V$  to -16.5~V,  $V_{CC} = 2.7~V$  to 5.25~V,  $V_{DRIVE} = 2.7~V$  to 5.25~V,  $V_{REF} = 2.5~V$  to 3.0~V internal/external,  $T_A = T_{MAX}$  to  $T_{MIN}$ . Timing specifications apply with a 32 pF load, unless otherwise noted. Sample tested during initial release to ensure compliance. All input signals are specified with  $t_r = t_f = 5~ns$  (10% to 90% of  $V_{DRIVE}$ ) and timed from a voltage level of 1.6~V.

Table 2.

| -                     | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> |                                              |         | Description                                                                            |

|-----------------------|----------------------------------------------|----------------------------------------------|---------|----------------------------------------------------------------------------------------|

| Parameter             | V <sub>cc</sub> < 4.75 V                     | $V_{cc} = 4.75 \text{ V to } 5.25 \text{ V}$ | Unit    | V <sub>DRIVE</sub> ≤ V <sub>CC</sub>                                                   |

| f <sub>SCLK</sub>     | 50                                           | 50                                           | kHz min |                                                                                        |

|                       | 10                                           | 10                                           | MHz max |                                                                                        |

| <b>t</b> CONVERT      | $16 \times t_{SCLK}$                         | 16 × t <sub>SCLK</sub>                       | ns max  | $t_{SCLK} = 1/f_{SCLK}$                                                                |

| t <sub>QUIET</sub>    | 75                                           | 60                                           | ns min  | Minimum time between end of serial read and next falling edge of $\overline{CS}$       |

| t <sub>1</sub>        | 12                                           | 5                                            | ns min  | Minimum CS pulse width                                                                 |

| $t_2^1$               | 25                                           | 20                                           | ns min  | $\overline{\text{CS}}$ to SCLK set-up time; bipolar input ranges (±10 V, ±5 V, ±2.5 V) |

|                       | 45                                           | 35                                           | ns min  | Unipolar input range (0 V to 10 V)                                                     |

| $t_3$                 | 26                                           | 14                                           | ns max  | Delay from CS until DOUT three-state disabled                                          |

| t <sub>4</sub>        | 57                                           | 43                                           | ns max  | Data access time after SCLK falling edge                                               |

| <b>t</b> <sub>5</sub> | $0.4 \times t_{SCLK}$                        | $0.4 \times t_{SCLK}$                        | ns min  | SCLK low pulse width                                                                   |

| t <sub>6</sub>        | $0.4 \times t_{SCLK}$                        | $0.4 \times t_{SCLK}$                        | ns min  | SCLK high pulse width                                                                  |

| t <sub>7</sub>        | 13                                           | 8                                            | ns min  | SCLK to data valid hold time                                                           |

| t <sub>8</sub>        | 40                                           | 22                                           | ns max  | SCLK falling edge to DOUT high impedance                                               |

|                       | 10                                           | 9                                            | ns min  | SCLK falling edge to DOUT high impedance                                               |

| t <sub>9</sub>        | 4                                            | 4                                            | ns min  | DIN set-up time prior to SCLK falling edge                                             |

| t <sub>10</sub>       | 2                                            | 2                                            | ns min  | DIN hold time after SCLK falling edge                                                  |

| t <sub>POWER-UP</sub> | 750                                          | 750                                          | ns max  | Power-up from autostandby                                                              |

|                       | 500                                          | 500                                          | μs max  | Power-up from full shutdown/autoshutdown mode, internal reference                      |

|                       | 25                                           | 25                                           | μs typ  | Power-up from full shutdown/autoshutdown mode, external reference                      |

$<sup>^1</sup>$  When using the 0 V to 10 V unipolar range, running at 500 kSPS throughput rate with  $t_2$  at 20 ns, the mark space ratio needs to be limited to 50:50.

Figure 2. Serial Interface Timing Diagram

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| Table 3.                                                 |                                                     |  |  |

|----------------------------------------------------------|-----------------------------------------------------|--|--|

| Parameter                                                | Rating                                              |  |  |

| V <sub>DD</sub> to AGND, DGND                            | −0.3 V to +16.5 V                                   |  |  |

| V <sub>SS</sub> to AGND, DGND                            | +0.3 V to -16.5 V                                   |  |  |

| $V_{DD}$ to $V_{CC}$                                     | $V_{CC} - 0.3 \text{ V to } +16.5 \text{ V}$        |  |  |

| V <sub>CC</sub> to AGND, DGND                            | -0.3 V to +7 V                                      |  |  |

| V <sub>DRIVE</sub> to AGND, DGND                         | −0.3 V to +7 V                                      |  |  |

| AGND to DGND                                             | -0.3 V to +0.3 V                                    |  |  |

| Analog Input Voltage to AGND                             | $V_{SS} - 0.3 \text{ V to } V_{DD} + 0.3 \text{ V}$ |  |  |

| Digital Input Voltage to DGND                            | −0.3 V to +7 V                                      |  |  |

| Digital Output Voltage to GND                            | -0.3 V to V <sub>DRIVE</sub> + 0.3 V                |  |  |

| REFIN to AGND                                            | $-0.3 \text{ V to V}_{CC} + 0.3 \text{ V}$          |  |  |

| Input Current to Any Pin Except<br>Supplies <sup>1</sup> | ±10 mA                                              |  |  |

| Operating Temperature Range                              | −55°C to +125°C                                     |  |  |

| Storage Temperature Range                                | −65°C to +150°C                                     |  |  |

| Junction Temperature                                     | 150°C                                               |  |  |

| Thermal Impedance                                        |                                                     |  |  |

| $\Theta_{JA}$                                            | 143°C/W                                             |  |  |

| $\theta_{JC}$                                            | 45°C/W                                              |  |  |

| Pb-Free Temperature, Soldering                           |                                                     |  |  |

| Reflow                                                   | 260(0)°C                                            |  |  |

| ESD                                                      | 2.5 kV                                              |  |  |

<sup>&</sup>lt;sup>1</sup> Transient currents of up to 100 mA do not cause SCR latch-up.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

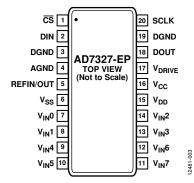

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CS                                     | Chip Select. Active low logic input. This input provides the dual function of initiating conversions on the AD7327-EP and frames the serial data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2       | DIN                                    | Data In. Data to be written to the on-chip registers is provided on this input and is clocked into the AD7327-EP on the falling edge of SCLK (see the Registers section of AD7327 data sheet).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3, 19   | DGND                                   | Digital Ground. Ground reference point for all digital circuitry on the AD7327-EP. The DGND and AGND voltages, ideally, share the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4       | AGND                                   | Analog Ground. Ground reference point for all analog circuitry on the AD7327-EP. Refer all analog input signals and any external reference signal to this AGND voltage. The AGND and DGND voltages, ideally, share the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5       | REFIN/OUT                              | Reference Input/Reference Output. The on-chip reference is available on this pin for external use to the AD7327-EP. The nominal internal reference voltage is 2.5 V, which appears at this pin. Place a 680 nF capacitor on the reference pin (see the Reference section of the AD7327 data sheet). Alternatively, the internal reference can be disabled and an external reference applied to this input. On power-up, the external reference mode is the default condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6       | Vss                                    | Negative Power Supply Voltage. Vss is the negative supply voltage for the analog input section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7 to 14 | V <sub>IN</sub> 0 to V <sub>IN</sub> 7 | Analog Input 0 to Analog Input 7. The analog inputs are multiplexed into the on-chip track-and-hold. The analog input channel for conversion is selected by programming the Channel Address Bit ADD2 through Channel Address Bit ADD0 in the control register. The inputs can be configured as eight single-ended inputs, four true differential input pairs, four pseudo differential inputs, or seven pseudo differential inputs. The configuration of the analog inputs is selected by programming the mode bits, Bit Mode 1 and Bit Mode 0, in the control register. The input range on each input channel is controlled by programming the range registers. Input ranges of $\pm 10 \text{ V}$ , $\pm 5 \text{ V}$ , $\pm 2.5 \text{ V}$ , and $0 \text{ V}$ to $\pm 10 \text{ V}$ can be selected on each analog input channel when a $\pm 2.5 \text{ V}$ reference voltage is used (see the Registers section of AD7327 data sheet). |

| 15      | $V_{DD}$                               | Positive Power Supply Voltage. V <sub>DD</sub> is the positive supply voltage for the analog input section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 16      | Vcc                                    | Analog Supply Voltage, 2.7 V to 5.25 V. V <sub>CC</sub> is the supply voltage for the ADC core on the AD7327-EP. Decouple this supply to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17      | V <sub>DRIVE</sub>                     | Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the interface operates. Decouple this pin to DGND. The voltage at this pin may be different to that at $V_{CC}$ , but $V_{DRIVE}$ must not exceed $V_{CC}$ by more than 0.3 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18      | DOUT                                   | Serial Data Output. The conversion output data is supplied to this pin as a serial data stream. The bits are clocked out on the falling edge of the SCLK input, and 16 SCLKs are required to access the data. The data stream consists of three channel identification bits, the sign bit, and 12 bits of conversion data. The data is provided MSB first (see the Serial Interface section of AD7327 data sheet).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 20      | SCLK                                   | Serial Clock, Logic Input. A serial clock input provides the SCLK used for accessing the data from the AD7327-EP. This clock is also used as the clock source for the conversion process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

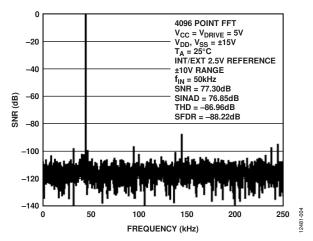

## TYPICAL PERFORMANCE CHARACTERISTICS

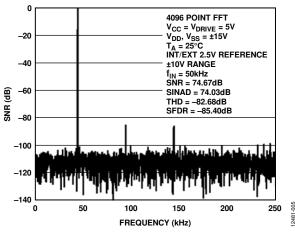

Figure 4. FFT True Differential Mode

Figure 5. FFT Single-Ended Mode

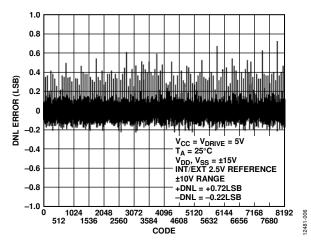

Figure 6. Typical DNL True Differential Mode

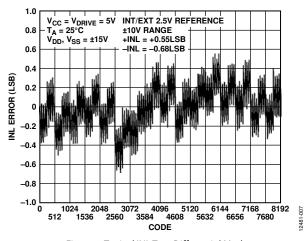

Figure 7. Typical INL True Differential Mode

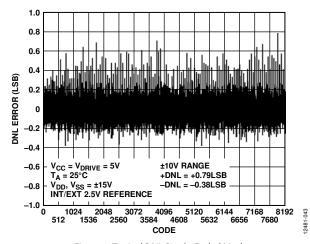

Figure 8. Typical DNL Single-Ended Mode

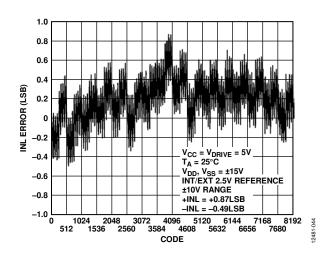

Figure 9. Typical INL Single-Ended Mode

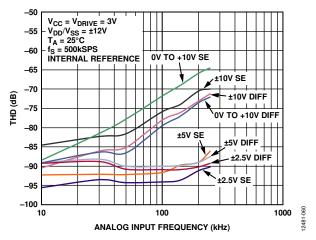

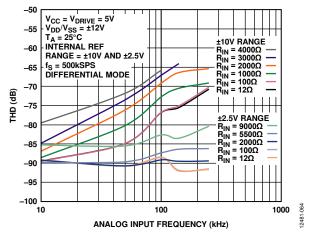

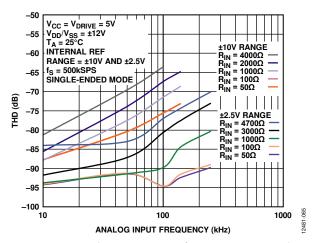

Figure 10. THD vs. Analog Input Frequency for Single-Ended (SE) and True Differential (Diff) Mode at 3 V V<sub>CC</sub>

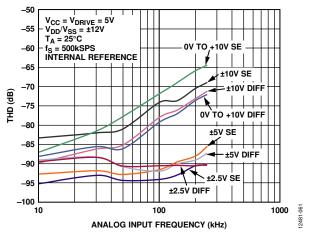

Figure 11. THD vs. Analog Input Frequency for Single-Ended (SE) and True Differential (Diff) Mode at 5 V V<sub>CC</sub>

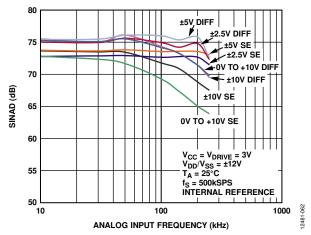

Figure 12. SINAD vs. Analog Input Frequency for Single-Ended (SE) and True Differential (Diff) Mode at 3 V V<sub>CC</sub>

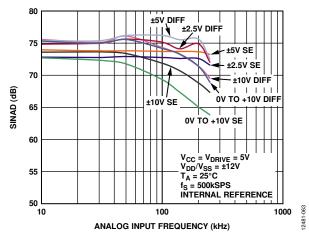

Figure 13. SINAD vs. Analog Input Frequency for Single-Ended (SE) and True Differential (Diff) Mode at 5 V V<sub>CC</sub>

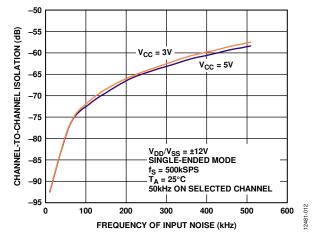

Figure 14. Channel-to-Channel Isolation

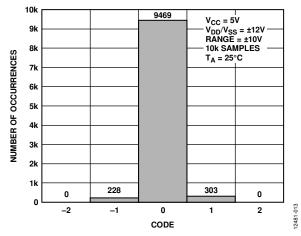

Figure 15. Histogram of Codes, True Differential Mode

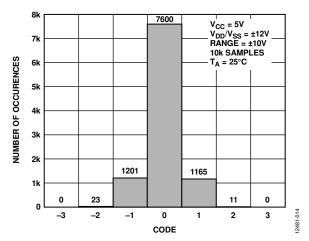

Figure 16. Histogram of Codes, Single-Ended Mode

Figure 17. CMRR vs. Common-Mode Ripple Frequency

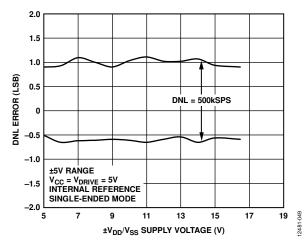

Figure 18. DNL Error vs.  $\pm V_{DD}/V_{SS}$  Supply Voltage at 500 kSPS

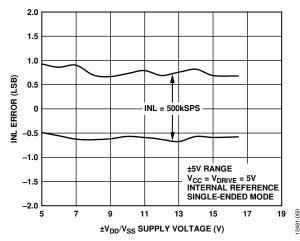

Figure 19. INL Error vs.  $\pm V_{DD}/V_{SS}$  Supply Voltage at 500 kSPS

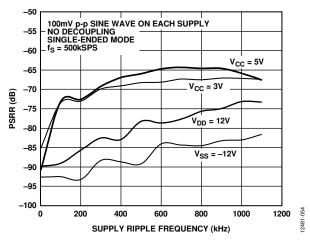

Figure 20. PSRR vs. Supply Ripple Frequency Without Supply Decoupling

Figure 21. THD vs. Analog Input Frequency for Various Source Impedances, True Differential Mode

Figure 22. THD vs. Analog Input Frequency for Various Source Impedances, Single-Ended Mode

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-153-AC

Figure 23. 20-Lead Thin Shrink Small Outline Package [TSSOP] (RU-20) Dimensions show in millimeters

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                               | Package Option |

|--------------------|-------------------|---------------------------------------------------|----------------|

| AD7327TRU-EP       | −55°C to +125°C   | 20-Lead Thin Shrink Small Outline Package [TSSOP] | RU-20          |

| AD7327TRU-EP-RL7   | −55°C to +125°C   | 20-Lead Thin Shrink Small Outline Package [TSSOP] | RU-20          |

| AD7327TRUZ-EP      | −55°C to +125°C   | 20-Lead Thin Shrink Small Outline Package [TSSOP] | RU-20          |

| AD7327TRUZ-EP-RL7  | −55°C to +125°C   | 20-Lead Thin Shrink Small Outline Package [TSSOP] | RU-20          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.