#### 8-CHANNELS SWITCH FOR MULTI-CELLS LI+/POLYMER BATTERY PACK

#### **Description**

AP9106 is 8-Channel analog switch which is suitable for up to 6-Cells in serial Li+/Polymer battery pack application.

AP9106 has four logic selection inputs (A/B/C/D). When all logic pins are set low, no channel is selected and the chip is turned off with shutdown mode. The A, B, C and D selection pins are compatible with TTL/CMOS logic level, can be connected to MCU I/O port directly to select the right channel respectively. The VOUT is output pin to indicate exactly the voltage of each battery cell.

AUX7, AUX8 pins are auxiliary channels, which can be connected to the NTC resistor to transfer the voltage variation into VOUT pin.

AP9106 is available in standard package of TSSOP-20.

#### **Features**

- ±1% Matching Error between any 2 Channels

- Up to 6-Cells in Serial Li+/Polymer Battery Pack Application with Single Chip

- Up to 11-cell in Serial Li+/Polymer Battery Pack Application with Dual Chip

- Ultra Low Current in Shutdown Mode: 1.0μA

- Compatible with TTL/CMOS for Logic Level

- Logic Level Shift Transfer

- Small Package: TSSOP-20

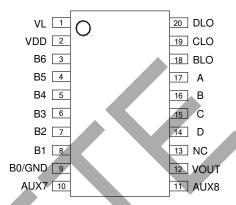

#### **Pin Assignments**

#### (Top View)

TSSOP-20

### **Applications**

- E-Bike Li+ Battery Pack

- Electric Tool Battery Pack

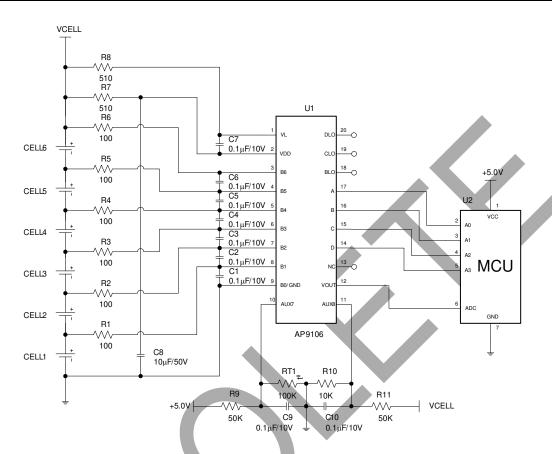

## **Typical Applications Circuit**

6-cell Battery (Single Chip) Application for AP9106

# **Truth Table for 6-cell (Single Chip) Battery Application**

|   | Logic | Input |   | Astino Observat                            | Outrook Waltana |  |

|---|-------|-------|---|--------------------------------------------|-----------------|--|

| Α | В     | С     | D | Active Channel                             | Output Voltage  |  |

| 0 | 0     | 0     | 0 | All channels OFF, chip is in shutdown mode | 0V              |  |

| 0 | 0     | 0     | 1 | QD1                                        | VCELL1          |  |

| 0 | 0     | 1     | 0 | QD2                                        | VCELL2          |  |

| 0 | 0     | 1     | 1 | QD3                                        | VCELL3          |  |

| 0 | 1     | 0     | 0 | QD4                                        | VCELL4          |  |

| 0 | 1     | 0     | 1 | QD5                                        | VCELL5          |  |

| 0 | 1     | 1     | 0 | QD6                                        | VCELL6          |  |

| 0 | 1     | 1     | 1 | QD7                                        | VTEMP           |  |

| 1 | 0     | 0     | 0 | QD8                                        | VTCELL          |  |

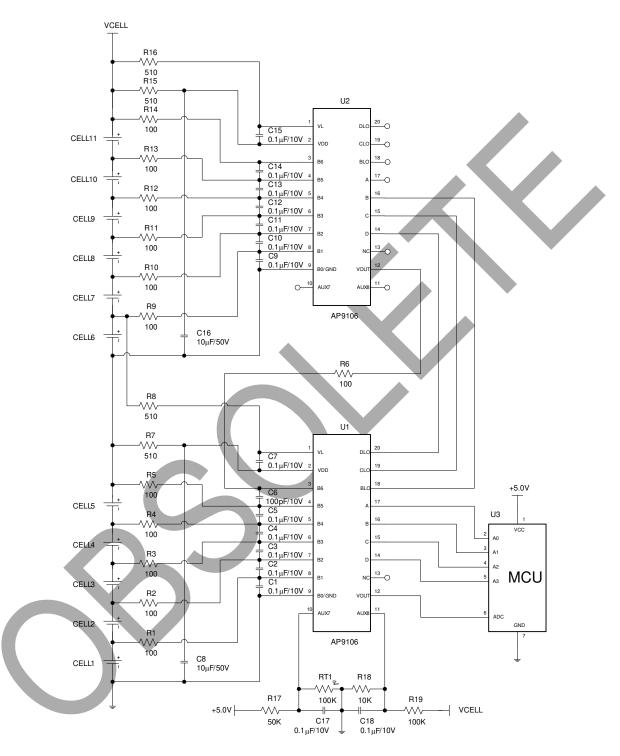

## **Typical Applications Circuit (Cont.)**

11-cell Battery (Dual Chips) Application for AP9106

# Truth Table for 11-cell (Dual Chips) Battery Application

| Logic Input |   | Active Champal (Lawer Chin) | Astive Channel (Umay Ohin) | <b>.</b>                                   |                                            |                |

|-------------|---|-----------------------------|----------------------------|--------------------------------------------|--------------------------------------------|----------------|

| A           | В | С                           | D                          | Active Channel (Lower Chip)                | Active Channel (Upper Chip)                | Output Voltage |

| 0           | 0 | 0                           | 0                          | All channels OFF, chip is in shutdown mode | All channels OFF, chip is in shutdown mode | 0V             |

| 0           | 0 | 0                           | 1                          | QD1                                        | Shutdown mode                              | VCELL1         |

| 0           | 0 | 1                           | 0                          | QD2                                        | Shutdown mode                              | VCELL2         |

| 0           | 0 | 1                           | 1                          | QD3                                        | Shutdown mode                              | VCELL3         |

| 0           | 1 | 0                           | 0                          | QD4                                        | Shutdown mode                              | VCELL4         |

| 0           | 1 | 0                           | 1                          | QD5                                        | Shutdown mode                              | VCELL5         |

| 0           | 1 | 1                           | 0                          | QD6                                        | Shutdown mode                              | 0V             |

| 0           | 1 | 1                           | 1                          | QD7                                        | Shutdown mode                              | VTEMP          |

| 1           | 0 | 0                           | 0                          | QD8                                        | Shutdown mode                              | VTCELL         |

| 1           | 0 | 0                           | 1                          | QD6                                        | QD1                                        | VCELL6         |

| 1           | 0 | 1                           | 0                          | QD6                                        | QD2                                        | VCELL7         |

| 1           | 0 | 1                           | 1                          | QD6                                        | QD3                                        | VCELL8         |

| 1           | 1 | 0                           | 0                          | QD6                                        | QD4                                        | VCELL9         |

| 1           | 1 | 0                           | 1                          | QD6                                        | QD5                                        | VCELL10        |

| 1           | 1 | 1                           | 0                          | QD6                                        | QD6                                        | VCELL11        |

| 1           | 1 | 1                           | 1                          | QD6                                        | QD7                                        | _              |

### **Pin Descriptions**

| Pin Number | Pin Name | Function                                                                   |

|------------|----------|----------------------------------------------------------------------------|

| 1          | VL       | Level shift logic power supply                                             |

| 2          | VDD      | Power supply                                                               |

| 3          | B6       | Positive node of sixth battery cell                                        |

| 4          | B5       | Positive node of fifth battery cell & negative node of sixth battery cell  |

| 5          | В4       | Positive node of fourth battery cell & negative node of fifth battery cell |

| 6          | В3       | Positive node of third battery cell & negative node of fourth battery cell |

| 7          | B2       | Positive node of second battery cell & negative node of third battery cell |

| 8          | B1       | Positive node of first battery cell & negative node of second battery cell |

| 9          | B0(GND)  | Ground and negative node of first battery cell                             |

| 10         | AUX7     | Auxiliary channel 7                                                        |

| 11         | AUX8     | Auxiliary channel 8                                                        |

| 12         | VOUT     | Switch output pin                                                          |

| 13         | NC       | No connected                                                               |

| 14         | D        | Channel selection logic input D                                            |

| 15         | c        | Channel selection logic input C                                            |

| 16         | В        | Channel selection logic input B                                            |

| 17         | A        | Channel selection logic input A                                            |

| 18         | BLO      | Channel selection logic output B                                           |

| 19         | CLO      | Channel selection logic output C                                           |

| 20         | DLO      | Channel selection logic output D                                           |

Notes:

- 1. VDD pin should always be connected to the positive node of top battery.

- 2. Voltage of VL pin should be equal to or larger than that of VDD pin.

# Truth Table and Relationship between Input Logic, Output Logic and Selected Channel

|   | Logic | Input |   | L   | ogic Outp | ut  | A .:                                       | Q V !!         |

|---|-------|-------|---|-----|-----------|-----|--------------------------------------------|----------------|

| Α | В     | С     | D | BLO | CLO       | DLO | Active Channel                             | Output Voltage |

| 0 | 0     | 0     | 0 | 0   | 0         | 0   | All channels OFF, chip is in shutdown mode | 0V             |

| 0 | 0     | 0     | 1 | 0   | 0         | 0   | QD1                                        | B1 vs. B0(GND) |

| 0 | 0     | 1     | 0 | 0   | 0         | 0   | QD2                                        | B2 vs. B1      |

| 0 | 0     | 1     | 1 | 0   | 0         | 0   | QD3                                        | B3 vs. B2      |

| 0 | 1     | 0     | 0 | 0   | 0         | 0   | QD4                                        | B4 vs. B3      |

| 0 | 1     | 0     | 1 | 0   | 0         | 0   | QD5                                        | B5 vs. B4      |

| 0 | 1     | 1     | 0 | 0   | 0         | 0   | QD6                                        | B6 vs. B5      |

| 0 | 1     | 1     | 1 | 0   | 0         | 0   | QD7                                        | AUX7 vs. GND   |

| 1 | 0     | 0     | 0 | 0   | 0         | 0   | QD8                                        | AUX8 vs. GND   |

| 1 | 0     | 0     | 1 | 0   | 0         | 1   | QD6                                        | B6 vs. B5      |

| 1 | 0     | 1     | 0 | 0   | 1         | 0   | QD6                                        | B6 vs. B5      |

| 1 | 0     | 1     | 1 | 0   | 1         | _   | QD6                                        | B6 vs. B5      |

| 1 | 1     | 0     | 0 | 1   | 0         | 0   | QD6                                        | B6 vs. B5      |

| 1 | 1     | 0     | 1 | 1   | 0         | 1   | QD6                                        | B6 vs. B5      |

| 1 | 1     | 1     | 0 | 1   | 1         | 0   | QD6                                        | B6 vs. B5      |

| 1 | 1     | 1     | 1 | 1   | 1         | 1   | QD6                                        | B6 vs. B5      |

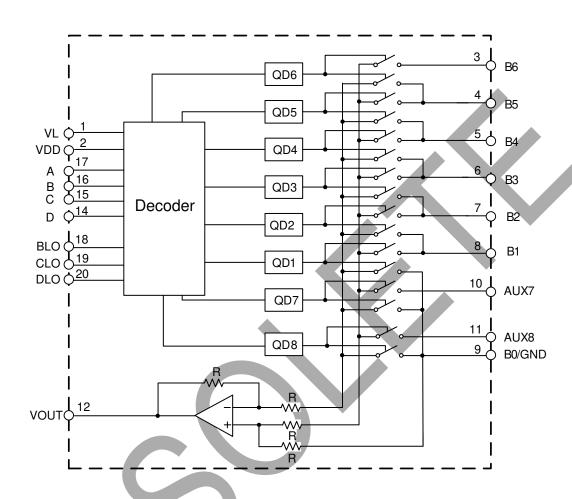

## **Functional Block Diagram**

### **Absolute Maximum Ratings** (Note 3)

| Symbol            | Parameter                                               | Rating      | Unit |

|-------------------|---------------------------------------------------------|-------------|------|

| $V_{DD}$          | Supply Voltage                                          | -0.3 to 35  | V    |

| V <sub>CELL</sub> | Voltage between $B_N$ and $B_{N+1}$ , AUX7/AUX8 and GND | -0.3 to 5   | V    |

| TJ                | Operating Junction Temperature Range                    | +150        | °C   |

| T <sub>STG</sub>  | Storage Temperature Range                               | -65 to +150 | °C   |

| T <sub>LEAD</sub> | Lead Temperature (Soldering, 10sec)                     | +260        | °C   |

| θJA               | Thermal Resistance                                      | 80          | °C/W |

| _                 | ESD (Machine Model)                                     | 200         | V    |

| _                 | ESD (Human Body Model)                                  | 2000        | V    |

Note 3: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

# **Recommended Operating Conditions**

| Symbol                           | Parameter                                                                                         | Min | Max | Unit |

|----------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|------|

| $V_{DD}$                         | Supply Voltage                                                                                    | 6.0 | 27  | V    |

| V <sub>CELL</sub>                | Battery Cell Voltage                                                                              | 2.0 | 4.5 | ٧    |

| V <sub>IN</sub>                  | Input Voltage (B6 vs. B5, B5 vs. B4, B4 vs. B3, B3 vs. B2, B2 vs. B1, B1 vs. GND, AUX7/8 vs. GND) | 2.0 | 4.5 | V    |

| T <sub>A</sub>                   | Operating Ambient Temperature                                                                     | -40 | +85 | °C   |

| V <sub>IL</sub> /V <sub>IH</sub> | Input Logic Level                                                                                 | 0   | 5.0 | V    |

Electrical Characteristics ( $V_{DD} = 21.6V$ ,  $V_L = V_{DD} + 4.4V = 26V$ ,  $T_A = +25$ °C, **Bold** typeface applies over full temperature -40°C  $\leq T_A \leq +85$ °C ranges, unless otherwise specified)

| Symbol                 | Parameter                                        | Test Conditions                                                                                                                  | Min  | Тур      | Max  | Unit          |  |  |

|------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|----------|------|---------------|--|--|

| V <sub>DD</sub>        | Supply Voltage                                   | _                                                                                                                                | 6.0  | _        | 27   | V             |  |  |

| IQ                     | Quiescent Current                                | _                                                                                                                                | _    | 0.2      | 0.5  | mA            |  |  |

| I <sub>SHUT</sub>      | Shutdown Current                                 | Set A, B, and C low                                                                                                              | _    | 1.0      | 2.0  | μΑ            |  |  |

| OPAMP Output Voltage   |                                                  |                                                                                                                                  |      |          |      |               |  |  |

| Vos                    | Offset Voltage                                   | Input DC voltage: 2.9V to 4.2V                                                                                                   | -100 | _        | +100 | mV            |  |  |

| V <sub>OL</sub>        | Out of Mallace Out to big                        |                                                                                                                                  | 2.0  |          | _    | V             |  |  |

| V <sub>OH</sub>        | Output Voltage Switching                         | _                                                                                                                                | J    | -        | 4.5  | V             |  |  |

| Switch                 |                                                  |                                                                                                                                  |      |          |      |               |  |  |

| laa                    | Bias Current                                     | For B2, B3, B4, B5 and B6 Pin                                                                                                    | ı    | 10       | 15   | μΑ            |  |  |

| I <sub>BIAS</sub>      | bias current                                     | For B1, AUX7, AUX8 Pin                                                                                                           |      |          | 1    | μΑ            |  |  |

| Ематсн                 | Channel Matching Error between any 2<br>Channels | Set all channel DC: 2.9V to 4.2V,<br>T <sub>A</sub> = -40 to +85°C,<br>(V <sub>MAX</sub> -V <sub>MIN</sub> )/average(CH1 to CH7) |      | ±1       |      | %             |  |  |

| _                      | Channel Isolation                                | f = 100Hz                                                                                                                        | _    | -80      | _    | dB            |  |  |

| V <sub>NO</sub>        | Output Noise                                     | BW = 100Hz, CH1 to CH7, DC input: 2.9V to 4.2V                                                                                   | _    | 50       | _    | $\mu V_{RMS}$ |  |  |

| tset                   | Channel Switching & Set-up Time                  | -                                                                                                                                | _    | 1.0      | _    | ms            |  |  |

| Logic Input (          | Voltage Mode)                                    |                                                                                                                                  |      |          |      |               |  |  |

| V <sub>IH</sub>        | Logic Input High Level                           | <b>A</b> , B, C, D                                                                                                               | 1.0  | _        | 5.0  | ٧             |  |  |

| V <sub>IL</sub>        | Logic Input Low Level                            | A, B, C, D                                                                                                                       | 0    | _        | 0.6  | ٧             |  |  |

| ال                     | Input Leakage Current                            | Set A, B, C, D low                                                                                                               | _    | _        | 1.0  | μΑ            |  |  |

| R <sub>PULL-DOWN</sub> | Pull Down Resistor                               | A, B, C, D                                                                                                                       | _    | 1.0      |      | ΜΩ            |  |  |

| Logic Output           | ogic Output (Voltage Mode)                       |                                                                                                                                  |      |          |      |               |  |  |

| V <sub>OL</sub>        | Logic Input Low Level                            | BLO, CLO, DLO                                                                                                                    | _    | $V_{DD}$ | _    | V             |  |  |

| VoH                    | Logic Input High Level                           | BLO, CLO, DLO                                                                                                                    | _    | VL       | _    | ٧             |  |  |

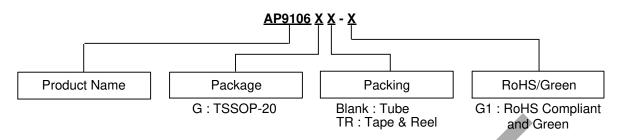

### **Ordering Information**

| Package  | Temperature Range | Part Number  | Marking ID | Packing     |

|----------|-------------------|--------------|------------|-------------|

|          | 40.               | AP9106G-G1   | AP9106GG   | Tube        |

| TSSOP-20 | -40 to +85°C      | AP9106GTR-G1 | AP9106GG   | Tape & Reel |

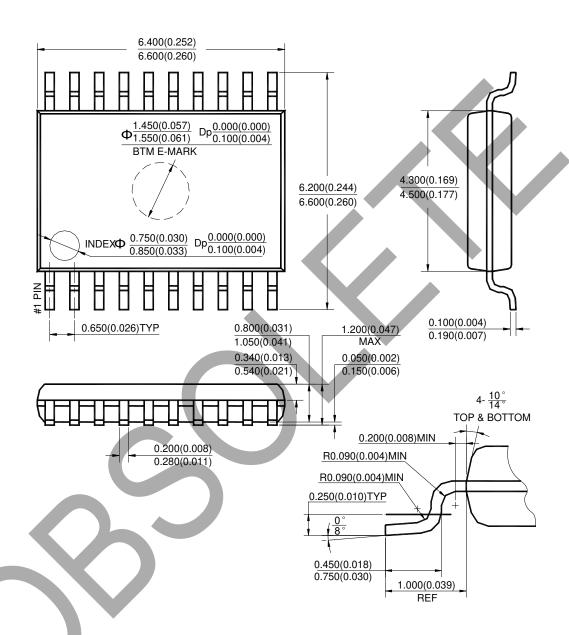

## Package Outline Dimensions (All dimensions in mm(inch).)

(1) Package Type: TSSOP-20

Note: Eject hole, oriented hole and mold mark is optional.

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2019, Diodes Incorporated

www.diodes.com

AP9106 12 of 12

Document number: DS41468 Rev. 2 - 4 www.diodes.com