# LITIX<sup>™</sup> Power

# TLD5099EP - Multitopology LITIX™ Power DC/DC Controller IC

1 Overview

# Description

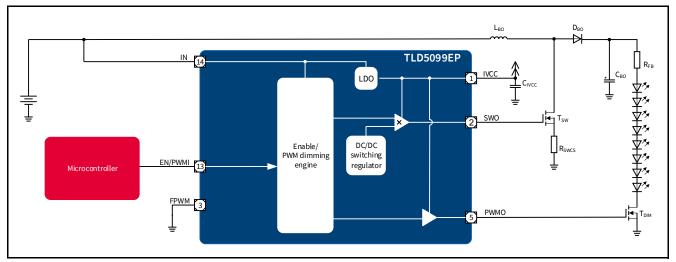

The TLD5099EP is a flexibly usable DC/DC boost controller with built in diagnosis and protection features especially designed to drive LEDs. It also includes a pulse width modulator to easily implement a dimming function

with reduced color shifting and a spread spectrum modulator to improve the EMI performance.

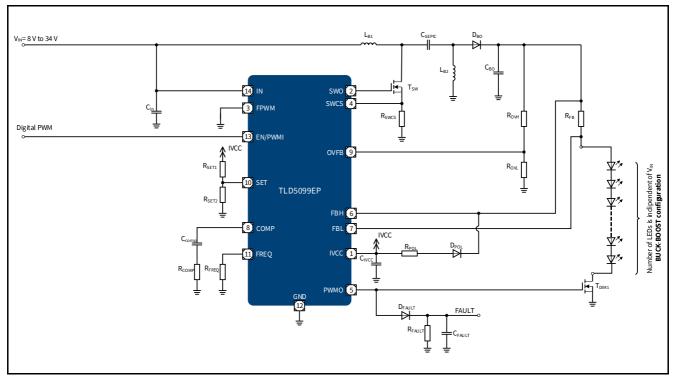

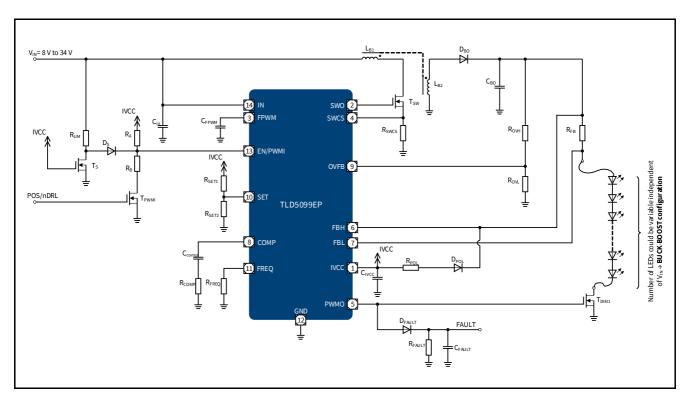

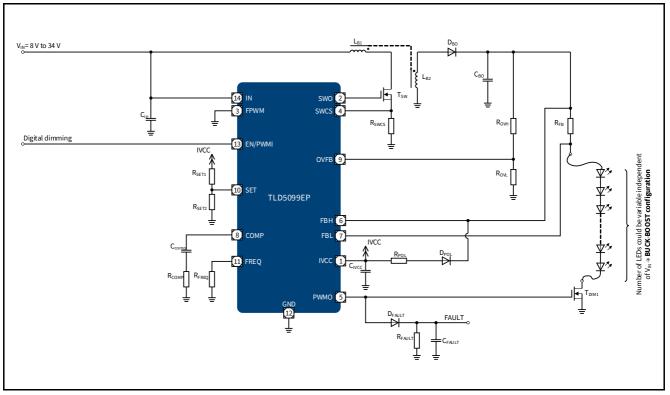

It is designed to support fixed current and fixed voltage configurations in multiple topologies such as Boost, Buck, Buck-Boost, SEPIC and Flyback by simply adjusting the external components. The TLD5099EP drives a low side n-channel power MOSFET from an internal 5 V linear regulator.

The switching frequency is adjustable in the range of 100 kHz to 500 kHz and can also be synchronized to an external clock source. A spread spectrum modulator can be activated to improve the EMI, by moving the energy of narrow harmonics peaks over a broadband spectrum.

The TLD5099EP can be flexibly dimmed by means of analog and/or PWM dimming. The enable function reduces the shut-down current consumption to  $I_{O OFF} < 15 \,\mu$ A at 105°C.

The current mode control scheme of this device provides a stable regulation loop maintained by small external compensation components. Additionally an integrated soft start feature limits the current peak as well as voltage overshoot at start-up. This IC is suited for use in the harsh automotive environments.

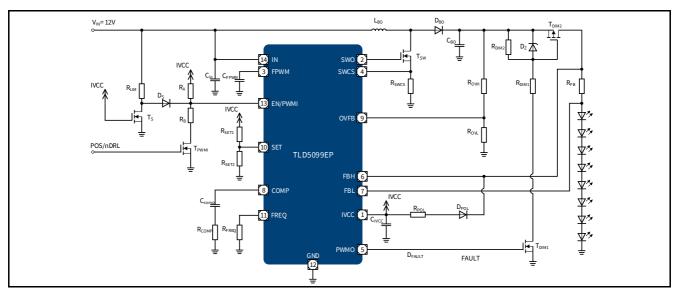

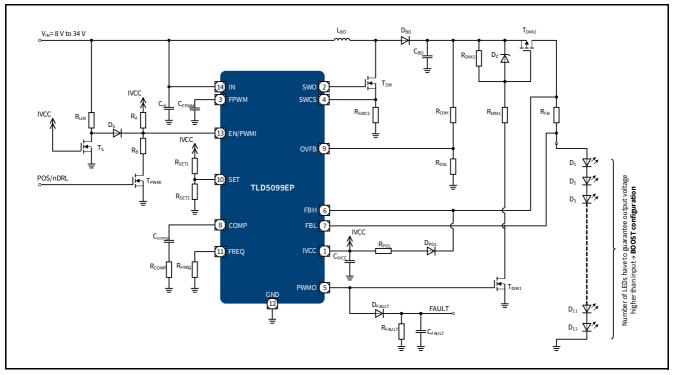

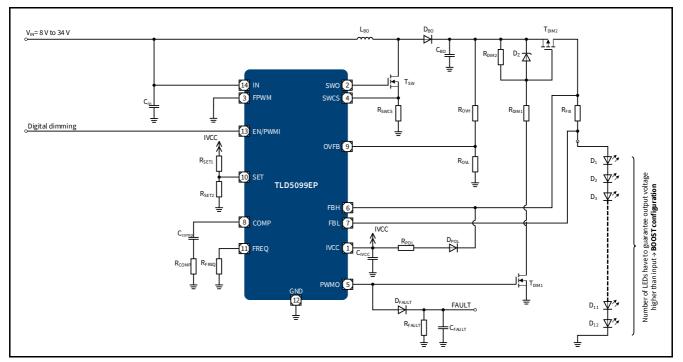

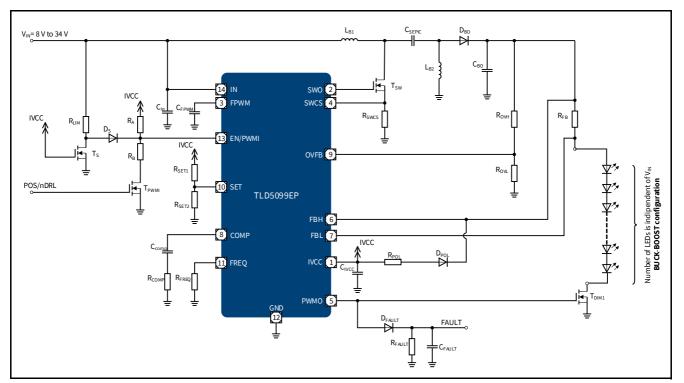

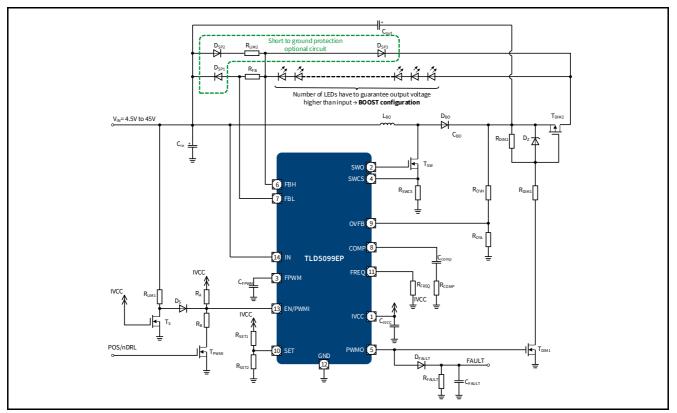

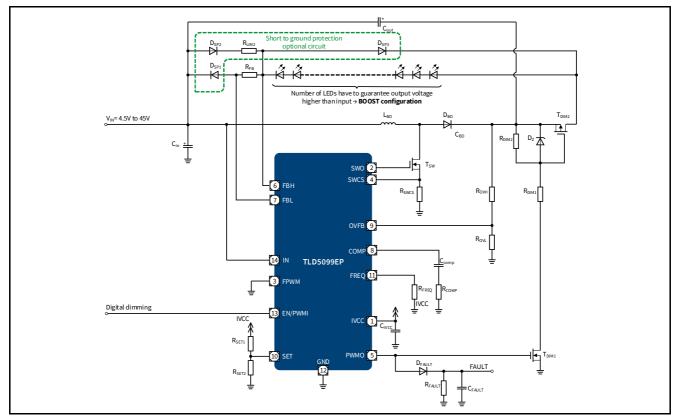

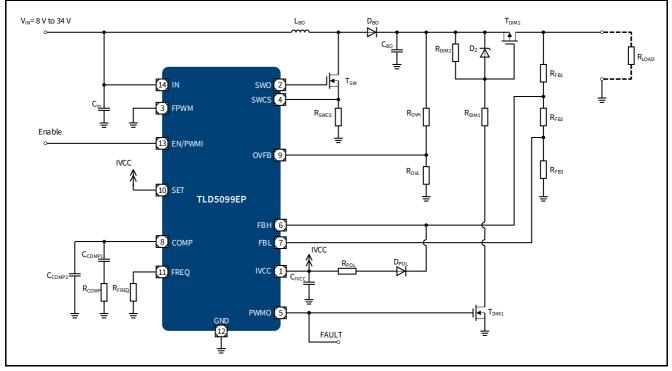

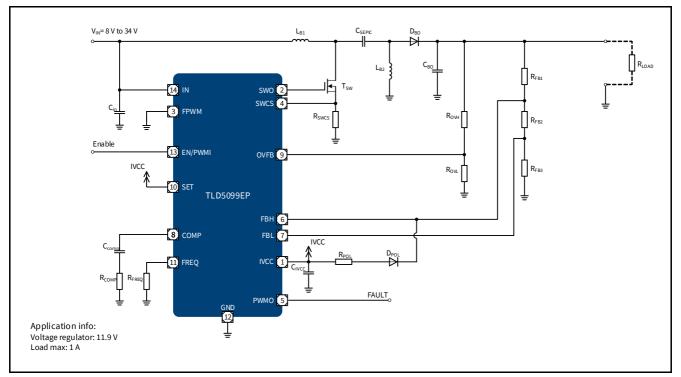

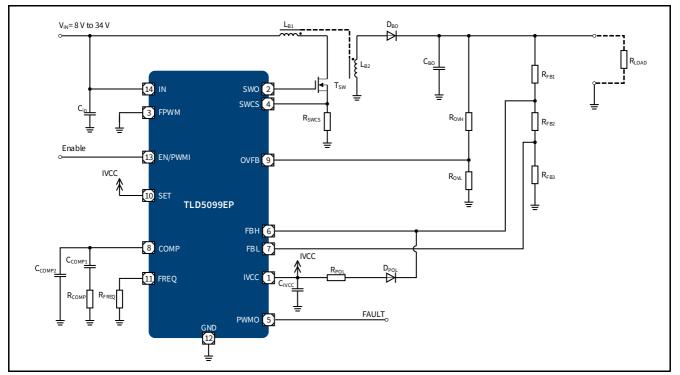

Figure 1 Typical application: Boost LED driver with short circuit protection circuitry

#### **Potential applications**

| Туре      | Package     | Marking |

|-----------|-------------|---------|

| TLD5099EP | PG-TSDSO-14 | TLD5099 |

# **Potential applications**

- Automotive exterior and interior lighting

- General illumination

- General purpose current/voltage controlled DC/DC driver

# Features

- Fixed current or fixed voltage configuration in Boost, Buck, Buck-Boost, SEPIC and Flyback topology

- Drives low-side external n-channel switching MOSFET from internal 5 V voltage regulator

- Flexible switching frequency range from 100 kHz to 500 kHz with spread spectrum modulator

- Synchronization with external clock source

- Wide input voltage range from 4.5 V to 45 V

- Enable & PWM functions with very low shutdown current:  $I_{Q_OFF} < 15 \mu A$  at 105°C

- Analog dimming and PWM dimming feature (embedded or external) to adjust average LED current

- PWMO gate driver for PWM dimming and output disconnection

| Feature                           | Symbol                 | Range                                                               |

|-----------------------------------|------------------------|---------------------------------------------------------------------|

| Nominal supply voltage range      | V <sub>IN</sub>        | 8 V 34 V                                                            |

| Extended supply voltage range     | V <sub>IN</sub>        | 4.5 V 45 V                                                          |

|                                   |                        | $V_{\rm IVCC} > V_{\rm IVCC,RTH,d}$ ; parameter deviations possible |

| Switching frequency range         | f <sub>FREQ</sub>      | 100 kHz 500 kHz oscillator frequency adjustment range               |

|                                   |                        | 250 kHz 500 kHz synchronization frequency capture range             |

| Maximum duty cycle                | D <sub>max,fixed</sub> | 91% fixed frequency mode                                            |

|                                   | D <sub>max,sync</sub>  | 88% synchronization mode                                            |

| Gate driver peak sourcing current | I <sub>SWO,SRC</sub>   | 380 mA (typical)                                                    |

| Gate driver peak sinking current  | I <sub>SWO,SNK</sub>   | 550 mA (typical)                                                    |

#### Table 1Product summary

# **Protection and diagnostic functions**

- Open circuit and short-to-ground detection

- Output overvoltage protection

- Short to GND protection

- Overtemperature shutdown

- Electrostatic discharge (ESD) protection

# **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100/101.

Datasheet

#### **Table of contents**

# **Table of contents**

| 1                                           | Overview                                                                                                                                                |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                           | Block diagram                                                                                                                                           |

| <b>3</b><br>3.1<br>3.2                      | Pin configuration5Pin assignment5Pin definitions and functions5                                                                                         |

| <b>4</b><br>4.1<br>4.2<br>4.3               | General product characteristics7Absolute maximum ratings7Functional Range9Thermal Resistance9                                                           |

| <b>5</b><br>5.1<br>5.2                      | Switching regulator11Description11Electrical characteristics12                                                                                          |

| <b>6</b><br>6.1<br>6.2<br>6.3<br>6.4        | Switching oscillator and synchronization14Description14Electrical characteristics15Typical performance characteristics of oscillator16Spread spectrum17 |

| <b>7</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5 | Enable and dimming function18Description18Enable function18Digital PWM dimming function18Embedded PWM dimming function19Electrical characteristics24    |

| <b>8</b><br>8.1<br>8.2                      | Linear regulator26Description26Electrical characteristics27                                                                                             |

| <b>9</b><br>9.1<br>9.2                      | Protection and diagnostic functions28Description28Electrical characteristics33                                                                          |

| <b>10</b><br>10.1<br>10.2<br>10.3           | Analog Dimming34Purpose of Analog Dimming34Description34Electrical characteristics38                                                                    |

| <b>11</b><br>11.1                           | Application information39Further application information46                                                                                              |

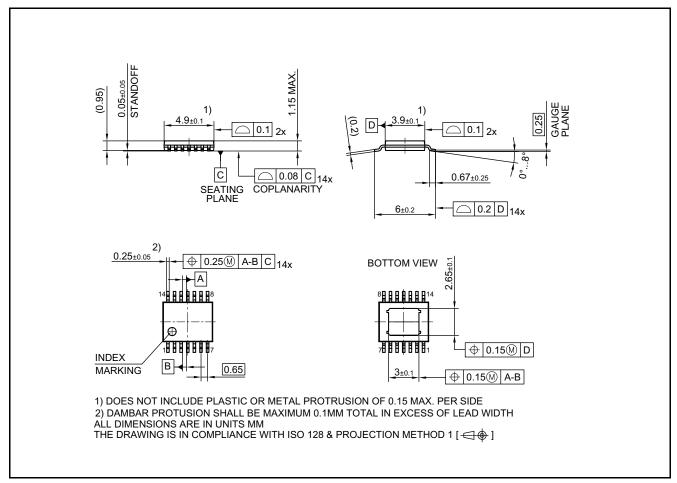

| 12                                          | Package outlines                                                                                                                                        |

| 13                                          | Revision history                                                                                                                                        |

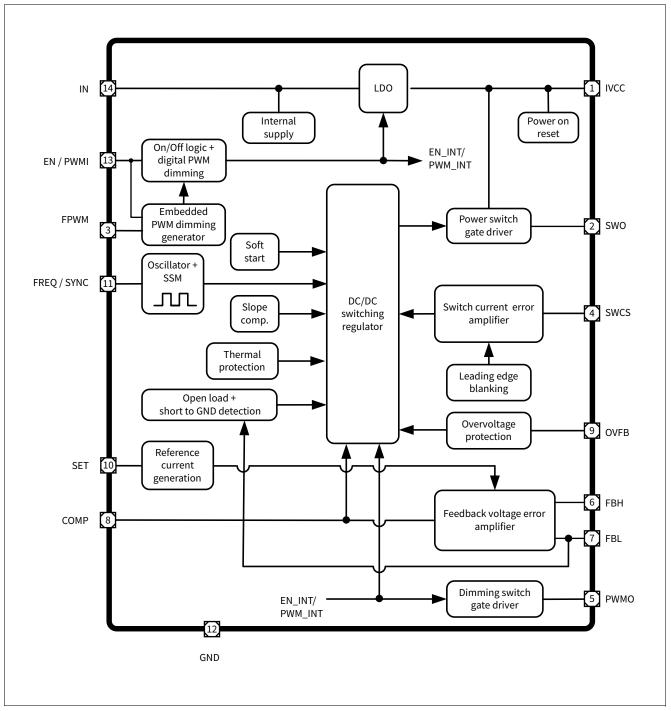

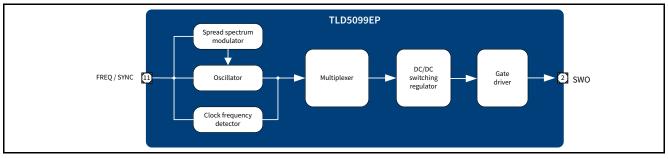

Block diagram

# 2 Block diagram

infineon

Pin configuration

# **3** Pin configuration

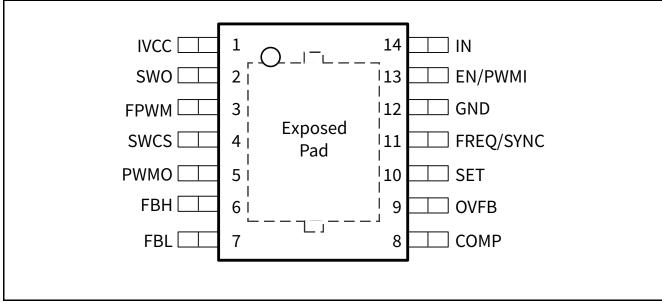

# 3.1 Pin assignment

Figure 3 Pin configuration TLD5099EP

# 3.2 Pin definitions and functions

#### Table 2Pin definition and function

| # | Symbol | Direction | Function                                                                                                                      |

|---|--------|-----------|-------------------------------------------------------------------------------------------------------------------------------|

| 1 | IVCC   | Output    | <b>Internal LDO</b><br>Used for internal biasing and gate drive. Bypass with external capacitor.<br>Pin must not be left open |

| 2 | SWO    | Output    | Switch gate driver<br>Connect to gate of external switching MOSFET                                                            |

| 3 | FPWM   | Output    | <b>PWM frequency selector</b><br>Connect external capacitor to set PWM frequency                                              |

| 4 | SWCS   | Input     | <b>Current sense</b><br>Detects the peak current through switch                                                               |

| 5 | РѠМО   | Output    | <b>PWM dimming</b><br>Connect to gate of external MOSFET                                                                      |

| 6 | FBH    | Input     | Voltage feedback positive<br>Non inverting Input (+)                                                                          |

| 7 | FBL    | Input     | Voltage feedback negative<br>Inverting Input (-)                                                                              |

| 8 | COMP   | Input     | <b>Compensation</b><br>Connect R and C network to pin for control loop stability                                              |

## **Pin configuration**

| #  | Symbol      | Direction | Function                                                                                                                                                                                                                                                                                                 |

|----|-------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9  | OVFB        | Input     | Overvoltage protection feedback                                                                                                                                                                                                                                                                          |

|    |             |           | Connect to resistive voltage divider to set overvoltage threshold                                                                                                                                                                                                                                        |

| 10 | SET         | Input     | <b>Analog dimming</b><br>Load current adjustment Pin. Pin must not be left open. If analog<br>dimming feature is not used connect to IVCC pin                                                                                                                                                            |

| 11 | FREQ / SYNC | Input     | <b>Frequency select or synchronization</b><br>Connect external resistor to GND to set frequency (two resistor sets are defined for activating or deactivating the Spread Spectrum Modulator)                                                                                                             |

| 12 | GND         | -         | Ground<br>Connect to system ground                                                                                                                                                                                                                                                                       |

| 13 | EN / PWMI   | Input     | <b>Enable or PWM</b><br>Apply logic "low" signal to disable device and put it in low current<br>consumption.<br>Apply logic "high" signal to enable device or PWM signal for dimming<br>LED.<br>Apply an analog signal (in a proper range) to enable a PWM engine which<br>works at a defined duty cycle |

| 14 | IN          | Input     | Supply<br>Supply for internal biasing                                                                                                                                                                                                                                                                    |

|    | EP          | -         | <b>Exposed Pad</b><br>Connect to external heat spreading GND Cu area (e.g. inner GND layer of<br>multilayer PCB with thermal vias)                                                                                                                                                                       |

**General product characteristics**

# 4 General product characteristics

# 4.1 Absolute maximum ratings

$T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Table 3 Absolute ma                                       | 1                                   |      |       |      |      | <b>.</b>                                                                                                     | Number   |

|-----------------------------------------------------------|-------------------------------------|------|-------|------|------|--------------------------------------------------------------------------------------------------------------|----------|

| Parameter                                                 | Symbol                              | •    | Value | 1    | Unit | Note or Test Condition                                                                                       | Number   |

|                                                           |                                     | Min. | Тур.  | Max. |      |                                                                                                              |          |

| Voltage                                                   | 1                                   |      | 1     |      | 1    |                                                                                                              | 1        |

| IN                                                        | V <sub>IN</sub>                     | -0.3 | -     | 45   | V    | -                                                                                                            | P_4.1.1  |

| Supply input                                              |                                     |      |       |      |      |                                                                                                              |          |

| EN / PWMI<br>Enable or PWM input                          | V <sub>EN</sub>                     | -40  | -     | 45   | V    | -                                                                                                            | P_4.1.2  |

| FBH-FBL<br>Feedback error amplifier<br>differential       | V <sub>fbh</sub> -V <sub>fbl</sub>  | -40  | -     | 61   | V    | The maximum delta<br>must not exceed 61 V<br>Differential signal (not<br>referred to GND)                    | P_4.1.3  |

| FBH<br>Feedback error amplifier<br>positive input         | V <sub>FBH</sub>                    | -40  | -     | 61   | V    | The difference between<br>V <sub>FBH</sub> and V <sub>FBL</sub> must not<br>exceed 61 V, refer to<br>P_4.1.3 | P_4.1.4  |

| FBL<br>Feedback error amplifier<br>negative input         | V <sub>FBL</sub>                    | -40  | -     | 61   | V    | The difference between<br>V <sub>FBH</sub> and V <sub>FBL</sub> must not<br>exceed 61 V, refer to<br>P_4.1.3 | P_4.1.5  |

| FBH and FBL current<br>Feedback error amplifier<br>inputs | I <sub>fbl</sub> , I <sub>fbh</sub> | -    | 1     | -    | mA   | t < 100 ms,<br>V <sub>FBH</sub> - V <sub>FBL</sub> = 0.3 V                                                   | P_4.1.6  |

| OVFB<br>Overvoltage feedback<br>input                     | V <sub>ovfb</sub>                   | -0.3 | -     | 5.5  | V    | -                                                                                                            | P_4.1.7  |

| OVFB<br>Overvoltage feedback<br>input                     | V <sub>ovfb</sub>                   | -0.3 | -     | 6.2  | V    | t < 10 s                                                                                                     | P_4.1.8  |

| SWCS<br>Switch current sense<br>Input                     | V <sub>swcs</sub>                   | -0.3 | -     | 5.5  | V    | -                                                                                                            | P_4.1.9  |

| SWCS<br>Switch current sense<br>input                     | V <sub>swcs</sub>                   | -0.3 | -     | 6.2  | V    | t < 10 s                                                                                                     | P_4.1.10 |

| SWO<br>Switch gate drive output                           | V <sub>swo</sub>                    | -0.3 | -     | 5.5  | V    | -                                                                                                            | P_4.1.11 |

#### Table 3Absolute maximum ratings1)

#### **General product characteristics**

# Table 3Absolute maximum ratings1)

| Parameter                                                         | Symbol                                   | Values |      |      | Unit | Note or Test Condition | Number   |

|-------------------------------------------------------------------|------------------------------------------|--------|------|------|------|------------------------|----------|

|                                                                   |                                          | Min.   | Тур. | Max. |      |                        |          |

| SWO<br>Switch gate drive output                                   | V <sub>swo</sub>                         | -0.3   | -    | 6.2  | V    | t < 10 s               | P_4.1.12 |

| FPWM<br>PWM frequency selector                                    | V <sub>FPWM</sub>                        | -0.3   | -    | 5.5  | V    | -                      | P_4.1.13 |

| FPWM<br>PWM frequency selector                                    | V <sub>FPWM</sub>                        | -0.3   | -    | 6.2  | V    | t < 10 s               | P_4.1.14 |

| COMP<br>Compensation input                                        | V <sub>COMP</sub>                        | -0.3   | -    | 5.5  | V    | -                      | P_4.1.15 |

| COMP<br>Compensation input                                        | V <sub>COMP</sub>                        | -0.3   | -    | 6.2  | V    | t < 10 s               | P_4.1.16 |

| FREQ / SYNC<br>Frequency and<br>synchronization input             | V <sub>FREQ</sub> /<br>V <sub>SYNC</sub> | -0.3   | -    | 5.5  | V    | -                      | P_4.1.17 |

| FREQ / SYNC<br>Frequency and<br>synchronization input             | V <sub>FREQ</sub> /<br>V <sub>SYNC</sub> | -0.3   | -    | 6.2  | V    | t < 10 s               | P_4.1.18 |

| PWMO<br>PWM dimming output                                        | V <sub>PWMO</sub>                        | -0.3   | -    | 5.5  | V    | -                      | P_4.1.19 |

| PWMO<br>PWM dimming output                                        | V <sub>PWMO</sub>                        | -0.3   | -    | 6.2  | V    | t < 10 s               | P_4.1.20 |

| SET<br>Analog dimming                                             | V <sub>SET</sub>                         | -0.3   | -    | 45   | V    | -                      | P_4.1.21 |

| IVCC<br>Internal linear voltage<br>regulator output               | V <sub>IVCC</sub>                        | -0.3   | -    | 5.5  | V    | -                      | P_4.1.23 |

| IVCC<br>Internal linear voltage<br>regulator output               | V <sub>IVCC</sub>                        | -0.3   | -    | 6.2  | V    | t < 10 s               | P_4.1.24 |

| Temperature                                                       |                                          |        |      |      | ÷    |                        |          |

| Junction temperature                                              | TJ                                       | -40    | -    | 150  | °C   | -                      | P_4.1.25 |

| Storage temperature                                               | T <sub>stg</sub>                         | -55    | _    | 150  | °C   | -                      | P_4.1.26 |

| ESD susceptibility                                                |                                          |        |      |      |      |                        |          |

| ESD resistivity of all pins                                       | $V_{\rm ESD_{HBM}}$                      | -2     | -    | 2    | kV   | HBM <sup>2)</sup>      | P_4.1.27 |

| ESD resistivity of IN,<br>EN/PWMI, FBH, FBL and<br>SET pin to GND | V <sub>ESD_HBM</sub>                     | -4     | -    | 4    | kV   | HBM <sup>2)</sup>      | P_4.1.28 |

| ESD resistivity                                                   | V <sub>esd_cdm</sub>                     | -500   |      | 500  | V    | CDM <sup>3)</sup>      | P_4.1.29 |

| ESD resistivity corner pins                                       | V <sub>ESD_CDM</sub>                     | -750   |      | 750  | V    | CDM <sup>3)</sup>      | P_4.1.30 |

1) Not subject to production test, specified by design

2) ESD susceptibility, Human Body Model "HBM" according to AEC Q100-002

3) ESD susceptibility, Charged Device Mode "CDM" according to AECQ100-011 Rev D

Datasheet

#### **General product characteristics**

Note:

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### 4.2 Functional Range

| Parameter                     | Symbol                     |      | Value | S    | Unit | Note or                                                                                         | Number  |

|-------------------------------|----------------------------|------|-------|------|------|-------------------------------------------------------------------------------------------------|---------|

|                               |                            | Min. | Тур.  | Max. |      | Test Condition                                                                                  |         |

| Extended supply voltage range | V <sub>IN</sub>            | 4.5  | -     | 45   | V    | <sup>1)</sup> V <sub>IVCC</sub> > V <sub>IVCC,RTH,d</sub> ;<br>parameter<br>deviations possible | P_4.2.1 |

| Nominal supply voltage range  | V <sub>IN</sub>            | 8    | -     | 34   | V    | -                                                                                               | P_4.2.2 |

| Feedback voltage<br>input     | $V_{\rm FBH}; V_{\rm FBL}$ | 3    | -     | 60   | V    | -                                                                                               | P_4.2.3 |

| Junction<br>temperature       | TJ                         | -40  | -     | 150  | °C   | -                                                                                               | P_4.2.4 |

#### Table 4Functional Range

1) Not subject to production test, specified by design

*Note:* Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 4.3 Thermal Resistance

*Note:* This thermal data was generated in accordance with JEDEC JESD51 standards. For further information visit **https://www.jedec.org**

#### Table 5Thermal Resistance

| Parameter           | Symbol            | Values |      |      | Unit | Note or                                    | Number  |

|---------------------|-------------------|--------|------|------|------|--------------------------------------------|---------|

|                     |                   | Min.   | Тур. | Max. |      | Test Condition                             |         |

| Junction to Case    | R <sub>thJC</sub> | -      | 16   | -    | K/W  | 1)2)                                       | P_4.3.1 |

| Junction to Ambient | R <sub>thJA</sub> | -      | 53   | -    | K/W  | <sup>1)3)</sup> 2s2p                       | P_4.3.2 |

| Junction to Ambient | R <sub>thJA</sub> | -      | 71   | -    | K/W  | <sup>1)3)</sup> 1s0p + 600 mm <sup>2</sup> | P_4.3.3 |

| Junction to Ambient | R <sub>thJA</sub> | -      | 83   | -    | K/W  | <sup>1)3)</sup> 1s0p + 300 mm <sup>2</sup> | P_4.3.4 |

1) Not subject to production test, specified by design

2) Specified  $R_{\text{thJC}}$  value is simulated at natural convection on a cold plate setup (all pins and the exposed pad are fixed to ambient temperature).  $T_A = 25^{\circ}$ C dissipates 1 W

#### **General product characteristics**

3) Specified R<sub>thJA</sub> value is according to JEDEC 2s2p (JESD 51-7) + (JESD 51-5) and JEDEC 1s0p (JESD 51-3) + heatsink area at natural convection on FR4 board; The device was simulated on a 76.2 x 114.3 x 1.5 mm board. The 2s2p board has 2 outer copper layers (2 x 70 µm Cu) and 2 inner copper layers (2 x 35 µm Cu), A thermal via (diameter = 0.3 mm and 25 µm plating) array was applied under the exposed pad and connected the first outer layer (top) to the first inner layer and second outer layer (bottom) of the JEDEC PCB. T<sub>A</sub> = 25°C, IC dissipates 1 W

Switching regulator

# 5 Switching regulator

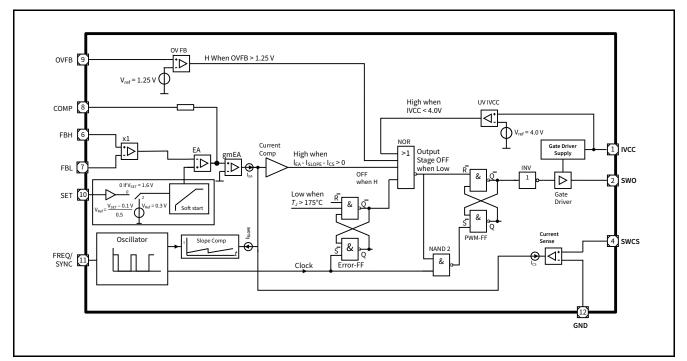

## 5.1 Description

The TLD5099EP regulator is suitable for Boost, Buck, Buck-Boost, SEPIC and Flyback configurations. The constant output current is especially useful for light emitting diode (LED) applications. The switching regulator function is implemented by a pulse width modulated (PWM) current mode controller.

The switching current mode controller uses the peak current through the external power switch and error in the output current to determine the appropriate pulse width duty cycle (on time) for constant output current. The current mode controller provides a modulated signal to an internal gate driver which drives an external n-channel enhancement mode metal oxide field effect transistor (MOSFET) power switch.

The current mode controller also has built-in slope compensation to prevent sub-harmonic oscillations which is a characteristic of current mode controllers operating at high duty cycles (>50% duty).

An additional built-in feature is an integrated soft start that limits the current through the inductor and external power switch during initialization. The soft start function gradually increases the inductor and switch current over  $t_{ss}$  (P\_5.2.9) to minimize potential overvoltage at the output.

Figure 4 Switching regulator block diagram

#### Switching regulator

# 5.2 Electrical characteristics

$V_{\rm IN}$  = 8 V to 34 V;  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

## Table 6 Electrical characteristics: Switching regulator

| Parameter                               | Symbol                                                       |       | Value | 5     | Unit | Note or                                                                                                                                                                                                 | Number  |

|-----------------------------------------|--------------------------------------------------------------|-------|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                         |                                                              | Min.  | Тур.  | Max.  |      | Test Condition                                                                                                                                                                                          |         |

| Regulator                               |                                                              |       |       | 1     |      |                                                                                                                                                                                                         |         |

| Feedback reference<br>voltage           | V <sub>REF</sub>                                             | 0.29  | 0.30  | 0.31  | V    | refer to <b>Figure 36</b><br>$V_{\text{REF}} = V_{\text{FBH}} - V_{\text{FBL}}$<br>$V_{\text{SET}} = 5 \text{ V}$<br>$I_{\text{LED}} = 350 \text{ mA}$<br>Differential signal<br>(not referred to GND)  | P_5.2.1 |

| Feedback reference<br>voltage           | V <sub>REF</sub>                                             | 0.057 | 0.06  | 0.063 | V    | refer to <b>Figure 36</b><br>$V_{\text{REF}} = V_{\text{FBH}} - V_{\text{FBL}}$<br>$V_{\text{SET}} = 0.4 \text{ V}$<br>$I_{\text{LED}} = 70 \text{ mA}$<br>Differential signal<br>(not referred to GND) | P_5.2.2 |

| Feedback reference<br>voltage offset    | V <sub>REF_offset</sub>                                      | _     | -     | 5     | mV   | refer to Figure 24<br>and Figure 36<br>$V_{REF} = V_{FBH} - V_{FBL}$<br>$V_{SET} = 0.1 V$<br>$V_{OUT} > V_{IN}$<br>Differential signal<br>(not referred to GND)                                         | P_5.2.3 |

| Voltage line<br>regulation              | $(\Delta V_{\rm REF}/V_{\rm REF})$<br>/ $\Delta V_{\rm IN}$  | -     | -     | 0.15  | %/V  | refer to <b>Figure 36</b><br>V <sub>IN</sub> = 8 V to 19 V;<br>V <sub>SET</sub> = 5 V;<br>I <sub>LED</sub> = 350 mA                                                                                     | P_5.2.4 |

| Voltage load<br>regulation              | (ΔV <sub>REF</sub> /V <sub>REF</sub> )<br>/ ΔI <sub>BO</sub> | -     | -     | 5     | %/A  | refer to Figure 36<br>$V_{SET} = 5 V;$<br>$I_{LED} = 100 \text{ to } 500 \text{ mA}$                                                                                                                    | P_5.2.5 |

| Switch peak<br>overcurrent<br>threshold | V <sub>SWCS</sub>                                            | 125   | 150   | 175   | mV   | $V_{\text{FBH}} = V_{\text{FBL}} = 5 \text{ V}$<br>$V_{\text{COMP}} = 3.5 \text{ V}$                                                                                                                    | P_5.2.6 |

| Maximum duty cycle                      | D <sub>MAX,fixed</sub>                                       | 91    | -     | -     | %    | Fixed frequency mode                                                                                                                                                                                    | P_5.2.7 |

| Maximum duty cycle                      | D <sub>MAX,sync</sub>                                        | 88    | -     | -     | %    | Synchronization mode                                                                                                                                                                                    | P_5.2.8 |

| Soft start ramp                         | t <sub>ss</sub>                                              | 350   | 1000  | 1500  | μs   | refer to <b>Figure 36</b><br>V <sub>SET</sub> = 5 V;<br>V <sub>REF</sub> rising from 5%<br>to 95% of typ. V <sub>REF</sub>                                                                              | P_5.2.9 |

## Switching regulator

| Parameter                              | Symbol               |      | Value | S    | Unit | Note or                                                                       | Number   |

|----------------------------------------|----------------------|------|-------|------|------|-------------------------------------------------------------------------------|----------|

|                                        |                      | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                                         |          |

| IFBH<br>Feedback high input<br>current | I <sub>FBH</sub>     | 38   | 46    | 54   | μA   | V <sub>FBH</sub> - V <sub>FBL</sub> = 0.3 V                                   | P_5.2.10 |

| IFBL<br>Feedback low input<br>current  | I <sub>FBL</sub>     | 15   | 21    | 27   | μΑ   | <i>V</i> <sub>FBH</sub> - <i>V</i> <sub>FBL</sub> = 0.3 V                     | P_5.2.11 |

| Switch current sense input current     | I <sub>SWCS</sub>    | 10   | 50    | 100  | μΑ   | V <sub>SWCS</sub> = 150 mV                                                    | P_5.2.12 |

| Input undervoltage<br>shutdown         | V <sub>IN,off</sub>  | 3.5  | -     | 4.5  | V    | V <sub>IN</sub> decreasing                                                    | P_5.2.13 |

| Input voltage<br>startup               | V <sub>IN,on</sub>   | -    | -     | 4.85 | V    | V <sub>IN</sub> increasing                                                    | P_5.2.14 |

| Gate driver for exte                   | rnal switch          |      | •     |      | •    |                                                                               | -        |

| Gate driver peak<br>sourcing current   | I <sub>SWO,SRC</sub> | -    | 380   | -    | mA   | <sup>1)</sup> $V_{SWO} = 1 V \text{ to } 4 V$<br>Current flows out of pin     | P_5.2.15 |

| Gate driver peak<br>sinking current    | I <sub>SWO,SNK</sub> | -    | 550   | -    | mA   | <sup>1)</sup> $V_{\rm SWO}$ = 4 V to 1 V                                      | P_5.2.16 |

| Gate driver output<br>rise time        | t <sub>R,SWO</sub>   | -    | 30    | 60   | ns   | <sup>1)</sup> $C_{L,SWO} = 3.3 \text{ nF};$<br>$V_{SWO} = 1 \text{ V to 4 V}$ | P_5.2.17 |

| Gate driver output<br>fall time        | t <sub>F,SWO</sub>   | -    | 20    | 40   | ns   | <sup>1)</sup> $C_{L,SWO} = 3.3 \text{ nF};$<br>$V_{SWO} = 4 \text{ V to 1 V}$ | P_5.2.18 |

| Gate driver output<br>voltage          | V <sub>swo</sub>     | 4.5  | -     | 5.5  | V    | <sup>1)</sup> $C_{L,SWO} = 3.3 \text{ nF}$                                    | P_5.2.19 |

## Table 6 Electrical characteristics: Switching regulator

1) Not subject to production test, specified by design

#### Switching oscillator and synchronization

# 6 Switching oscillator and synchronization

#### 6.1 Description

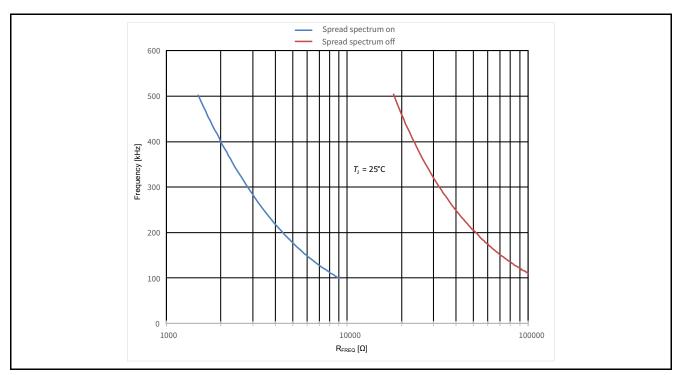

#### **RFREQ vs. switching frequency**

The internal oscillator is used to determine the switching frequency of the regulator. The switching frequency (from 100 kHz to 500 kHz) and the status of spread spectrum modulator can be selected with an external resistor referred to GND.

The range scale of the usable resistor is divided in two sections; for lower values of resistor it selects the switching frequency with the spread spectrum modulator "on", while for higher values of the range it selects the switching frequency with the spread spectrum modulator "off".

To set the desired switching frequency with spread spectrum modulator "off", the external resistor value is calculated by means of the formula shown below and is summarized in **Figure 7**.

$$R_{FREQ-SSMoff} = \frac{1}{(340 \cdot 10^{-12} \cdot f_{FREQ})^{1.13}}$$

To set the desired switching frequency with spread spectrum modulator "on", the external resistor value is calculated by means of the formula shown below.

(6.2)

(6.1)

$$R_{FREQ-SSMon} = \frac{1}{(600 \cdot 10^{-12} \cdot f_{FREQ})^{0.943}} - (600)$$

In addition, the oscillator is capable of changing from the frequency set by the external resistor to a synchronized frequency from an external clock source. If an external clock source is provided on the pin FREQ/SYNC, then the internal oscillator synchronizes to this external clock frequency and the boost regulator switches at the synchronized frequency. The synchronization frequency capture range is 250 kHz to 500 kHz.

Figure 5 Oscillator and synchronization block diagram

#### Switching oscillator and synchronization

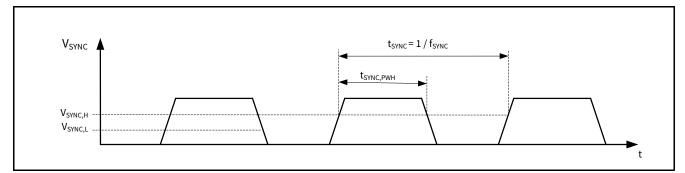

#### Figure 6 Synchronization timing diagram

#### 6.2 Electrical characteristics

$V_{IN}$  = 8 V to 34 V;  $T_J$  = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                                       | Symbol                |      | Value | S    | Unit | Note or<br>Test Condition                                     | Number  |

|-------------------------------------------------|-----------------------|------|-------|------|------|---------------------------------------------------------------|---------|

|                                                 |                       | Min. | Тур.  | Max. |      |                                                               |         |

| Oscillator                                      |                       |      |       |      |      |                                                               |         |

| Oscillator frequency                            | f <sub>FREQ</sub>     | 250  | 300   | 350  | kHz  | $R_{\rm FREQ}$ = 33 k $\Omega$                                | P_6.2.1 |

| Oscillator frequency<br>adjustment range        | f <sub>freq</sub>     | 100  | -     | 500  | kHz  | _                                                             | P_6.2.2 |

| FREQ / SYNC supply current                      | I <sub>FREQ</sub>     | -    | -     | 3    | mA   | $V_{\rm FREQ} = 0  \rm V$                                     | P_6.2.3 |

| Frequency voltage                               | V <sub>FREQ</sub>     | 0.56 | 0.6   | 0.64 | V    | $R_{\rm FREQ}$ = 33 k $\Omega$<br>( $f_{\rm FREQ}$ = 300 kHz) | P_6.2.4 |

| Synchronization                                 |                       |      |       |      |      |                                                               |         |

| Synchronization frequency capture range         | f <sub>SYNC</sub>     | 250  | -     | 500  | kHz  | -                                                             | P_6.2.5 |

| Synchronization signal high logic level valid   | V <sub>SYNC,H</sub>   | 3.0  | -     | -    | V    | 1)2)                                                          | P_6.2.6 |

| Synchronization signal<br>low logic level valid | V <sub>SYNC,L</sub>   | -    | -     | 0.8  | V    | 1)2)                                                          | P_6.2.7 |

| Synchronization signal logic high pulse width   | t <sub>sync,pwm</sub> | 200  | -     | -    | ns   | 1)2)                                                          | P_6.2.8 |

| Table 7 | Electrical characteristics: Oscillator and synchronization  |

|---------|-------------------------------------------------------------|

|         | Electrical characteristics. Oscillator and synthemotization |

1) Synchronization of external PWM "on" signal to falling edge

2) Not subject to production test, specified by design

*Note:* Maximum capacitor on pin FREQ / SYNC has to be less than 150 pF (including parasitics effect)

## Switching oscillator and synchronization

# 6.3 Typical performance characteristics of oscillator

| <b>R<sub>FREQ</sub> [k</b> Ω] | f <sub>sw</sub> [kHz] | Spread spectrum |

|-------------------------------|-----------------------|-----------------|

| 1.8                           | 435                   |                 |

| 2.2                           | 370                   |                 |

| 2.7                           | 311                   |                 |

| 3.3                           | 260                   | ON              |

| 3.9                           | 224                   |                 |

| 4.7                           | 188                   |                 |

| 5.6                           | 159                   |                 |

| 6.8                           | 132                   |                 |

| 8.2                           | 110                   |                 |

| 22                            | 422                   |                 |

| 27                            | 352                   |                 |

| 33                            | 295                   |                 |

| 39                            | 254                   | OFF             |

| 47                            | 216                   |                 |

| 56                            | 185                   |                 |

| 68                            | 156                   |                 |

| 82                            | 132                   |                 |

| Table 8 | Switching frequency f | w versus frequenc | y select resistor to GND R <sub>FREO</sub> |

|---------|-----------------------|-------------------|--------------------------------------------|

|         |                       | VV                |                                            |

#### Switching oscillator and synchronization

# 6.4 Spread spectrum

The spread spectrum modulation technique significantly improves the EMI performance in the lower frequency range of the spectrum (e.g. f < 30 MHz).

By using the spread spectrum technique, it is possible to optimize the input and output filters to fulfill the EMC requirements. Moreover, the need for low ESR input capacitors is relaxed because the input capacitor series resistor is important for the low frequency filter characteristic. This can be an economic benefit if there is a strong requirement for average limits.

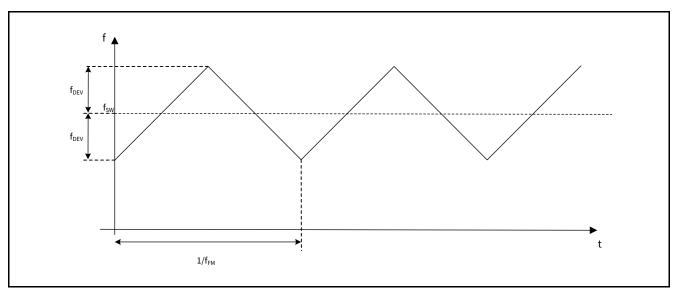

The modulation frequency  $f_{FM}$ , (P\_6.4.1) is internally fixed, while the modulation depth is a fraction of the switching frequency  $f_{DEV}$ , (P\_6.4.2).

Figure 8 Spread spectrum modulator

| Parameter            | Symbol           |      | Value | S    | Unit | Note or                                                                                 | Number  |

|----------------------|------------------|------|-------|------|------|-----------------------------------------------------------------------------------------|---------|

|                      |                  | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                                                   |         |

| Modulation frequency | f <sub>FM</sub>  | -    | 7     | -    | kHz  | 1)                                                                                      | P_6.4.1 |

|                      |                  |      |       |      |      | $1.5 \text{ k}\Omega \leq R_{\text{FREQ}} \leq 9 \text{ k}\Omega$                       |         |

| Modulation depth     | f <sub>DEV</sub> | -    | 15    | -    | %    | 1)                                                                                      | P_6.4.2 |

|                      | 52.              |      |       |      |      | <b>Related to switching</b>                                                             |         |

|                      |                  |      |       |      |      | frequency f <sub>FREQ</sub>                                                             |         |

|                      |                  |      |       |      |      | frequency $f_{\text{FREQ}}$<br>1.5 k $\Omega \le R_{\text{FREQ}} \le 9 \text{ k}\Omega$ |         |

1) Not subject to production test, specified by design

Enable and dimming function

# 7 Enable and dimming function

# 7.1 Description

Enable and dimming functions are related on the status of the pin **EN / PWMI**.

For different values of the voltage on this pin, the device has different behaviors as described below:

- If a valid logic "low" is present (it means V<sub>EN/PWMI</sub> < V<sub>EN/PWMI,OFF</sub>), the device is powered off (refer to Chapter 7.2)

- If a valid logic "high" is present (it means V<sub>EN/PWMI</sub> > V<sub>EN/PWMI,ON</sub>), the device is powered on and it can accept a digital PWM (refer to Chapter 7.3)

- If an analog signal is in between V<sub>EN/PWMI,DC\_0</sub> and V<sub>EN/PWMI,DC\_100</sub>, the device and the embedded PWM engine are powered on (refer to Chapter 7.4)

## 7.2 Enable function

The enable function powers the device on or off. At the start-up or if a valid logic low signal on enable pin **EN / PWMI** for a time longer than  $t_{\text{EN,OFF,DEL}}$  (P\_7.5.5) powers off the device; in this case, the current consumption is less than  $I_{\text{Q_OFF}}$  (P\_7.5.23).

At the start-up, to fully activate the device, a valid logic high has to be present while the **IVCC** reaches the level  $V_{\text{IVCC,RTH,i}}$  (P\_8.2.8)

The enable function features an integrated pull down resistor  $R_{\text{EN_INT}}$  (P\_7.5.12), which ensures that the IC is shut down and the power switch is off in case the enable pin EN is left open.

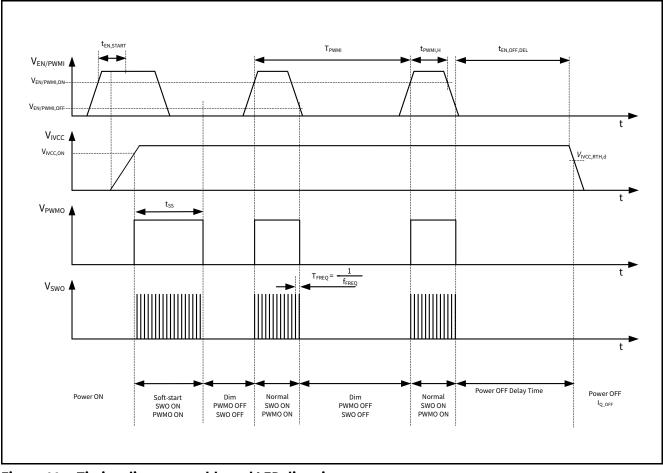

## 7.3 Digital PWM dimming function

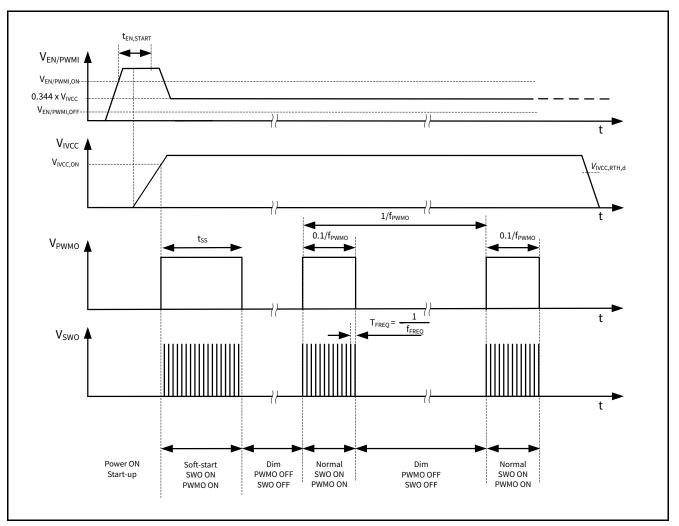

The digital PWM dimming function is activated when a valid logic high/low pattern is present on **EN / PWMI**. The **EN / PWMI** signal enables and disable the gate drivers (in accordance with the logic signal present in the pin) and modulates the average current on the load. The internal blocks involved in this function are shown in **Figure 9**.

When PWM logic is activated, the device differentiates between enable off and PWM dimming signal by requiring the enable off at the **EN / PWMI** pin to stay low for the **Enable turn off delay time** (P\_7.5.5). The pattern and the timing constraints are shown in **Figure 10**.

Figure 9 Block diagram and simplified application circuit enable and LED dimming

#### **Enable and dimming function**

Figure 10 Timing diagram enable and LED dimming

Note: The slope of the  $V_{IVCC}$  is related to the filter capacitor. Therefore its steady state condition can be achieved after  $t_{EN,START}$ .

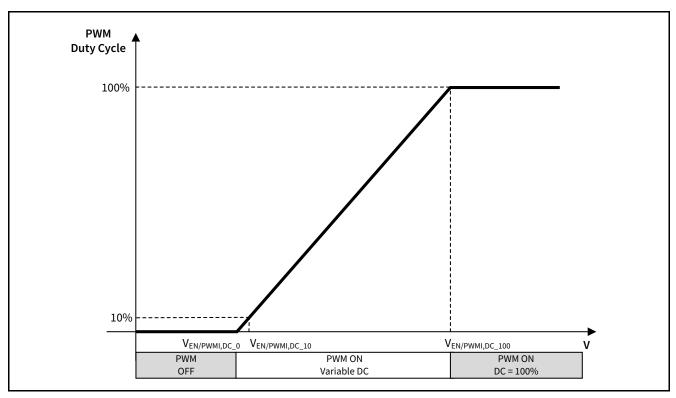

#### 7.4 Embedded PWM dimming function

The embedded PWM dimming function (PWM engine) is activated in the voltage window in between a valid logic "low" level and a valid logic "high" level (P\_7.5.8. and P\_7.5.9, respectively). In this voltage window, a duty cycle (DC) on PWMO output is generated according to the analog voltage applied on the pin. The desired DC value can be calculated by the following formula:

$$DC[\%] = \frac{V_{EN/PWMI} - 0.32 \cdot V_{IVCC}}{0.24 \cdot V_{IVCC}} \cdot 100[\%]$$

On calculation of the  $V_{\text{EN/PWMI}}$  voltage, the pull-down resistor (P\_7.5.12) that features the shut down when the pin is left open, has to be taken into account. If this value is taken into account and a voltage divider between IVCC and ground is used (**Figure 12**), the DC can be described by the following formula:

$$DC[\%] = \frac{\frac{R_B \parallel R_{EN_{INT}}}{R_B \parallel R_{EN_{INT}} + R_A} - 0.32}{0.24} \cdot 100[\%]$$

Datasheet

(7.1)

(7.2)

# infineon

# LITIX<sup>™</sup> Power TLD5099EP

#### **Enable and dimming function**

The frequency of PWMO signal is also programmable by changing the value of the capacitor on the pin **FPWM**; two internal current generators charge and discharge the capacitor and this signal supplies an internal divider to produce the desired frequency (**Figure 12**).

Figure 11 Duty cycle variation as a function of V<sub>EN/PWMI</sub>

#### **Enable and dimming function**

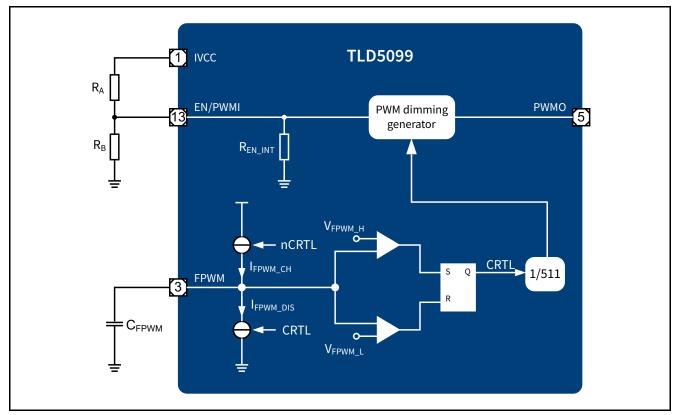

Figure 12 Block diagram of PWM engine

The relation between PWM frequency and the capacitor is described by the following formula:

$$f_{PWMO} = \frac{1}{511 \cdot C_{FPWM} \cdot (V_{FPWM_{-}H} - V_{FPWM_{-}L}) \cdot \left(\frac{1}{|I_{FPWM_{-}CH}|} + \frac{1}{|I_{FPWM_{-}DIS}|}\right)}$$

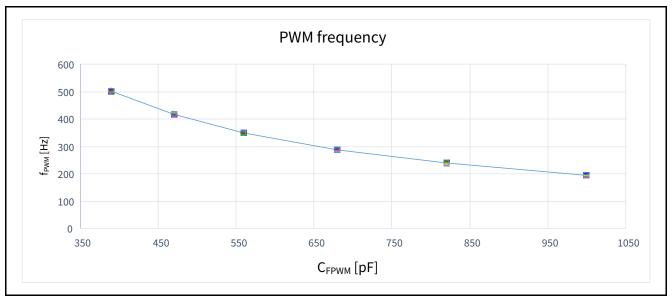

In the typical case, the variation of  $f_{PWMO}$  as a function of  $C_{FPWM}$  is shown in **Figure 13**. To have a small impact of parasitic capacitance, it is suggested to put this capacitor quite close to the pin **FPWM**. The signal produced by the PWM engine (with the desired DC and frequency) enables and disables the gate drivers and modulates the average current on the load.

(7.3)

#### **Enable and dimming function**

Figure 13 PWM frequency variation as a function of C<sub>FPWM</sub>

| ruste 10 commercial capacitor c <sub>FPWM</sub> values vs. 1 white queries (FPWMO |                         |  |  |  |  |  |

|-----------------------------------------------------------------------------------|-------------------------|--|--|--|--|--|

| С <sub>FPWM</sub> [pF]                                                            | f <sub>FPWMO</sub> [Hz] |  |  |  |  |  |

| 390                                                                               | 502                     |  |  |  |  |  |

| 470                                                                               | 416                     |  |  |  |  |  |

| 560                                                                               | 349                     |  |  |  |  |  |

| 680                                                                               | 288                     |  |  |  |  |  |

| 820                                                                               | 239                     |  |  |  |  |  |

| 1000                                                                              | 196                     |  |  |  |  |  |

|                                                                                   |                         |  |  |  |  |  |

Table 10Commercial capacitor  $C_{FPWM}$  values vs. PWM frequency  $f_{FPWMO}$

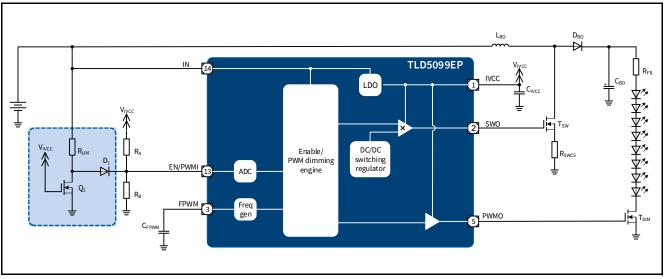

As reported in **Chapter 7.2**, during the start-up (and only during this phase), the device needs a valid logic high on the pin **EN / PWMI** to wake-up the internal logic. The valid logic high on pin EN/PWMI has to be granted until the voltage of IVCC reaches its steady state (P\_8.2.8). A proposal circuit to obtain this behavior is shown in **Figure 14** and the necessary added components are highlighted in the blue box.

It acts as follows:

- at start-up Q1 is off and  $V_{\rm IN}$  supplies pin **EN / PWMI** through  $R_{\rm LIM}$  and it starts up the circuit

- when the TLD5099EP is ready to work (e.g. the IVCC has reached its steady state), the IVCC switches on Q1 (the current through Q1 is limited by R<sub>LIM</sub>)

- then, the voltage on pin **EN / PWMI** given by the resistor divider  $R_A$ ,  $R_B$  provides the desired duty cycle

The diode D1 ensures the proper behavior for the biasing.

This start-up circuit is needed only if embedded PWM dimming function is used. Proper dimensioning of  $R_{\text{LIM}}$ and voltage divider ( $R_{\text{A}}$  and  $R_{\text{B}}$ ) resistors is needed to ensure the start-up of the device. As described above,  $V_{\text{EN/PWMI}}$  has to be higher than  $V_{\text{EN/PWMI,ON}}$  during start-up. Fixing  $R_{\text{LIM}}$ ,  $R_{\text{B}}$  can be calculated as follows:

$$R_B > \frac{V_{EN/PWMI,ON}}{\left(V_{IN} - V_{D1} - V_{EN/PWMI,ON}\right)} \cdot R_{LIM}$$

Datasheet

(7.4)

#### Enable and dimming function

Then,  $R_A$  has to be calculated in accordance with the desired duty cycle.

Figure 14 Block diagram of analog PWM dimming with simplified application circuit

Figure 15 Timing diagram enable and LED dimming with PWM engine

#### Enable and dimming function

# 7.5 Electrical characteristics

$V_{\rm IN}$  = 8 V to 34 V;  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Table 11 Electri | cal characteristics: Enable and dimming |

|------------------|-----------------------------------------|

|------------------|-----------------------------------------|

| Parameter                                    | Symbol                     | Values                      |                            |                             | Unit | Note or                                                                    | Number   |  |

|----------------------------------------------|----------------------------|-----------------------------|----------------------------|-----------------------------|------|----------------------------------------------------------------------------|----------|--|

|                                              |                            | Min.                        | Тур.                       | Max.                        |      | Test Condition                                                             |          |  |

| Enable / PWM Input                           |                            |                             |                            |                             |      |                                                                            |          |  |

| Enable/PWMI<br>turn on threshold             | V <sub>EN/PWMI,ON</sub>    | 3                           | -                          | -                           | V    | -                                                                          | P_7.5.1  |  |

| Enable/PWMI<br>turn off threshold            | V <sub>EN/PWMI,OFF</sub>   | -                           | -                          | 0.8                         | V    | -                                                                          | P_7.5.2  |  |

| Enable/PWMI<br>high input current            | I <sub>EN/PWMI,H</sub>     | -                           | -                          | 100                         | μA   | $V_{\rm EN/PWMI} = 16.0  \rm V$                                            | P_7.5.3  |  |

| Enable/PWMI<br>low input current             | I <sub>EN/PWMI,L</sub>     | -                           | 0.1                        | 1                           | μΑ   | $V_{\rm EN/PWMI} = 0.5 V$                                                  | P_7.5.4  |  |

| Enable turn off<br>delay time                | t <sub>en,off,del</sub>    | 8                           | 10                         | 12                          | ms   | -                                                                          | P_7.5.5  |  |

| PWMI min. duty time                          | t <sub>PWMI,H</sub>        | 6                           | -                          | -                           | μs   | -                                                                          | P_7.5.6  |  |

| Enable startup time                          | t <sub>en,start</sub>      | 100                         | -                          | -                           | μs   | 1)                                                                         | P_7.5.7  |  |

| PWM engine min.<br>voltage                   | V <sub>EN/PWM,DC_0</sub>   | 0.313<br>*V <sub>IVCC</sub> | 0.32<br>*V <sub>IVCC</sub> | -                           | V    | PWM engine sets DC<br>PWMO = 0%                                            | P_7.5.8  |  |

| PWM engine max.<br>voltage                   | V <sub>EN/PWM,DC_100</sub> | -                           | 0.56<br>*V <sub>IVCC</sub> | 0.571<br>*V <sub>IVCC</sub> | V    | PWM engine sets DC<br>PWMO = 100%                                          | P_7.5.9  |  |

| PWM engine DC                                | DC <sub>PWMO,DC_10%</sub>  | 8.5                         | 10                         | 11.5                        | %    | $V_{\rm EN/PWM} = 0.344 * V_{\rm IVCC}$                                    | P_7.5.10 |  |

| PWM frequency range                          | f <sub>PWMO</sub>          | 100                         | _                          | 500                         | Hz   | 1)                                                                         | P_7.5.11 |  |

| Enable / PWMI internal<br>pull-down resistor | R <sub>en_int</sub>        | 0.7                         | 1.35                       | 2                           | MΩ   | <sup>1)</sup><br>V <sub>EN/PWMI</sub> = 1.5 V 3 V                          | P_7.5.12 |  |

| FPWM charging<br>current                     | I <sub>FPWM_CH</sub>       | -150                        | -200                       | -250                        | μΑ   | 1)                                                                         | P_7.5.13 |  |

| FPWM discharging<br>current                  | I <sub>FPWM_DIS</sub>      | 150                         | 200                        | 250                         | μΑ   | 1)                                                                         | P_7.5.14 |  |

| FPWM voltage rising<br>threshold             | V <sub>FPWM_H</sub>        | 1.9                         | 2                          | 2.1                         | V    | 1)                                                                         | P_7.5.15 |  |

| FPWM voltage falling<br>threshold            | V <sub>FPWM_L</sub>        | 0.9                         | 1                          | 1.1                         | V    | 1)                                                                         | P_7.5.16 |  |

| PWM frequency                                | f <sub>PWMO</sub>          | 265                         | 350                        | 435                         | Hz   | <sup>1)</sup> $C_{\rm FPWM}$ = 560 pF                                      | P_7.5.17 |  |

| Gate driver for dimmi                        |                            |                             |                            |                             |      |                                                                            | <u>.</u> |  |

| PWMO gate driver<br>peak sourcing current    | I <sub>PWMO,SRC</sub>      | -                           | 230                        | -                           | mA   | <sup>1)</sup> $V_{PWMO} = 1 V \text{ to } 4 V$<br>Current flows out of pin | P_7.5.18 |  |

| PWMO gate driver<br>peak sinking current     | I <sub>PWMO,SNK</sub>      | _                           | 370                        | -                           | mA   | <sup>1)</sup> $V_{\rm PWMO} = 4  \rm V  to  1  \rm V$                      | P_7.5.19 |  |

#### **Enable and dimming function**

## Table 11 Electrical characteristics: Enable and dimming

| Parameter                                      | Symbol              |      | Values |      | Unit | Note or                                                                                                                                                                             | Number   |

|------------------------------------------------|---------------------|------|--------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                |                     | Min. | Тур.   | Max. |      | Test Condition                                                                                                                                                                      |          |

| PWMO gate driver output rise time              | t <sub>r,pwmo</sub> | -    | 50     | 100  | ns   | <sup>1)</sup> $C_{L,PWMO} = 3.3 \text{ nF};$<br>$V_{PWMO} = 1 \text{ V to 4 V}$                                                                                                     | P_7.5.20 |

| PWMO gate driver output fall time              | t <sub>F,PWMO</sub> | -    | 30     | 60   | ns   | <sup>1)</sup> $C_{L,PWMO} = 3.3 \text{ nF};$<br>$V_{PWMO} = 4 \text{ V to 1 V}$                                                                                                     | P_7.5.21 |

| PWMO gate driver output voltage                | V <sub>PWMO</sub>   | 4.5  | -      | 5.5  | V    | <sup>1)</sup> $C_{L,PWMO} = 3.3 \text{ nF}$                                                                                                                                         | P_7.5.22 |

| <b>Current consumption</b>                     |                     | L.   |        |      |      | ·                                                                                                                                                                                   | ·        |

| Current consumption, shutdown mode             | I <sub>Q_OFF</sub>  | -    | -      | 15   | μA   | $V_{\rm EN/PWMI} = 0.5 V;$<br>$T_{\rm J} \le 105^{\circ}{\rm C};$<br>$V_{\rm IN} = 16 V$                                                                                            | P_7.5.23 |

| Current consumption, active mode <sup>2)</sup> | I <sub>Q_ON</sub>   | -    | -      | 7    | mA   | <sup>2)</sup> $V_{\text{EN/PWMI}} \ge 4.75 \text{ V};$<br>$R_{\text{FREQ}} = 33 \text{ k}\Omega$<br>$I_{\text{BO}} = 0 \text{ mA};$<br>$V_{\text{SWO}} = 0\% \text{ duty}$<br>cycle | P_7.5.24 |

1) Not subject to production test, specified by design

2) Dependency on switching frequency and gate charge of external switches

**Linear regulator**

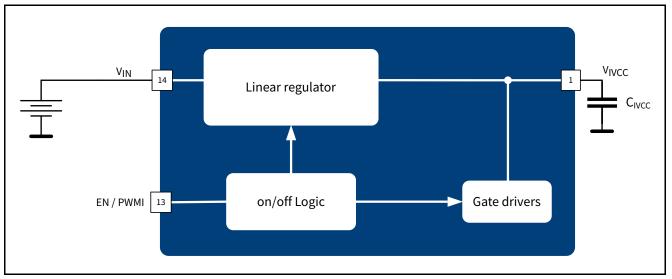

# 8 Linear regulator

# 8.1 Description

The internal linear voltage regulator supplies the internal gate drivers with a typical voltage of 5 V and current up to  $I_{\text{LIM,min}}$  (P\_8.2.2). An external output capacitor with ESR lower than  $R_{\text{IVCC,ESR}}$  (P\_8.2.5) is required on pin IVCC for stability and buffering transient load currents. During normal operation the external MOSFET switches will draw transient currents from the linear regulator and its output capacitor. Proper sizing of the output capacitor must be considered to supply sufficient peak current to the gate of the external MOSFET switches.

#### Integrated undervoltage protection for the external switching MOSFET

An integrated undervoltage reset threshold circuit monitors the linear regulator output voltage ( $V_{IVCC}$ ) and resets the device in case the output voltage falls below the IVCC undervoltage reset switch off threshold ( $V_{IVCC,RTH,d}$ ). The undervoltage reset threshold for the IVCC pin helps to protect the external switches from excessive power dissipation by ensuring the gate drive voltage is sufficient to enhance the gate of an external logic level n-channel MOSFET.

Figure 16 Voltage regulator block diagram and simplified application circuit

#### Linear regulator

## 8.2 Electrical characteristics

$V_{IN}$  = 8 V to 34 V;  $T_J$  = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                                          | Symbol                  |      | Value | 5    | Unit | Note or                                                                                        | Number  |

|----------------------------------------------------|-------------------------|------|-------|------|------|------------------------------------------------------------------------------------------------|---------|

|                                                    |                         | Min. | Тур.  | Max. |      | Test Condition                                                                                 |         |

| Output voltage                                     | V <sub>IVCC</sub>       | 4.85 | 5     | 5.15 | V    | $6 V \le V_{\rm IN} \le 45 V$ $0.1 \text{ mA} \le I_{\rm IVCC} \le 40 \text{ mA}$              | P_8.2.1 |

| Output current<br>limitation                       | / <sub>LIM</sub>        | 51   | -     | 90   | mA   | $V_{\rm IN} = 13.5 \text{ V}$<br>$V_{\rm IVCC} = 4.5 \text{ V}$<br>Current flows out of<br>pin | P_8.2.2 |

| Drop out voltage                                   | V <sub>DR</sub>         | -    | -     | 0.5  | V    | V <sub>IN</sub> = 4.5 V<br>V <sub>IVCC</sub> = 25 mA                                           | P_8.2.3 |

| IVCC buffer<br>capacitor                           | C <sub>IVCC</sub>       | 0.47 | 1     | 100  | μF   | 1)2)3)                                                                                         | P_8.2.4 |

| IVCC buffer<br>capacitor ESR                       | R <sub>IVCC, ESR</sub>  | -    | -     | 0.5  | Ω    | 1)2)                                                                                           | P_8.2.5 |

| Undervoltage reset<br>headroom                     | V <sub>IVCC,HDRM</sub>  | 100  | -     | -    | mV   | V <sub>IVCC</sub> decreasing<br>V <sub>IVCC</sub> - V <sub>IVCC,RTH,d</sub>                    | P_8.2.6 |

| IVCC undervoltage<br>reset switch-off<br>threshold | V <sub>IVCC,RTH,d</sub> | 3.6  | -     | 4.0  | V    | <sup>4)</sup> V <sub>IVCC</sub> decreasing                                                     | P_8.2.7 |

| IVCC undervoltage<br>reset switch-on<br>threshold  | V <sub>IVCC,RTH,i</sub> | -    | -     | 4.5  | V    | V <sub>IVCC</sub> increasing                                                                   | P_8.2.8 |

Table 12 Electrical characteristics: Line regulator

1) Not subject to production test, specified by design

2) Minimum value given is needed for regulator stability; application might need higher capacitance than the minimum

3) If embedded PWM engine is used, a 4.7 µF value has to be chosen as a minimum

4) Selection of external switching MOSFET is crucial and the V<sub>IVCC,RTH,d min</sub>. as worst case the threshold voltage of MOSFET must be considered

Protection and diagnostic functions

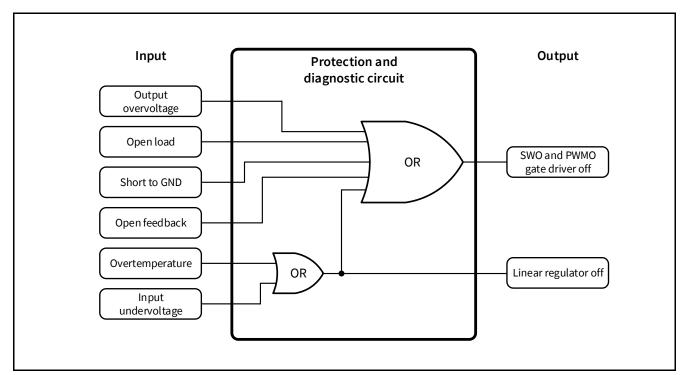

# 9 Protection and diagnostic functions

## 9.1 Description

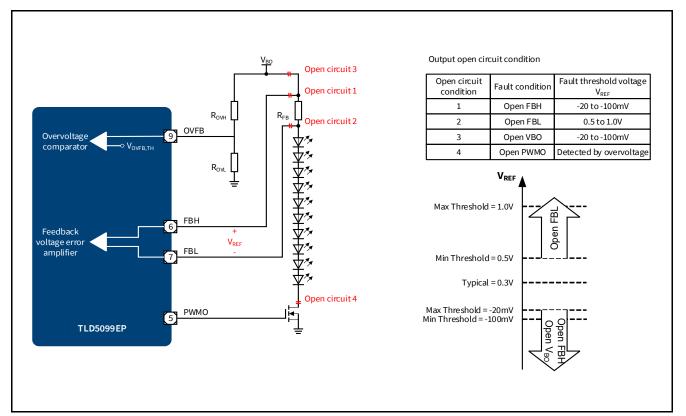

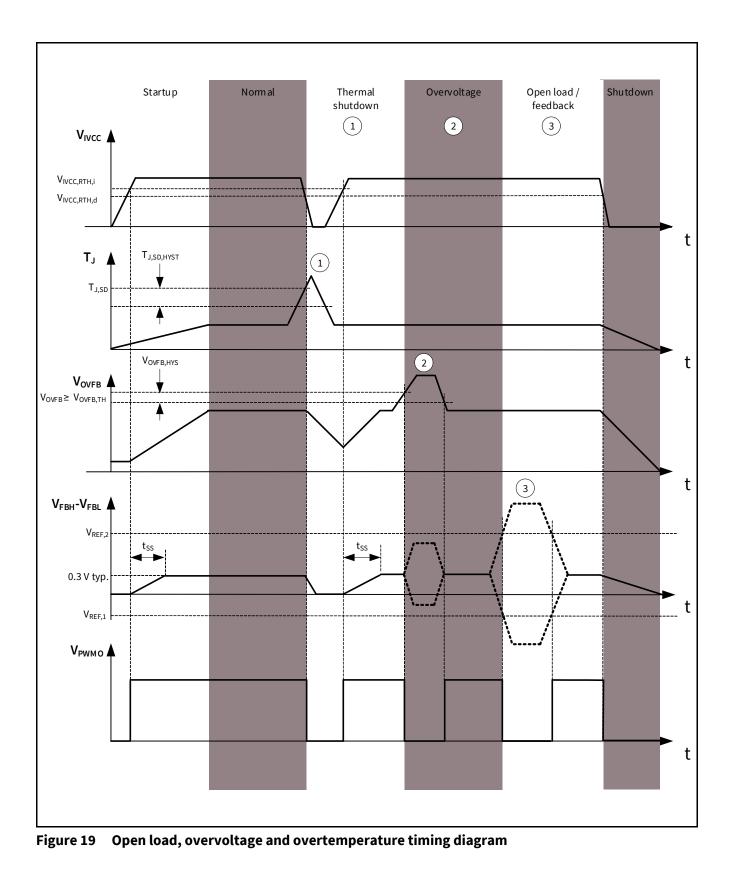

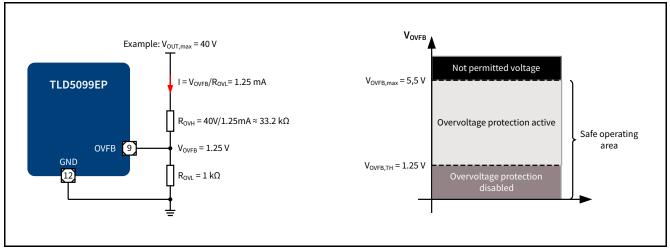

The TLD5099EP has integrated circuits to diagnose and protect against output overvoltage, open load, open feedback and overtemperature faults. Additionally the FBH and FBL potential is monitored and in case the LED load is shorted to GND (see description **Figure 22**) the regulator stops the operation and protects the system. In case any of the six fault conditions occur the PWMO and SWO signal will change to an active logic "low" signal to communicate that a fault has occurred, while IVCC shutdown occurs only in case of overtemperature or input undervoltage (detailed overview in **Figure 17** and **Table 13** below). **Figure 18** illustrates the various open load and open feedback conditions. In case of an overtemperature condition the integrated thermal shutdown function turns off the gate drivers and internal linear voltage regulator. The typical junction shutdown is an integrated protection function designed to prevent IC destruction and is not intended for continuous use in normal operation (**Figure 20**). To calculate the proper overvoltage protection resistor values an example is given in **Figure 21**.

Figure 17 Protection and diagnostic function block diagram

#### **Protection and diagnostic functions**

| Table 13 D | Diagnosis | truth | table <sup>1)</sup> |

|------------|-----------|-------|---------------------|

|------------|-----------|-------|---------------------|

| Input                 |       |     | Output     |          |  |

|-----------------------|-------|-----|------------|----------|--|

| Condition             | Level | SWO | PWMO       | IVCC     |  |

| Overvoltage at output | False | Sw  | High or Sw | Active   |  |

|                       | True  | Low | Low        | Active   |  |

| Open load             | False | Sw  | High or Sw | Active   |  |

|                       | True  | Low | Low        | Active   |  |

| Short to GND at LED   | False | Sw  | High or Sw | Active   |  |

| chain                 | True  | Low | Low        | Active   |  |

| Open feedback         | False | Sw  | High or Sw | Active   |  |

|                       | True  | Low | Low        | Active   |  |

| Overtemperature       | False | Sw  | High or Sw | Active   |  |

|                       | True  | Low | Low        | Shutdown |  |

| Undervoltage at input | False | Sw  | High or Sw | Active   |  |

|                       | True  | Low | Low        | Shutdown |  |

1) Sw = Switching; False = Condition does NOT exist; True = Condition does exist

Figure 18 Open Load and open feedback conditions

# **Protection and diagnostic functions**

# **Protection and diagnostic functions**

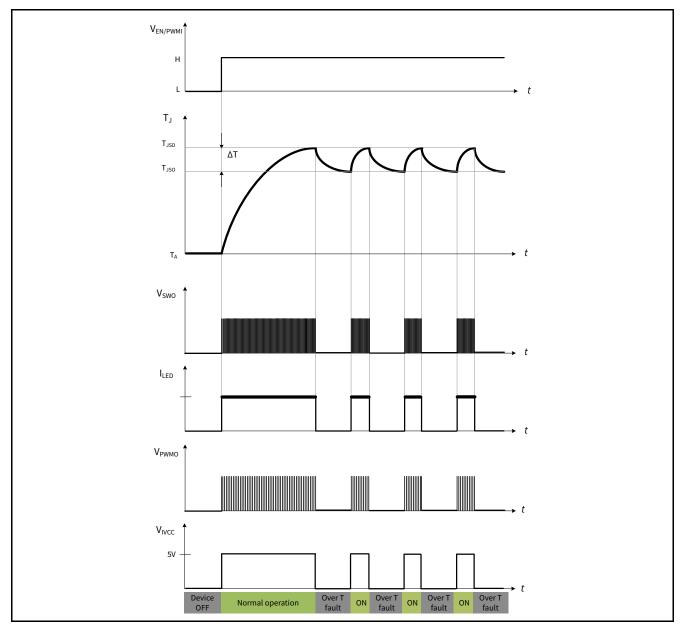

Figure 20 Device overtemperature protection behavior

#### Protection and diagnostic functions

Figure 21 Overvoltage protection description

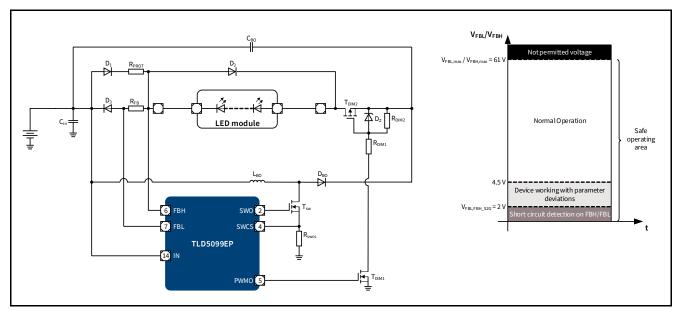

#### Short to GND protection for high-side return applications (B2B) from Figure 32 and Figure 33

The FBH and FBL pins features a short to GND detection threshold ( $V_{\text{FBL,FBH}_S2G}$ ). If the potential on these pins is below this threshold the device stops its operation. This means that the PWMO signal changes to inactive state ("low" potential) and the corresponding p-channel ( $T_{\text{DIM2}}$ ) is switched off accordingly and protects the LED chain. For the B2B application some external components are needed to ensure a "low" potential during a short circuit event.  $D_1$  and  $D_2$  are low power diodes (BAS70) and the resistor  $R_{\text{PROT}}$  (10 k $\Omega$ ) is needed to limit the current through this path. The diode  $D_3$  should be a high power diode and is needed to protect the  $R_{\text{FB}}$  and the FBH and FBL pins in case of an short circuit to GND event. This short circuit detection and protection concept considers potential faults for LED chains (LED modules) which are separated from the ECU via two wires (at the beginning and at the end of the LED chain). If the short circuit condition disappears, the device will re-start with a soft start.

Figure 22 Short circuit to GND protection

#### Protection and diagnostic functions

## 9.2 Electrical characteristics

$V_{IN}$  = 8 V to 34 V;  $T_J$  = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

#### Table 14 Electrical characteristics: Protection and diagnosis

| Parameter                                                        | Symbol                   | Values  |      |      | Unit | Note or                                                                                                | Number  |

|------------------------------------------------------------------|--------------------------|---------|------|------|------|--------------------------------------------------------------------------------------------------------|---------|

|                                                                  |                          | Min.    | Тур. | Max. |      | <b>Test Condition</b>                                                                                  |         |

| Short circuit protectio                                          | on                       | 1       | I    | I    |      |                                                                                                        | I       |

| FBH and FBL short-<br>circuit fault sensing<br>common mode range | V <sub>fbl,fbh_s2g</sub> | 1.5     | -    | 2    | V    | refer to <b>Figure 22</b><br>$V_{\text{FBH}} = V_{\text{FBL}}$<br>decreasing                           | P_9.2.1 |

| Temperature protecti                                             | on                       |         |      |      |      |                                                                                                        |         |

| Overtemperature shutdown                                         | T <sub>J,SD</sub>        | 160     | 175  | 190  | °C   | <sup>1)</sup> refer to <b>Figure 20</b>                                                                | P_9.2.2 |

| Overtemperature shutdown hystereses                              | T <sub>J,SD,HYST</sub>   | -       | 15   | -    | °C   | 1)                                                                                                     | P_9.2.3 |

| Overvoltage protectio                                            | n                        | 1       | I    | I    |      | -                                                                                                      |         |

| Output overvoltage<br>feedback threshold<br>increasing           | V <sub>ovfb,th</sub>     | 1.21    | 1.25 | 1.29 | V    | refer to Figure 21                                                                                     | P_9.2.4 |

| Output overvoltage<br>feedback hysteresis                        | V <sub>ovfb,hys</sub>    | 50      | -    | 150  | mV   | <sup>1)</sup> Output voltage decreasing                                                                | P_9.2.5 |

| Overvoltage reaction time                                        | t <sub>ovprr</sub>       | 2       | -    | 10   | μs   | Output voltage decreasing                                                                              | P_9.2.6 |

| Overvoltage feedback input current                               | I <sub>OVFB</sub>        | -1      | 0.1  | 1    | μA   | V <sub>OVFB</sub> = 1.25 V                                                                             | P_9.2.7 |

| Open load and open fe                                            | edback diag              | nostics |      | ·    |      |                                                                                                        |         |

| Open load/feedback<br>threshold                                  | V <sub>REF,1,3</sub>     | -100    | -    | -20  | mV   | refer to <b>Figure 18</b><br>$V_{\text{REF}} = V_{\text{FBH}} - V_{\text{FBL}}$<br>Open circuit 1 or 3 | P_9.2.8 |

| Open feedback<br>threshold                                       | V <sub>REF,2</sub>       | 0.5     | -    | 1    | V    | V <sub>REF</sub> = V <sub>FBH</sub> - V <sub>FBL</sub><br>Open circuit 2                               | P_9.2.9 |

1) Specified by design; not subject to production test

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

Analog Dimming

# 10 Analog Dimming

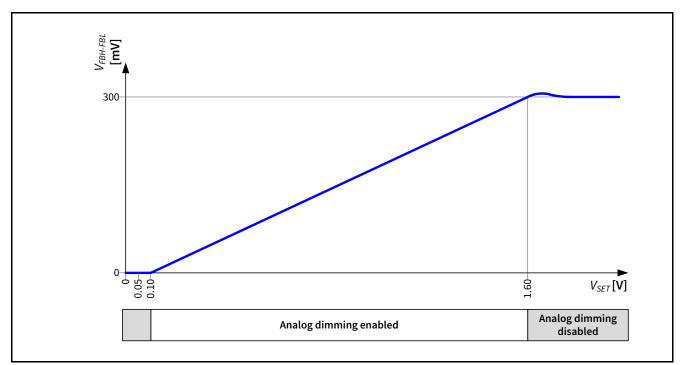

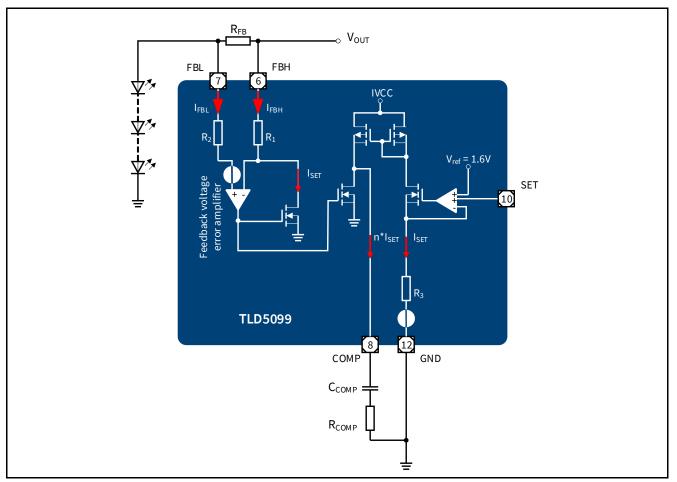

The SET pin influences the feedback voltage error amplifier by generating an internal current accordingly to its voltage ( $V_{SET}$ ). If the analog dimming feature is not needed, this pin must be connected to IVCC or external voltage supply higher than 1.6 V. Different application scenarios are described in **Figure 25**. This pin can also go outside of the ECU for instance if a thermistor is connected on a separated LED module and the analog dimming input is used to thermally protect the LEDs. For reverse battery protection of this pin an external series resistor should be placed to limit the current.

# 10.1 Purpose of Analog Dimming

- It is difficult for LED manufacturers to deliver LEDs which have the same brightness, colorpoint and forward voltage class. Due to this relatively wide spread of the crucial LED parameters automotive customers order LEDs from one or maximum two different colorpoint classes. The LED manufacturer must preselect the LEDs to deliver the requested colorpoint class. These preselected LEDs are matched in terms of the colorpoint but a variation of the brightness remains. To correct the brightness deviation an analog dimming feature is needed. The mean LED current can be adjusted by applying an external voltage V<sub>SET</sub> at the SET pin.

- 2. If the DC/DC application is separated from the LED loads the ECU manufacturers aim is to develop one hardware which should be able to handle different load current conditions (e.g. 80 mA to 400 mA) to cover different applications. To achieve this average LED current adjustment the analog dimming is a crucial feature.

## 10.2 Description

#### **Application Example**

Desired LED current = 400 mA. For the calculation of the correct feedback resistor  $R_{FB}$  the following equation can be used: This formula is valid if the analog dimming feature is disabled and  $V_{SET} > 1.6$  V.

$$I_{LED} = \frac{V_{REF}}{R_{FB}} \rightarrow R_{FB} = \frac{V_{REF}}{I_{LED}} \rightarrow R_{FB} = \frac{0.3V}{400mA} = 750m\Omega$$

(10.1)

Related electrical parameter is guaranteed with  $V_{SET} = 5 \text{ V}$  (P\_5.2.1) A decrease of the average LED current can be achieved by controlling the voltage at the SET pin ( $V_{SET}$ ) between 0.1 V and 1.6 V. The mathematical relation is given in the formula below:

$$I_{LED} = \frac{V_{SET} - 0.1V}{5 \cdot R_{FB}}$$

(10.2)

Refer to the concept drawing in Figure 24.

If  $V_{\text{SET}}$  is equal to or smaller than 50 mV, the switching activity is stopped and  $I_{\text{LED}} = 0$  A

#### Analog Dimming

Figure 23 Basic relationship between V<sub>REF</sub> and V<sub>SET</sub> voltage

Figure 24 Concept drawing analog dimming

# infineon

#### Analog Dimming

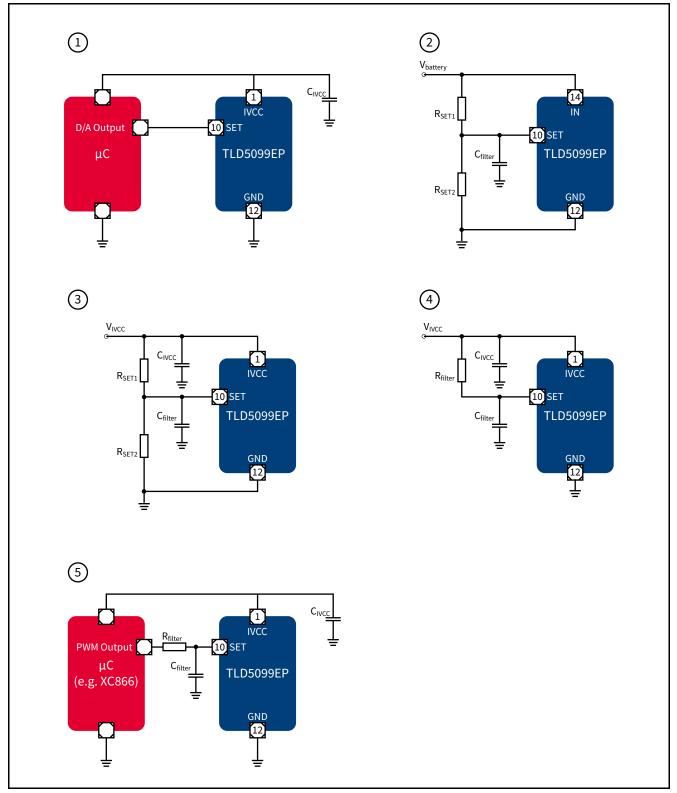

#### Multi-purpose usage of the analog dimming feature

- 1. A  $\mu$ C integrated digital analog converter (DAC) output or a stand alone DAC can be used to supply the SET pin of the TLD5099EP. The integrated voltage regulator ( $V_{IVCC}$ ) can be used to supply the  $\mu$ C or external components if the current consumption does not exceed 20 mA.