# ANALOG DEVICES

# Low Cost, High Speed, IC Operational Amplifier

FEATURES

Me

High Slew Rate:  $70V/\mu s$ Wide Bandwidth: 12MHz $60^{\circ}$  Phase Margin (At Unity Gain Crossover) Drives 300pF Load Guaranteed Low Offset Drift:  $15\mu V/^{\circ}C$  Max (AD518K) Pin Compatible With 118-Type Op Amp Series Mil Standard Parts Available 8-Pin Plastic Mini-DIP or TO-99 Hermetic

PRODUCT DESCRIPTION

tal Can

The AD518J, AD518K, and AD518S are high speed precision monolithic operational amplifiers designed for applications where slew rate and wide bandwidth are required, but low cost and ease of use are essential. The devices are internally compensated for unity gain applications with a 60° phase margin to insure stability, a minimum unity gain slew rate of  $50V/\mu s$ , and a typical bandwidth of 12MHz. In addition, in inverting applications external feedforward compensation may be added to increase the slew rate to over  $100V/\mu s$ , and nearly double the bandwidth. If desired, settling time to 0.1% can be reduced to under  $1\mu s$  with a single external capacitor.

The AD518's dc performance is consistent with its precision dynamic characteristics. The devices feature offset voltages below 2mV, maximum offset drifts of  $15\mu$ V/°C, and offset currents below 50nA max.

The high slew rate, fast settling time, ease of use, and low cost of the AD518 make it ideal for use with D/A and A/D converters, as well as active filters, sample-and-hold circuits, and as a general purpose, fast, wideband amplifier. The AD518 is supplied in the TO-99 package. The AD518J and AD518K are specified for operation over the 0 to  $+70^{\circ}$ C temperature range; the AD518S for operation from  $-55^{\circ}$ C to  $+125^{\circ}$ C.

## PROPUCT HIGHLIGHTS

The AD518 offers the user high speed performance and flexibility previously unavailable at low cost .....

- Internal compensation for unity gain application

- Capability to increase slew rate to over 100V/µs and double the bandwidth by an external feedforward technique

- Capability to reduce settling time to under  $1\mu$ s to 0.1% with a single external capacitor

- Differential input capability

- 2. The phase margin of the AD518, uncompensated at the unity gain crossover frequency, is 60°, providing unconditional stability for all conditions. This conservative phase margin represents a clear improvement over that of the 118 series IC op amps currently available.

- 3. The static performance of the AD518 is consistent with its excellent dynamic performance, providing offset voltage drift under  $15\mu V/^{\circ}C$ , CMRR of 80dB, and offset current below 50nA.

- 4. Every AD518 receives a 24 hour stabilization bake at +150°C to ensure reliability and long-term stability.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

P.O.

Box 280; Norwood, Massachusetts 02062 U.S.A.

Tel: 617/329-4700

Twx: 710/394-6577

Telex: 174059

Cables: ANALOG NORWOODMASS

# **SPECIFICATIONS** (@ +25°C and V<sub>s</sub> = $\pm$ 15V dc unless otherwise specified)

| Model                                                                                                                                                               | AD518J                     |                       |                   | AD518K                  |                       |               | AD518S                  |                                                          |                 |                              |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------|-------------------|-------------------------|-----------------------|---------------|-------------------------|----------------------------------------------------------|-----------------|------------------------------|---|

|                                                                                                                                                                     | Min                        | Тур                   | Max               | Min                     | Тур                   | Max           | Min                     | Тур                                                      | Max             | Units                        |   |

| $\begin{split} & \text{OPEN LOOP GAIN} \\ & V_O=\pm 10V, R_L \geq 2k\Omega \\ & T_{min} \text{ to } T_{max}, R_L = 2k\Omega \end{split}$                            | <b>25,000</b><br>20,000    | 100,000               |                   | <b>50,000</b><br>25,000 | 100,000               |               | <b>50,000</b><br>25,000 | 100,000                                                  |                 | V/V<br>V/V                   |   |

| OUTPUT CHARACTERISTICS<br>Voltage ( $@$ R <sub>L</sub> = 2k $\Omega$ , T <sub>min</sub> to T <sub>max</sub><br>Output Current<br>Short Circuit Current              | ±12                        | ±13<br>±10<br>25      |                   | ±12                     | ±13<br>±10<br>25      |               | ±12                     | ±13<br>±10<br>25                                         |                 | V<br>mA<br>mA                | 2 |

| FREQUENCY RESPONSE<br>Unity Gain Small Signal<br>Slew Rate, Unity Gain<br>Settling Time to 0.1%<br>Phase Margin, Uncompensated at Unity<br>Gain Crossover Frequency | 50                         | 12<br>70<br>800<br>60 |                   | 50                      | 12<br>70<br>800<br>60 |               | 50                      | 12<br>70<br>800<br>60                                    |                 | MHz<br>V/µs<br>ns<br>Degrees |   |

| INPUT OFFSET VOLTAGE<br>Initial Offset<br>Input Offset Voltage or T <sub>min</sub> to T <sub>max</sub><br>Input <u>Offset V</u> oltage vs. Supply or                |                            | 4                     | <b>10</b><br>15   |                         | 2                     | 4<br>6        |                         | 2                                                        | 4<br>6          | mV<br>mV                     |   |

| 7 min to Tmax                                                                                                                                                       | 65                         | 80                    |                   | 80                      | 90                    |               | 80                      | 90                                                       |                 | dB                           |   |

| INPUT BIAS CORRECT<br>Initial<br>T <sub>min</sub> to T <sub>max</sub>                                                                                               | $\sum$                     | 120                   | <b>500</b><br>750 |                         | 120                   | 250<br>400    |                         | 120                                                      | 250<br>400      | nA<br>nA                     |   |

| NPUT OFFSET CURVENT<br>Initial<br>Tm to Tmax                                                                                                                        | $\left\{ \right. \right\}$ | 30                    | 200               | $\bigcirc$              | 5                     | 50<br>100     |                         | 6                                                        | 50<br>100       | nA<br>nA                     |   |

| INPUT IMPEDANCE                                                                                                                                                     | 9.5                        | 3.0                   | (                 | 0.5                     | 3.0                   |               | 0.5                     | 3.0                                                      |                 | MΩ                           | - |

| INPUT VOLTAGE RANGE <sup>1</sup><br>Differential<br>Common Mode<br>Common Mode Rejection                                                                            | 70                         | ±11.5<br>=Vs<br>100   | $\mathcal{I}($    | 80                      | ± 11 5<br>± Vs<br>190 | / /           | 80                      | $ \begin{array}{c}                                     $ |                 | V<br>V<br>ap                 |   |

| POWER SUPPLY<br>Rated Performance<br>Operating<br>Quiescent Current                                                                                                 | ± 5                        | ± 15<br>5             | ±20<br>10         | ±5                      | ± 15                  | ±20<br>7      |                         | ± 15                                                     | ±18<br>±20<br>7 | V<br>V<br>µA                 |   |

| TEMPERATURE RANGE<br>Operating, Rated Performance<br>Storage                                                                                                        | 0<br>- 65                  |                       | + 70<br>+ 150     | 0<br>- 65               |                       | + 70<br>+ 150 | - 55<br>- 65            | ~                                                        | + 125<br>+ 150  |                              |   |

| PACKAGE OPTIONS<br>TO-99 Style (H08A)<br>Plastic Mini-DIP                                                                                                           |                            | AD518JH<br>AD518JN    |                   | x                       | AD518KH<br>AD518KN    |               |                         | AD518SH                                                  | I               |                              |   |

NOTES

<sup>1</sup>The inputs are shunted with back-to-back diodes; if the differential input may exceed ± 1 volt, a resistor should be used to limit the input current to 10mA Specifications subject to change without notice.

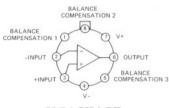

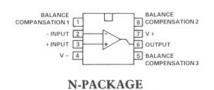

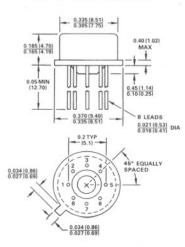

#### PIN CONFIGURATION Top View

H-PACKAGE

Specifications shown in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

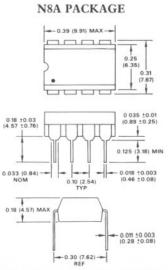

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### TO-99 STYLE (H08A)

#### STABILITY & PHASE MARGIN

Perhaps one of the most meaningful ways to express the relative stability of a closed loop amplifier is in terms of phase margin. Phase margin is measured at that frequency where the open loop gain of the amplifier becomes unity or OdB. It is the additional amount of phase shift that, if introduced in the loop, would make the loop unstable.

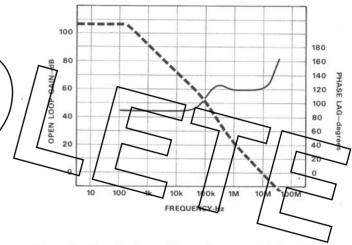

At very low frequencies the gain of most operational amplifiers is generally large. Moreover, the amplifier output signal is very nearly in phase with the differential input signal. This output is, therefore, nearly 180° out of phase with the feedback signal applied to the inverting input. At sufficiently high frequencies the gain of the amplifier begins to decrease as a function of frequency, with the resulting consequence of a lagging phase characteristic. That is, as the gain falls with increasing frequency, the phase of the output signal at a given frequency will lag the phase of the input signal. The phase shift depends most critically on the slope of the gain curve with respect to the logarithm of the frequency at the requency where the phase is measured. If the gain changes more rapidly than 12dB/octave over a substantial frequency range the minimum resulting phase shift may exceed 180° To insure amplifier stability it is necessary that the phase shift near the unity gain frequency (12MHz in the AD518) is less than 180°. Moreover, it is generally required that the phase shift be substantially below the critical stability point to insure proper system performance. If the unity gain phase shift approaches 180°, the system will be on the verge of oscillation. As a result, there will be a large peak in the closed loop response near the unity loop gain frequency. This sharply peaked frequency response generally causes an undesirable small signal transient response with a poorly damped overshoot.

The term *phase margin* refers to the difference between 180° and the actual frequency-dependent phase shift at the system unity gain frequency. It is the margin between the actual system phase shift and the critical phase shift at which oscillation will occur. Not only does it indicate the relative immunity to oscillation, but it also gives some indication about the peaking and overshoot that can be expected.

The simple pole or frequency response of a single R-C network has a gain slope of 6dB/octave. This response has an associated phase shift which is asymptotic to  $-90^{\circ}$ . Linear systems which are dominated by this characteristic in their open loop response are stable. They show no overshoot or ringing in their small signal transient response. Additional poles, either above or below the unity loop gain frequency, will add phase shift. As phase shift increases up to a lagging phase of about  $120^{\circ}$ , representing a  $60^{\circ}$  phase margin, little or no peaking will result. As the unity gain phase shift increases, peaking becomes more and more evident. For example, as the phase shift reaches  $160^{\circ}$  ( $20^{\circ}$  of phase margin), between 9 and 10dB of peaking will occur.

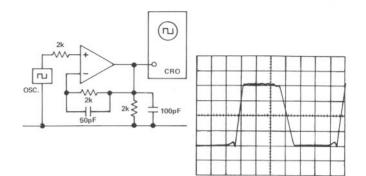

The AD518 has been designed for a  $60^{\circ}$  phase margin at the unity gain crossover frequency, for absolute stability and absence of ringing and overshoot. (Note the transient response of the AD518 in Figure 1.) Note also in Figure 2 that the phase shift at 12MHz, the unity gain crossover frequency, is  $120^{\circ}$ , representing  $60^{\circ}$  of phase margin.

Figure 1. Transient Response of the AD518

Figure 2. Amplitude and Phase Response of the AD518

#### THE FLEXIBILITY OF THE AD518

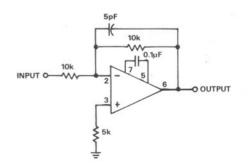

MINIMUM SETTLING TIME APPLICATIONS For applications where a minimum settling time is desired, the settling time of the AD518 may be reduced significantly by employing the compensation scheme suggested in Figure 3.

Figure 3. Minimum Settling Time Compensation

Using the  $0.1\mu$ F capacitor from Pin 5 to V+ (Pin 7), the settling time to 0.1% is reduced from  $2\mu$ s to 800ns.

### HIGHER BANDWIDTH OR

#### HIGHER SLEW RATE APPLICATIONS

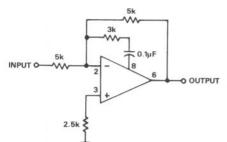

For applications where higher bandwidth is desired, the bandwidth of the AD518 may be increased to nearly 25MHz by using the feedforward technique shown in Figure 4.

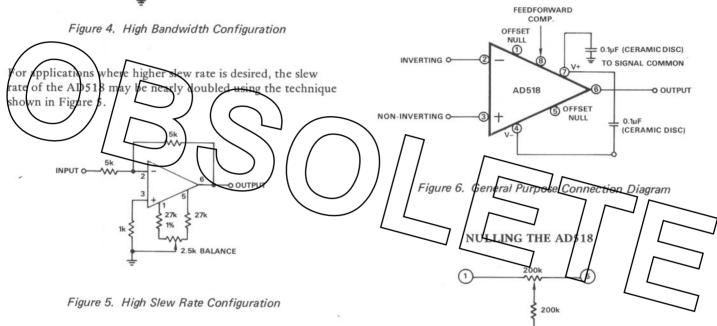

while the  $0.1\mu$ F capacitor from V+ to signal ground should be returned to signal common. This signal common, which is bypassed to pin 7, is defined as that point at which the input signal source, the feedback network, and the return side of the load are joined to the power common.

When using the AD518, this decoupling configuration should be used in conjunction with the configuration of Figures 3, 4 and 5, depending on the specific application.

Note that the diagram shows each individual capacitor directly connected to the appropriate terminal. In addition, it is suggested that all connections be made short and direct, and as physically close to the can as possible, so that the length of any conducting path shared by external components will be minimized.

Note that the techniques of Figures 4 and 5 may be used in conjunction with each other to both double the bandwidth to 25MHz and increase the slew rate to  $100-140V/\mu s$ .

#### **USING THE AD518**

The connection scheme employed when using the AD518 is considerably more important than for low frequency, general purpose amplifiers. The primary purpose of the  $0.1\mu$ F bypass capacitors shown in Figure 6 is to convert the distributed high frequency ground to a lumped single point (the V+ point). The V+ to V-  $0.1\mu$ F capacitor equalizes the supply grounds,

### OTHER IC HIGH SPEED AMPLIFIERS AVAILABLE

(7) V4

- AD507 35MHz Gain Bandwidth Slew Rate of 25V/µs min Bias Current of 15nA max Offset Voltage Drift of 15µV/°C max

- AD509 Settles to 0.01% in 1μs Settles to 0.1% in 200ns Slew Rate of 100V/μs min