# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

# **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

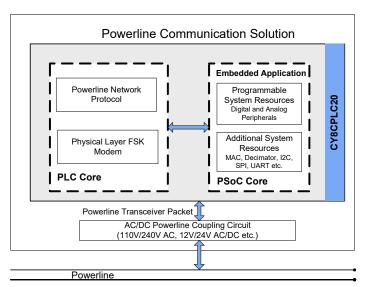

# Powerline Communication Solution

#### **Features**

- Powerline communication solution

- □ Integrated powerline modem PHY

- □ Frequency shift keying modulation

- □ Configurable baud rates up to 2400 bps

- □ Powerline optimized network protocol

- □ Integrates data link, transport, and network layers

- □ Supports bidirectional half duplex communication

- □ 8-bit CRC error detection to minimize data loss

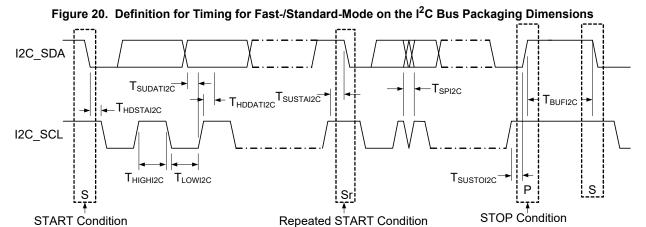

- □ I<sup>2</sup>C enabled powerline application layer

- □ Supports I<sup>2</sup>C frequencies of 50, 100, and 400 kHz

- □ Reference designs for 110 V/240 V AC and 12 V/24 V AC/DC Powerlines

- □ Reference designs comply with CENELEC EN 50065-1:2001 and FCC Part 15

- Powerful Harvard-architecture Processor

- M8C processor speeds to 24 MHz

- □ Two 8x8 multiply, 32-bit accumulate

- Programmable system resources (PSoC<sup>®</sup> Blocks)

- ☐ 12 Rail-to-Rail Analog PSoC Blocks provide:

- Up to 14-bit ADCs

- Up to 9-bit DACs

- Programmable gain amplifiers

- · Programmable filters and comparators

- □ 16 Digital PSoC Blocks provide:

- 8 to 32-bit Timers, Counters, and PWMs

- · CRC and PRS Modules

- · Up to four full duplex UARTs

- Multiple SPI™ masters or slaves

- · Connectable to all GPIO Pins

- □ Complex peripherals by combining blocks

- Flexible on-chip memory

- □ 32 KB flash program storage 50,000 erase or write cycles

- □ 2 KB SRAM data storage

- EEPROM emulation in flash

- Programmable pin configurations

- □ 25 mA sink, 10 mA source on all GPIOs

- □ Pull-up, Pull-down, high Z, strong, or open drain drive Modes on all GPIO

- □ Up to 12 analog inputs on all GPIOs

- □ Configurable interrupt on all GPIOs

- Additional system resources

- □ I<sup>2</sup>C slave, master, and multi-master to 400 kHz

- □ Watchdog and sleep timers

- □ User-configurable low-voltage detection

- □ Integrated supervisory circuit

- □ On-chip precision voltage reference

- Complete development tools

- □ Free development software (PSoC Designer™)

- □ Full-featured in-circuit emulator (ICE) and programmer

- □ Full-speed emulation

- □ Complex breakpoint structure

- □ 128 KB trace memory

- Complex events

- C Compilers, assembler, and linker

# **Logic Block Diagram**

#### More Information

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article "How to Design with PSoC® 1, PowerPSoC®, and PLC – KBA88292". Following is an abbreviated list for PSoC 1:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP

- In addition, PSoC Designer includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 1 are:

- ☐ Getting Started with PSoC® 1 AN75320

- □ PSoC® 1 Getting Started with GPIO AN2094

- □ PSoC<sup>®</sup> 1 Analog Structure and Configuration AN74170

- □ PSoC® 1 Switched Capacitor Analog Blocks AN2041

- □ Selecting Analog Ground and Reference AN2219

**Note:** For CY8CPLC20 devices related Application note please click here.

- Development Kits:

- □ CY3210-PSoCEval1 supports all PSoC 1 Mixed-Signal Array families, including automotive, except CY8C25/26xxx devices. The kit includes an LCD module, potentiometer, LEDs, and breadboarding space.

- CY3214-PSoCEvalUSB features a development board for the CY8C24x94 PSoC device. Special features of the board include USB and CapSense development and debugging support.

**Note:** For CY8CPLC20 devices related Development Kits please click here.

The MiniProg1 and MiniProg3 devices provide interfaces for flash programming and debug.

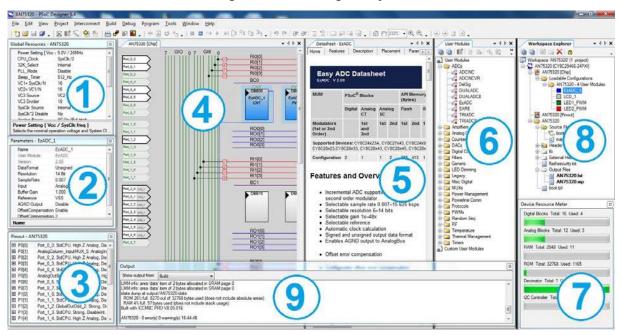

#### **PSoC Designer**

PSoC Designer is a free Windows-based Integrated Design Environment (IDE). Develop your applications using a library of pre-characterized analog and digital peripherals in a drag-and-drop design environment. Then, customize your design leveraging the dynamically generated API libraries of code. Figure 1 shows PSoC Designer windows. **Note:** This is not the default view.

- Global Resources all device hardware settings.

- Parameters the parameters of the currently selected User Modules.

- 3. Pinout information related to device pins.

- 4. **Chip-Level Editor –** a diagram of the resources available on the selected chip.

- 5. Datasheet the datasheet for the currently selected UM

- User Modules all available User Modules for the selected device.

- 7. **Device Resource Meter –** device resource usage for the current project configuration.

- 8. **Workspace** a tree level diagram of files associated with the project.

- 9. **Output –** output from project build and debug operations.

**Note:** For detailed information on PSoC Designer, go to PSoC<sup>®</sup> Designer > Help > Documentation > Designer Specific Documents > IDE User Guide.

Figure 1. PSoC Designer Layout

### **Contents**

| PLC Functional Overview                           | . 4 |

|---------------------------------------------------|-----|

| Robust Communication using Cypress's PLC Solution | n 4 |

| Powerline Modem PHY                               | . 4 |

| Network Protocol                                  | . 5 |

| PSoC Core                                         | 9   |

| Programmable System Resources                     | . 9 |

| Additional System Resources                       | 12  |

| Development Tools                                 |     |

| PSoC Designer Software Subsystems                 | 12  |

| Designing with PSoC Designer                      | 13  |

| Select User Modules                               | 13  |

| Configure User Modules                            |     |

| Organize and Connect                              | 13  |

| Generate, Verify, and Debug                       |     |

| PLC User Modules                                  |     |

| Pin Information                                   |     |

| 28-Pin Part Pinout                                |     |

| 48-Pin Part Pinout                                |     |

| 100-Pin Part Pinout (On-Chip Debug)               |     |

| Register Reference                                |     |

| Register Conventions                              |     |

| Register Mapping Tables                           |     |

| Electrical Specifications                         |     |

| Absolute Maximum Ratings                          |     |

| Operating Temperature                             |     |

| DC Electrical Characteristics                     |     |

| AC Electrical Characteristics                     | 32  |

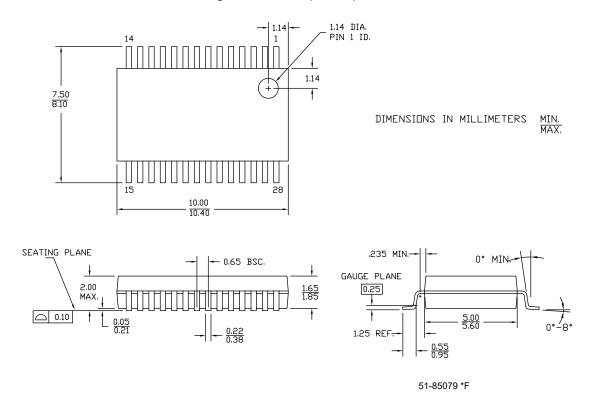

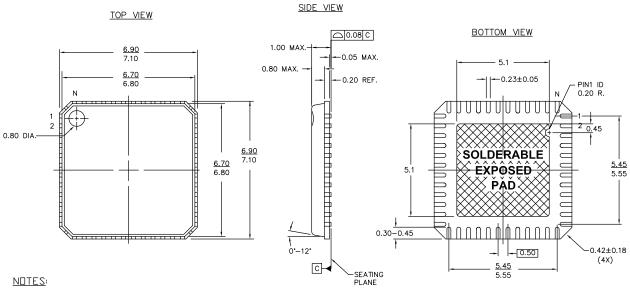

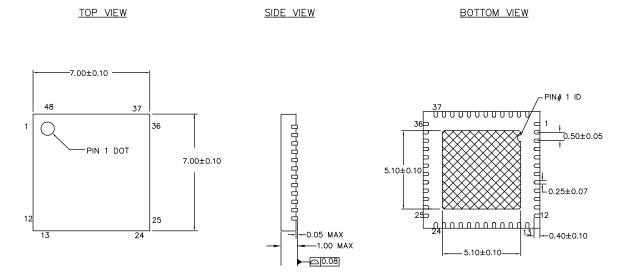

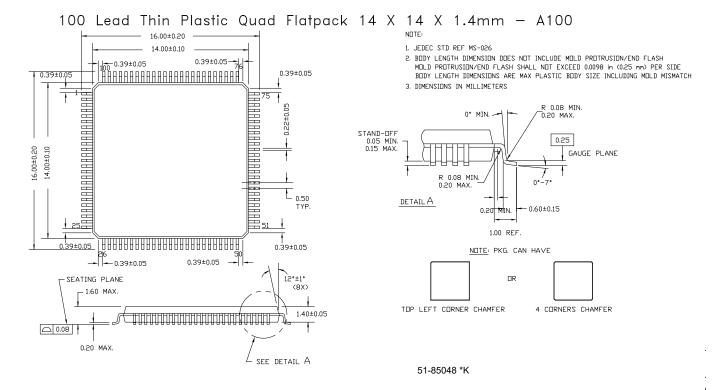

| Packaging information                   | 41 |

|-----------------------------------------|----|

| Packaging Dimensions                    | 41 |

| Thermal Impedances                      | 44 |

| Capacitance on Crystal Pins             | 45 |

| Solder Reflow Peak Temperature          | 45 |

| Development Tool Selection              | 46 |

| Software                                | 46 |

| Development Kits                        |    |

| Evaluation Kits                         | 47 |

| Device Programmers                      |    |

| Ordering Information                    |    |

| Ordering Code Definitions               | 48 |

| Acronyms                                |    |

| Acronyms Used                           | 49 |

| Reference Documents                     |    |

| Document Conventions                    | 50 |

| Units of Measure                        | 50 |

| Numeric Conventions                     | 50 |

| Glossary                                | 50 |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      | 58 |

| Products                                |    |

| PSoC® Solutions                         | 58 |

| Cypress Developer Community             | 58 |

| Technical Support                       | 58 |

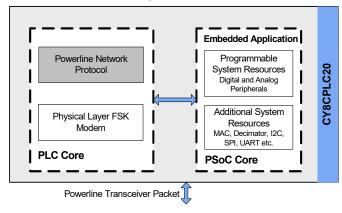

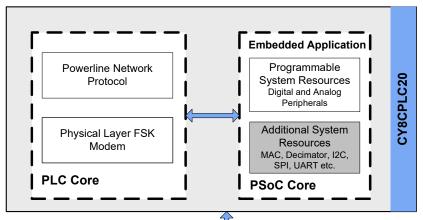

#### **PLC Functional Overview**

The CY8CPLC20 is an integrated powerline communication (PLC) chip with the powerline modem PHY and network protocol stack running on the same device. Apart from the PLC core, the CY8CPLC20 also offers Cypress's revolutionary PSoC technology that enables system designers to integrate multiple functions on the same chip.

#### Robust Communication using Cypress's PLC Solution

Powerlines are available everywhere in the world and are a widely available communication medium for PLC technology. The pervasiveness of powerlines also makes it difficult to predict the characteristics and operation of PLC products. Because of the variable quality of powerlines around the world, implementing robust communication has been an engineering challenge for years. The Cypress PLC solution enables secure and reliable communications. Cypress PLC features that enable robust communication over powerlines include:

- Integrated Powerline PHY modem with optimized filters and amplifiers to work with lossy high voltage and low voltage powerlines.

- Powerline optimized network protocol that supports bidirectional communication with acknowledgement-based signaling. In case of data packet loss due to bursty noise on the powerline, the transmitter has the capability to retransmit data

- The powerline network protocol also supports an 8-bit CRC for error detection and data packet retransmission.

- A Carrier sense multiple access (CSMA) scheme is built into the network protocol that minimizes collisions between packet transmissions on the powerline and supports multiple masters and reliable communication on a bigger network.

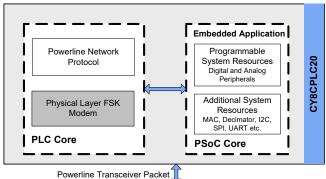

#### **Powerline Modem PHY**

Figure 2. Physical Layer FSK Modem

Powerline Communication Solution

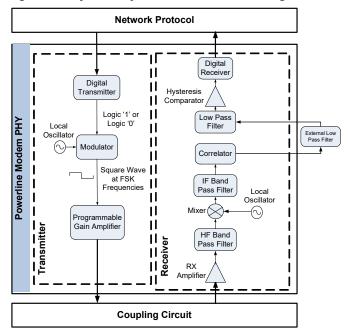

The physical layer of the Cypress PLC solution is implemented using an FSK modem that enables half duplex communication on any high voltage and low voltage powerline. This modem supports raw data rates up to 2400 bps. A block diagram is shown in Figure 3.

Figure 3. Physical Layer FSK Modem Block Diagram

#### Transmitter Section

Digital data from the network layer is serialized by the digital transmitter and fed as input to the modulator. The modulator divides the local oscillator frequency by a definite factor depending on whether the input data is high level logic '1' or low level logic '0'. It then generates a square wave at 133.3 kHz (logic '0') or 131.8 kHz (logic '1'), which is fed to the Programmable Gain Amplifier to generate FSK modulated signals. This enables tunable amplification of the signal depending on the noise in the channel. The logic '1' frequency can also be configured as 130.4 kHz for wider FSK deviation.

#### Receiver Section

The incoming FSK signal from the powerline is input to a high frequency (HF) band pass filter that filters out-of-band frequency components and outputs a filtered signal within the desired spectrum of 125 kHz to 140 kHz for further demodulation. The mixer block multiplies the filtered FSK signals with a locally generated signal to produce heterodyned frequencies.

The intermediate frequency (IF) band pass filters further remove out-of-band noise as required for further demodulation. This signal is fed to the correlator, which produces a DC component (consisting of logic '1' and '0') and a higher frequency component.

The output of the correlator is fed to a low pass filter (LPF) that outputs only the demodulated digital data at 2400 baud and suppresses all other higher frequency components generated in the correlation process. The output of the LPF is digitized by the

hysteresis comparator. This eliminates the effects of correlator delay and false logic triggers due to noise. The digital receiver deserializes this data and outputs to the network layer for interpretation.

#### Coupling Circuit Reference Design

The coupling circuit couples low voltage signals from the CY8CPLC20 to the powerline. The topology of this circuit is determined by the voltage on the powerline and design constraints mandated by powerline usage regulations.

Cypress provides reference designs for a range of powerline voltages including 110 V/240 V AC and 12 V/24 V AC/DC. The CY8CPLC20 is capable of data communication over other AC/DC Powerlines as well with the appropriate external coupling circuit. The 110 V AC and 240 V AC designs are compliant to the following powerline usage regulations:

- FCC Part 15 for North America

- EN 50065-1:2001 for Europe

#### **Network Protocol**

Cypress's powerline optimized network protocol performs the functions of the data link and network layers in an ISO/OSI-equivalent model.

Figure 4. Powerline Network Protocol

Powerline Communication Solution

The network protocol implemented on the CY8CPLC20 supports the following features:

- Bidirectional half-duplex communication

- Master-slave or peer-to-peer network topologies

- Multiple masters on powerline network

- 8-bit logical addressing supports up to 256 powerline nodes

- 16-bit extended logical addressing supports up to 65536 powerline nodes

- 64-bit physical addressing supports up to 2<sup>64</sup> powerline nodes

- Individual, broadcast or group mode addressing

- Carrier Sense Multiple Access (CSMA)

- Full control over transmission parameters

- □ Acknowledged

- Unacknowledged

- □ Repeated Transmit

#### CSMA and Timing Parameters

- CSMA The protocol provides the random selection of a period between 85 and 115 ms (out of seven possible values in this range) in which the band-in-use (BIU) detector must indicate that the line is not in use, before attempting a transmission.

- BIU A Band-In-Use detector, as defined under CENELEC EN 50065-1, is active whenever a signal that exceeds 86 dBmVrms anywhere in the range 131.5 kHz to 133.5 kHz is present for at least 4 ms. This threshold can be configured for different end-system applications not requiring CENELEC compliance. The modem tries to retransmit after every 85 to 115 ms when the band is in use. The transmitter times out after 1.1 seconds to 3 seconds (depending on the noise on the Powerline) and generates an interrupt to indicate that the transmitter was unable to acquire the powerline.

#### Powerline Transceiver Packet

The powerline network protocol defines a powerline transceiver (PLT) packet structure, which is used for data transfer between nodes across the powerline. Packet formation and data transmission across the powerline network are implemented internally in CY8CPLC20.

A PLT packet is divided into a variable length header (minimum 6 bytes to maximum 20 bytes, depending on address type), a variable length payload (minimum 0 bytes to maximum 31 bytes), and a packet CRC byte.

This packet (preceded by a one byte preamble "0xAB") is then transmitted by the powerline modem PHY and the external coupling circuit across the powerline.

The format of the PLT packet is shown in Table 1 on page 5.

Table 1. Powerline Transceiver (PLT) Packet Structure

| Byte<br>Offset | Bit Offset |        |         |                 |                     |          |              |         |  |  |  |

|----------------|------------|--------|---------|-----------------|---------------------|----------|--------------|---------|--|--|--|

|                | 7          | 6      | 5       | 4               | 3                   | 2        | 1            | 0       |  |  |  |

| 0x00           | SA<br>Type | DA     | Туре    | Service<br>Type | RSVD                | RSVD     | Response     | RSVD    |  |  |  |

| 0x01           | (8-Bi      | t Logi | ical, 1 |                 | ation Ac<br>ended L |          | r 64-Bit Phy | rsical) |  |  |  |

| 0x02           | (8-Bi      | t Logi | ical, 1 |                 | rce Addi<br>ended L |          | r 64-Bit Phy | rsical) |  |  |  |

| 0x03           |            |        |         | С               | omman               | d        |              |         |  |  |  |

| 0x04           | F          | RSVD   |         |                 | Pa                  | iyload L | ength        |         |  |  |  |

| 0x05           |            | Sec    | Num     |                 | Powe                | rline Pa | cket Heade   | r CRC   |  |  |  |

| 0x06           |            |        |         |                 |                     |          |              |         |  |  |  |

|                |            |        |         | Payload         | (0 to 3°            | 1 Bytes) |              |         |  |  |  |

|                |            |        | Powe    | erline Tra      | nsceive             | r Packet | t CRC        |         |  |  |  |

#### Packet Header

The packet header contains the first 6 bytes of the packet when 1-byte logical addressing is used. When 8-byte physical

addressing is used, the source and destination addresses each contain 8 bytes. In this case, the header can consist of a maximum of 20 bytes. Unused fields marked RSVD are for future expansion and are transmitted as bit 0. Table 2 describes the PLT packet header fields in detail.

Table 2. Powerline Transceiver (PLT) Packet Header

| Field<br>Name   | No. of<br>Bits | Tag                         | Description                                                                                                       |

|-----------------|----------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------|

| SA Type         | 1              | Source<br>Address Type      | 0 – Logical Addressing<br>1 – Physical Addressing                                                                 |

| DA Type         | 2              | Destination<br>Address Type | 00 – Logical Addressing<br>01 – Group Addressing<br>10 – Physical Addressing<br>11 – Invalid                      |

| Service<br>Type | 1              |                             | 0 – Unacknowledged Messaging<br>1 – Acknowledged Messaging                                                        |

| Response        | 1              | Response                    | Not an acknowledgement or response packet     Acknowledgement or response packet                                  |

| Seq Num         | 4              | Sequence<br>Number          | 4-bit unique identifier for each packet between source and destination.                                           |

| Header<br>CRC   | 4              |                             | 4-bit CRC value. This enables the receiver to suspend receiving the rest of the packet if its header is corrupted |

#### Payload

The packet payload has a length of 0 to 31 bytes. Payload content is user defined and can be read or written through I<sup>2</sup>C.

#### Packet CRC

The last byte of the packet is an 8-bit CRC value used to check packet data integrity. This CRC calculation includes the header and payload portions of the packet and is in addition to the powerline packet header CRC.

#### Sequence Numbering

The sequence number is increased for every new unique packet transmitted. If in acknowledged mode and an acknowledgment is not received for a given packet, that packet is re-transmitted (if TX\_Retry > 0) with the same sequence number. If in unacknowledged mode, the packet is transmitted (TX\_Retry + 1) times with the same sequence number.

If the receiver receives consecutive packets from the same source address with the same sequence number and packet CRC, it does not notify the host of the reception of the duplicate packet. If in acknowledged mode, it still sends an acknowledgment so that the transmitter knows that the packet was received.

#### Addressing

The CY8CPLC20 has three modes of addressing:

■ Logical addressing: Every CY8CPLC20 node can have either a 8-bit logical address or a 16-bit logical address. The logical address of the PLC Node is set by the local application or by a remote node on the Powerline.

- Physical addressing: Every CY8CPLC20 has a unique 64-bit physical address.

- Group addressing: This is explained in the next section.

#### Group Membership

Group membership enables the user to multicast messages to select groups. The CY8CPLC20 supports two types of group addressing:

- Single Group Membership The network protocol supports up to 256 different groups on the network in this mode. In this mode, each PLC node can only be part of a single group. For example, multiple PLC nodes can be part of Group 131.

- Multiple Group Membership The network protocol supports eight different groups in this mode and each PLC node can be a part of multiple groups. For example, a single PLC node can be a part of Group 3, Group 4, and Group 7 at the same time.

Both these membership modes can also be used together for group membership. For example, a single PLC node can be a part of Group 131 and also multiple groups such as Group 3, Group 4, and Group 7.

The group membership ID for broadcasting messages to all nodes in the network is 0x00.

The service type is always set to Unacknowledgment Mode in Group Addressing Mode. This is to avoid acknowledgment flooding on the powerline during multicast.

#### Remote Commands

In addition to sending normal data over the Powerline, the CY8CPLC10 can also send (and request) control information to (and from) another node on the network. The type of remote command to transmit is set by the TX\_CommandID register and when received, is stored in the RX CommandID register.

When a control command (Command ID = 0x01-0x08 and 0x0C-0x0F) is received, the protocol automatically processes the packet (if Lock\_Configuration is '0'), responds to the initiator, and notifies the host of the successful transmission and reception.

When the send data command (ID 0x09) or request for data command (ID 0x0A) is received, the protocol replies with an acknowledgment packet (if TX\_Service\_Type = '1'), and notify the host of the new received data. If the initiator doesn't receive the acknowledgment packet within 500ms, it notifies the host of the no acknowledgment received condition.

When a response command (ID 0x0B) is received by the initiator within 1.5s of sending the request for data command, the protocol notifies the host of the successful transmission and reception. If the response command is not received by the initiator within 1.5s, it notifies the host of the no response received condition.

The host is notified by updating the appropriate values in the INT\_Status register (including Status\_Value\_Change).

The command IDs 0x30-0xff can be used for custom commands that would be processed by the external host (e.g. set an LED color, get a temperature/voltage reading).

The available remote commands are described in Table 3 with the respective Command IDs.

**Table 3. Remote Commands**

| Cmd ID | Command Name           | Description                                                                                  | Payload (TX Data)                                                                                        | Response (RX Data)                                                                                                                                                                                                                            |

|--------|------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01   | SetRemote_TXEnable     | Sets the TX Enable bit in the PLC Mode Register. Rest of the PLC Mode register is unaffected | 0 - Disable Remote TX<br>1 - Enable Remote TX                                                            | If Remote Lock Config = 0,<br>Response = 00 (Success)<br>If Remote Lock Config = 1,<br>Response = 01 (Denied)                                                                                                                                 |

| 0x03   | SetRemote_ExtendedAddr | Set the Addressing to<br>Extended Addressing Mode                                            | 0 - Disable Extended<br>Addressing<br>1 - Enable Extended<br>Addressing                                  | If Remote Lock Config = 0,<br>Response = 00 (Success)<br>If Remote Lock Config = 1,<br>Response = 01 (Denied)                                                                                                                                 |

| 0x04   | SetRemote_LogicalAddr  | Assigns the specified logical address to the remote PLC node                                 | If Ext Address = 0, Payload = 8-bit Logical Address If Ext Address = 1, Payload = 16-bit Logical Address | If Remote Lock Config = 0,<br>Response = 00 (Success)<br>If Remote Lock Config = 1,<br>Response = 01 (Denied)                                                                                                                                 |

| 0x05   | GetRemote_LogicalAddr  | Get the Logical Address of the remote PLC node                                               | None                                                                                                     | If Remote TX Enable = 0, Response = None If Remote TX Enable = 1, {If Ext Address = 0, Response = 8-bit Logical Address If Ext Address = 1, Response = 16-bit Logical Address}                                                                |

| 0x06   | GetRemote_PhysicalAddr | Get the Physical Address of the remote PLC node                                              | None                                                                                                     | If Remote TX Enable = 0,<br>Response = None<br>If Remote TX Enable = 1,<br>Response = 64-bit Physical<br>Address                                                                                                                              |

| 0x07   | GetRemote_State        | Request PLC_Mode Register content from a Remote PLC node                                     | None                                                                                                     | If Remote TX Enable = 0,<br>Response = None<br>If Remote TX Enable = 1,<br>Response = Remote PLC<br>Mode register                                                                                                                             |

| 0x08   | GetRemote_Version      | Get the Version Number of the Remote Node                                                    | None                                                                                                     | If TX Enable = 0, Response =<br>None<br>If TX Enable = 1, Response =<br>Remote Version register                                                                                                                                               |

| 0x09   | SendRemote_Data        | Transmit data to a Remote Node.                                                              | Payload = Local TX<br>Data                                                                               | If Local Service Type = 0,<br>Response = None<br>If Local Service Type = 1,<br>Response = Ack                                                                                                                                                 |

| 0x0A   | RequestRemote_Data     | Request data from a Remote<br>Node                                                           | Payload = Local TX<br>Data                                                                               | If Local Service Type = 1, Response = Ack Then, the remote node host must send a ResponseRemote_Data command. The response must be completely transmitted within 1.5s of receiving the request. Otherwise, the requesting node will time out. |

| 0x0B   | ResponseRemote_Data    | Transmit response data to a Remote Node.                                                     | Payload = Local TX<br>Data                                                                               | None                                                                                                                                                                                                                                          |

| 0x0C   | SetRemote_BIU          | Enables/Disables BIU functionality at the remote node                                        | 0 - Enable Remote BIU<br>1 - Disable Remote BIU                                                          | If Remote Lock Config = 0,<br>Response = 00 (Success)<br>If Remote Lock Config = 1,<br>Response = 01 (Denied)                                                                                                                                 |

Document Number: 001-48325 Rev. \*O

**Table 3. Remote Commands** (continued)

| Cmd ID        | Command Name              | Description                                     | Payload (TX Data)                                                                                            | Response (RX Data)                                                                                                                                                          |

|---------------|---------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0D          | SetRemote_ThresholdValue  | Sets the Threshold Value at the Remote node     | 3-bit Remote<br>Threshold Value                                                                              | If Remote Lock Config = 0,<br>Response = 00 (Success)<br>If Remote Lock Config = 1,<br>Response = 01 (Denied)                                                               |

| 0x0E          | SetRemote_GroupMembership | Sets the Group Membership of<br>the Remote node | Byte0 - Remote SIngle<br>Group Membership<br>Address<br>Byte1-Remote Multiple<br>Group Membership<br>Address | If Remote Lock Config = 0,<br>Response = 00 (Success)<br>If Remote Lock Config = 1,<br>Response = 01 (Denied)                                                               |

| 0x0F          | GetRemote_GroupMembership | Gets the Group Membership of<br>the Remote node | None                                                                                                         | If Remote TX Enable = 0, Response = None If Remote TX Enable = 1, Response = Byte0 - Remote SIngle Group Membership Address Byte1- Remote Multiple Group Membership Address |

| 0x10-<br>0x2F | Reserved                  |                                                 |                                                                                                              |                                                                                                                                                                             |

| 0x30-<br>0xFF | User Defined Command Set  |                                                 |                                                                                                              |                                                                                                                                                                             |

#### **PSoC Core**

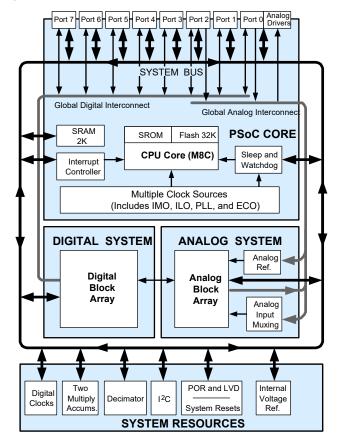

The CY8CPLC20 is based on the Cypress PSoC® 1 architecture. The PSoC platform consists of many *Programmable System-on-chip Controller* devices. These devices are designed to replace multiple traditional MCU-based system components with one, low-cost single-chip programmable device. PSoC devices include configurable blocks of analog and digital logic, and programmable interconnects. This architecture enables the user to create customized peripheral configurations that match the requirements of each individual application. Additionally, a fast CPU, flash program memory, SRAM data memory, and configurable I/Os are included in a range of convenient pinouts and packages.

The PSoC architecture, as shown in Figure 5, consists of four main areas: PSoC Core, digital system, analog system, and system resources. Configurable global busing enables all the device resources to be combined into a complete custom system. The CY8CPLC20 family can have up to five I/O ports that connect to the global digital and analog interconnects, providing access to 16 digital blocks and 12 analog blocks.

The PSoC core is a powerful engine that supports a rich feature set. The core includes a CPU, memory, clocks, and configurable GPIO (General Purpose I/O).

Figure 5. PSoC Core

The M8C CPU core is a powerful processor with speeds up to 24 MHz, providing a 4 MIPS 8-bit Harvard architecture microprocessor. The CPU uses an interrupt controller with 25 vectors, to simplify programming of realtime embedded events. Program execution is timed and protected using the included Sleep and Watchdog timers (WDT).

Memory encompasses 32 KB of Flash for program storage, 2 KB of SRAM for data storage, and up to 2 KB of EEPROM emulated using Flash. Program Flash uses four protection levels on blocks of 64 bytes, enabling customized software IP protection.

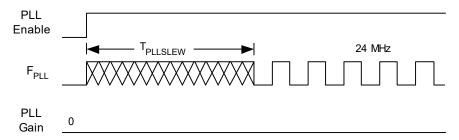

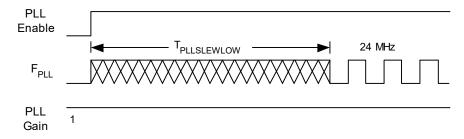

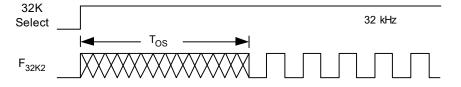

The PSoC device incorporates flexible internal clock generators, including a 24 MHz internal main oscillator (IMO) accurate to 2.5 percent over temperature and voltage. The 24 MHz IMO can also be doubled to 48 MHz for the digital system use. A low power 32 kHz internal low speed oscillator (ILO) is provided for the sleep timer and WDT. If crystal accuracy is desired, the ECO (32.768 kHz external crystal oscillator) is available for use as a real time clock (RTC) and can optionally generate a crystal-accurate 24 MHz system clock using a PLL. When operating the powerline transceiver (PLT) user module, the ECO must be selected to ensure accurate protocol timing. The clocks, together with programmable clock dividers (as a System Resource), provide the flexibility to integrate almost any timing requirement into the PSoC device.

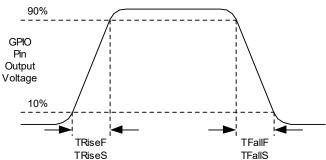

PSoC GPIOs provide connection to the CPU, digital, and analog resources of the device. Each pin's drive mode may be selected from eight options, enabling great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on high level, low level, and change from last read.

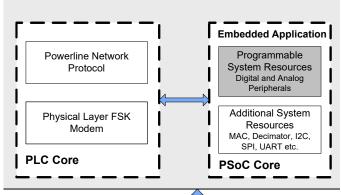

#### **Programmable System Resources**

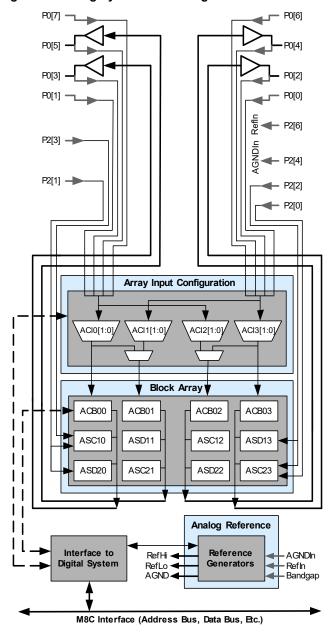

Figure 6. Programmable System Resources

Powerline Transceiver Packet

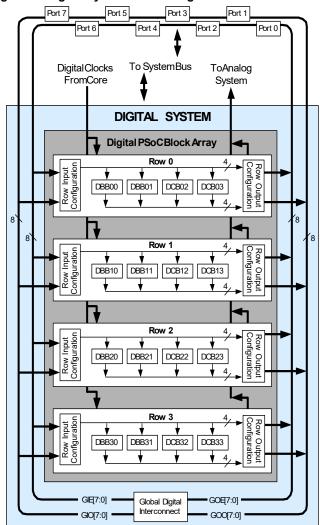

#### The Digital System

The digital system contains 16 digital PSoC blocks. Each block is an 8-bit resource that can be used alone, or combined with other blocks to form 8-, 16-, 24-, and 32-bit peripherals called user modules. Digital peripheral configurations include:

- PWMs (8- to 32-bit)

- PWMs with dead band (8- to 32-bit)

- Counters (8- to 32-bit)

- Timers (8- to 32-bit)

- UART 8 bit with selectable parity (up to four)

- SPI master and slave (up to four each)

- I<sup>2</sup>C slave and multi-master (one available as a System Resource)

- Cyclical Redundancy Checker and Generator (8- to 32-bit)

- IrDA (up to four)

- Pseudo Random Sequence Generators (8- to 32-bit)

The digital blocks can be connected to any GPIO through a series of global buses that can route any signal to any pin. The buses also enable signal multiplexing and perform logic operations. This configurability frees your designs from the constraints of a fixed peripheral controller.

Figure 7. Digital System Block Diagram

#### The Analog System

The analog system contains 12 configurable blocks, each containing an opamp circuit, enabling the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common PSoC analog functions (most available as user modules) are:

- Analog-to-digital converters (up to four, with 6- to 14-bit resolution, selectable as Incremental, Delta Sigma, and SAR)

- Filters (2, 4, 6, or 8 pole band pass, low pass, and notch)

- Amplifiers (up to four, with selectable gain to 48x)

- Instrumentation amplifiers (up to two, with selectable gain to 93x)

- Comparators (up to four, with 16 selectable thresholds)

- DACs (up to four, with 6- to 9-bit resolution)

- Multiplying DACs (up to four, with 6- to 9-bit resolution)

- High current output drivers (4 with 40 mA drive as a Core Resource)

- 1.3 V reference (as a System Resource)

- DTMF Dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

Analog blocks are provided in columns of three, which includes one continuous time (CT) and two switched capacitor (SC) blocks, as shown in the Figure 8.

Figure 8. Analog System Block Diagram

#### **Additional System Resources**

Figure 9. CY8CPLC20: Additional System Resources

#### Powerline Communication Solution

Powerline Transceiver Packet

System resources, some of which have been previously listed, provide additional capability useful to complete systems. Resources include a multiplier, decimator, low-voltage detection, and power on reset. The following statements describe the merits of each system resource.

- Digital clock dividers provide three customizable clock frequencies for use in applications. The clocks can be routed to both the digital and analog systems. Additional clocks are generated using digital PSoC blocks as clock dividers.

- Multiply accumulate (MAC) provides a fast 8-bit multiplier with 32-bit accumulate, to assist in general math and digital filters.

- The decimator provides a custom hardware filter for digital signal processing applications including the creation of Delta Sigma ADCs.

- The I<sup>2</sup>C module provides 100 and 400 kHz communication over two wires. Slave, master, and multi-master modes are supported.

- Low-voltage detection (LVD) interrupts signal the application of falling voltage levels, while the advanced Power On Reset (POR) circuit eliminates the need for a system supervisor.

- An internal 1.3 V reference provides an absolute reference for the analog system, including ADCs and DACs.

### **Development Tools**

PSoC Designer™ is the revolutionary integrated design environment (IDE) that you can use to customize PSoC to meet your specific application requirements. PSoC Designer software accelerates system design and time to market. Develop your applications using a library of precharacterized analog and digital peripherals (called user modules) in a drag-and-drop design environment. Then, customize your design by leveraging the dynamically generated application programming interface (API) libraries of code. Finally, debug and test your designs with the integrated debug environment, including in-circuit emulation and standard software debug features. PSoC Designer includes:

- Application editor graphical user interface (GUI) for device and user module configuration and dynamic reconfiguration

- Extensive user module catalog

- Integrated source-code editor (C and assembly)

- Free C compiler with no size restrictions or time limits

- Built-in debugger

- In-circuit emulation

- Built-in support for communication interfaces:

- ☐ Hardware and software I<sup>2</sup>C slaves and masters

- □ Full-speed USB 2.0

- □ Up to four full-duplex universal asynchronous receiver/transmitters (UARTs), SPI master and slave, and wireless

PSoC Designer supports the entire library of PSoC 1 devices and runs on Windows XP, Windows Vista, and Windows 7.

#### **PSoC Designer Software Subsystems**

### Design Entry

In the chip-level view, choose a base device to work with. Then select different onboard analog and digital components that use the PSoC blocks, which are called user modules. Examples of user modules are analog-to-digital converters (ADCs), digital-to-analog converters (DACs), amplifiers, and filters. Configure the user modules for your chosen application and connect them to each other and to the proper pins. Then generate your project. This prepopulates your project with APIs and libraries that you can use to program your application.

The tool also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic reconfiguration makes it possible to change configurations at run time. In essence, this lets you to use more than 100 percent of PSoC's resources for an application.

#### Code Generation Tools

The code generation tools work seamlessly within the PSoC Designer interface and have been tested with a full range of debugging tools. You can develop your design in C, assembly, or a combination of the two.

**Assemblers**. The assemblers allow you to merge assembly code seamlessly with C code. Link libraries automatically use absolute addressing or are compiled in relative mode, and linked with other software modules to get absolute addressing.

**C Language Compilers**. C language compilers are available that support the PSoC family of devices. The products allow you to create complete C programs for the PSoC family devices. The optimizing C compilers provide all of the features of C, tailored to the PSoC architecture. They come complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

#### Debugger

PSoC Designer has a debug environment that provides hardware in-circuit emulation, allowing you to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow you to read and program and read and write data memory, and read and write I/O registers. You can read and write CPU registers, set and clear breakpoints, and provide program run, halt, and step control. The debugger also lets you to create a trace buffer of registers and memory locations of interest.

#### Online Help System

The online help system displays online, context-sensitive help. Designed for procedural and quick reference, each functional subsystem has its own context-sensitive help. This system also provides tutorials and links to FAQs and an Online Support Forum to aid the designer.

#### In-Circuit Emulator

A low-cost, high-functionality in-circuit emulator (ICE) is available for development support. This hardware can program single devices.

The emulator consists of a base unit that connects to the PC using a USB port. The base unit is universal and operates with all PSoC devices. Emulation pods for each device family are available separately. The emulation pod takes the place of the PSoC device in the target board and performs full-speed (24 MHz) operation.

### **Designing with PSoC Designer**

The development process for the PSoC device differs from that of a traditional fixed-function microprocessor. The configurable analog and digital hardware blocks give the PSoC architecture a unique flexibility that pays dividends in managing specification change during development and lowering inventory costs. These configurable resources, called PSoC blocks, have the ability to implement a wide variety of user-selectable functions. The PSoC development process is:

- 1. Select user modules.

- 2. Configure user modules.

- 3. Organize and connect.

- 4. Generate, verify, and debug.

#### **Select User Modules**

PSoC Designer provides a library of prebuilt, pretested hardware peripheral components called "user modules." User modules make selecting and implementing peripheral devices, both analog and digital, simple.

#### **Configure User Modules**

Each user module that you select establishes the basic register settings that implement the selected function. They also provide parameters and properties that allow you to tailor their precise configuration to your particular application. For example, a PWM User Module configures one or more digital PSoC blocks, one for each eight bits of resolution. Using these parameters, you can establish the pulse width and duty cycle. Configure the parameters and properties to correspond to your chosen application. Enter values directly or by selecting values from drop-down menus. All of the user modules are documented in datasheets that may be viewed directly in PSoC Designer or on the Cypress website. These user module datasheets explain the internal operation of the user module and provide performance specifications. Each datasheet describes the use of each user module parameter, and other information that you may need to successfully implement your design.

#### **Organize and Connect**

Build signal chains at the chip level by interconnecting user modules to each other and the I/O pins. Perform the selection, configuration, and routing so that you have complete control over all on-chip resources.

#### Generate, Verify, and Debug

When you are ready to test the hardware configuration or move on to developing code for the project, perform the "Generate Configuration Files" step. This causes PSoC Designer to generate source code that automatically configures the device to your specification and provides the software for the system. The generated code provides APIs with high-level functions to control and respond to hardware events at run time, and interrupt service routines that you can adapt as needed.

A complete code development environment lets you to develop and customize your applications in C, assembly language, or both.

The last step in the development process takes place inside PSoC Designer's Debugger (accessed by clicking the Connect icon). PSoC Designer downloads the HEX image to the ICE where it runs at full-speed. PSoC Designer debugging capabilities rival those of systems costing many times more. In addition to traditional single-step, run-to-breakpoint, and watch-variable features, the debug interface provides a large trace buffer. It lets you to define complex breakpoint events that include monitoring address and data bus values, memory locations, and external signals.

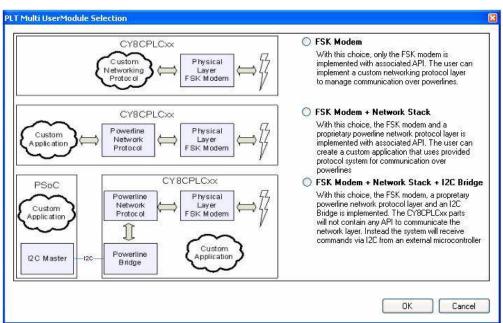

#### **PLC User Modules**

Powerline transceiver (PLT) user module (UM) enables data communication over powerlines up to baud rates of 2400 bps. This UM also exposes all the APIs from the network protocol for ease of application development. The UM, when instantiated, provides the user with three implementation modes:

- FSK Modem Only This mode enables the user to use the raw FSK modem and build any network protocol or application with the help of the APIs generated by the modem PHY.

- FSK Modem + Network Stack This mode enables the user to use the Cypress network protocol for PLC and build any application with the APIs provided by the network protocol.

- FSK Modem + Network Stack + I2C This mode enables the user to interface the CY8CPLC20 with any other microcontroller or PSoC device. Users can also split the application between the PLC device and the external microcontroller. If the external microcontroller is a PSoC device, then the I2C UMs can be used to interface it with the PLC device.

Figure 10 on page 14 shows the starting window for the PLT UM with the three implementation modes from which the user can choose.

Figure 10. PLT User Module

The power consumption estimate of the CY8CPLC20 chip with the PLT User Module loaded along with the other User Modules can be determined using the application note AN54416 titled "Using CY8CPLC20 in Powerline Communication (PLC) Applications" at <a href="http://www.cypress.com">http://www.cypress.com</a>.

#### Pin Information

The CY8CPLC20 PLC device is available in a variety of packages which are listed and illustrated in the following tables. Every port pin (labeled with a "P") is capable of Digital I/O. However, Vss,  $V_{DD}$  and XRES are not capable of Digital I/O.

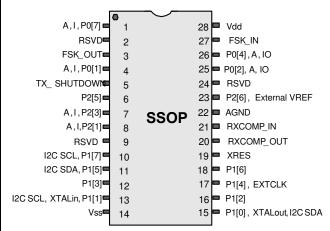

#### 28-Pin Part Pinout

Table 4. 28-Pin Part Pinout (SSOP)

| D:         | Τ\      | ре     |                 |                                                                                                                                                                   |  |  |

|------------|---------|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin<br>No. | Digital | Analog | Pin Name        | Description                                                                                                                                                       |  |  |

| 1          | I/O     |        | P0[7]           | Analog column mux input                                                                                                                                           |  |  |

| 2          | Res     | erved  | RSVD            | Reserved                                                                                                                                                          |  |  |

| 3          |         | 0      | FSK_OUT         | Analog FSK Output                                                                                                                                                 |  |  |

| 4          | I/O     |        | P0[1]           | Analog column mux input                                                                                                                                           |  |  |

| 5          | 0       |        | TX_SHUTD<br>OWN | Output to disable PLC transmit<br>circuitry in receive mode<br>Logic '0' - When the Modem is<br>transmitting<br>Logic '1' - When the Modem is not<br>transmitting |  |  |

| 6          | I/O     |        | P2[5]           |                                                                                                                                                                   |  |  |

| 7          | I/O     | I      | P2[3]           | Direct switched capacitor block Input                                                                                                                             |  |  |

| 8          | I/O     |        | P2[1]           | Direct switched capacitor block Input                                                                                                                             |  |  |

| 9          | Res     | erved  | RSVD            | Reserved                                                                                                                                                          |  |  |

| 10         | I/O     |        | P1[7]           | I <sup>2</sup> C Serial clock (SCL)                                                                                                                               |  |  |

| 11         | I/O     |        | P1[5]           | I <sup>2</sup> C Serial data (SDA)                                                                                                                                |  |  |

| 12         | I/O     |        | P1[3]           | XTAL_STABILITY. Connect a 0.1 μF capacitor between the pin and Vss.                                                                                               |  |  |

| 13         | I/O     |        | P1[1]           | Crystal (XTALin <sup>[2]</sup> ), ISSP-SCLK <sup>[1]</sup> , I <sup>2</sup> C SCL                                                                                 |  |  |

| 14         | Po      | wer    | Vss             | Ground Connection                                                                                                                                                 |  |  |

| 15         | I/O     |        | P1[0]           | Crystal (XTALout <sup>[2]</sup> ),<br>ISSP-SDATA <sup>[1]</sup> , I <sup>2</sup> C SDA                                                                            |  |  |

| 16         | I/O     |        | P1[2]           |                                                                                                                                                                   |  |  |

| 17         | I/O     |        | P1[4]           | Optional External Clock Input (EXTCLK <sup>[2]</sup> )                                                                                                            |  |  |

| 18         | I/O     |        | P1[6]           |                                                                                                                                                                   |  |  |

| 19         | In      | put    | XRES            | Active high external reset with internal pull-down                                                                                                                |  |  |

| 20         |         | 0      | RXCOMP_<br>OUT  | Analog Output To External Low Pass Filter Circuitry                                                                                                               |  |  |

| 21         |         |        | RXCOMP_<br>IN   | Analog Input From The External Low Pass Filter Circuitry                                                                                                          |  |  |

| 22         | Analog  | Ground | AGND            | Analog Ground. Connect a 1.0 μF capacitor between the pin and Vss.                                                                                                |  |  |

| 23         | I/O     |        | P2[6]           | External Voltage Reference (VREF)                                                                                                                                 |  |  |

| 24         | Res     | erved  | RSVD            | Reserved                                                                                                                                                          |  |  |

| 25         | I/O     | I/O    | P0[2]           | Analog column mux input and column output                                                                                                                         |  |  |

| 26         | I/O     | I/O    | P0[4]           | Analog column mux input and column output                                                                                                                         |  |  |

| 27         |         |        | FSK_IN          | Analog FSK Input                                                                                                                                                  |  |  |

| 28         | Po      | wer    | $V_{DD}$        | Supply Voltage                                                                                                                                                    |  |  |

Figure 11. CY8CPLC20 28-Pin PLC Device

$\textbf{LEGEND} : A = Analog, \ I = Input, \ O = Output., \ RSVD = Reserved \ (Should be left unconnected)$

#### Notes

- 1. These are the ISSP pins, which are not High Z at POR (Power On Reset). See the PSoC Technical Reference Manual for details.

- When using the PLT user module, the external crystal is always required for protocol timing. For the FSK modem, either enable the PLL Mode or select the external 24 MHz on P1[4]. Do not use the IMO.

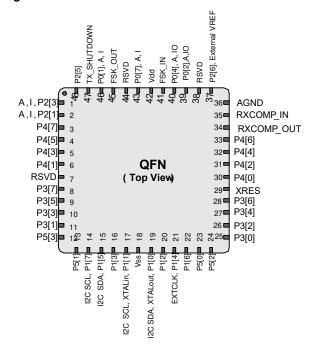

### 48-Pin Part Pinout

## Table 5. 48-Pin Part Pinout (QFN)[3]

| T          |         |               |                 |                                                                                                                                                        |  |  |  |  |

|------------|---------|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin<br>No. | Digital | rpe<br>Analog | Pin Name        | Description                                                                                                                                            |  |  |  |  |

| 1          | I/O     | ı             | P2[3]           | Direct switched capacitor block input                                                                                                                  |  |  |  |  |

| 2          | I/O     | ı             | P2[1]           | Direct switched capacitor block input                                                                                                                  |  |  |  |  |

| 3          | I/O     |               | P4[7]           |                                                                                                                                                        |  |  |  |  |

| 4          | I/O     |               | P4[5]           |                                                                                                                                                        |  |  |  |  |

| 5          | I/O     |               | P4[3]           |                                                                                                                                                        |  |  |  |  |

| 6          | I/O     |               | P4[1]           |                                                                                                                                                        |  |  |  |  |

| 7          | Rese    | erved         | RSVD            | Reserved                                                                                                                                               |  |  |  |  |

| 8          | I/O     |               | P3[7]           |                                                                                                                                                        |  |  |  |  |

| 9          | I/O     |               | P3[5]           |                                                                                                                                                        |  |  |  |  |

| 10         | I/O     |               | P3[3]           |                                                                                                                                                        |  |  |  |  |

| 11         | I/O     |               | P3[1]           |                                                                                                                                                        |  |  |  |  |

| 12         | I/O     |               | P5[3]           |                                                                                                                                                        |  |  |  |  |

| 13         | I/O     |               | P5[1]           |                                                                                                                                                        |  |  |  |  |

| 14         | I/O     |               | P1[7]           | I <sup>2</sup> C Serial clock (SCL)                                                                                                                    |  |  |  |  |

| 15         | I/O     |               | P1[5]           | I <sup>2</sup> C Serial data (SDA)                                                                                                                     |  |  |  |  |

| 16         | I/O     |               | P1[3]           | XTAL STABILITY. Connect a 0.1 μF                                                                                                                       |  |  |  |  |

|            |         |               |                 | capacitor between the pin and Vss.                                                                                                                     |  |  |  |  |

| 17         | I/O     |               | P1[1]           | Crystal (XTALin <sup>[2]</sup> ), I <sup>2</sup> C Serial Clock (SCL), ISSP-SCLK <sup>[1]</sup>                                                        |  |  |  |  |

| 18         | Po      | wer           | Vss             | Ground Connection                                                                                                                                      |  |  |  |  |

| 19         | I/O     |               | P1[0]           | Crystal (XTALout <sup>[2]</sup> ), I <sup>2</sup> C Serial Data (SDA), ISSP-SDATA <sup>[1]</sup>                                                       |  |  |  |  |

| 20         | I/O     |               | P1[2]           |                                                                                                                                                        |  |  |  |  |

| 21         | I/O     |               | P1[4]           | Optional External clock input (EXTCLK <sup>[2]</sup> )                                                                                                 |  |  |  |  |

| 22         | I/O     |               | P1[6]           |                                                                                                                                                        |  |  |  |  |

| 23         | I/O     |               | P5[0]           |                                                                                                                                                        |  |  |  |  |

| 24         | I/O     |               | P5[2]           |                                                                                                                                                        |  |  |  |  |

| 25         | I/O     |               | P3[0]           |                                                                                                                                                        |  |  |  |  |

| 26         | I/O     |               | P3[2]           |                                                                                                                                                        |  |  |  |  |

| 27         | I/O     |               | P3[4]           |                                                                                                                                                        |  |  |  |  |

| 28         | I/O     |               | P3[6]           |                                                                                                                                                        |  |  |  |  |

| 29         | In      | put           | XRES            | Active high external reset with internal pull-down                                                                                                     |  |  |  |  |

| 30         | I/O     |               | P4[0]           |                                                                                                                                                        |  |  |  |  |

| 31         | I/O     |               | P4[2]           |                                                                                                                                                        |  |  |  |  |

| 32         | I/O     |               | P4[4]           |                                                                                                                                                        |  |  |  |  |

| 33         | I/O     |               | P4[6]           |                                                                                                                                                        |  |  |  |  |

| 34         |         | 0             | RXCOMP_<br>OUT  | Analog output to external Low Pass Filter Circuitry                                                                                                    |  |  |  |  |

| 35         |         | I             | RXCOMP_<br>IN   | Analog input from external Low Pass Filter Circuitry                                                                                                   |  |  |  |  |

| 36         | Analog  | Ground        | AGND            | Analog ground. Connect a 1.0 µF capacitor between the pin and Vss.                                                                                     |  |  |  |  |

| 37         | I/O     |               | P2[6]           | External Voltage Reference (VREF)                                                                                                                      |  |  |  |  |

| 38         | Rese    | erved         | RSVD            | Reserved                                                                                                                                               |  |  |  |  |

| 39         | I/O     | I/O           | P0[2]           | Analog column mux input and column output                                                                                                              |  |  |  |  |

| 40         | I/O     | I/O           | P0[4]           | Analog column mux input and column output                                                                                                              |  |  |  |  |

| 41         |         |               | FSK_IN          | Analog FSK Input                                                                                                                                       |  |  |  |  |

| 42         | Po      | wer           | $V_{DD}$        | Supply Voltage                                                                                                                                         |  |  |  |  |

| 43         | I/O     |               | P0[7]           | Analog Column Mux Input                                                                                                                                |  |  |  |  |

| 44         | Rese    | erved         | RSVD            | Reserved                                                                                                                                               |  |  |  |  |

| 45         |         | 0             | FSK_OUT]        | Analog FSK Output                                                                                                                                      |  |  |  |  |

| 46         | I/O     |               | P0[1]           | Analog Column Mux Input                                                                                                                                |  |  |  |  |

| 47         | 0       |               | TX_SHUT<br>DOWN | Output to disable transmit circuitry in receive mode Logic '0' - When the Modem is transmitting Logic '1' - When the Modem is not transmitting milting |  |  |  |  |

| 48         | I/O     |               | P2[5]           | 9                                                                                                                                                      |  |  |  |  |

|            |         |               | 6-3             | 1                                                                                                                                                      |  |  |  |  |

Figure 12. CY8CPLC20 48-Pin PLC Device

48 I/O P2[5] LEGEND: A = Analog, I = Input, O = Output, RSVD = Reserved (should be left unconnected).

Note

3. The QFN package has a center pad that must be connected to ground (Vss).

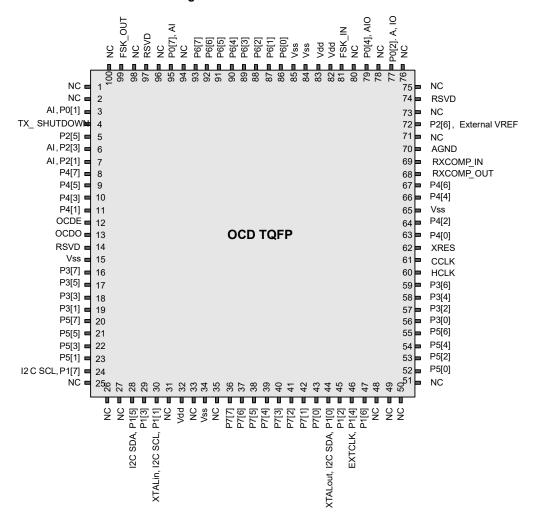

### 100-Pin Part Pinout (On-Chip Debug)

The 100-pin TQFP part is for the CY8CPLC20-OCD On-Chip Debug PLC device. Note that the OCD parts are only used for in-circuit debugging. OCD parts are NOT available for production.

Table 6. 100-Pin OCD Part Pinout (TQFP)

| Pin<br>No. | Digital    | Analog | Name            | Description                                                                                                                                    | Pin<br>No. | Digital       | Analog | Name                     | Description                                                                                     |

|------------|------------|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|--------|--------------------------|-------------------------------------------------------------------------------------------------|

| 1          |            |        | NC              | No connection                                                                                                                                  | 51         |               |        | NC                       | No connection                                                                                   |

| 2          |            |        | NC              | No connection                                                                                                                                  | 52         | I/O           |        | P5[0]                    |                                                                                                 |

| 3          | I/O        |        | P0[1]           | Analog column mux input                                                                                                                        | 53<br>54   | I/O           |        | P5[2]                    |                                                                                                 |

| 4          | 0          |        | TX_SHUT<br>DOWN | Output to disable transmit circuitry in receive mode Logic '0' - When the Modem is transmitting Logic '1' - When the Modem is not transmitting |            | 1/0           |        | P5[4]                    |                                                                                                 |

| 5          | I/O        |        | P2[5]           |                                                                                                                                                | 55         | I/O           |        | P5[6]                    |                                                                                                 |

| 6          | I/O        | ı      | P2[3]           | Direct switched capacitor block input                                                                                                          | 56         | I/O           |        | P3[0]                    |                                                                                                 |

| 7          | I/O        | ı      | P2[1]           | Direct switched capacitor block input                                                                                                          | 57         | I/O           |        | P3[2]                    |                                                                                                 |

| 8          | I/O        |        | P4[7]           |                                                                                                                                                | 58         | I/O           |        | P3[4]                    |                                                                                                 |

| 9          | I/O        |        | P4[5]           |                                                                                                                                                | 59         | I/O           |        | P3[6]                    |                                                                                                 |

| 10         | 1/0        |        | P4[3]           |                                                                                                                                                | 60         |               |        | HCLK                     | OCD high speed clock output                                                                     |

| 11         | I/O        |        | P4[1]           |                                                                                                                                                | 61         | ļ             |        | CCLK                     | OCD CPU clock output                                                                            |

| 12         |            |        | OCDE            | OCD even data I/O                                                                                                                              | 62         |               | put    | XRES                     | Active high pin reset with internal pull-down                                                   |

| 13         | _          |        | OCDO            | OCD odd data output                                                                                                                            | 63         | I/O           |        | P4[0]                    |                                                                                                 |

| 14         | Rese       |        | RSVD            | Reserved                                                                                                                                       | 64         | 1/0           |        | P4[2]                    |                                                                                                 |

| 15         | Pov        | wer    | Vss             | Ground connection                                                                                                                              | 65         |               | wer    | Vss                      | Ground connection                                                                               |

| 16         | 1/0        |        | P3[7]           |                                                                                                                                                | 66         | 1/0           |        | P4[4]                    |                                                                                                 |

| 17         | 1/0        |        | P3[5]           |                                                                                                                                                | 67         | I/O           |        | P4[6]                    |                                                                                                 |

| 18         | 1/0        |        | P3[3]<br>P3[1]  |                                                                                                                                                | 68<br>69   |               | 0      | RXCOMP<br>_OUT<br>RXCOMP | Analog output to external low pass filter circuitry  Analog Input from external low pass filter |

|            | 1/0        |        |                 |                                                                                                                                                | 70         | C**           | ound   | _IN<br>AGND              | circuitry                                                                                       |

| 20         |            |        | P5[7]           |                                                                                                                                                |            |               | ouna   |                          | Analog ground. connect a 1.0 µF capacitor between the pin and Vss.                              |

| 21         | 1/0        |        | P5[5]<br>P5[3]  |                                                                                                                                                | 71         | 1/0           | ı      | NC<br>P2[6]              | no connection                                                                                   |