# INTEGRATED CIRCUITS

Product Specification Revision 3.1 PUBLIC INFORMATION 2006 July 18 079231

### CONTENTS

| 1                                     | FEATURES 3                                                                                                      |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1.1<br>1.2<br>1.3<br>1.4              | Protocol.3Memory.3Supported Standards3Security Features3                                                        |

| 1.5                                   | Delivery Types 3                                                                                                |

| 2                                     | GENERAL DESCRIPTION 4                                                                                           |

| 2.1<br>2.1.1<br>2.1.2<br>2.1.3        | Target Markets4Animal Identification4Laundry Automation4Beer Keg and Gas Cylinder Logistic4                     |

| 2.1.4<br>2.1.5<br>2.1.6               | Pigeon Race Sports       4         Security Applications       4         Access Control, Company Cards,       4 |

| 2.2                                   | Amusement Parks.4Customer Application Support andTraining.4                                                     |

| 3                                     | ORDERING INFORMATION 5                                                                                          |

| 4                                     | BLOCKDIAGRAM 6                                                                                                  |

| 5                                     | REFERENCE DOCUMENTS 6                                                                                           |

| 6                                     | MEMORY ORGANISATION 7                                                                                           |

| 6.1<br>6.1.1<br>6.2<br>6.3            | Unique Identifier (UID)8Product identifier (PID)8HITAG S Plain Mode8HITAG S Authentication Mode9                |

| 7                                     | FUNCTIONAL DESCRIPTION 10                                                                                       |

| 7.1<br>7.2<br>7.3                     | Basic System Configuration                                                                                      |

| 7.3.1<br>7.3.2<br>7.4                 | Coding.13Data Rate14Data Transmission: Read/Write Device $\rightarrow$ Transponder (Physical Layer).15          |

| 7.4.1<br>7.4.2                        | Coding15Modulation details17                                                                                    |

| 8                                     | CONFIGURATION 18                                                                                                |

| 8.1<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3 | Configuration Page18Delivery Configuration21HITAG S3221HITAG S25622HITAG S204823                                |

| 9                                     | PROTOCOL TIMING 24                                                                                              |

| 9.1<br>9.2                            | Read/Write Device waiting time before sending<br>the first command                                              |

|                                       | a subsequent command 25                                                                                         |

# HTS IC H32/HTS IC H56/HTS IC H48

| 9.3<br>9.4                                                                                                   | Reset Time                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.5<br>9.6                                                                                                   | an EOF                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9.7                                                                                                          | transmitting data in TTF Mode                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10                                                                                                           | STATE DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10.1<br>10.2<br>10.3                                                                                         | General Description of States31HITAG S 3232HITAG S 256 and HITAG S 204833                                                                                                                                                                                                                                                                                                                                                                                           |

| 11                                                                                                           | COMMAND SET                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br>11.11<br>12<br>12.1<br>12.2 | General Comments       34         UID REQUEST xx       34         AC SEQUENCE       35         SELECT (UID)       36         CHALLENGE       37         SELECT_QUIET (UID)       38         READ PAGE       38         READ BLOCK       39         WRITE PAGE       40         WRITE BLOCK       41         QUIET       42         TRANSPONDER TALKS FIRST (TTF)       MODE         MODE       43         32 Bit TTF Mode       43         64 Bit TTF Mode       43 |

| 12.3<br>13                                                                                                   | 128 Bit TTF Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 13.1                                                                                                         | OF CRC                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13.2                                                                                                         | HITAG S Transponder                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13.2.1<br>13.2.2                                                                                             | Read/Write Device.45Standard Response Protocol Mode.45Advanced/Fast Advanced ResponseProtocol Mode45                                                                                                                                                                                                                                                                                                                                                                |

| 13.3                                                                                                         | Source Code for CRC-Checksum 46                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14                                                                                                           | ABBREVIATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15                                                                                                           | DATA SHEET STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16                                                                                                           | DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 17                                                                                                           | DISCLAIMERS                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 18                                                                                                           | REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# HTS IC H32/HTS IC H56/HTS IC H48

### **1 FEATURES**

- Integrated Circuit for Contactless Identification Transponders and Cards

- Integrated resonance capacitor of 210 pF with  $\pm\,5$  % tolerance over full production

- Frequency range 100..150 kHz.

#### 1.1 Protocol

- Modulation Read/Write Device → Transponder: 100 % ASK and Binary Pulse Length Coding

- Modulation Transponder → Read/Write Device: Strong ASK modulation with Anticollision, Manchester and Biphase Coding

- Fast Anticollision Protocol for inventory tracking: 100 Tags in 3.2 seconds

- Data integrity check (CRC)

- Optional Transponder Talks First Modes with user defined data length

- Temporary switch from Transponder Talks First into Reader Talks First Mode

- Data Rate Read/Write Device to Transponder: 5.2 kBit/s

- Data Rates Transponder to Read/Write Device: 2 kBit/s, 4 kBit/s, 8 kBit/s

#### 1.2 Memory

- Three memory options (32 Bit UID, 256 Bit, 2048 Bit)

- More than 100000 erase/write cycles

- 10 years non volatile data retention

- Secure Memory Lock functionality

#### 1.3 Supported Standards

- Full compliant to ISO 11784/85 Animal ID

- Targeted to operated on hardware infrastructure of new upcoming standards

- ISO14223 (Animal ID with anticollision and read/write functionality)

- ISO 18000-2 (AIDC Techniques-RFID or Item Management)

- Supports German Waste Management Standard and Pigeon Race Standard

### 1.4 Security Features

- 32 Bit Unique Identification Number (UID)

- 48 Bit secret key based encrypted authentication

#### 1.5 Delivery Types

- Sawn, gold bumped 8" Wafer

- Contactless Chip Card Module MOA2

- I Connect (Low Cost Flip Chip Package)

# HTS IC H32/HTS IC H56/HTS IC H48

### 2 GENERAL DESCRIPTION

The HITAG<sup>™</sup> product line is well known and established in the contactless identification market.

Due to the open marketing strategy of Philips Semiconductors there are various manufacturers well established for both the transponders / cards as well as the Read/Write Devices. All of them supporting HITAG 1 and HITAG 2 transponder IC's. With the new HITAG S family, this existing infrastructure is extended with the next generation of IC's being substantially smaller in mechanical size, lower in cost, offering more operation distance and speed, but still being operated with the same reader infrastructure and transponder manufacturing equipment.

#### One Protocol - three memory options.

The protocol and command structure for HITAG S is based on HITAG 1, including anticollision algorithm.

Three different memory sizes are offered and can be operated using exactly the same protocol.

| HITAG S 32   | 32 Bit Unique Identifier | Read Only  |

|--------------|--------------------------|------------|

| HITAG S 256  | 256 Bit Total Memory     | Read/Write |

| HITAG S 2048 | 2048 Bit Total Memory    | Read/Write |

### 2.1 Target Markets

#### 2.1.1 ANIMAL IDENTIFICATION

Basically, the animal id market can be divided into two different areas:

#### a) Identification of pet animals

Some countries require that the your dog/cat is being microchiped prior to immigration. But it is also of advantage in case your pet is getting lost. The microchiped pet gets easily identified with a handheld reader and thus can be distinguished from stray animals.

The ISO standard 11784/85 is well established in this markets and HITAG S 256 and HITAG S 2048 are compliant to this standard, while offering additional memory for storage of customised off line data, such as phone number/address of the pets owner.

# b) Identification and Tracking of livestock like cattle, pork and sheep

Being compatible with the ISO 11784/85 reader infrastructure, HITAG S can be switched temporarily into read/write mode, thus enabling additional features, like e.g. off line data storage directly on the animals tag

This concept has already been standardised within ISO 14223/1.

#### 2.1.2 LAUNDRY AUTOMATION

- Identify 200 pcs of garment with one Read/Write Device

- Long operation distance with typical small shaped laundry button transponders

- Insensitive to harsh conditions like pressure, heat and water.

#### 2.1.3 BEER KEG AND GAS CYLINDER LOGISTIC

- Recognising a complete pallet of gas cylinders at one time.

- Long writing distance.

- Voluntarily change between TTF Mode with user defined data length and Read/Write Modes with out changing the configuration on the transponder.

- Authenticity check at the beer pubs- between beer bumper and supplied beer keg, provides a safe protection of the beer brand.

### 2.1.4 PIGEON RACE SPORTS

According to European pigeon race standards, offering the additional shadow memory, that is required in some European companies.

#### 2.1.5 SECURITY APPLICATIONS

Authenticity check for high level brands or for original refilling e.g. toner for fax machines.

#### 2.1.6 ACCESS CONTROL, COMPANY CARDS, AMUSEMENT PARKS

The included encrypted authentication feature is well suited for applications like access control and vending machines. In particular the combined application with one company card opening the barrier for the car parking, opening the access to the building and rooms with different security levels, offering drinks and coffee from the vending machines in the socialising area.

### 2.2 Customer Application Support and Training

Within the dedicated CAS team within the BU Identification.

Please Contact:

### info.bli@philips.com

Accompanying Data Sheets and Application Notes:

http://www.semiconductors.com/markets/identification/ customer/download/index.html#hitag

# HTS IC H32/HTS IC H56/HTS IC H48

### **3 ORDERING INFORMATION**

| EXTENDED TYPE<br>NUMBER   | DESCRIPTION                    | MEMORY<br>SIZE   | ORDERING<br>CODE | PACKAGE   | TEMPERATURE<br>RANGE (°C) |  |

|---------------------------|--------------------------------|------------------|------------------|-----------|---------------------------|--|

| HTS IC H32 01EW/V4        | Sawn 8" wafer on foil (FFC),   | <b>32</b> Bit    | 9352 729 70005   | —         |                           |  |

| HTS IC H56 01EW/V4        | 150 $\mu$ m, inked and mapped, | 2 <b>56</b> Bit  | 9352 729 71005   | —         | -25 °C to +85 °C          |  |

| HTS IC H48 01EW/V4        | with gold bumps                | 20 <b>48</b> Bit | 9352 729 73005   | —         |                           |  |

|                           |                                |                  |                  |           |                           |  |

| HTS MO <b>H32</b> 01EV    | MOA2 Package                   | <b>32</b> Bit    | 9352 729 69118   |           | -25 °C to +85 °C          |  |

| HTS MO <b>H56</b> 01EV    |                                | 2 <b>56</b> Bit  | 9352 729 72118   | SOT500AA1 |                           |  |

| HTS MO H48 01EV           |                                | 20 <b>48</b> Bit | 9352 729 74118   |           |                           |  |

|                           |                                |                  |                  |           |                           |  |

| HTS FC H32 01EV/DH        | Flip Chip Package, Hot         | 32 Bit           | 9352 729 75118   |           |                           |  |

| HTS FC H56 01EV/DH        | Laminated                      | 2 <b>56</b> Bit  | 9352 729 76118   | SOT732AA1 | -25 °C to +85 °C          |  |

| HTS FC <b>H48</b> 01EV/DH |                                | 20 <b>48</b> Bit | 9352 729 77118   |           |                           |  |

# HTS IC H32/HTS IC H56/HTS IC H48

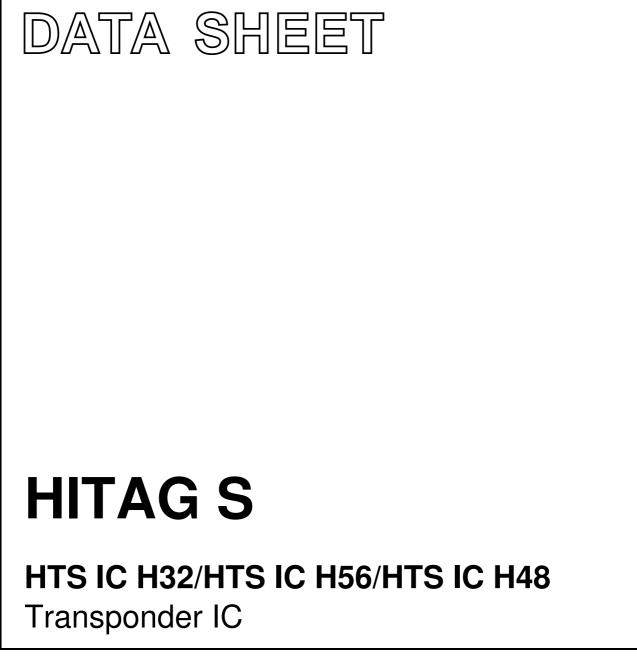

### 4 BLOCKDIAGRAM

The HITAG S Transponder requires no external power supply. The contactless interface generates the power supply and the system clock via the resonant circuitry by inductive coupling to the Read/Write Device (RWD). The interface also demodulates data transmitted from the RWD to the HITAG S Transponder, and modulates the magnetic field for data transmission from the HITAG S Transponder to the RWD.

Data are stored in a non-volatile memory (EEPROM). The EEPROM has a capacity up to 2048 Bit and is organised in 64 Pages consisting of 4 Bytes each (1 Page = 32 Bits).

#### 5 REFERENCE DOCUMENTS

- General Quality Specification

- General Specification for 8" Wafer

- Bumped Wafer Specification

- Addendum Bumped Wafer Specification HTS IC H32/ HTS IC H56/ HTS IC H48 (electrical values)

- Contactless Chip Card Module Specification

- Addendum Contactless Chip Card Module Specification HTS MO H32/HTS MO H56/HTS MO H48

- Flip Chip Package Specification

- Addendum Flip Chip Package Specification HTS FC H32/HTS FC H56/HTS FC H48

- Application Note HITAG S Coil Design Guide.

# HTS IC H32/HTS IC H56/HTS IC H48

### 6 MEMORY ORGANISATION

|          | 1               |          | , н      | ITAG S Ty | ре  |

|----------|-----------------|----------|----------|-----------|-----|

|          | Page<br>Address | 32 Bit   | H32      | H56       | H48 |

| -        | 0x00            | Page 0   |          |           |     |

| Block 0  | 0x01            | Page 1   | <u>`</u> |           |     |

| loc      | 0x02            | Page 2   |          |           |     |

| ш        | 0x03            | Page 3   |          |           |     |

| -        | 0x04            | Page 4   |          |           |     |

| *<br>-   | 0x05            | Page 5   |          |           |     |

| Block 1  | 0x06            | Page 6   |          |           |     |

| ш        | 0x07            | Page 7   |          | •         |     |

| -        | 0x08            | Page 8   |          | <u> </u>  |     |

| Block 2  | 0x09            | Page 9   |          |           |     |

|          | 0x0A            | Page10   |          |           |     |

| ш        | 0x0B            | Page 11  |          |           |     |

|          | 0x0C            | Page 12  |          |           |     |

| Х<br>С   | 0x0D            | Page 13  |          |           |     |

| Block 3  | 0x0E            | Page 14  |          |           |     |

|          | 0x0F            | Page 15  |          |           |     |

| _        | 0x10            | Page 16  |          |           |     |

|          | 0x3B            | Page 59  |          |           |     |

| -        | 0x3C            | Page 60  |          |           |     |

| Block 15 | 0x3D            | Page 61  |          |           |     |

| š        | 0x3E            | Page 62  |          |           |     |

| Ē        | 0x3F            | Page 63  |          |           |     |

| -        |                 | . 490 00 |          |           |     |

The EEPROM has a capacity up to 2048 Bit and is organised in 16 Blocks, consisting of 4 Pages each, for commands with Block access. A Page consists of 4 Bytes each (1 Page = 32 Bits) and is the smallest access unit.

Addressing is done Page by Page (Page 0 up to 63) and access is gained either Page by Page or Block by Block entering the respective Page start address. In case of Block Read/Write access, the transponder is processed from the start Page address within one block to the end of the corresponding block.

Three different types of HITAG S IC's with different memory sizes as shown in the figure above are available.

### HTS IC H32/HTS IC H56/HTS IC H48

### 6.1 Unique Identifier (UID)

Page 0 contains the 32 Bit Unique Identifier (UID) which is programmed during the manufacturing process. Page 0 access: Read Only (RO)

|              |     | MSByte |     |       |     |     |       |     |     | LSByte |     |

|--------------|-----|--------|-----|-------|-----|-----|-------|-----|-----|--------|-----|

| Page Address | MSB | LSB    | MSB |       | LSB | MSB |       | LSB | MSB |        | LSB |

| 0x00         |     | UID 3  |     | UID 2 |     |     | UID 1 |     |     | UID 0  |     |

#### 6.1.1 PRODUCT IDENTIFIER (PID)

The Product Identifier (PID) for the HITAG S Transponder IC is coded in the UID 3 Byte of the Unique Identifier (UID). This enables to distinguish between different ICs of the HITAG family.

| UI    | D3    |

|-------|-------|

| MSB   | LSB   |

| PID 1 | PID 0 |

Condition for HITAG S: PID 1 = 0x7 - 0xF and PID  $0 \neq 0x5 - 0x6$

#### 6.2 HITAG S Plain Mode

#### Page 1

In Plain Mode, Page 1 contains three configuration Bytes CON 0 to CON 2 and a reserved byte.

|              | MSByte   | •   |     |       |     |     |       |     |     | LSByte |     |

|--------------|----------|-----|-----|-------|-----|-----|-------|-----|-----|--------|-----|

| Page Address | MSB      | LSB | MSB |       | LSB | MSB |       | LSB | MSB |        | LSB |

| 0x01         | Reserved | d   |     | CON 2 |     |     | CON 1 |     |     | CON 0  |     |

### Page 2 - 63

In Plain Mode, Pages 2 - 63 can be used to store user data.

|              |     | MSByte |     |     |        |     |     |        |     |     | LSByte |     |

|--------------|-----|--------|-----|-----|--------|-----|-----|--------|-----|-----|--------|-----|

| Page Address | MSB |        | LSB |

| 0x02-0x3F    |     | Data 3 |     |     | Data 2 |     |     | Data 1 |     |     | Data 0 |     |

#### Memory Map for HITAG S in Plain Mode:

|              | MSByte   |         |         | LSByte  |

|--------------|----------|---------|---------|---------|

| Page Address | MSB LSB  | MSB LSB | MSB LSB | MSB LSB |

| 0x00         | UID 3    | UID 2   | UID 1   | UID 0   |

| 0x01         | Reserved | CON 2   | CON 1   | CON 0   |

| 0x02         | Data 3   | Data 2  | Data 1  | Data 0  |

| 0x03         | Data 3   | Data 2  | Data 1  | Data 0  |

|              |          |         |         |         |

# HTS IC H32/HTS IC H56/HTS IC H48

### 6.3 HITAG S Authentication Mode

#### Page 1

In Authentication Mode, Page 1 contains three configuration Bytes CON 0 to CON 2 and the password high Byte PWDH 0.

|              |     | MSByte |     |       |     |     |       |     |     | LSByte |     |

|--------------|-----|--------|-----|-------|-----|-----|-------|-----|-----|--------|-----|

| Page Address | MSB | LSB    | MSB |       | LSB | MSB |       | LSB | MSB |        | LSB |

| 0x01         |     | PWDH 0 |     | CON 2 |     |     | CON 1 |     |     | CON 0  |     |

#### Page 2

In Authentication Mode, Page 2 contains the password low Bytes PWDL 0 and PWDL 1 and the key high Bytes KEYH 0 and KEYH 1.

|              |     | MSByte |     |     |        |     |     |        |     |     | LSByte |     |

|--------------|-----|--------|-----|-----|--------|-----|-----|--------|-----|-----|--------|-----|

| Page Address | MSB |        | LSB |

| 0x02         |     | KEYH 1 |     |     | KEYH 0 |     |     | PWDL 1 |     |     | PWDL 0 |     |

#### Page 3

In Authentication Mode, Page 3 contains the key low Bytes KEYL 0 - KEYL 3.

| MSByte       |        |     |     |        |     | LSByte |     |        |     |

|--------------|--------|-----|-----|--------|-----|--------|-----|--------|-----|

| Page Address | MSB    | LSB | MSB | LSB    | MSB | LSB    | MSB |        | LSB |

| 0x03         | KEYL 3 |     |     | KEYL 2 |     | KEYL 1 |     | KEYL 0 |     |

### Page 4 - 63

|              |     | MSByte |     |     |        |     |     |        |     |     | LSByte |     |

|--------------|-----|--------|-----|-----|--------|-----|-----|--------|-----|-----|--------|-----|

| Page Address | MSB |        | LSB |

| 0x04 – 0x3F  |     | Data 3 |     |     | Data 2 |     |     | Data 1 |     |     | Data 0 |     |

#### Memory Map for HITAG S in Authentication Mode:

|              | MSByte |     |        |     |        |     | LSByte |     |

|--------------|--------|-----|--------|-----|--------|-----|--------|-----|

| Page Address | MSB    | LSB | MSB    | LSB | MSB    | LSB | MSB    | LSB |

| 0x00         | UID 3  |     | UID 2  |     | UID 1  |     | UID 0  |     |

| 0x01         | PWDH 0 |     | CON 2  |     | CON 1  |     | CON 0  |     |

| 0x02         | KEYH 1 |     | KEYH 0 |     | PWDL 1 |     | PWDL 0 |     |

| 0x03         | KEYL 3 |     | KEYL 2 |     | KEYL 1 |     | KEYL 0 |     |

| 0x04         | Data 3 |     | Data 2 |     | Data 1 |     | Data 0 |     |

| 0x05         | Data 3 |     | Data 2 |     | Data 1 |     | Data 0 |     |

|              | 1      |     |        |     |        |     |        | ]   |

# HTS IC H32/HTS IC H56/HTS IC H48

### 7 FUNCTIONAL DESCRIPTION

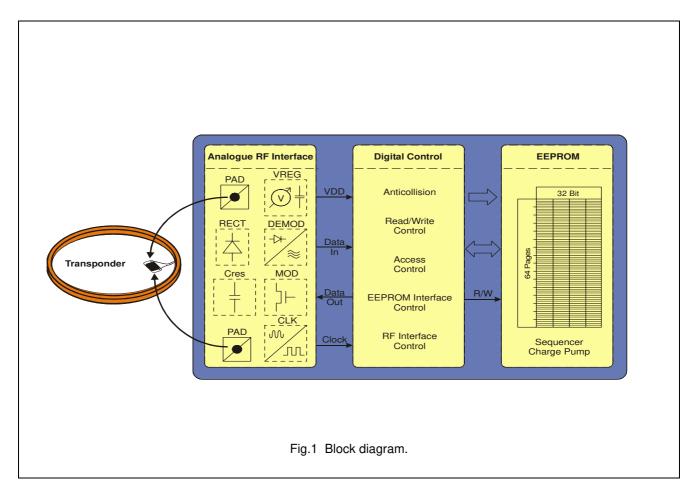

### 7.1 Basic System Configuration

The following block diagram shows in principle the HITAG system configuration

A control and data processing unit controls the modulation of the carrier signal and processes data coming back from the demodulator circuit.

HTS IC H32/HTS IC H56/HTS IC H48

### 7.2 Energy Transmission

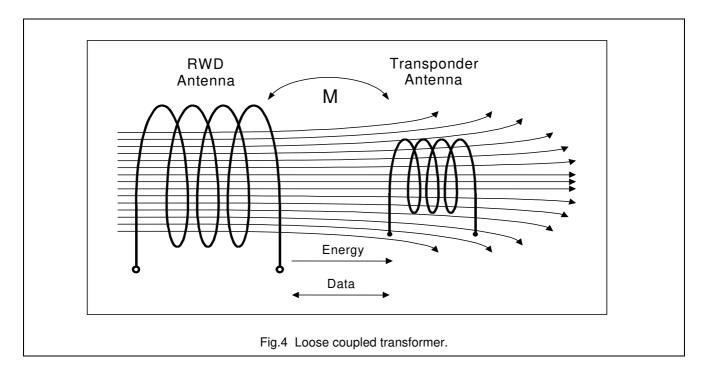

Passive transponders must somehow be supplied with energy to be able to operate. In the HITAG System, this is achieved by using the principle of a loose coupled transformer:

The RWD antenna generates a magnetic field. Some of the generated magnetic flux flows through the transponder antenna and induces a voltage there. The voltage drives a current and the transponder will start operating. As this current will be very small when the transponder is far away from the antenna, the HITAG S Transponder IC is designed for low power consumption.

The principle of a loose coupled transformer enables also a bi-directional data transmission.

# HTS IC H32/HTS IC H56/HTS IC H48

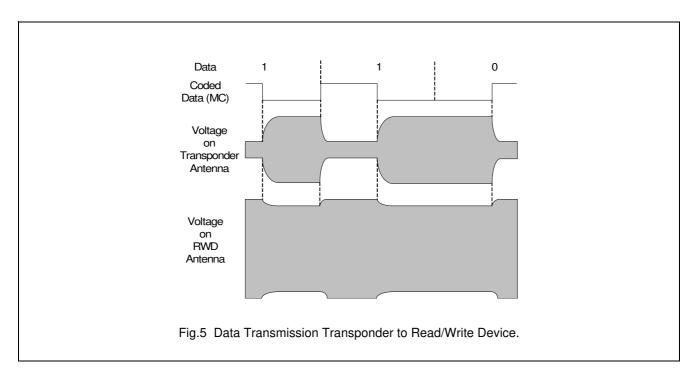

### 7.3 Data Transmission: Transponder $\rightarrow$ Read/Write Device

For data transmission from the HITAG S Transponder to the RWD, the implemented method is called 'load modulation'. Here the HITAG S Transponder continuously changes the load on the magnetic field, by in principle turning on/off a resistor, according to the information to transmit. Alteration of the magnetic field is detected by the receiver of the RWD.

The modulation ratio of the RWD antenna voltage depends on the coupling factor of the antenna configuration (RWD antenna size, transponder antenna size, distance between the antennas,...).

# HTS IC H32/HTS IC H56/HTS IC H48

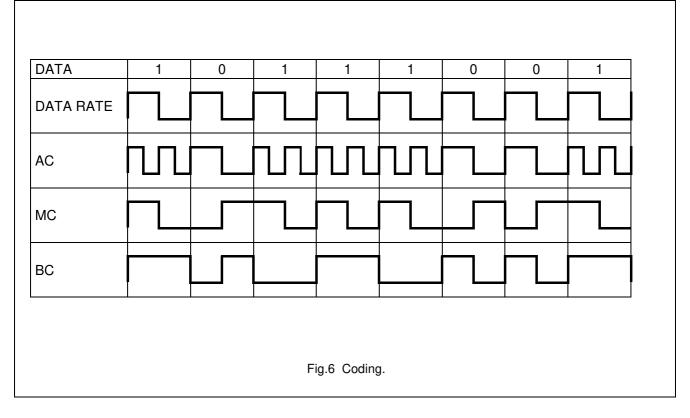

### 7.3.1 CODING

Three different coding techniques for different States and Modes of the HITAG S Transponder IC are used (see also Chapters 11 "Command Set" and 12 "Transponder Talks First (TTF) Mode":

- AC: Anticollision Coding in Init State

- MC: Manchester Coding in Selected State and in Transponder Talks First State

- BC: Biphase Coding in Transponder Talks First State

A high level of the above coding signals means the physical state 'modulator on' (field loaded), a low level means 'modulator off' (field unloaded).

# HTS IC H32/HTS IC H56/HTS IC H48

### 7.3.2 DATA RATE

The data rate for HITAG S Transponder in Reader Talks First (RTF) Mode depends on the corresponding UID REQUEST xx command.

For Transponder Talks First (TTF) Mode the data rate can be defined by configuration

### Table 1

| MODE    | CODING  | BIT RATE | BIT LENGTH        |  |

|---------|---------|----------|-------------------|--|

| HITAG S | AC      | 2 kBit/s | 64 T <sub>0</sub> |  |

| RTF     | AC      | 4 kBit/s | 32 T <sub>0</sub> |  |

|         | MC      | 4 kBit/s | 32 T <sub>0</sub> |  |

| Mode    | INIC    | 8 kBit/s | 16 T <sub>0</sub> |  |

|         |         | 2 kBit/s | 64 T <sub>0</sub> |  |

| HITAG S | MC      | 4 kBit/s | 32 T <sub>0</sub> |  |

|         |         | 8 kBit/s | 16 T <sub>0</sub> |  |

| TTF     |         | 2 kBit/s | 64 T <sub>0</sub> |  |

| Mode    | Biphase | 4 kBit/s | 32 T <sub>0</sub> |  |

|         |         | 8 kBit/s | 16 T <sub>0</sub> |  |

### Note

$T_{0...}$ Carrier period time (<sup>1</sup>/<sub>125 kHz</sub> = 8 µs nominal).

# HTS IC H32/HTS IC H56/HTS IC H48

# 7.4 Data Transmission: Read/Write Device $\rightarrow$ Transponder (Physical Layer)

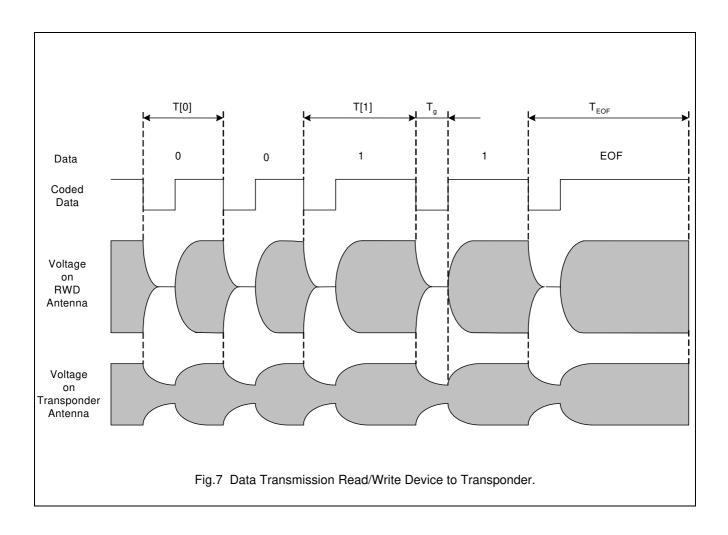

Data are transmitted to the transponder using Amplitude Shift Keying (ASK) modulation with a modulation index of 100 %. When the field is switched off, the physical state is named low field, otherwise high field.

### 7.4.1 CODING

Binary Pulse Length Coding (BPLC) is used to encode the data stream.

All coded data Bits and the end of frame (EOF) condition start with a low field of length Tg.

Afterwards the field is switched on again.

- '0' and '1' can be distinguished by the duration of T[0] and T[1].

- The end of the data transmission is characterised by an end of frame condition.

The following figure shows the data transmission from the Read/Write Device to the transponder.

# HTS IC H32/HTS IC H56/HTS IC H48

| SYMBOL           | DESCRIPTION                         | DURATION                           |

|------------------|-------------------------------------|------------------------------------|

| Tg               | Gap time                            | 410 T <sub>0</sub> <sup>(1)</sup>  |

| T[0]             | Logic 0 Bit length                  | 1822 T <sub>0</sub> <sup>(1)</sup> |

| T[1]             | Logic 1 Bit length                  | 2630 T <sub>0</sub> <sup>(1)</sup> |

| T <sub>EOF</sub> | Duration for end of frame condition | > 36 T <sub>0</sub>                |

Note

1. This application specific values must be within this frame, but have to be optimized for each application depending on rise and decay times of the RWD antenna voltage and the transponder antenna quality factor!

$T_{0...}$ Carrier period time (1/<sub>125 kHz</sub> = 8 µs nominal).

The average Bit rate from the Read/Write Device to the HITAG S Transponder therefore is:

Bit rate =  $\frac{2}{T[0] + T[1]} = 5.2$ kBit/s

Note: The end of each data sequence from the Read/Write Device to the HITAG S Transponder has to be a EOF condition.

# HTS IC H32/HTS IC H56/HTS IC H48

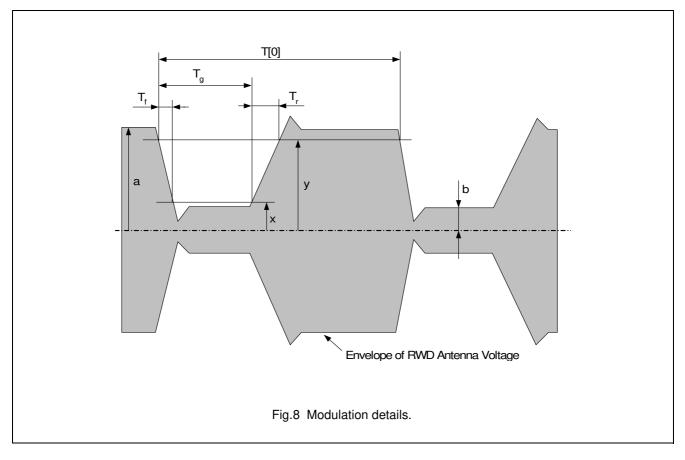

### 7.4.2 MODULATION DETAILS

x = 0.05 a, y = 0.95 a

m = (a - b) / (a + b)....Modulation index

| SYMBOL                        | MIN | МАХ                        |  |  |

|-------------------------------|-----|----------------------------|--|--|

| m                             | 95% | 100%                       |  |  |

| Τ <sub>f</sub>                | 0   | 0.5 T <sub>g</sub>         |  |  |

| T <sub>r</sub> <sup>(1)</sup> | 0   | 1 (T[0] – T <sub>g</sub> ) |  |  |

#### Note

1. This application specific value must be within this range, but has to be optimized depending on transponder coil quality factor and Read performance requirements. For high quality factor transponder coils, a lower rise time  $T_r$  should be implemented (recommended  $T_r = 0.5$  (T[0] –  $T_g$ )) to achieve the maximum possible performance.

The following table shows two examples of modulation timing parameters for typical short- and long range applications.

| SYMBOL         | SHORT RANGE<br>APPLICATION | LONG RANGE<br>APPLICATION |  |  |  |

|----------------|----------------------------|---------------------------|--|--|--|

| Τ <sub>g</sub> | 6 T <sub>0</sub>           | 9 T <sub>0</sub>          |  |  |  |

| T[0]           | 20 T <sub>0</sub>          | 22 T <sub>0</sub>         |  |  |  |

| T[1]           | 28 T <sub>0</sub>          | 28 T <sub>0</sub>         |  |  |  |

| T <sub>f</sub> | 3 T <sub>0</sub>           | 4 T <sub>0</sub>          |  |  |  |

| Tr             | 4 T <sub>0</sub>           | 5 T <sub>0</sub>          |  |  |  |

# HTS IC H32/HTS IC H56/HTS IC H48

### 8 CONFIGURATION

#### 8.1 Configuration Page

Memory Page 1 contains the three configuration Bytes CON 0, CON 1 and CON 2 (see Chapter "Memory Organisation"). Changes on the Configuration Bytes are effective after a power on reset of the HITAG S Transponder.

#### **CON0: Memory Type Information**

|       |       |       | CC    | N0    |       |        |        |

|-------|-------|-------|-------|-------|-------|--------|--------|

| MSB   |       |       |       |       |       |        | LSB    |

| RES 5 | RES 4 | RES 3 | RES 2 | RES 1 | RES 0 | MEMT 1 | MEMT 0 |

The following table describes the **Mem**ory Type Bits MEMT 0 and MEMT 1 of configuration byte CON 0.

| MEMT 1 | MEMT 0 | MEMORY TYPE |

|--------|--------|-------------|

| 0      | 0      | 32 Bit      |

| 0      | 1      | 256 Bit     |

| 1      | 0      | 2048 Bit    |

| 1      | 1      | Reserved    |

Bits RES 0 to RES 5 are reserved for future use. Only Read access to configuration byte CON 0 is possible.

#### CON 1: Mode and Lock Bits

| MSB |      |         |         |        |        |      | LSB |

|-----|------|---------|---------|--------|--------|------|-----|

| AUT | TTFC | TTFDR 1 | TTFDR 0 | TTFM 1 | TTFM 0 | LCON | LKP |

CONI

If the **Aut**hentication Bit AUT = '0' the HITAG S Transponder IC is configured in Plain Mode and can be selected directly by the SELECT (UID) command and the corresponding UID. For Bit AUT = '1' the HITAG S Transponder IC is configured in Authentication Mode and can only be Selected with the SELECT (UID) command and a following secure CHALLENGE sequence (see also Chapters 10 "State Diagram" and 11 "Command Set").

#### Table 3 Authentication Bit AUT

| AUT | HITAG S MODE   |

|-----|----------------|

| 0   | Plain          |

| 1   | Authentication |

### HTS IC H32/HTS IC H56/HTS IC H48

The Transponder Talks First Coding Bit TTFC defines the used coding during transmitting data to the RWD. This effects the TTF State only.

Table 4 Transponder Talks First Coding Bit TTFC

| TTFC | CODING IN TTF STATE |  |  |  |

|------|---------------------|--|--|--|

| 0    | Manchester          |  |  |  |

| 1    | Biphase             |  |  |  |

The Transponder Talks First Data Rate Bits TTFDR 0 and TTFDR 1 select the data rate used during transmission of data to the RWD. This effects the TTF State only.

Table 5

Transponder Talks First Data Rate Bits TTFDR 0 and TTFDR 1

| TTFDR 1 | TTFDR 0 | DATA RATE IN TTF STATE          |  |  |  |

|---------|---------|---------------------------------|--|--|--|

| 0       | 0       | 4 kBit                          |  |  |  |

| 0       | 1       | 8 kBit                          |  |  |  |

| 1       | 0       | 2 kBit                          |  |  |  |

| 1       | 1       | 2 kBit and Pigeon Race Standard |  |  |  |

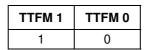

The Transponder Talks First Mode Bits TTFM 0 and TTFM 1 defines the number of Pages continuously transmitted to the RWD. This effects the TTF State only.

| Table 6 | Transponder | Talks First M | Iode Bits | TTFM 0 and TTFM 1 |

|---------|-------------|---------------|-----------|-------------------|

|---------|-------------|---------------|-----------|-------------------|

| TTFM 1 | TTFM 0 | PAGES TRANSMITTED IN TTF STATE |  |  |  |

|--------|--------|--------------------------------|--|--|--|

| 0      | 0      | TTF Mode disabled (= RTF Mode) |  |  |  |

| 0      | 1      | Page 4, Page 5                 |  |  |  |

| 1      | 0      | Page 4, Page 5, Page 6, Page 7 |  |  |  |

| 1      | 1      | Page 4                         |  |  |  |

The Lock Configuration Bit LCON defines the access rights on the configuration Bytes CON 1 and CON 2. This Bit is one time programmable (OTP).

Table 7

Lock Configuration Bit LCON

| LCON | ACCESS RIGHT CON 1 AND CON 2 |

|------|------------------------------|

| 0    | Read / Write                 |

| 1    | CON 1: Read Only.            |

|      | CON 2: OTP                   |

### HTS IC H32/HTS IC H56/HTS IC H48

The Lock Key and Password Bit LKP defines the access rights of the PWDH 0 Byte of Page 1, password low Bytes and key high Bytes of Page 2 and key low Bytes of Page 3 when configured in Authentication Mode. In Plain Mode this Bit can be used to lock the user data of Page 2 and Page 3.

#### Table 8 Lock Key and Password Bit LKP

| LKP | ACCESS RIGHT KEY AND PASSWORD/PAGE 2 AND PAGE 3 |

|-----|-------------------------------------------------|

| 0   | Read / Write                                    |

| 1   | Read Only in Plain Mode                         |

|     | No Access in Authentication Mode                |

Attention: In order to prevent further access to key and password, the following procedure must take place: After setting Bit LKP to '1' the Lock Configuration Bit LCON must be set to '1', because the Bit LKP has no OTP functionality!

#### CON 2: Memory Lock Bits

|       |       |       | CC    | N2    |       |       |       |   |

|-------|-------|-------|-------|-------|-------|-------|-------|---|

| MSB   |       |       |       |       |       |       | LSB   |   |

| LCK 7 | LCK 6 | LCK 5 | LCK 4 | LCK 3 | LCK 2 | LCK 1 | LCK 0 | l |

#### Table 9 Description of Memory Lock Bits

| BIT | SYMBOL | FUNCTION               | ACCESS RIGHTS | COMMENT                                                                                                                                                       |

|-----|--------|------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | LCK 7  | Lock Page 4 and Page 5 | 0Read / Write | OTP if LCON = '1'                                                                                                                                             |

|     |        |                        | 1Read Only    | If Pigeon Race Standard is enabled<br>(TTFDR 0 = TTFDR 1 = '1') 16 Bits (Data 3<br>u. Data 2) of Page 5 remain still<br>Read/Write accessible for LCK 7 = '1' |

| 6   | LCK 6  | Lock Page 6 and Page 7 | 0Read / Write | OTP if LCON = '1'                                                                                                                                             |

|     |        |                        | 1Read Only    |                                                                                                                                                               |

| 5   | LCK 5  | Lock Page 8 – Page 11  | 0Read / Write | OTP if LCON = '1'                                                                                                                                             |

|     |        |                        | 1Read Only    |                                                                                                                                                               |

| 4   | LCK 4  | Lock Page 12 – Page 15 | 0Read / Write | OTP if LCON = '1'                                                                                                                                             |

|     |        |                        | 1Read Only    |                                                                                                                                                               |

| 3   | LCK 3  | Lock Page 16 – Page 23 | 0Read / Write | OTP if LCON = '1'                                                                                                                                             |

|     |        |                        | 1Read Only    |                                                                                                                                                               |

| 2   | LCK 2  | Lock Page 24 – Page 31 | 0Read / Write | OTP if LCON = '1'                                                                                                                                             |

|     |        |                        | 1Read Only    |                                                                                                                                                               |

| 1   | LCK 1  | Lock Page 32 – Page 47 | 0Read / Write | OTP if LCON = '1'                                                                                                                                             |

|     |        |                        | 1Read Only    |                                                                                                                                                               |

| 0   | LCK 0  | Lock Page 48 – Page 63 | 0Read / Write | OTP if LCON = '1'                                                                                                                                             |

|     |        |                        | 1Read Only    |                                                                                                                                                               |

# HTS IC H32/HTS IC H56/HTS IC H48

### 8.2 Delivery Configuration

#### 8.2.1 HITAG S32

This delivery configuration is valid for the following HITAG S 32 types:

- HTS IC H32 01EW/V4

- HTS MO H32 01EV

- HTS FC H32 01EV/DH

|     | MSByte |       |     |     |     | LSB | yte |

|-----|--------|-------|-----|-----|-----|-----|-----|

| MSB | LSI    | B MSB | LSB | MSB | LSB | MSB | LSB |

|     | UID 3  | UID   | 2   | U   | D 1 | UID | 0 0 |

The 32 Bit Unique Identifier (UID) is programmed during the manufacturing process. Access rights: Read Only (RO).

On a Select (UID) command the HITAG S 32 Transponder IC sends back three Reserved Bytes and the Byte CON 0 containing the Memory Type Information.

| MSI | Byte         |     |     |     |     | LSE | Byte |

|-----|--------------|-----|-----|-----|-----|-----|------|

| MSB | LSB          | MSB | LSB | MSB | LSB | MSB | LSB  |

| >   | X            | )   | X   | >   | <   | CC  | N0   |

| MSB | CON 0<br>MSB |     |     |     |     |     |      |

| Х   | Х            | Х   | Х   | Х   | Х   | 0   | 0    |

The content of Bits and Bytes marked with 'X' are not defined at delivery!

# HTS IC H32/HTS IC H56/HTS IC H48

### 8.2.2 HITAG S256

This delivery configuration is valid for the following HITAG S 256 types:

- HTS IC **H56** 01EW/V4

- HTS MO H56 01EV

- HTS FC H56 01EV/DH

|              | MSByte |           |         |         |  |

|--------------|--------|-----------|---------|---------|--|

| Page Address | MSB LS | B MSB LSB | MSB LSB | MSB LSB |  |

| 0x00         | UID 3  | UID 2     | UID 1   | UID 0   |  |

| 0x01         | 0xAA   | 0x00      | 0x00    | CON 0   |  |

| 0x02         | 0x4E   | 0x4F      | 0x54    | 0x48    |  |

| 0x03         | 0x52   | 0x4B      | 0x49    | 0x4D    |  |

| 0x04         | Х      | Х         | Х       | Х       |  |

| 0x05         | Х      | Х         | Х       | Х       |  |

| 0x06         | Х      | Х         | Х       | Х       |  |

| 0x07         | Х      | Х         | Х       | Х       |  |

CON 0

| MSB |   |   |   |   |   |   | LSB |

|-----|---|---|---|---|---|---|-----|

| Х   | Х | Х | Х | Х | Х | 0 | 1   |

The content of Bits and Bytes marked with 'X' are not defined at delivery!

- The 32 Bit Unique Identifier (UID) is programmed during the manufacturing process.

- Modes: Reader Talks First (RTF), Plain

- Access Rights:

- UID: Read Only

- Page 1: Read/Write with exception of byte CON 0 (Read Only)

- Page 2 Page 7: Read/Write

# HTS IC H32/HTS IC H56/HTS IC H48

### 8.2.3 HITAG S2048

This delivery configuration is valid for the following HITAG S 2048 types:

- HTS IC H48 01EW/V4

- HTS MO H48 01EV

- HTS FC H48 01EV/DH

|              | MSByte |      |        |      |        |      | LSByte |     |

|--------------|--------|------|--------|------|--------|------|--------|-----|

| Page Address | MSB    | LSB  | MSB    | LSB  | MSB    | LSB  | MSB    | LSB |

| 0x00         | UID 3  |      | UID 2  |      | UID 1  |      | UID 0  |     |

| 0x01         | 0xAA   |      | 0x00   |      | 0x00   |      | CON 0  |     |

| 0x02         | 0x4E   | 0x4E |        |      | 0x54   |      | 0x48   |     |

| 0x03         | 0x52   | 0x52 |        | 0x4B |        | 0x49 |        |     |

| 0x04         | Х      |      | Х      |      | Х      |      | Х      |     |

| 0x05         | Х      |      | Х      |      | Х      |      | Х      |     |

|              | I<br>I |      | I<br>I |      | I<br>I |      | 1      | I   |

| 0x3E         | Х      |      | Х      |      | Х      |      | Х      |     |

| 0x3F         | Х      |      | Х      |      | Х      |      | Х      |     |

| CON | 0 |

|-----|---|

|-----|---|

| MSB |   |   |   |   |   |   | LSB |

|-----|---|---|---|---|---|---|-----|

| Х   | Х | Х | Х | Х | Х | 1 | 0   |

The content of Bits and Bytes marked with 'X' are not defined at delivery!

- The 32 Bit Unique Identifier (UID) is programmed during the manufacturing process.

- Modes: Reader Talks First (RTF), Plain

- Access Rights:

- UID: Read Only

- Page 1: Read/Write with exception of byte CON 0 (Read Only)

- Page 2 Page 63: Read/Write

## HTS IC H32/HTS IC H56/HTS IC H48

#### 9 PROTOCOL TIMING

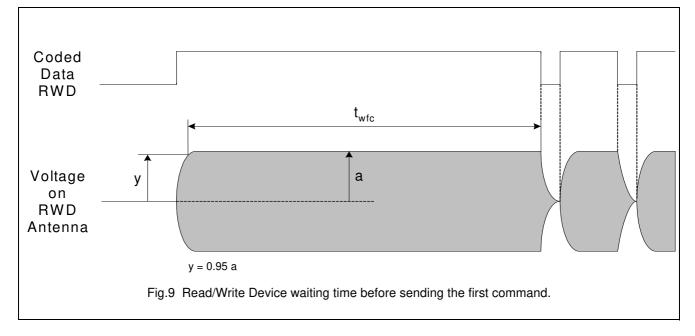

#### 9.1 Read/Write Device waiting time before sending the first command

After switching on the powering field, the Read/Write Device has to wait at least the minimum time  $t_{wfc} = 280 T_0$  before sending the first command. The first command must not be sent later than the maximum time  $t_{wfc} = 5000 T_0$ .

|                  | MIN | ТҮР | MAX  | UNIT           |

|------------------|-----|-----|------|----------------|

| t <sub>wfc</sub> | 280 |     | 5000 | T <sub>0</sub> |

### HTS IC H32/HTS IC H56/HTS IC H48

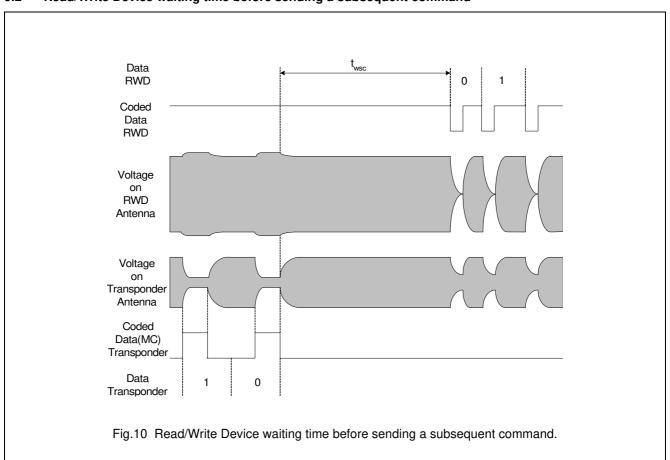

#### 9.2 Read/Write Device waiting time before sending a subsequent command

When the Read/Write Device has received the response from the HITAG S Transponder to a previous command, the RWD has to wait at least the minimum time  $t_{wsc} = 90 T_0$  before sending a subsequent command or Write data after a Write command. The subsequent command or Write data must not be sent later than the maximum time  $t_{wsc} = 5000 T_0$ .

|                  | MIN | ТҮР | MAX  | UNIT           |

|------------------|-----|-----|------|----------------|

| t <sub>wsc</sub> | 90  |     | 5000 | T <sub>0</sub> |

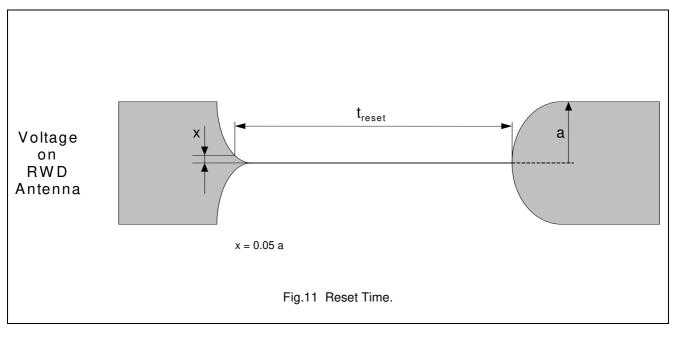

#### Table 12

|                    | MIN | ТҮР | MAX | UNIT |

|--------------------|-----|-----|-----|------|

| t <sub>reset</sub> | 4.8 |     |     | ms   |

26

# HITAG S

### HTS IC H32/HTS IC H56/HTS IC H48

### 9.3 Reset Time

The powering field must be switched off for at least  $t_{reset} = 4.8$  ms to generate a reset of the HITAG S IC and to enter it into Power Off State.

# HTS IC H32/HTS IC H56/HTS IC H48

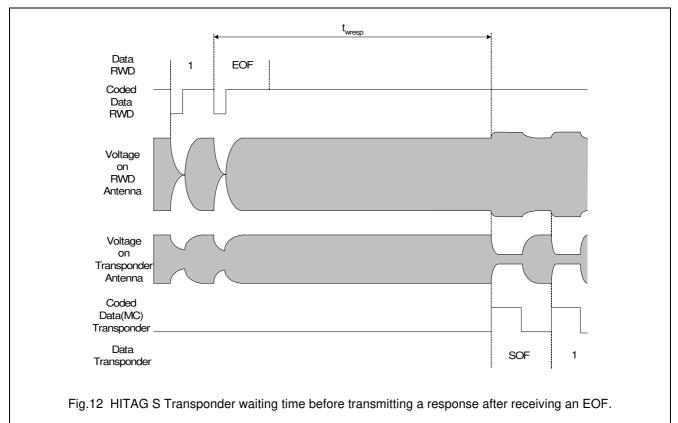

#### 9.4 HITAG S Transponder waiting time before transmitting a response after receiving an EOF

When receiving a End of Frame (EOF) condition from the Read/Write Device, the transponder waits t<sub>wresp</sub> before transmitting data. The values given below are specific to transmission system parameters e.g. coil quality factor, RWD antenna quality factor.

#### Table 13

|                        | MIN | ТҮР | MAX | UNIT           |

|------------------------|-----|-----|-----|----------------|

| t <sub>wresp</sub> (1) | 204 | 208 | 212 | T <sub>0</sub> |

#### Note

1. Valid for coil quality factors  $Q_{coil} < 30$ .

# HTS IC H32/HTS IC H56/HTS IC H48

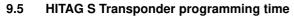

When receiving the EOF of the write data from the Read/Write Device, the transponder waits  $t_{prog}$  before transmitting the SOF and acknowledge to confirm correct programming.

|                   | MIN | ТҮР | MAX | UNIT           |

|-------------------|-----|-----|-----|----------------|

| t <sub>prog</sub> | 716 | 721 | 726 | T <sub>0</sub> |

### HTS IC H32/HTS IC H56/HTS IC H48

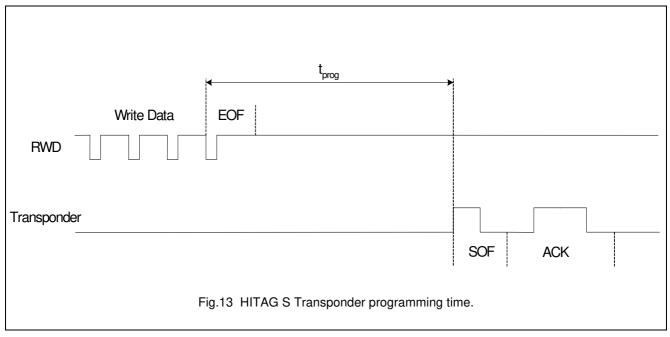

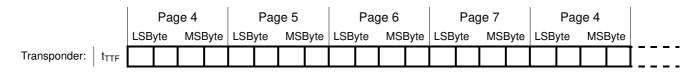

#### 9.6 HITAG S Transponder waiting time before transmitting data in TTF Mode

After switching on the powering field, the HITAG S Transponder waits a time  $t_{TTF}$  before transmitting data if it is configured in TTF Mode.

|                  | MIN | ТҮР | МАХ | UNIT           |

|------------------|-----|-----|-----|----------------|

| t <sub>TTF</sub> | 565 | 585 | 625 | T <sub>0</sub> |

# HTS IC H32/HTS IC H56/HTS IC H48

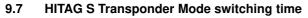

With an UID REQUEST xx command starting with the first bit after  $t_{switch}$ , a HITAG S Transponder configured in TTF Mode can be switched into RTF Mode. The Read/Write Device has to wait at least the minimum time  $t_{switch} = 280 T_0$  and must not wait longer than the maximum time  $t_{switch} = 520 T_0$ . The HITAG S Transponder responds to this command with the UID and changes into Init State.

|                     | MIN | ТҮР | МАХ | UNIT           |

|---------------------|-----|-----|-----|----------------|

| t <sub>switch</sub> | 280 | 400 | 520 | T <sub>0</sub> |

# HTS IC H32/HTS IC H56/HTS IC H48

#### **10 STATE DIAGRAM**

#### 10.1 General Description of States

#### Power Off

The powering magnetic field is switched off or the HITAG S Transponder is out of field.

#### Ready

After start up phase, the HITAG S Transponder is ready to receive the first command.

#### Init

The HITAG S Transponder enters this State after the first UID REQUEST xx command. In this State the Response Protocol Mode (see Chapter11 "Command Set") may be changed by further UID REQUEST xx commands. If there are several HITAG S Transponders in the field of the RWD antenna at the same time, the AC SEQUENCE can be started to determine the UID of every HITAG S Transponder.

#### Authenticate

The HITAG S Transponder enters this State after a valid SELECT (UID) command when configured in Authentication Mode. After an encrypted CHALLENGE Authentication the HITAG S Transponder changes into the Selected State.

#### Selected

The HITAG S Transponder enters this State after a valid SELECT (UID) command when configured in Plain Mode or a SELECT (UID) and CHALLENGE sequence when configured in Authentication Mode. Only one HITAG S Transponder in the field of the RWD antenna can be Selected at the same time. In this State, Read and Write operations are possible. Data Transmission is not encrypted even if configured in Authentication Mode.

#### Quiet

The HITAG S Transponder enters this State after a SELECT\_QUIET command in Init State or a QUIET command in Selected State. In this State, the HITAG S Transponder will not answer to any command. Switching off the powering magnetic field or moving the HITAG S Transponder out of field enters it into the Power Off State.

### Transponder Talks First (TTF)

The HITAG S Transponder enters this State when configured in TTF Mode if no UID REQUEST xx command is received within the Mode switch window. Once entered this State, the HITAG S Transponder continuously transmits data with configurable data coding, data rate and data length.

# HTS IC H32/HTS IC H56/HTS IC H48

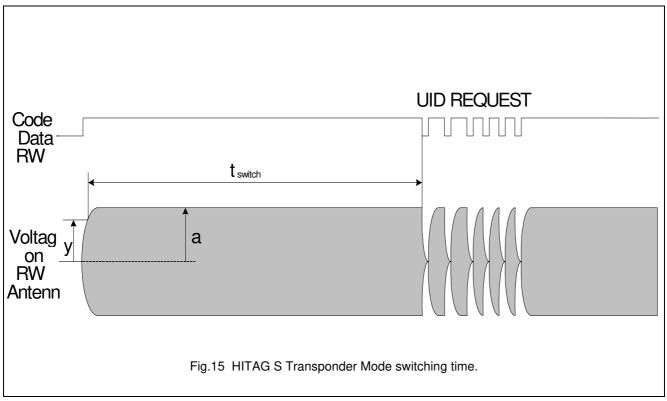

#### 10.2 HITAG S 32

#### Note:

Switching off the powering magnetic field or moving the HITAG S Transponder out of the RWD antenna field, enters the HITAG S Transponder into the Power Off State, independently of its actual State.

### HTS IC H32/HTS IC H56/HTS IC H48

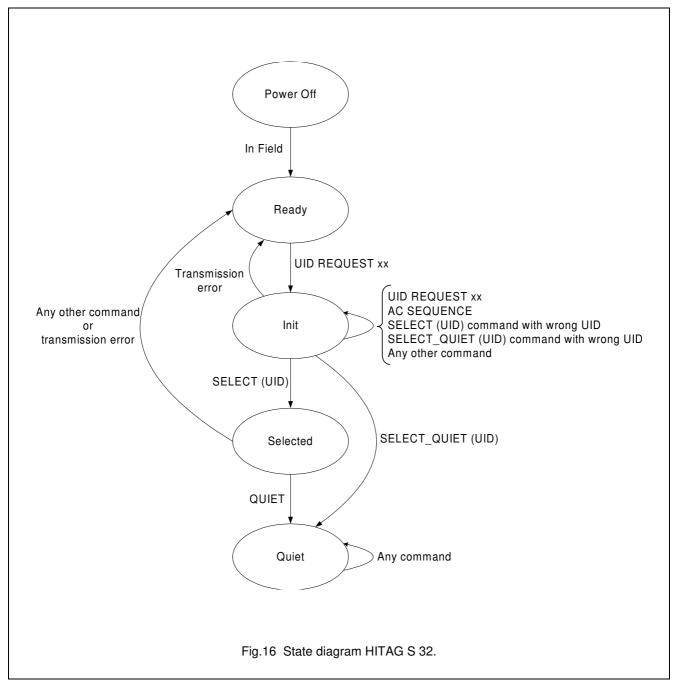

### 10.3 HITAG S 256 and HITAG S 2048

#### Note:

Switching off the powering magnetic field or moving the HITAG S Transponder out of the RWD antenna field, enters the HITAG S Transponder into the Power Off State, independently of its actual State.

# HTS IC H32/HTS IC H56/HTS IC H48

#### 11 COMMAND SET

#### 11.1 General Comments

For HITAG S 32 only the commands described in the corresponding State diagram are valid commands.

#### 11.2 UID REQUEST xx

|      | MSB     | LSB     |     |

|------|---------|---------|-----|

| RWD: | UID REQ | UEST xx | EOF |

| LSByte      |                    |     |       |     |     |             |     |       | MSI | Byte |

|-------------|--------------------|-----|-------|-----|-----|-------------|-----|-------|-----|------|

|             |                    |     | MSB   | LSB | MSB | LSB         | MSB | LSB   | MSB | LSB  |

| Transponder | t <sub>wresp</sub> | SOF | UID 0 |     |     | UID 1       | l   | JID 2 | UII | D 3  |

|             |                    | N = | 1     | 8   | 9.  | <b>k</b> 16 | 17  | 24    | 25  | 32   |

N...physical Bit position during air transmission. N=25 is the bit with the highest valence 2<sup>31</sup>.

k...Any collision position (see command AC SEQUENCE)

After the RWD transmits this command, all HITAG S Transponders located in the field of the RWD antenna respond with a start of frame pattern followed by the corresponding 32 Bit UID. The complete response of the HITAG S Transponder is transmitted in Anticollision Coding (AC, see Section 7.3.1 "Coding").

#### Table 17 Coding

|                  | MSB LSB | RESPONSE PROTOCOL MODE |

|------------------|---------|------------------------|

| UID REQUEST Std  | 00110   | Standard               |

| UID REQUEST Adv  | 1100x   | Advanced               |

| UID REQUEST FAdv | 11010   | Fast Advanced          |

#### Note

1. x... can be '0' or '1'

The Response Protocol Mode defined by the corresponding UID Request command determines the coding, data rate and the SOF pattern of the HITAG S Transponder response.

#### Table 18

| RESPONSE PROTOCOL MODE | SOF   | CODING | DATA RATE |

|------------------------|-------|--------|-----------|

| Standard               | '1'   | AC     | 2 kBit/s  |

| Advanced               | '111' | AC     | 2 kBit/s  |

| Fast Advanced          | '111' | AC     | 4 kBit/s  |

A HITAG S Transponder in Ready State changes into Init State after receiving a correct UID REQUEST xx command.

A HITAG S Transponder being already in Init State remains in Init State after receiving a further correct UID REQUEST xx command.

Always the latest UID REQUEST xx command defines the Response Protocol Mode for the following commands.

### HTS IC H32/HTS IC H56/HTS IC H48

### 11.3 AC SEQUENCE

If more than one HITAG S Transponder is in the field of the antenna a special designed RWD detects the first collision at the **Bit position N = k** of the UID response. As a result the RWD starts an Anticollision Sequence (AC SEQUENCE).

This command consists of a 5 Bit number (k4 to k0) describing the physical Bit position k where the collision occurred followed by (k - 1) Bits of the detected UID and a Bit (one or zero) at the collision position. An 8 Bit CRC (cyclic redundancy check) of this sequence is also sent to the transponders.

|         | MSB   |    |    |    | LSB | 1k            | MSB LSB |     |                    |     |                      |

|---------|-------|----|----|----|-----|---------------|---------|-----|--------------------|-----|----------------------|

| RWD:    | k4    | k3 | k2 | k1 | k0  | k Bits of UID | CRC 8   | EOF |                    |     |                      |

|         |       |    |    |    |     |               |         |     |                    |     |                      |

| Transpo | onder |    |    |    |     |               |         |     | t <sub>wresp</sub> | SOF | (32 – k) Bits of UID |

|         |       |    |    |    |     |               |         |     |                    | N = | k+132                |

After transmitting this command, all HITAG S Transponders which first k Bits of the own UID match with the k received UID Bits, answer with the SOF and the rest of their own UID.

If a collision occurs again the described cycle has to be repeated until one valid UID of the transponders in the field is determined.

The complete response of the HITAG S Transponder is transmitted in Anticollision Coding (AC).

#### Table 19

| RESPONSE PROTOCOL MODE | SOF   | CODING | DATA RATE |

|------------------------|-------|--------|-----------|

| Standard               | '1'   | AC     | 2 kBit/s  |

| Advanced               | '111' | AC     | 2 kBit/s  |

| Fast Advanced          | '111' | AC     | 4 kBit/s  |

During the AC SEQUENCE commands the HITAG S Transponder stays in Init State. **Even those HITAG S Transponders where the k received Bits of the UID do not match remain in Init State.**

# HTS IC H32/HTS IC H56/HTS IC H48

### 11.4 SELECT (UID)

The SELECT (UID) command consists of 5 Zero-Bits followed by the determined 32 Bit UID and an 8 Bit Cyclic Redundancy Check (CRC). The selected transponder then responds with a start of frame pattern (SOF) followed by the content of the Configuration Page and depending on the Response Protocol Mode with an 8 Bit CRC.

| LSByte |       |     |     |     | MSByte |     |     |     |     |     |     |     |  |

|--------|-------|-----|-----|-----|--------|-----|-----|-----|-----|-----|-----|-----|--|

|        |       | MSB | LSB | MSB | LSB    | MSB | LSB | MSB | LSB | MSB | LSB |     |  |

| RWD:   | 00000 | UID | 0 0 | UID | D 1    | UID | 2   | UID | 03  | CR  | C 8 | EOF |  |

|        |     | MSB | LS  |

|--------|-----|-----|-----|

| twresp | SOF | CO  | N 0 |

Transponder

|                    |     | MSB | LSB | MSB | LSB | MSB | LSB | MSB  | LSB   | MSB | LSB |

|--------------------|-----|-----|-----|-----|-----|-----|-----|------|-------|-----|-----|

| t <sub>wresp</sub> | SOF | CO  | N 0 | CO  | N 1 | CO  | N 2 | Rese | erved | CR  | C 8 |

MSByte

LSByte

The complete response of the HITAG S Transponder is transmitted in Manchester Coding (MC).

In Plain Mode the MSByte of Page 1 is a Reserved Byte, in Authentication Mode this Byte contains the password high Byte PWDH 0. At the response on a SELECT (UID) command of a HITAG S Transponder configured in Authentication Mode (Bit AUT = 1, keys and password locked), this PWDH 0 Byte is dissolved by '1' Bits.

#### Table 20

| RESPONSE PROTOCOL MODE | SOF      | CRC8 | CODING | DATA RATE |

|------------------------|----------|------|--------|-----------|

| Standard               | '1'      | no   | MC     | 4 kBit/s  |

| Advanced               | '111111' | yes  | MC     | 4 kBit/s  |

| Fast Advanced          | '111111' | yes  | MC     | 8 kBit/s  |

In Plain Mode (Bit AUT = 0) the HITAG S Transponder changes into Selected State after receiving a correct SELECT (UID) command.

In Authentication Mode (Bit AUT = 1) the HITAG S Transponder changes into Authenticate State after receiving a correct SELECT (UID) command and waits for the CHALLENGE command.

# HTS IC H32/HTS IC H56/HTS IC H48

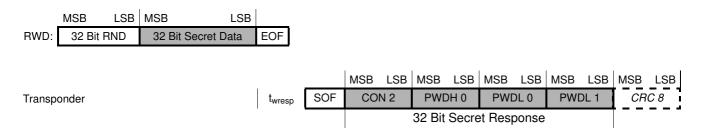

### 11.5 CHALLENGE

By means of the response of the SELECT (UID) command the RWD detects that the HITAG S Transponder is configured in Authentication Mode (Bit AUT = 1) and starts the encrypted Challenge sequence.

The Read/Write Device sends a 32 Bit Random Number (RND) and a 32 Bit secret data stream to the transponder. In order to perform the secret data stream, a security co-processor is required on the read/write Device. For more information please contact us at - info.bli@philips.com.

If the received secret data stream corresponds with the secret data stream calculated by the HITAG S Transponder, a 32 Bit Secret Response (secret data stream encrypting the configuration byte CON 2, password high byte PWDH 0 and password low Bytes PWDL 0 and PWDL 1) is transmitted after the SOF.

The response of the HITAG S Transponder is transmitted in Manchester Coding (MC).

#### Table 21

| RESPONSE PROTOCOL MODE | SOF      | CRC8 | CODING | DATA RATE |

|------------------------|----------|------|--------|-----------|

| Standard               | '1'      | no   | MC     | 4 kBit/s  |

| Advanced               | '111111' | yes  | MC     | 4 kBit/s  |

| Fast Advanced          | '111111' | yes  | MC     | 8 kBit/s  |

A HITAG S Transponder configured in Authentication Mode changes from Authenticate State into Selected State only after a correct CHALLENGE Sequence.

Note: Even with AUT=1 further data transmission for read and write commands is done in plain mode.

twresp

ACK

01

SOF

### HITAG S

# HTS IC H32/HTS IC H56/HTS IC H48

### 11.6 SELECT\_QUIET (UID)

With this command a HITAG S Transponder in Init State can be directly entered into the Quiet State.

| LSByte |       |     |     |     |     | MSE | Byte |     |     |   |     |     |     |  |

|--------|-------|-----|-----|-----|-----|-----|------|-----|-----|---|-----|-----|-----|--|

|        |       | MSB | LSB | MSB | LSB | MSB | LSB  | MSB | LSB |   | MSB | LSB |     |  |

| RWD:   | 00000 | UIE | 0 0 | UIE | D 1 | UID | 02   | UIE | 03  | 0 | CRO | C 8 | EOF |  |

Transponder

The 'start of frame' (SOF) pattern and the acknowledge (ACK) is transmitted in Manchester Coding.

#### Table 22

| RESPONSE PROTOCOL MODE | SOF      | CODING | DATA RATE |

|------------------------|----------|--------|-----------|

| Standard               | '1'      | MC     | 4 kBit/s  |

| Advanced               | '111111' | MC     | 4 kBit/s  |

| Fast Advanced          | '111111' | MC     | 8 kBit/s  |

A HITAG S Transponder, once entered the Quiet State can only be enabled by switching off the powering magnetic field for at least a time  $t_{reset}$  or the HITAG S Transponder must be moved out of the antenna field (Power Off State).

#### 11.7 READ PAGE

After a HITAG S Transponder was selected by the corresponding SELECT (UID) command (or SELECT (UID) and CHALLENGE for Authentication Mode) a read operation of data stored on the EEPROM can be performed. After transmitting the READ PAGE command, the Page address PADR (8 Bits) and the 8 Bit Cyclic Redundancy Check CRC 8, the HITAG S Transponder responds with the SOF and 32 Bits data of the corresponding Page.

|      |      | MSB | LSB | MSB | LSB |     |  |

|------|------|-----|-----|-----|-----|-----|--|

| RWD: | 1100 | PAI | DR  | CR  | C 8 | EOF |  |

|             | LSByte             |     |     |     |     | MSByte |     |     |     |     |     |     |  |

|-------------|--------------------|-----|-----|-----|-----|--------|-----|-----|-----|-----|-----|-----|--|

|             |                    |     | MSB | LSB | MSB | LSB    | MSB | LSB | MSB | LSB | MSB | LSB |  |

| Transponder | t <sub>wresp</sub> | SOF | Dat | a 0 | Dat | a 1    | Dat | a 2 | Dat | ta3 | CR  | C 8 |  |

The highest Page address (PADR) is 0x 3F, therefore the two highest Bits must be '0'.

| RESPONSE PROTOCOL MODE | SOF      | CRC8 | CODING | DATA RATE |

|------------------------|----------|------|--------|-----------|

| Standard               | '1'      | no   | MC     | 4 kBit/s  |

| Advanced               | '111111' | yes  | MC     | 4 kBit/s  |

| Fast Advanced          | '111111' | yes  | MC     | 8 kBit/s  |

# HTS IC H32/HTS IC H56/HTS IC H48

### 11.8 READ BLOCK

After transmitting the READ BLOCK command, the Page address PADR (8 Bits) within a block and the 8 Bit Cyclic Redundancy Check CRC 8, the HITAG S Transponder responds with the SOF and 32 up to 128 Bits of data beginning with the addressed Page within a Block to the last Page of the corresponding Block.

|      |      | MSB | LSB | MSB | LSB |     | _ |

|------|------|-----|-----|-----|-----|-----|---|

| RWD: | 1101 | PAI | DR  | CR  | C 8 | EOF |   |

|             |                    |     | LSB | Byte |     |     |     |     | MSE | Byte | LSE | Byte | MSE     | Byte |     |     |

|-------------|--------------------|-----|-----|------|-----|-----|-----|-----|-----|------|-----|------|---------|------|-----|-----|

|             |                    |     | MSB | LSB  | MSB | LSB | MSB | LSB | MSB | LSB  | MSB | LSB  | <br>MSB | LSB  | MSB | LSB |

| Transponder | t <sub>wresp</sub> | SOF | Dat | a 0  | Dat | a 1 | Dat | a 2 | Dat | ta3  | Dat | a 0  | Dat     | a 3  | CR  | C 8 |

| RESPONSE PROTOCOL MODE | SOF        | CRC8 | CODING | DATA RATE |

|------------------------|------------|------|--------|-----------|

| Standard               | <b>'1'</b> | no   | MC     | 4 kBit/s  |

| Advanced               | '111111'   | yes  | MC     | 4 kBit/s  |

| Fast Advanced          | '111111'   | yes  | MC     | 8 kBit/s  |

# HTS IC H32/HTS IC H56/HTS IC H48

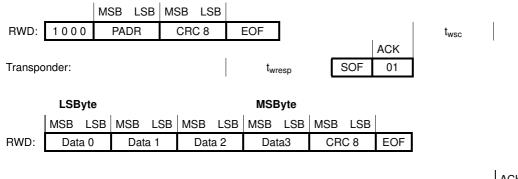

#### 11.9 WRITE PAGE

After a HITAG S Transponder was selected by the corresponding SELECT (UID) command (or SELECT (UID) and CHALLENGE for Authentication Mode) a write operation of data onto the memory can be carried out. Least significant Byte is always transmitted first. E.g. in order to change the configuration page the byte Con0 would have to be transmitted first.

After transmitting the WRITE PAGE command, the Page address PADR (8 Bits) and the 8 Bit Cyclic Redundancy Check (CRC 8), the HITAG S Transponder responds with the SOF and an acknowledge (ACK) to confirm the reception of a correct WRITE PAGE command. After the waiting time  $t_{wsc}$  the RWD transmits the write data with CRC 8. After the programming time  $t_{prog}$  the HITAG S Transponder responds with a SOF and an acknowledge to confirm correct programming.

Transponder:

ACK t<sub>wresp</sub> SOF 01

| RESPONSE PROTOCOL MODE | SOF      | CODING | DATA RATE |

|------------------------|----------|--------|-----------|

| Standard               | '1'      | MC     | 4 kBit/s  |

| Advanced               | '111111' | MC     | 4 kBit/s  |

| Fast Advanced          | '111111' | MC     | 8 kBit/s  |

# HTS IC H32/HTS IC H56/HTS IC H48

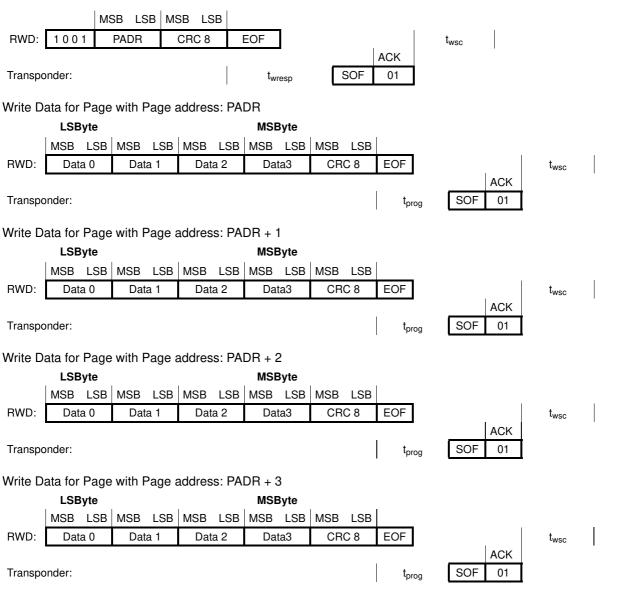

#### 11.10 WRITE BLOCK

After transmitting the WRITE BLOCK command, the Page address PADR (8 Bits) within a Block and the 8 Bit Cyclic Redundancy Check (CRC 8), the HITAG S Transponder responds with the SOF and an acknowledge (ACK) to confirm the reception of a correct WRITE BLOCK command. After the waiting time  $t_{wsc}$  the RWD transmits the write data with CRC 8 Page by Page (1 to 4 Pages depending on the Page address PADR within the corresponding block). After the programming time  $t_{prog}$  the HITAG S Transponder responds with a SOF and an acknowledge to confirm correct programming of each Page.

| RESPONSE PROTOCOL MODE | SOF      | CODING | DATA RATE |

|------------------------|----------|--------|-----------|

| Standard               | '1'      | MC     | 4 kBit/s  |

| Advanced               | '111111' | MC     | 4 kBit/s  |

| Fast Advanced          | '111111' | MC     | 8 kBit/s  |

# HTS IC H32/HTS IC H56/HTS IC H48

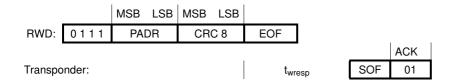

### 11.11 QUIET

With this command a Selected HITAG S Transponder can be entered into the Quiet State.

A valid Page address PADR (8 Bits) and Cyclic Redundancy Check (CRC 8) must be sent for command structure reasons only.

After the response wait time t<sub>wresp</sub> the HITAG S Transponder responds with a SOF and an acknowledge to confirm entering the Quiet State.

#### Table 27

| RESPONSE PROTOCOL MODE | SOF      | CODING | DATA RATE |

|------------------------|----------|--------|-----------|

| Standard               | '1'      | MC     | 4 kBit/s  |

| Advanced               | '111111' | MC     | 4 kBit/s  |

| Fast Advanced          | '111111' | MC     | 8 kBit/s  |

A HITAG S Transponder, once entered the Quiet State can only be reactivated after switching off the powering magnetic field for at least a time t<sub>reset</sub> or the HITAG S Transponder must be moved out of the antenna field (Power Off State).

# HTS IC H32/HTS IC H56/HTS IC H48

#### 12 TRANSPONDER TALKS FIRST (TTF) MODE

This special mode of the HITAG S Transponder enables data transmission to a Read/Write Device without sending any command. The TTF Mode can be enabled/disabled and configured by setting the corresponding Bits of the Configuration byte CON 1 (see Chapter 8 "Configuration").

A HITAG S Transponder configured in TTF Mode can be switched temporarily into Reader Talks First (RTF) Mode by sending a UID REQUEST xx command within a defined window after turning on the powering field. The HITAG S Transponder will leave this temporarily RTF Mode after switching off the powering field or moving it out of the RWD antenna field.

If the HITAG S Transponder is configured in TTF Mode and no Mode switch command is sent by the RWD within the defined switch window it enters the TTF State. Depending on the configuration, the HITAG S Transponder transmits the data with different coding, data rate and data length. It is recommended to use some of the data bits as a well defined start sequence.

#### 12.1 32 Bit TTF Mode

#### **Configuration:**

| TTFM 1 | TTFM 0 |  |  |  |

|--------|--------|--|--|--|

| 1      | 1      |  |  |  |

In this Mode, the HITAG S Transponder continuously transmits the data content of Page 4.

|                               | Page 4  |         |               |         | Page 4  |         |         |         |         |  |

|-------------------------------|---------|---------|---------------|---------|---------|---------|---------|---------|---------|--|

|                               | LSByte  |         | LSByte MSByte |         | LSByte  |         |         |         | LSByte  |  |

|                               | MSB LSB | MSB LSB | MSB LSB       | MSB LSB | MSB LSB | MSB LSB | MSB LSB | MSB LSB | MSB LSB |  |

| Transponder: t <sub>TTF</sub> | Data 0  | Data 1  | Data 2        | Data3   | Data 0  | Data 1  | Data 2  | Data3   | Data 0  |  |

The data rate and the data coding can be chosen independently by configuration Bits TTFC, TTFDR 0 and TTFDR 1.

#### 12.2 64 Bit TTF Mode

Configuration:

| TTFM 1 | TTFM 0 |  |  |  |

|--------|--------|--|--|--|

| 0      | 1      |  |  |  |

In this Mode, the HITAG S Transponder continuously transmits the data content of Page 4 and Page 5.

|                               | Page 4  |         |         |         | Page 5  |         |         |         | Page 4  | 4 |

|-------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---|

|                               | LSByte  |         | MSByte  | LSByte  |         |         |         | LSByte  | е       |   |

|                               | MSB LSB |   |

| Transponder: t <sub>TTF</sub> | Data 0  | Data 1  | Data 2  | Data3   | Data 0  | Data 1  | Data 2  | Data3   | Data 0  |   |

The data rate and the data coding can be chosen independently by configuration Bits TTFC, TTFDR 0 and TTFDR 1. Note: This Mode may be used for Pigeon race standards.

# HTS IC H32/HTS IC H56/HTS IC H48

### 12.3 128 Bit TTF Mode

### **Configuration:**

In this Mode, the HITAG S Transponder continuously transmits the data content of Page 4, Page 5, Page 6 and Page 7.

The data rate and the data coding can be chosen independently by configuration Bits TTFC, TTFDR 0 and TTFDR 1.

Note: This Mode may be used for ISO 11784/85 Animal ID standard and German Waste Management standard (BDE) respectively.

# HTS IC H32/HTS IC H56/HTS IC H48

#### 13 DATA INTEGRITY / CALCULATION OF CRC

The following explanations show the features of the HITAG S protocol to protect read and write access to transponders from undetected errors.

#### 13.1 Data Transmission: Read/Write Device to HITAG S Transponder