# AM571x Industrial Development Kit (IDK) Evaluation Module (EVM) Hardware

# **User's Guide**

Literature Number: SPRUI97D May 2017—Revised September 2019

# **Contents**

| Prefa | ace      |                                  | . 5 |

|-------|----------|----------------------------------|-----|

| 1     | Introdu  | ction                            | . 6 |

|       | 1.1      | Description                      | . 6 |

|       | 1.2      | System View                      | . 7 |

| 2     | Functio  | nal Description                  | 11  |

|       | 2.1      | Processor                        | 12  |

|       | 2.2      | Clocks                           | 12  |

|       | 2.3      | Reset Signals                    | 12  |

| 3     | Power 9  | Supplies                         | 13  |

|       | 3.1      | Power Source                     | 13  |

|       | 3.2      | TPS6590377 PMIC                  | 13  |

|       | 3.3      | AVS Control                      | 13  |

|       | 3.4      | Other Power Supplies             | 14  |

| 4     | Configu  | uration/Setup                    | 15  |

|       | 4.1      | Boot Configuration               | 15  |

|       | 4.2      | I2C Address Assignments          | 15  |

|       | 4.3      | SEEPROM Header                   | 16  |

|       | 4.4      | JTAG Emulation                   | 16  |

| 5     | Memori   | es Supported                     | 17  |

|       | 5.1      | DDR3L SDRAM                      | 17  |

|       | 5.2      | SPI NOR Flash                    | 17  |

|       | 5.3      | Board Identity Memory            | 17  |

|       | 5.4      | SD/MMC                           | 17  |

|       | 5.5      | eMMC NAND Flash                  | 17  |

| 6     | Etherne  | et Ports                         | 18  |

|       | 6.1      | 100Mb Ethernet Ports on PRU-ICSS | 18  |

|       | 6.2      | Gigabit (1000Mb) Ethernet Ports  | 18  |

| 7     | USB Po   | orts                             | 19  |

|       | 7.1      | Processor USB Port 1             | 19  |

|       | 7.2      | Processor USB Port 2             | 19  |

|       | 7.3      | FTDI USB Port                    | 19  |

| 8     | PCle     |                                  | 20  |

| 9     | Video II | nput and Output                  | 20  |

|       | 9.1      | Camera                           | 20  |

|       | 9.2      | HDMI                             | 20  |

|       | 9.3      | LCD                              | 20  |

| 10    | Industri | ial Interfaces                   | 21  |

|       | 10.1     | Profibus                         | 21  |

|       | 10.2     | DCAN                             | 21  |

|       | 10.3     | RS-485                           | 21  |

| 11    | User In  | terfaces                         | 21  |

2

#### www.ti.com

|       | 11.1       | Tri-color LEDs                                                                                                      | 21 |

|-------|------------|---------------------------------------------------------------------------------------------------------------------|----|

|       | 11.2       | Industrial Inputs                                                                                                   | 21 |

|       | 11.3       | Industrial Outputs / LEDs                                                                                           | 21 |

| 12    | Pin Use    | Description                                                                                                         | 22 |

|       | 12.1       | Functional Interface Mapping                                                                                        | 22 |

|       | 12.2       | GPIO Pin Mapping                                                                                                    | 22 |

| 13    | Board C    | Connectors                                                                                                          | 24 |

| 14    | EVM Im     | portant Notice                                                                                                      | 37 |

| Appe  | endix A K  | Known Deficiencies in AM571x IDK EVM                                                                                | 38 |

| • •   | A.1        | Power solution not sufficient for full PCIe plug-in card compliance                                                 |    |

|       | A.2        | Early versions of the AM571x IDK EVM not installed with SOC devices rated for the full industrial temperature range |    |

|       | A.3        | AM571x IDK EVM does not support eMMC HS200 mode                                                                     |    |

|       | A.4        | PCIe PERSTn line not in proper state at start-up                                                                    |    |

|       | A.5        | EDIO connectors J4 and J7 should support real-time debugging for both PRU1 and PRU2                                 |    |

|       | A.6        | HDQ implementation not correct                                                                                      |    |

|       | A.7        | Removing the power plug and inserting it again while the power supply is energized may cause damage                 |    |

|       | A.8        | Software shutdown of PMIC not operational                                                                           |    |

|       | A.9        | CCS System Reset fails                                                                                              |    |

|       | A.10       | AM571x IDK EVM design contains 2 clamp circuits that may not be necessary                                           |    |

|       | A.11       | Crystal connected to osc0 needs to have 50ppm or better long term accuracy                                          |    |

|       | A.12       | Software must program the CDCE913 for 0pf load capacitance                                                          |    |

|       | A.13       | Protection diode D2 should be rated for 5V                                                                          |    |

|       | A.14       | PHY address LSB for U9 and U15 can be latched incorrectly                                                           | 40 |

|       | A.15       | 3.3-V clamp circuit needs more margin                                                                               | 40 |

|       | A.16       | Current PMIC does not provide the mandated power down sequence                                                      | 40 |

|       | A.17       | Power supply droop may cause board reset                                                                            | 40 |

|       | A.18       | AM5718 pin N21 must be connected to 1.8 V, as it is VDDS18V_DDR1 and not N/C                                        | 40 |

|       | A.19       | VOUT1 is used at 3.3 V, which violates erratum i920                                                                 | 40 |

|       | A.20       | PMIC OSC16MCAP pin mistakenly grounded                                                                              | 40 |

| Revis | sion Histo | ory                                                                                                                 | 41 |

|       |            |                                                                                                                     |    |

# **List of Figures**

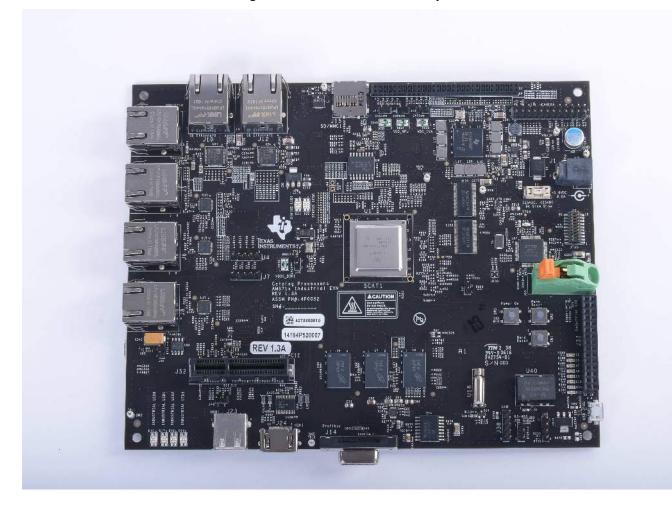

| 1  | AM571x IDK EVM - Top View                                    | 7  |

|----|--------------------------------------------------------------|----|

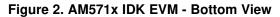

| 2  | AM571x IDK EVM - Bottom View                                 | 8  |

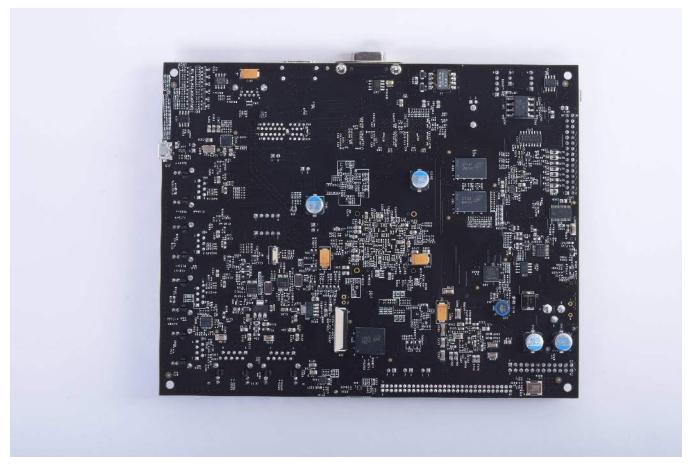

| 3  | AM571x IDK EVM with Camera Board Installed                   | 9  |

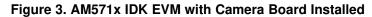

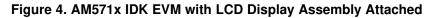

| 4  | AM571x IDK EVM with LCD Display Assembly Attached            | 10 |

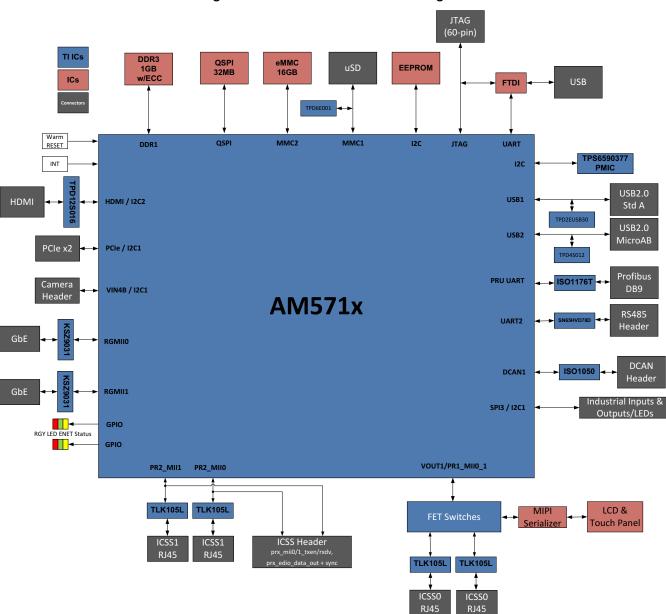

| 5  | AM571x IDK EVM Block Diagram                                 | 11 |

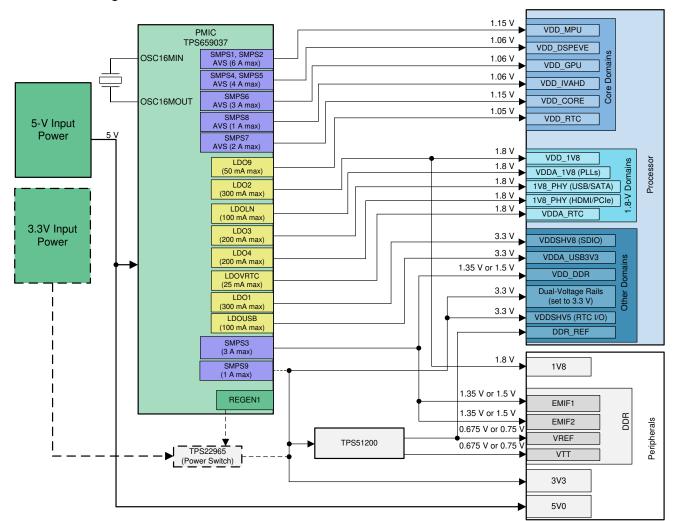

| 6  | Connections from the TPS6590377 PMIC to the AM571x Processor | 14 |

|    | List of Tables                                               |    |

| 1  | I2C1/IND_I2C                                                 | 15 |

| 2  | I2C2/AM571X_HDMI_DDC                                         | 15 |

| 3  | SEEPROM Header                                               | 16 |

| 4  | PRU-ICSS Ethernet Ports                                      | 18 |

| 5  | GPIO Pin Mapping                                             | 23 |

| 6  | Expansion Connector - J21                                    | 24 |

| 7  | I/O Expansion Header Connector - J37                         | 26 |

| 8  | MicroSD Connector - J15                                      | 27 |

| 9  | Power Jack Connector - J1                                    | 27 |

| 10 | Power Terminal Block Connector - J2                          | 27 |

| 11 | PRU1ETH0 RJ45 Connector - J3                                 | 28 |

| 12 | PRU1ETH1 RJ45 Connector - J5                                 | 28 |

| 13 | PRU2ETH0 RJ45 Connector - J6                                 | 29 |

| 14 | PRU2ETH1 RJ45 Connector - J8                                 | 29 |

| 15 | PRU2ETH0 Test Header Connector - J7                          | 30 |

| 16 | PRU2ETH1 Test Header Connector - J4                          | 30 |

| 17 | Camera Connector - J9                                        | 30 |

| 18 | GigE RJ45 Connector - J10                                    | 31 |

| 19 | GigE RJ45 Connector - J12                                    | 31 |

| 20 | LCD Module FFC Connector - J16                               | 32 |

| 21 | Touchscreen Controller FFC Connector - J17                   | 32 |

| 22 | HDMI Standard A-type Connector - J24                         | 33 |

| 23 | CTI-20 JTAG Connector - J18                                  | 33 |

| 24 | JTAG USB Micro-AB Connector - J19                            | 34 |

| 25 | USB Port 1 USB2.1 Standard A-type Connector - J23            | 34 |

| 26 | USB Port 2 USB2.1 Micro-AB Connector - J45                   | 34 |

| 27 | CAN Header Connector - J38                                   | 35 |

| 28 | Profibus DB9F Connector - J14                                | 35 |

| 29 | RS-485 Header Connector - J39                                | 35 |

| 30 | PCIe Connector – J52                                         | 36 |

### Read This First

#### **About This Manual**

This document describes the hardware architecture of the AM571x Industrial Development Kit (IDK) Evaluation Module (EVM) (Part# TMDXIDK571x) that supports the Texas Instruments Sitara<sup>™</sup> ARM® Cortex®-A15 AM571x processor family.

#### Glossary

*TI Glossary* — This glossary lists and explains terms, acronyms, and definitions.

#### **Related Documentation From Texas Instruments**

For product information, visit the Texas Instruments website at http://www.ti.com.

SPRS957— AM571x Sitara Processors Silicon Revision 2.0 Data Manual

SPRZ436— AM571x Sitara Processors Silicon Errata. Describes the known exceptions to the functional specifications for the device.

**SPRUHZ7**— AM571x Sitara Processors Silicon Revision 2.0, 1.0 Technical Reference Manual. Details the integration, the environment, the functional description, and the programming models for each peripheral and subsystem in the device.

#### **Support Resources**

TI E2E™ support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### **Trademarks**

Sitara, E2E, Code Composer Studio, SmartReflex are trademarks of Texas Instruments. ARM, Cortex are registered trademarks of ARM Limited. Windows is a registered trademark of Microsoft Corporation.

# AM571x Industrial Development Kit (IDK) Evaluation Module (EVM) Hardware

#### 1 Introduction

This document describes the hardware architecture of the AM571x Industrial Development Kit (IDK) Evaluation Module (EVM) (Part# TMDXIDK571x) that supports the Texas Instruments Sitara<sup>™</sup> ARM® Cortex®-A15 AM571x processor family.

#### 1.1 Description

The AM571x IDK is a standalone test, development, and evaluation module that enables developers to write software and develop hardware for industrial control and industrial communications applications. It has been equipped with a TI AM5718 processor and a defined set of features to allow you to experience industrial communication solutions using various serial or Ethernet based interfaces. Using standard interfaces, the AM571x IDK may interface to other processors or systems and act as a communication gateway or controller. In addition, it can directly operate as a standard remote I/O system or a sensor connected to an industrial communication network.

The AM571x IDK contains embedded emulation circuitry to quickly enable developers to begin using this IDK. The embedded emulation logic allows emulation and debug using standard development tools such as the Texas Instruments Code Composer Studio™ integrated development environment (IDE) by simply connecting a USB cable to a Windows®-based computer.

The standard (4-port Ethernet) configuration for the AM571x IDK EVM provides the following functionality:

- Two Gigabit (1000Mb) metallic ports connected via PHY/RGMII to the on-chip Ethernet switch

- Two 100Mb metallic ports connected via PHY/MII to the PRU-ICSS subsystems

- LCD panel output from Display Parallel Interface (DPI) Video Output 1

Reconfiguration through header shunt removal provides an alternate 6-port Ethernet configuration:

- Two Gigabit (1000Mb) metallic ports connected via PHY/RGMII to the on-chip Ethernet switch

- Four 100Mb metallic ports connected via PHY/MII to the PRU-ICSS subsystems

Software support for the AM571x IDK EVM is provided within the Processor Software Development Kit (SDK) package. This includes both Linux and RTOS support.

www.ti.com Introduction

#### 1.2 System View

The system view of the AM571x IDK EVM consists of the main board and the camera board. There is also an optional LCD panel and touch screen assembly that can be attached to the AM571x IDK EVM.

The top and the bottom views of the AM571x IDK EVM are provided in Figure 1 and Figure 2, respectively.

The top view of the AM571x IDK EVM with the camera board installed is provided in Figure 3. The side view of the AM571x IDK EVM with the optional LCD display assembly attached is provided in Figure 4.

Figure 1. AM571x IDK EVM - Top View

*Introduction* www.ti.com

www.ti.com Introduction

Introduction www.ti.com

www.ti.com Functional Description

#### 2 Functional Description

The AM571x IDK EVM is implemented on a single board with interface circuitry, memory ICs, and connectors around the AM5718 processor. The board also contains power conversion circuitry to efficiently create the needed power supply voltages from a single +5V input. As stated previously, this EVM ships with a separate camera module that plugs in to the main board. An optional LCD panel and touch screen assembly can be purchased separately and mounted on to the main board.

Figure 5 shows the functional block diagram of the AM571x IDK EVM.

Figure 5. AM571x IDK EVM Block Diagram

Functional Description www.ti.com

#### 2.1 Processor

The AM5718 processor is the central processing unit for this IDK EVM. The interface circuitry, memory ICs, and connectors implemented on the board around the AM5718 processor provide development support for the many industrial communication interfaces available on this platform. See the AM571x Sitara Processors Silicon Revision 2.0 Data Manual (SPRS957) and the AM571x Sitara Processors Technical Reference Manual (SPRUHZ7) for details about the processor.

The AM571x IDK EVM contains system configuration for the boot mode control inputs SYSBOOT[15..0]. These can be strapped using resistors. The default configuration will meet the needs of most developers. Resistor reconfiguration is supported so that you can explore other boot configurations of the AM571x processor. See Section 4 for more details.

#### 2.2 Clocks

The main clock for the processor is derived from a 20-MHz crystal. An on-board oscillator in the AM571x processor generates the base clock and the subsequent module clocks as needed within the AM571x processor. The board design supports a crystal attached to the RTC block, but this is not needed since RTC-only mode is not supported in this device.

#### 2.3 Reset Signals

The AM571x processor contains 3 reset inputs and an output indicating a reset is in progress. The reset pins are:

- PORz: PORz is a hard reset that resets everything including emulation logic. It also tri-states most outputs.

- RESETn: RESETn is a device reset commonly driven by control logic or emulation.

- RTC\_PORz: Separate PORz for the RTC module that must be driven at the same time as PORz. (Note that PORz and RTC\_PORz can only be directly connected as long as VDDSHV3 and VDDSHV5 are driven at the same voltage.)

- RSTOUTn: Output signal from SOC indicating that the device has entered reset. This is used to reset other circuits that must be reset at the same time as the processor.

More details about the behavior of these reset pins within the AM571x processor can be found in the AM571x Sitara Processors Silicon Revision 2.0 Data Manual (SPRS957). There are push buttons on the IDK that can initiate either a RESETn or PORz input. SW1 can drive PORz active (low) and SW2 can drive RESETn active (low).

There is a device erratum in all of the AM571x devices that prevents use of RESETn independent from PORz (see i862, Reset Should Use PORz, in the AM571x Sitara Processors Silicon Errata (SPRZ436). The workaround is to generate PORz whenever a device reset occurs even if it is from an internal initiator. This is accomplished through cooperation with the PMIC paired with the AM571x device on the IDK EVM. The RSTOUTn output from the AM571x device is connected to the NRESWARM input of the PMIC. This initiates a re-start that drives RESET\_OUT low and resets all voltages to their initial values. Since RESET\_OUT from the PMIC is connected to PORz in the AM571x device, a hard reset is forced on the SOC that meets the needs of the erratum workaround.

The AM571x IDK EVM is started by pressing the start-up push button, SW3. The POWERHOLD input can be connected to VRTC\_OUT in customer designs to cause the board to power-on as soon as the main supply is stable.

The configuration of the PMIC to provide RESET\_OUT from the NRESWARM input creates an always-on implementation. This always-on mode of operation prevents software shut-down of the IDK. Customer designs should have power-good monitoring circuitry such as a TPS3808 connected to the main supply to the PMIC that is connected to the PMIC RESET\_IN, as shown in the AM571x IDK EVM schematic (v1.3). The TPS3808 can detect the main supply voltage dropping and then trigger the PMIC to execute a controlled shut-down that meets the requirements in the AM571x Sitara Processors Silicon Revision 2.0 Data Manual (SPRS957).

www.ti.com Power Supplies

#### 3 Power Supplies

This section describes how the power supplies required for the design are generated.

#### 3.1 Power Source

The AM571x IDK EVM uses an external 5V power supply. The 5V power input is converted into different voltage levels to provide power inputs to the AM571x processor and other circuitry.

Early versions of the AM571x IDK EVM shipped with the GlobTek, Inc. external power supply with the part number TR9CA6500LCP-N, model number GT-43008-3306-1.0-T3. This external power supply is rated for an output voltage of +5VDC with an output current up to 6.5A. This external power supply contains applicable regional product regulatory/safety certification requirements for most worldwide locations. If you cannot use this supply, one with equivalent ratings that is approved for your location must be obtained.

Note that recently sold IDK EVMs do not ship with a power supply in the box due to international concerns. Also note that the power supply listed above is being discontinued. The manufacturer has provided a drop-in replacement. This is the TR9CA8000LCPIM(R6B), which is readily available from distributors such as Digikey.

The AM571x IDK EVM contains a right angle mounted power connector that accepts the +5VDC supply input on the center pin with the outer shell as the common return. The power connector accepts a mating plug with a 2.5-mm ID and a 5.5-mm OD.

Removing the power plug and inserting it again while the power supply is energized may damage the AM571x IDK EVM and/or other devices attached to the board such as emulators that provide an alternate path to ground. Removal of AC power from the external power supply is a safer method, if required.

It is recommended that the external power supply have the common return bonded to earth ground. If this is not possible, a separate connection from the board ground to earth ground may need to be provided. Terminal block J53 is added for this purpose.

#### 3.2 TPS6590377 PMIC

The power requirements of the processor are met by the TPS6590377 Power Management IC (PMIC). The power sequencing requirements of the AM571x processor are also handled by the TPS6590377 PMIC. Figure 6 shows the supply connections from the TPS6590377 PMIC to the AM571x processor.

Refer to the AM571x Sitara Processors Silicon Revision 2.0 Data Manual (SPRS957) for more information about the required supply voltages and supply sequencing. Also refer to the TPS659037 Power Management Unit (PMU) for Processor Data Manual (SLIS165) and the TPS659037 User's Guide to Power AM572x and AM571x User's Guide (SLIU011) for details about its operation.

Note that the production version of the AM571x IDK EVM uses the TPS6590377 PMIC that supplies the voltages needed for the latest silicon version of the AM5718 processor. Beta prototype IDK EVM units used the TPS6590375 PMIC and Alpha prototype IDK EVM units used the TPS6590372 PMIC.

#### 3.3 AVS Control

The AM571x processor consumes most of its power in its core logic. Therefore, minimizing the voltage supplied to this core logic can minimize power consumption. SmartReflex™ technology is used to provide this optimized solution.

This core logic is separated into multiple segments that can each be controlled separately. In this way, applications that need more performance in some processing blocks can operate at higher performance levels by increasing the supply voltage, while other processing blocks that do not require the same level of performance can operate at lower voltage thus further optimizing system power consumption.

The TPS6590377 PMIC is connected to the I2C1 on the AM5718 processor. This allows the application software to individually control the AVS supply outputs. It also allows the application to control the voltage generated by LDO1 that is used for the SDIO interface that operates at either 1.8V or 3.3V depending on the operating mode.

Power Supplies www.ti.com

Figure 6. Connections from the TPS6590377 PMIC to the AM571x Processor

#### 3.4 Other Power Supplies

The AM571x IDK EVM contains 8 other power conversion devices that support the interface and memory circuitry:

- TPS63010 Buck-Boost Converter: This converter generates 5.0V from the main supply input. It supplies this voltage to the industrial interface circuits, the HDMI interface and to the USB master ports.

- TPS61085 Boost Converter: This converter generates 12.0V from the main supply input. It supplies

voltage to the industrial interface circuits and the PCle card connector.

- TPS51200 DDR Termination Voltage LDO (2 each): This LDO provides the push/pull termination current required for the DDR3 memory interfaces. There is one implemented for each DDR3 EMIF.

- LP38693ADJ Low-Dropout Regulator: This LDO generates the 3.7V LCD bias voltage.

- TPS61081DRC LCD Backlight Generator: This Boost converter generates the LCD backlight supply.

- TPS71712 Low-Dropout Regulator: This LDO generates the 1.2V supply needed for the LCD driver logic.

- TPS76650 Low-Dropout Regulator: This LDO generates the 5.0V supply needed for the Profibus interface.

- R1Z-3.305HP Isolated DC-DC Supply: This converter generates 5.0V isolated from the primary 3.3V DC supply on board for the DCAN interface.

Configuration/Setup www.ti.com

#### 4 Configuration/Setup

This section discusses the board configuration.

#### 4.1 **Boot Configuration**

Various boot configurations can be set using the pull-up/pull-down resistor combinations provided on the SYSBOOT[15..0] pins. Boot configuration pins are latched upon de-assertion of the PORz pin. Refer to the AM571x Sitara Processors Silicon Revision 2.0 Data Manual (SPRS957) for more details. The AM571x IDK EVM is configured by default to 0x8106 to enable UBOOT/Linux boot from the SDCARD. The secondary boot device selected by this boot mode is QSPI1.

#### 4.2 **I2C Address Assignments**

The AM571x IDK EVM contains multiple I2C buses connected to a master port on the processor. Each bus contains one or more I2C slave devices that must have unique addresses to prevent contention. Table 1 and Table 2 list the addresses of the I2C slave devices attached to buses I2C1 and I2C2. respectively.

Table 1. I2C1/IND I2C

| I2C Slave Device                        | Address(es)                  |

|-----------------------------------------|------------------------------|

| TPS590377 PMIC, U3                      | 0x58, 0x59, 0x5A, 0x5B, 0x12 |

| Camera Header, J9                       | Undefined                    |

| CDCE913 Ethernet Clock Generator A, U23 | 0x65                         |

| TPIC2810 Industrial Output Driver, U89  | 0x60                         |

| LCD Panel Driver TC358778, U73          | 0x0E                         |

| Touchscreen FPC Connector, J17          | _                            |

| ID Memory SEEPROM, U33                  | 0x50                         |

| PCIe Card Connector, J52                | Undefined                    |

| Expansion Connector, J21                | Undefined                    |

Table 2. I2C2/AM571X HDMI DDC

| I2C Slave Device                        | Address(es) |

|-----------------------------------------|-------------|

| HDMI Bridge, U46                        | _           |

| CDCE913 Ethernet Clock Generator B, U25 | 0x65        |

NOTE: SCL/SDA names are swapped between the HDMI DDC port and I2C2 port on AM57xx devices - I2C2 schematic connections to U25 must be reversed.

Configuration/Setup www.ti.com

#### 4.3 SEEPROM Header

Each of the AM571x IDK EVMs has a unique serial number. This serial number is printed on a sticker attached to the IDK and it is programmed into a SEEPROM memory device connected to the AM5718 processor over the I2C bus. The SEEPROM also contains board details such as board type, version, configuration, and so on. This information is stored in a structure at the beginning of the SEEPROM in a known format that can be read by the application software. These values are all stored with the first character or MSB stored at the lowest addressable location in each field. Table 3 lists all of the fields in this header definition.

Table 3. SEEPROM Header

| Name                         | Size (bytes) | Contents                                                                                                                                                                                               |  |

|------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Header 4                     |              | MSB 0xEE3355AA LSB                                                                                                                                                                                     |  |

| Board Name                   | 8            | Name for board in ASCII "AM571IDK" = AM571x Industrial Development Kit EVM.                                                                                                                            |  |

| Version                      | 4            | Hardware version code for board in ASCII "1.3A" = revision 01.3A                                                                                                                                       |  |

| Serial Number 12             |              | Serial number of the board. This is a 12-character string that is: WWYY4P52nnnn, where WW = 2 digit week of the year of production, YY = 2 digit year of production, nnnn = incrementing board number. |  |

| Configuration Option         | 32           | Codes to show the configuration setup on this board. Reserved.                                                                                                                                         |  |

| Ethernet MAC 6<br>Address #0 |              | Ethernet MAC Address #0 assigned to the AM571x IDK EVM. This is the first of a block of addresses available for the Industrial Interface ports.                                                        |  |

| Ethernet MAC 6<br>Address #5 |              | Ethernet MAC Address #5 assigned to the AM571x IDK EVM. This is the last of a block of 6 contiguous addresses available for the industrial interface ports.                                            |  |

| Available                    | 32696        | Available user space for other non-volatile codes/data.                                                                                                                                                |  |

#### 4.4 JTAG Emulation

The AM571x IDK EVM supports embedded XDS100V2 USB Emulation through the USB Micro-AB connector, J19, and the FTDI controller. This controller is powered from the USB VBUS, thus the emulator connection to the PC is retained whenever the IDK is power cycled.

The AM571x IDK EVM also has a 20-pin CTI JTAG connector, J18, to support standard external emulators that may operate more efficiently than the embedded XDS100V2 emulation. The AM571x IDK EVM does not support emulation trace capability.

www.ti.com Memories Supported

#### 5 Memories Supported

The AM571x IDK EVM supports on-board memories including DDR3L SDRAM, SPI NOR Flash, eMMC NAND Flash, and I2C SEEPROM. It also supports a MicroSD card socket that can add memory storage.

#### 5.1 DDR3L SDRAM

The AM571x IDK EVM design supports a single bank of DDR3L SDRAM that is attached to the EMIF on the AM5718 processor. The EMIF can support up to 2GB of DDR3L SDRAM memory at speeds up to 1333MT/s. The SDRAM implemented on the EMIF on the IDK EVM contains two 4Gbit (256M × 16) SDRAMs for a total of 1GB of DDR3L SDRAM memory. The part number for the DDR3L SDRAM memory used is MT41K256M16HA-125 that contains timing for 1600MT/s operation. The package used is the 96-ball TFBGA package. See the AM571x Sitara Processors Technical Reference Manual (SPRUHZ7) for memory locations for this memory.

The EMIF also contains an SDRAM attached to the ECC byte lane. Use of ECC on the DDR3L interface is currently highly constrained by limitations in the AM571x devices. Refer to the AM571x Sitara Processors Silicon Errata (SPRZ436) for more details.

#### 5.2 SPI NOR Flash

The AM571x IDK EVM supports a 256Mbit (32MB) SPI Flash Memory from Spansion (S25FL256S) in a 16-pin SOIC package. It is connected to the QSPI port of the AM5718 device.

#### 5.3 Board Identity Memory

Each of the AM571x IDK EVM boards contains a 256Kb (32KB) Serial EEPROM that contains board-specific data. This data allows the application software to automatically detect the type of board that it is running on and also to determine its version and, potentially, optional features. Other hardware specific data can be stored on this memory device as well. The part number of the memory device is CAT24C256WI-G in a SOIC-8 package. Refer to Section 4 for details on the data stored in this memory.

#### 5.4 SD/MMC

The SD/MMC connector on the AM571x IDK EVM is a MicroSD connector (part number SCHA5B0200). This is a standard SD/MMC card type of connector. It is connected to the MMC1 port of the AM571x processor that is optimized for this use. Refer to the AM571x Sitara Processors Silicon Revision 2.0 Data Manual (SPRS957) and the AM571x Sitara Processors Technical Reference Manual (SPRUHZ7) for supported card types and densities.

The SDWP input pin to the MMC1 port is connected to a 2-pin header, J44. The default state has the pin pulled high. Shorting the header pulls the pin low. The polarity of this input is programmable; thus, the hardware does not define whether a high or low level indicates Write Protest is active or not.

The transient protection implemented at the SDCARD connector is the TPD6E001.

#### 5.5 eMMC NAND Flash

The MMC2 port on the AM571x processor supports eMMC memory devices, since it has 8 data lines. The eMMC footprint is compliant with the JEDEC/MMC standard. Boards have been assembled and successfully tested with the Kingston EMMC16G-S100 and the Micron MTFC16GAKAECN-2M WT. These are 16GB eMMC NAND Flash memories that are standard version 5.0 compliant.

Ethernet Ports www.ti.com

#### 6 Ethernet Ports

The AM571x IDK EVM supports up to four 100Mb Industrial Ethernet ports attached to the PRU-ICSS subsystems and up to two Gigabit (1000Mb) Ethernet ports connected to the integrated Ethernet switch. The final number of available ports depends on the configuration selection:

- 4-port Ethernet mode: provides two 100Mb Industrial Ethernet ports and two Gigabit (1000Mb) Ethernet ports.

- 6-port Ethernet mode: provides four 100Mb Industrial Ethernet ports and two Gigabit (1000Mb) Ethernet ports.

Selection between these Ethernet modes is controlled by header J51. Installing a shunt on header J51 that shorts these pins together enables 4-port Ethernet mode. Removing the shunt from these pins enables 6-port Ethernet mode. The LCD output is only available when 4-port Ethernet mode is selected.

#### 6.1 100Mb Ethernet Ports on PRU-ICSS

The AM571x IDK EVM contains four 100Mb Ethernet ports that each connect to an industrial PHY/Transceiver (TLK105L), which then connect to RJ45 metallic connectors, with integrated magnetics, J3, J5, J6, and J8. These Ethernet transceivers are connected to the PRU1 and PRU2 subsystems within the AM5718 processor. Table 4 shows the mapping from the PRU-ICSS ports to the RJ45 connectors.

The COL functionality on the MII interface is not used. The TLK105L contains a feature that must be enabled via software that provides rapid link status on the COL pin. Therefore, this pin is connected to the RXLINK input to the PRU-ICSS ports for this purpose.

Test headers J4 and J7 are available to support real-time code development. The signals contained are available for simplified probing.

The reset for the transceivers is driven low coincident with the PORz reset to the AM5718 processor. The reset for each transceiver can also be driven low individually by separate GPIO signals from the processor. A 25-MHz clock is provided into each of the TLK105L industrial transceivers.

| Connector | PRU-ICSS Port | MDIO Address | Notes                                                                                             |

|-----------|---------------|--------------|---------------------------------------------------------------------------------------------------|

| J3        | PRU1ETH0      | 0x0 on PRU1  | Not available in all configuration selections. MII pins multiplexed with VOUT1 to the LCD bridge. |

| J5        | PRU1ETH1      | 0x1 on PRU1  | Not available in all configuration selections. MII pins multiplexed with VOUT1 to the LCD bridge. |

| J6        | PRU2ETH0      | 0x0 on PRU2  |                                                                                                   |

| J8        | PRU2ETH1      | 0x1 on PRU2  |                                                                                                   |

**Table 4. PRU-ICSS Ethernet Ports**

#### 6.2 Gigabit (1000Mb) Ethernet Ports

The AM571x IDK EVM contains two Gigabit (1000Mb) Ethernet PHY/Transceivers (KSZ9031RN) interfaced to connectors J10 (RGMII0) and J12 (RGMII1). These Gigabit Ethernet transceivers are connected over RGMII0 and RGMII1 to the Ethernet switch block within the AM5718 processor.

The resets for the transceivers are driven low coincident with the PORz reset to the AM5718 processor. A 25-MHz clock is provided into each of the KSZ9031RN Gigabit transceivers.

www.ti.com USB Ports

#### 7 USB Ports

The AM571x IDK EVM contains three USB ports. Two ports are attached to the USB peripherals USB1 and USB2 on the AM5718 processor. The third port provides both XDS100V2 JTAG emulation and UART Console over the USB. This port simplifies the development environment for programmers using computers that support this capability such as Windows®-based computers.

#### 7.1 Processor USB Port 1

Processor port USB1 is implemented only as a USB host (master). It supports only the USB2.1 (high speed and lower) data rates. The connector on the board, J23, is a USB2.1 Standard A-type connector. The ESD devices implemented on this USB port are the TPD2EUSB30 for the DP and DM lines.

Since processor USB port 1 supports host mode, it has the capability to drive 5.0V power on the VBUS pin. The TPS2065D load switch is controlled by the USB1 DRVVBUS pin for this purpose.

#### 7.2 Processor USB Port 2

Processor port USB2 is implemented as either USB host (master) or USB device (slave). It supports only the USB2.1 (high speed and lower) data rates. The connector on the board, J45, is a USB2.1 Micro-AB connector. The ESD device implemented on this USB port is the TPD4S012.

Since processor USB port 2 supports host mode, it has the capability to drive 5.0V power on the VBUS pin. The TPS2051 load switch is controlled by the USB2 DRVVBUS pin for this purpose.

The USB2.1 standard defines different ranges of capacitance for the VBUS pin depending on whether it is host or device. Since this port can do either, the AM571x IDK EVM provides the capability to meet either requirement. The VBUS pin from the connector contains a  $4.7\mu F$  capacitor that is appropriate for device mode operation. When operating in host mode, 2-pin header J50 can be shorted to add  $150\mu F$  of additional capacitance to the VBUS pin. The shunt for this header is shown on the schematic as M2. It is not installed on units when shipped as we expect this port to primarily be used in device mode.

#### 7.3 FTDI USB Port

The FTDI bridge device provides both XDS100V2 JTAG emulation and UART Console over the USB. The connector on the board, J19, is a USB Micro-AB connector but it only operates in device (slave) mode with the FTDI bridge device. The ESD device implemented on this USB port to the FTDI bridge is the TPD2E001. Refer to Section 4.4 for more details on this functionality.

The FTDI USB device is implemented so that it operates from the VBUS power provided over the USB cable. This allows the FTDI device to remain fully operational during an AM571x IDK EVM power cycle. This in turn allows the console port to the PC to remain active to allow logging from the serial port immediately as the AM5718 device boots. It also provides faster re-connect for the XDS100V2 JTAG emulator.

*PCIe* www.ti.com

#### **PCle**

The AM571x processors contain two lanes of peripheral component interconnect express (PCIe). These can be implemented either as a single, dual-lane port or as two single-lane ports. The PCle peripheral can be configured to either be a Root Complex (master) or an Endpoint (slave). The AM571x IDK EVM implements a single dual-lane port as a Root Complex. The AM571x IDK EVM terminates this dual-lane port in a ×4 PCIe female connector that accepts standard PCIe Endpoint cards.

A 2-pin header, J49, is available to provide the 3V3\_AUX power separate from the primary 3V3 supply. This is needed for some cards and PCIe driver configurations. The shunt, shown on the schematic as M1, should be installed when the board is received since 3V3 AUX will be needed in most cases. Please refer to the documentation for the card being installed to determine whether this shunt should remain installed.

The PERSTn reset for the connector is driven low coincident with the PORz reset to the AM5718 processor. The PERSTn reset to the connector can also be driven low by a GPIO signal from the processor. This reset can also be blocked by a GPIO signal from the processor.

A 100-MHz clock is provided separately to both the PCIe peripheral and to the PCIe connector. These clocks are buffered outputs from the same low-jitter source.

The AM571x IDK EVM is compatible with standard PCIe plug-in cards but not fully compliant with the PCIe CEM standard. It does not support hot-plug and also does not provide sufficient current on the 3.3V and 12V pins for all plug-in cards. It is currently limited to about 0.5A on each supply.

#### 9 **Video Input and Output**

The AM571x processor family supports industrial video capture and display in addition to its industrial communications capabilities. The AM571x IDK EVM contains a camera header for attaching a module containing a camera sensor as well as support for an LCD panel display and HDMI video output.

#### 9.1 Camera

The AM571x IDK EVM supports a camera daughterboard that attaches to a 24-pin (2 × 24) header, J9. The custom-designed camera module from TI, previously designed for the AM437x IDK EVM, mounts on this header. This header is connected to VIN4B on the AM5718 processor.

The 2Mp camera board contains the Darling Industrial camera module (part number DC-OVBD420AH). The camera module contains the OmniVision OV2659 camera sensor. Please contact OmniVision for the latest documentation on this sensor.

#### 9.2 HDMI

The AM571x IDK EVM supports an HDMI connector driven from the HDMI port on the AM5718 processor. The connector on the board, J24, is an HDMI Standard A-type connector. It is implemented with the TPD12S016 HDMI companion chip. This companion chip provides I2C level shifting buffers, 5V load switch, and multi-channel ESD protection.

#### 9.3 LCD

The AM571x IDK EVM is available with an optional LCD panel that also has a capacitive touch overlay. The video output driven for the LCD panel from the AM5718 processor is on VOUT1. A MIPI bridge device from Toshiba, TC358778, is implemented to convert from the 24-bit RGB presented on the VOUT1 pins to serial MIPI RGB streams. The LCD panel is shipped with FPC cables that plug into J16 for the MIPI video and into J17 for the touchscreen controller. Both the MIPI bridge device and the touchscreen controller are connected to the IND I2C chain from processor port I2C1.

The LCD output functionality is available only when the AM571x IDK EVM is configured for the 4-port Ethernet mode. When the AM571x IDK EVM is configured for the 6-port Ethernet mode, the LCD output is no longer available since the same pins on the AM5718 device are used for both functions.

NOTE: Installing a shunt on header J51 that shorts these pins together enables 4-port Ethernet mode. Removing the shunt from these pins enables 6-port Ethernet mode.

www.ti.com Industrial Interfaces

#### 10 Industrial Interfaces

There are additional industrial interfaces implemented on the AM571x IDK EVM to help showcase the flexibility of the AM57xx line of processors.

#### 10.1 Profibus

A compliant Profibus interface is implemented using the ISO1176T isolation device, transformer and TPS76650 LDO regulator. This circuit terminates to a DB9F connector, J14. This Profibus interface is driven by UART0 from the first PRU-ICSS block, PR1.

#### 10.2 DCAN

The AM5718 processor contains two Controller Area Network (DCAN) interfaces. DCAN port 1 is routed out to the ISO1050 isolation device and then to the 5-pin header, J38. The R1Z-3.305HP isolated DC-DC supply provides an isolated 3.3V supply for this DCAN interface.

#### 10.3 RS-485

The AM571x IDK EVM contains an RS-485 interface on 3-pin header, J39. This is enabled by the SN65HVD78D Half-Duplex RS-485 Transceiver. The transceiver controls the half-duplex communication and also provides high-voltage transient protection. This interface is attached to the SOC-level UART2 port for RX and TX data. The UART TX data line is monitored by PR2\_PRU1, so that PRU code can monitor TX activity and then control the DE and REn lines into the transceiver.

#### 11 User Interfaces

The AM571x IDK EVM contains GPIO expanders that provide industrial inputs and outputs to support development. The outputs contain LEDs for immediate feedback. There are also tri-color LEDs connected to GPIOs to support development.

#### 11.1 Tri-color LEDs

There are 6 tri-color LEDs connected to SOC GPIO pins that can be used to support development. There is a separate GPIO assigned for each color: red, green, and yellow. Color mixing by turning on more than one GPIO at a time will not provide the expected result since the separate colors have different intensities due to the physics of the LED composition. Tri-color LEDs D16, D17, D18, and D19 are designated Industrial LEDs. Tri-color LEDs D22 and D23 are designated Status LEDs.

#### 11.2 Industrial Inputs

For industrial 24v digital inputs, an SN65HVS882 Digital-input Serializer for industrial digital inputs is used to accept standard signals from the 30-pin ( $15 \times 2$ ) I/O Expansion Header, J37. The input values are clocked into the SPI3 port of the AM5718 processor.

#### 11.3 Industrial Outputs / LEDs

I2C to 8-bit LED driver TPIC2810 is used to drive the eight Industrial output LEDs D5 to D12. The I2C interface is connected to the I2C1 port of the AM5718 processor along with the other devices on the IND\_I2C bus. The eight LED driver outputs are also driven to the I/O Expansion Header, J37. All the LEDs are green in color.

Pin Use Description www.ti.com

#### 12 Pin Use Description

#### 12.1 Functional Interface Mapping

Some signals of the AM5718 device are connected to a fixed device on the EVM where it cannot be changed. However, some of the signals of the AM5718 device are connected to devices on the AM571x IDK EVM based on the profile setting.

#### 12.2 GPIO Pin Mapping

The developer can enable GPIO pins individually, as needed, as output, input, or both. Most of the LVCMOS pins not currently allocated for other peripheral use can be defined as GPIO pins. Table 5 is a compliment to the schematic and the recommended settings in the pinmux tool. Each of the defined GPIO pins are listed along with the associated pin name and ball number and mode. The last column lists the available physical pull-up (PU) or pull-down (PD) resistor attached or the recommended internal pull-up or pull-down resistor defined in the pinmux file provided for the AM571x IDK EVM.

www.ti.com Pin Use Description

**Table 5. GPIO Pin Mapping**

| Pin Name      | GPIO#    | Pin # | IDK Net Name / Function  | Direction | Pull Up /<br>Pull Down   |

|---------------|----------|-------|--------------------------|-----------|--------------------------|

| MCASP2_AXR4   | GPIO1_4  | D15   | AM57XX_INDETHER_LED0_YEL | Output    | EXT PD                   |

| MCASP2_AXR7   | GPIO1_5  | A17   | AM57XX_INDETHER_LED1_YEL | Output    | EXT PD                   |

| GPMC_CS0      | GPIO2_19 | T1    | AM57XX_STATUSLED1_YEL    | Output    | EXT PD                   |

| GPMC_CS3      | GPIO2_21 | P1    | AM57XX_STATUSLED1_GRN    | Output    | EXT PD                   |

| GPMC_CLK      | GPIO2_22 | P7    | 6PORT_LCDn               | Input     | EXT PU                   |

| GPMC_ADVN_ALE | GPIO2_23 | N1    | GPIO_IND_LDn             | Output    | EXT PU                   |

| GPMC_OEN_REN  | GPIO2_24 | M5    | GPIO_VPP_PWR_EN          | Output    | EXT PD                   |

| GPMC_WEN      | GPIO2_25 | M3    | AM57XX_STATUSLED0_RED    | Output    | EXT PD                   |

| GPMC_BEN0     | GPIO2_26 | N6    | AM57XX_STATUSLED0_GRN    | Output    | EXT PD                   |

| GPMC_BEN1     | GPIO2_27 | M4    | AM57XX_STATUSLED0_YEL    | Output    | EXT PD                   |

| GPMC_WAIT0    | GPIO2_28 | N2    | AM57XX_STATUSLED1_RED    | Output    | EXT PD                   |

| MCASP2_AXR6   | GPIO2_29 | B17   | AM57XX_INDETHER_LED1_GRN | Output    | EXT PD                   |

| VIN2A_CLK0    | GPIO3_28 | E1    | PRU1ETH0_INTn            | Input     | INT PU                   |

| VIN2A_DE0     | GPIO3_29 | G2    | PRU1ETH1_INTn            | Input     | INT PU                   |

| VIN2A_FLD0    | GPIO3_30 | H7    | PRU2ETH0_INTn            | Input     | INT PU                   |

| VIN2A_HSYNC0  | GPIO3_31 | G1    | PRU2ETH1_INTn            | Input     | INT PU                   |

| VIN2A_VSYNC0  | GPIO4_0  | G6    | AM57XX_INDETHER_LED0_GRN | Output    | EXT PD                   |

| VOUT1_FLD     | GPIO4_21 | B11   | eMMC_RSTn                | Output    | EXT PU                   |

| MCASP1_ACLKR  | GPIO5_0  | B14   | GB_ETH0_INTn             | Input     | EXT PU                   |

| MCASP1_FSR    | GPIO5_1  | J14   | GB_ETH1_INTn             | Input     | EXT PU                   |

| MCASP1_AXR2   | GPIO5_4  | G13   | PCIE_CRDPRESENT          | Input     | EXT PU                   |

| MCASP1_AXR3   | GPIO5_5  | J11   | PCIE_WAKEn               | Input     | EXT PU                   |

| MCASP1_AXR4   | GPIO5_6  | E12   | TOUCH_INT                | Input     | INT PU                   |

| MCASP1_AXR5   | GPIO5_7  | F13   | GPIO_AM571X_USB2_ID      | I/O       | EXT PU                   |

| MCASP1_AXR6   | GPIO5_8  | C12   | GPIO_PRU1_ETH_RESETn     | Output    | EXT PU                   |

| MCASP1_AXR7   | GPIO5_9  | D12   | GPIO_PRU2_ETH_RESETn     | Output    | EXT PU                   |

| UART3_RXD     | GPIO5_18 | V2    | GPIO_PCIE_SWRSTn         | Output    | INT PU                   |

| UART3_TXD     | GPIO5_19 | Y1    | GPIO_PCIE_RSTDRVn        | Output    | INT PU                   |

| MCASP2_AXR5   | GPIO6_7  | B16   | AM57XX_INDETHER_LED1_RED | Output    | EXT PD                   |

| GPIO6_14      | GPIO6_14 | E21   | CAM_ENn                  | Output    | PU/PD on camera<br>board |

| GPIO6_15      | GPIO6_15 | F20   | GPIO_TOUCH_RESETn        | Output    | EXT PU                   |

| GPIO6_16      | GPIO6_16 | F21   | PMIC_INT                 | Input     | INT PU                   |

| XREF_CLK2     | GPIO6_19 | B26   | AM57XX_INDETHER_LED0_RED | Output    | EXT PD                   |

| SPI1_SCLK     | GPIO7_7  | A25   | AM57XX_AUDIOBUZZER_TRIG  | Output    | EXT PD                   |

| SPI1_D1       | GPIO7_8  | F16   | AM57XX_INDETHER_LED2_GRN | Output    | EXT PD                   |

| SPI1_D0       | GPIO7_9  | B25   | AM57XX_INDETHER_LED2_RED | Output    | EXT PD                   |

| SPI1_CS0      | GPIO7_10 | A24   | AM57XX_INDETHER_LED2_YEL | Output    | EXT PD                   |

| SPI1_CS1      | GPIO7_11 | A22   | AM57XX_INDETHER_LED3_RED | Output    | EXT PD                   |

| UART1_RXD     | GPIO7_22 | B27   | GPIO_USB2_VBUS_DET       | Input     | EXT PU                   |

| UART1_CTSN    | GPIO7_24 | E25   | AM57XX_INDETHER_LED3_YEL | Output    | EXT PD                   |

| UART1_RTSN    | GPIO7_25 | C27   | AM57XX_INDETHER_LED3_GRN | Output    | EXT PD                   |

Board Connectors www.ti.com

#### 13 Board Connectors

This section shows the pin-outs for the connectors on the AM571x IDK EVM.

**Table 6. Expansion Connector - J21**

|     | Table 0. Expansion Col |                       |

|-----|------------------------|-----------------------|

| Pin | Signal Name            | Secondary Signal Name |

| 1   | V3_3D                  | _                     |

| 2   | V5_0D                  | _                     |

| 3   | AM571X_PRU1ETH1_COL    | PR1_EDC_LATCH0        |

| 4   | GPMC_CS0               | ETH_MDIO_CLK          |

| 5   | PR1_MII1_CRS           | _                     |

| 6   | GPMC_CS3               | ETH_MDIO_DATA         |

| 7   | PR1_MII1_MR1_CLK       | _                     |

| 8   | GPMC_ADVN_ALE          | UART1_TXD             |

| 9   | PR1_MII1_RXDV          | _                     |

| 10  | GPMC_OEN_REN           | UART1_TXD             |

| 11  | PR1_MII1_RXD3          | _                     |

| 12  | GPMC_WEN               | PR1_MII0_RXER         |

| 13  | PR1_MII1_RXD2          | PR2_EDC_LATCH0        |

| 14  | GPMC_BEN0              | PR1_MII0_RXLINK       |

| 15  | PR1_MII1_RXD1          | PR2_EDC_LATCH1        |

| 16  | GPMC_BEN1              | PR1_MII0_COL          |

| 17  | PR1_MII1_RXD0          | PR2_EDC_SYNC0         |

| 18  | AM57XX_PRU2ETH1_CRS    | AM571X_RGMII0_TXCLK   |

| 19  | PR1_MII_MT0_CLK        | PR2_EDC_SYNC1         |

| 20  | AM57XX_PRU2ETH1_COL    | AM571X_RGMII0_TXCTL   |

| 21  | PR1_MII0_TXD3          | _                     |

| 22  | DGND                   | _                     |

| 23  | PR1_MII0_TXD2          | _                     |

| 24  | SPI2_SCLK              | AM571X_RGMII0_TD0     |

| 25  | SYS_RESETn             |                       |

| 26  | SPI2_DIN               | AM571X_RGMII0_TD1     |

| 27  | IND_I2C_SCL            | _                     |

| 28  | SPI2_DOUT              | AM571X_RGMII0_TD2     |

| 29  | IND_I2C_SDA            |                       |

| 30  | SPI2_CS0n              | AM571X_RGMII0_TD3     |

| 31  | AM57XX_GPMC_AD0        | PR1_MII0_TXEN         |

| 32  | AM57XX_GPMC_AD8        | AM571X_VIN2A_CLK0     |

| 33  | AM57XX_GPMC_AD1        | PR1_MII0_TXD1         |

| 34  | AM57XX GPMC AD9        | AM571X VIN2A DE0      |

| 35  | AM57XX GPMC AD2        | PR1 MII0 TXD0         |

| 36  | AM57XX GPMC AD10       | AM571X_VIN2A_FLD0     |

| 37  | AM57XX_GPMC_AD3        | PR1_MII_MR0_CLK       |

| 38  | AM57XX_GPMC_AD11       | AM571X_VIN2A_HSYNC0   |

| 39  | DGND                   |                       |

| 40  | DGND                   | _                     |

| 41  | CAN1_RXDF              | _                     |

| 42  | AM57XX GPMC AD12       | AM571X VIN2A VSYNC0   |

| 43  | CAN1 TXDF              | <u> </u>              |

| 44  | AM57XX GPMC AD13       | AM57XX PR1 UART0 RXD  |

|     |                        |                       |

www.ti.com Board Connectors

Table 6. Expansion Connector - J21 (continued)

| Pin | Signal Name           | Secondary Signal Name |

|-----|-----------------------|-----------------------|

| 45  | PR1_MII0_RXDV         | _                     |

| 46  | AM57XX_GPMC_AD14      | AM57XX_PR1_UART0_TXD  |

| 47  | PR1_MII0_RXD3         | _                     |

| 48  | AM57XX_GPMC_AD15      | AM571X_VIN2A_D2       |

| 49  | AM57XX_PR2_PROFI_TXEN | _                     |

| 50  | HDQ                   | AM571X_RGMII0_RXCLK   |

| 51  | AM57XX_GPMC_AD4       | PR1_MII0_RXD2         |

| 52  | GPMC_WAIT0            | _                     |

| 53  | AM57XX_GPMC_AD5       | PR1_MII0_RXD1         |

| 54  | AM571X_PRU1ETH1_TXD1  | AM57XX_PRU2ETH0_CRS   |

| 55  | AM57XX_GPMC_AD6       | PR1_MII0_RXD0         |

| 56  | AM571X_PRU1ETH1_TXD0  | AM57XX_PRU2ETH0_COL   |

| 57  | AM57XX_GPMC_AD7       | <del>-</del>          |

| 58  | GPMC_CLK              | <del>_</del>          |

| 59  | DGND                  | <del>_</del>          |

| 60  | DGND                  | <del></del>           |

Board Connectors www.ti.com

Table 7. I/O Expansion Header Connector - J37

| Pin | Signal Name  |

|-----|--------------|

| 1   | INDUS_INPUT0 |

| 2   | V12_0D       |

| 3   | INDUS_INPUT1 |

| 4   | V12_0D       |

| 5   | INDUS_INPUT2 |

| 6   | V12_0D       |

| 7   | INDUS_INPUT3 |

| 8   | V12_0D       |

| 9   | INDUS_INPUT4 |

| 10  | V12_0D       |

| 11  | INDUS_INPUT5 |

| 12  | V12_0D       |

| 13  | INDUS_INPUT6 |

| 14  | V12_0D       |

| 15  | INDUS_INPUT7 |

| 16  | V12_0D       |

| 17  | DGND         |

| 18  | No Connect   |

| 19  | DRAIN0       |

| 20  | DRAIN1       |

| 21  | DRAIN2       |

| 22  | DRAIN3       |

| 23  | DRAIN4       |

| 24  | DRAIN5       |

| 25  | DRAIN6       |

| 26  | DRAIN7       |

| 27  | V5_0D        |

| 28  | V5_0D        |

| 29  | DGND         |

| 30  | DGND         |

www.ti.com Board Connectors

#### **Table 8. MicroSD Connector - J15**

| Pin | Pin Name | Signal Name |

|-----|----------|-------------|

| 1   | DAT2     | MMC_D2      |

| 2   | DAT3     | MMC_D3      |

| 3   | CMD      | MMC_CMD     |

| 4   | VDD      | V3_3D       |

| 5   | CLOCK    | MMC_CLK     |

| 6   | DGND     | VSS         |

| 7   | DAT0     | MMC_D0      |

| 8   | DAT1     | MMC_D1      |

| 9   | GND      | DGND        |

| 10  | CD       | MMC1_SDCD   |

| 11  | GND3     | DGND        |

| 12  | GND4     | DGND        |

| 13  | GND5     | DGND        |

| 14  | GND6     | DGND        |

| 15  | GND7     | DGND        |

| 16  | GND8     | DGND        |

Table 9. Power Jack Connector - J1

| Pin | Signal Name |

|-----|-------------|

| 1   | VPWRIN_JCK  |

| 2   | DGND        |

| 3   | DGND        |

Table 10. Power Terminal Block Connector - J2

| Pin | Signal Name |

|-----|-------------|

| 1   | VPWRIN_JCK  |

| 2   | DGND        |

Board Connectors www.ti.com

Table 11. PRU1ETH0 RJ45 Connector - J3

| Pin   | Pin Name        | Signal Name        |

|-------|-----------------|--------------------|

| 1     | RD+             | PRU1ETHER0_RDP     |

| 2     | RD-             | PRU1ETHER0_RDN     |

| 3     | RCT             | V3_3D              |

| 4     | TCT             | V3_3D              |

| 5     | TD+             | PRU1ETHER0_TDP     |

| 6     | TD-             | PRU1ETHER0_TDN     |

| 7     | N/C             | No connect         |

| 8     | AC GND          | DGND               |

| 9     | YEL LED Anode   | V3_3D              |

| 10    | YEL LED Cathode | RXLINK             |

| 11    | GRN LED Anode   | V3_3D              |

| 12    | GRN LED Cathode | PRU1ETH0_LINKLED   |

| SHLD1 | Shield          | AGNDFRAME_PRU1ETH0 |

| SHLD2 | Shield          | AGNDFRAME_PRU1ETH0 |

Table 12. PRU1ETH1 RJ45 Connector - J5

| Pin   | Pin Name        | Signal Name        |

|-------|-----------------|--------------------|

| 1     | RD+             | PRU1ETHER1_RDP     |

| 2     | RD-             | PRU1ETHER1_RDN     |

| 3     | RCT             | V3_3D              |

| 4     | TCT             | V3_3D              |

| 5     | TD+             | PRU1ETHER1_TDP     |

| 6     | TD-             | PRU1ETHER1_TDN     |

| 7     | N/C             | No connect         |

| 8     | AC GND          | DGND               |

| 9     | YEL LED Anode   | V3_3D              |

| 10    | YEL LED Cathode | RXLINK             |

| 11    | GRN LED Anode   | V3_3D              |

| 12    | GRN LED Cathode | PRU1ETH1_LINKLED   |

| SHLD1 | Shield          | AGNDFRAME_PRU1ETH1 |

| SHLD2 | Shield          | AGNDFRAME_PRU1ETH1 |

www.ti.com Board Connectors

#### Table 13. PRU2ETH0 RJ45 Connector - J6

| Pin   | Pin Name        | Signal Name        |

|-------|-----------------|--------------------|

| 1     | RD+             | PRU2ETHER0_RDP     |

| 2     | RD-             | PRU2ETHER0_RDN     |

| 3     | RCT             | V3_3D              |

| 4     | TCT             | V3_3D              |

| 5     | TD+             | PRU2ETHER0_TDP     |

| 6     | TD-             | PRU2ETHER0_TDN     |

| 7     | N/C             | No connect         |

| 8     | AC GND          | DGND               |

| 9     | YEL LED Anode   | V3_3D              |

| 10    | YEL LED Cathode | RXLINK             |

| 11    | GRN LED Anode   | V3_3D              |

| 12    | GRN LED Cathode | PRU2ETH0_LINKLED   |

| SHLD1 | Shield          | AGNDFRAME_PRU2ETH0 |

| SHLD2 | Shield          | AGNDFRAME_PRU2ETH0 |

Table 14. PRU2ETH1 RJ45 Connector - J8

| Pin   | Pin Name        | Signal Name        |

|-------|-----------------|--------------------|

| 1     | RD+             | PRU2ETHER1_RDP     |

| 2     | RD-             | PRU2ETHER1_RDN     |

| 3     | RCT             | V3_3D              |

| 4     | TCT             | V3_3D              |

| 5     | TD+             | PRU2ETHER1_TDP     |

| 6     | TD-             | PRU2ETHER1_TDN     |

| 7     | N/C             | No connect         |

| 8     | AC GND          | DGND               |

| 9     | YEL LED Anode   | V3_3D              |

| 10    | YEL LED Cathode | RXLINK             |

| 11    | GRN LED Anode   | V3_3D              |

| 12    | GRN LED Cathode | PRU2ETH1_LINKLED   |

| SHLD1 | Shield          | AGNDFRAME_PRU2ETH1 |

| SHLD2 | Shield          | AGNDFRAME_PRU2ETH1 |

Board Connectors www.ti.com

#### Table 15. PRU2ETH0 Test Header Connector - J7

| Pin | Signal Name         | Net Name             |

|-----|---------------------|----------------------|

| 1   | RT2_MII0_TXEN       | AM57XX_PRU2ETH0_TXEN |

| 2   | RT2_MII0_RXDV       | AM57XX_PRU2ETH0_RXDV |

| 3   | RT2_MII0_EDIO_DATA0 | AM571X_VIN2A_VSYNC0  |

| 4   | RT2_MII0_EDIO_DATA1 | AM57XX_PR1_UART0_TXD |

| 5   | DGND                | <del>_</del>         |

Table 16. PRU2ETH1 Test Header Connector - J4

| Pin | Signal Name         | Net Name            |

|-----|---------------------|---------------------|

| 1   | RT2_MII1_TXEN       | PRU2ETH1_TXEN       |

| 2   | RT2_MII1_RXDV       | PRU2ETH1_RXDV       |

| 3   | RT2_MII1_EDIO_DATA0 | AM57XX_VIN2A_HSYNC0 |

| 4   | RT2_MII1_EDIO_DATA1 | AM57XX_VIN2A_DE0    |

| 5   | DGND                | DGND                |

Table 17. Camera Connector - J9

| Pin | Pin Name   | Signal Name        |

|-----|------------|--------------------|

| 1   | Power      | VMAIN              |

| 2   | CAM1_VSYNC | DGND               |

| 3   | CAM1_DATA0 | AM571X_VIN4B_DATA0 |

| 4   | CAM1_HSYNC | _                  |

| 5   | CAM1_DATA1 | AM571X_VIN4B_DATA1 |

| 6   | CAM1_DATA6 | AM571X_VIN4B_DATA6 |

| 7   | CAM1_DATA2 | AM571X_VIN4B_DATA2 |

| 8   | CAM1_DATA7 | AM571X_VIN4B_DATA7 |

| 9   | CAM1_PCLK  | AM571X_VIN4B_PCLK  |

| 10  | No Connect | _                  |

| 11  | GND        | DGND               |

| 12  | GND        | DGND               |

| 13  | CAM1_DATA3 | AM571X_VIN4B_DATA3 |

| 14  | No Connect | _                  |

| 15  | CAM1_DATA4 | AM571X_VIN4B_DATA4 |

| 16  | CAM1_GIO0  | PU to V3_3D        |

| 17  | CAM1_WEN   | AM571X_VIN4B_DATA5 |

| 18  | CAM1_GIO1  | CAM_ENn            |

| 19  | CAM1_DATA5 | AM571X_VIN4B_DE    |

| 20  | CAM1_FIELD | AM571X_VIN4B_FLD   |

| 21  | GND        | DGND               |

| 22  | I2C_SCL    | IND_I2C_SCL        |

| 23  | Clock      | 20.000 MHz Osc Out |

| 24  | I2C_SDA    | IND_I2C_SDA        |

www.ti.com Board Connectors

### Table 18. GigE RJ45 Connector - J10

| Pin   | Pin Name       | Signal Name          |

|-------|----------------|----------------------|

| 1     | CH-GND         | DGND                 |

| 2     | VCC            | No connect           |

| 3     | MX3+           | ETHER0_D3P           |

| 4     | MX3-           | ETHER0_D3N           |

| 5     | MX2+           | ETHER0_D2P           |

| 6     | MX2-           | ETHER0_D2N           |

| 7     | MX1+           | ETHER0_D1P           |

| 8     | MX1-           | ETHER0_D1N           |

| 9     | MX0+           | ETHER0_D0P           |

| 10    | MX0-           | ETHER0_D0N           |

| 11    | RT GRN Anode   | PU to PHY0_LED_ACTn  |

| 12    | RT YEL Anode   | DGND                 |

| 13    | LEFT GRN Anode | DGND                 |

| 14    | LEFT YEL Anode | PU to PHY0_LED_LINKn |

| SHLD1 | Shield         | AGND_GBETH0          |

| SHLD2 | Shield         | AGND_GBETH0          |

Table 19. GigE RJ45 Connector - J12

| Pin   | Pin Name       | Signal Name          |

|-------|----------------|----------------------|

| 1     | CH-GND         | DGND                 |

| 2     | VCC            | No connect           |

| 3     | MX3+           | ETHER1_D3P           |

| 4     | MX3-           | ETHER1_D3N           |

| 5     | MX2+           | ETHER1_D2P           |

| 6     | MX2-           | ETHER1_D2N           |

| 7     | MX1+           | ETHER1_D1P           |

| 8     | MX1-           | ETHER1_D1N           |

| 9     | MX0+           | ETHER1_D0P           |

| 10    | MX0-           | ETHER1_D0N           |

| 11    | RT GRN Anode   | PU to PHY1_LED_ACTn  |

| 12    | RT YEL Anode   | DGND                 |

| 13    | LEFT GRN Anode | DGND                 |

| 14    | LEFT YEL Anode | PU to PHY1_LED_LINKn |

| SHLD1 | Shield         | AGND_GBETH1          |

| SHLD2 | Shield         | AGND_GBETH1          |

Board Connectors www.ti.com

#### Table 20. LCD Module FFC Connector - J16

| Pin | Pin Name         | Signal Name |

|-----|------------------|-------------|

| 1   | _                | No Connect  |

| 2   | _                | No Connect  |

| 3   | VCC              | V3_7LCD     |

| 4   | VCC              | V3_7LCD     |

| 5   | VCC              | V3_7LCD     |

| 6   | <del>_</del>     | No Connect  |

| 7   | GND              | DGND        |

| 8   | MIPI_LN3_N       | LCD_MIPI3N  |

| 9   | MIPI_LN3_P       | LCD_MIPI3P  |

| 10  | GND              | DGND        |

| 11  | MIPI_LN2_N       | LCD_MIPI2N  |

| 12  | MIPI_LN2_P       | LCD_MIPI2P  |

| 13  | GND              | DGND        |

| 14  | MIPI_LN1_N       | LCD_MIPI1N  |

| 15  | MIPI_LN1_P       | LCD_MIPI1P  |

| 16  | GND              | DGND        |

| 17  | MIPI_LN0_N       | LCD_MIPI0N  |

| 18  | MIPI_LN0_P       | LCD_MIPI0P  |

| 19  | GND              | DGND        |

| 20  | MIPI_CLK_N       | LCD_CLKN    |

| 21  | MIPI_CLK_P       | LCD_CLKP    |

| 22  | GND              | DGND        |

| 23  | LED_CATHODE      | VLED-       |

| 24  | LED_CATHODE      | VLED-       |

| 25  | LED_CATHODE      | VLED-       |

| 26  | LED_CATHODE      | VLED-       |

| 27  | LED_CATHODE      | VLED-       |

| 28  | LED_CATHODE      | VLED-       |

| 29  | LED Anode Supply | VLED+       |

| 30  | LED Anode Supply | VLED+       |

| 31  | _                | No Connect  |

| 32  | _                | No Connect  |

Table 21. Touchscreen Controller FFC Connector - J17

| Pin | Pin Name   | Signal Name       |

|-----|------------|-------------------|

| 1   | SDA        | IND_I2C_SDA       |

| 2   | SCL        | IND_I2C_SCL       |

| 3   | TSC_RESETn | GPIO_TOUCH_RESETn |

| 4   | TSC_INT    | TOUCH_INT         |

| 5   | V+         | V3_3D             |

| 6   | GND        | DGND              |

www.ti.com Board Connectors

Table 22. HDMI Standard A-type Connector - J24

| Pin  | Pin Name    | Signal Name     |

|------|-------------|-----------------|

| 1    | DAT2+       | HDMI_TX2+       |

| 2    | DAT2_S      | DGND            |

| 3    | DAT2-       | HDMI_TX2-       |

| 4    | DAT1+       | HDMI_TX1+       |

| 5    | DAT1_S      | DGND            |

| 6    | DAT1-       | HDMI_TX1-       |

| 7    | DAT0+       | HDMI_TX0+       |

| 8    | DAT0_S      | DGND            |

| 9    | DAT0-       | HDMI_TX0-       |

| 10   | CLK+        | HDMI_CLK+       |

| 11   | CLK_S       | DGND            |

| 12   | CLK-        | HDMI_CLK-       |

| 13   | CEC         | HDMICONN_CEC    |

| 14   | N/C         | No Connect      |

| 15   | SCL         | HDMICONN_I2CSCL |

| 16   | SDA         | HDMICONN_I2CSDA |

| 17   | DDC/CEC GND | DGND            |

| 18   | +5V         | V5_0HDMICONN    |

| 19   | HPLG        | HDMICONN_HPLG   |

| MTG1 | Shield      | DGND            |

| MTG2 | Shield      | DGND            |

| MTG3 | Shield      | DGND            |

| MTG4 | Shield      | DGND            |

Table 23. CTI-20 JTAG Connector - J18

| Pin | Pin Name    | Signal Name |

|-----|-------------|-------------|

| 1   | TMS         | JTAG_TMS    |

| 2   | TRSTn       | JTAG_TRSTn  |

| 3   | TDI         | JTAG_TDI    |

| 4   | TDIS        | PD to GND   |

| 5   | TVDD        | PU to V3_3D |

| 6   | PU to V3_3D | _           |

| 7   | TDO         | JTAG_TDO    |

| 8   | DGND        | _           |

| 9   | TCKRTN      | RTCK        |

| 10  | DGND        | EMU_DET     |

| 11  | TCK         | JTAG_TCK    |

| 12  | DGND        | _           |

| 13  | EMU0        | JTAG_EMU0   |

| 14  | EMU1        | JTAG_EMU1   |

| 15  | SRST        | EMU_RSTn    |

| 16  | DGND        | _           |

| 17  | EMU2        | No Connect  |

| 18  | EMU3        | No Connect  |

| 19  | EMU4        | No Connect  |

| 20  | DGND        |             |

Board Connectors www.ti.com

#### Table 24. JTAG USB Micro-AB Connector - J19

| Pin | Pin Name   | Signal Name |

|-----|------------|-------------|

| 1   | VBUS       | VUSB_JTAG   |

| 2   | DM         | EMU_USB_DM  |

| 3   | DP         | EMU_USB_DP  |

| 4   | ID         | No Connect  |

| 5   | GND        | DGND        |

| S1  | S1         | GNDUSBJ     |

| S2  | S2         | GNDUSBJ     |

| S3  | <b>S</b> 3 | GNDUSBJ     |

| S4  | S4         | GNDUSBJ     |

Table 25. USB Port 1 USB2.1 Standard A-type Connector - J23

| Pin | Pin Name | Signal Name  |

|-----|----------|--------------|

| 1   | VBUS     | VUSB_VBUS1   |

| 2   | DM       | USB1_CONN_DM |

| 3   | DP       | USB1_CONN_DP |

| 4   | GND      | DGND         |

| S1  | S1       | GNDUSB1      |

| S2  | S2       | GNDUSB1      |

Table 26. USB Port 2 USB2.1 Micro-AB Connector - J45

| Pin | Pin Name | Signal Name  |

|-----|----------|--------------|

| 1   | VBUS     | VUSB_VBUS2   |

| 2   | DM       | USB2_CONN_DM |

| 3   | DP       | USB2_CONN_DP |

| 4   | ID       | USB2_ID      |

| 5   | GND      | DGND         |

| S1  | S1       | GNDUSB2      |

| S2  | S2       | GNDUSB2      |

| S3  | S3       | GNDUSB2      |

| S4  | S4       | GNDUSB2      |

www.ti.com Board Connectors

#### Table 27. CAN Header Connector - J38

| Pin | Signal Name |

|-----|-------------|

| 1   | VCAN1       |

| 2   | CAN1_H      |

| 3   | CAN1_L      |

| 4   | GND_CAN1    |

| 5   | No Connect  |

Table 28. Profibus DB9F Connector - J14

| Pin | Signal Name |

|-----|-------------|

| 1   | No Connect  |

| 2   | No Connect  |

| 3   | PROFIBUS_A  |

| 4   | No Connect  |

| 5   | GND_PROFI   |

| 6   | VPROFI      |

| 7   | No Connect  |

| 8   | PROFIBUS_B  |

| 9   | No Connect  |

Table 29. RS-485 Header Connector - J39

| Pin | Signal Name |

|-----|-------------|

| 1   | RS485_A     |

| 2   | RS485_B     |

| 3   | DGND        |

Board Connectors www.ti.com

Table 30. PCle Connector - J52

| Table 30. PCIe Connector – J52 |                |                 |

|--------------------------------|----------------|-----------------|

| Pin                            | Pin Nmae       | Signal Name     |

| B1                             | +12 V          | V12_0D          |

| B2                             | +12 V          | V12_0D          |

| B3                             | +12 V          | V12_0D          |

| B4                             | Ground         | DGND            |

| B5                             | SMCLK          | PCIE_SMB_CLK    |

| B6                             | SMDAT          | PCIE_SMB_DATA   |

| B7                             | Ground         | DGND            |

| B8                             | +3.3V          | V3_3D           |

| B9                             | TRST#          | PCIE_TRSTn      |

| B10                            | +3.3V AUX      | V3_3AUX_PCIE    |

| B11                            | WAKE#          | PCIE_WAKEn      |

| B12                            | CLKREQ#        | No Connect      |

| B13                            | Ground         | DGND            |

| B14                            | HSOp(0)        | PCIECONN_PETp0  |

| B15                            | HSOn(0)        | PCIECONN_PETn0  |

| B16                            | Ground         | DGND            |

| B17                            | PRSNT2#        | DGND            |

| B18                            | Ground         | DGND            |

| B19                            | HSOp(1)        | PCIECONN_PETp1  |

| B20                            | HSOn(1)        | PCIECONN_PETn1  |

| B21                            | Ground         | DGND            |

| B22                            | Ground         | DGND            |

| B23                            | HSOp(2)        | No Connect      |

| B24                            | HSOn(2)        | No Connect      |

| B25                            | Ground         | DGND            |

| B26                            | Ground         | DGND            |

| B27                            | HSOp(3)        | No Connect      |

| B28                            | HSOn(3)        | No Connect      |

| B29                            | Ground         | DGND            |

| B30                            | Reserved       | No Connect      |

| B31                            | PRSNT2#        | DGND            |

| B32                            | Ground         | DGND            |

| A1                             | PRSNT1#        | PCIE_CRDPRESENT |

| A2                             | +12 V          | V12_0D          |

| A3                             | +12 V<br>+12 V | V12_0D          |

| A4                             | Ground         | DGND            |

| A5                             | TCK            | PD to DGND      |

| A6                             | TDI            | PU to V3_3D     |

| A7                             | TDO            | TP20            |

| A8                             | TMS            | PU to V3_3D     |

| A9                             | +3.3V          |                 |

|                                |                | V3_3D           |

| A10                            | +3.3V          | V3_3D           |

| A11                            | PERST#         | PCIE_PERSTn     |

| A12                            | Ground         | DGND            |

| A13                            | REFCLK+        | PCIE_REFCLKP    |

| A14                            | REFCLK-        | PCIE_REFCLKN    |

| A15                            | Ground         | DGND            |

| A16                            | HSIp(0)        | PCIE_PERp0      |

www.ti.com EVM Important Notice

Table 30. PCle Connector – J52 (continued)

| Pin | Pin Nmae | Signal Name       |

|-----|----------|-------------------|

| A17 | HSIn(0)  | PCIE_PERn0        |

| A18 | Ground   | DGND              |

| A19 | Reserved | No Connect        |

| A20 | Ground   | DGND              |

| A21 | HSIp(1)  | AM57XX_PCIE_PERp1 |

| A22 | HSIn(1)  | AM57XX_PCIE_PERn1 |

| A23 | Ground   | DGND              |

| A24 | Ground   | DGND              |

| A25 | HSIp(2)  | No Connect        |

| A26 | HSIn(2)  | No Connect        |

| A27 | Ground   | DGND              |

| A28 | Ground   | DGND              |

| A29 | HSIp(3)  | No Connect        |

| A30 | HSIn(3)  | No Connect        |

| A31 | Ground   | DGND              |