**AP2011**

### ■ Features

- Single 10V to 40V Supply Application

- 1.25V + 2.0% Voltage Reference

- Virtual Frequency Control<sup>TM</sup>.

- Fast Transient Response.

- Synchronous Operation for High Efficiency

- Current Limit Function.

- Small Size with Minimum External Components

- Soft Start and Shutdown Functions

- Industrial Temperature Range

- Under Voltage Lockout Function

- SOP-14L Pb-Free Package

### **■** Applications

- Microprocessor Core Supply

- Low Cost Synchronous Applications

- Voltage Regulator Modules (VRM)

- Networking Power Supplies

- Sequenced Power Supplies

- Telecommunication Power Supplies.

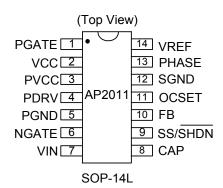

## Pin Assignments

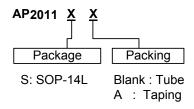

## Ordering Information

### ■ General Description

AP2011 is a low-cost, full featured, synchronous voltage-mode controller designed for use in single ended power supply applications primary where efficiency is of Synchronous operation allows for the elimination of heat sinks in many applications. The AP2011 is ideal for implementing DC/DC converters needed to power advanced microprocessors in low cost systems or in distributed power applications where efficiency is important. Internal level-shift, high-side drive circuitry, and preset shoot-thru control, allows the use of inexpensive 1P+1N-channel power switches.

AP2011's features include temperature ompensated voltage reference, Virtual Frequency Control<sup>TM</sup> method to reduce external component count, an internal virtual frequency 200KHz oscillator, under-voltage lockout protection, soft-start, shutdown function and current sense comparator circuitry.

Virtual Frequency Control is a trademark of PWRTEK, LLC.

## **■ Pin Descriptions**

| Pin Name | Pin<br>No. | Description                                                                               |  |  |  |

|----------|------------|-------------------------------------------------------------------------------------------|--|--|--|

| PGATE    | 1          | Level shift-gate driver                                                                   |  |  |  |

| VCC      | 2          | Internal regulator voltage                                                                |  |  |  |

| PVCC     | 3          | Power VCC                                                                                 |  |  |  |

| PDRV     | 4          | PMOS Gat driver                                                                           |  |  |  |

| PGND     | 5          | Power Ground                                                                              |  |  |  |

| NGATE    | 6          | Low side driver output (N MOSFET)                                                         |  |  |  |

| VIN      | 7          | Chip supply voltage                                                                       |  |  |  |

| CAP      | 8          | Charge pump pin                                                                           |  |  |  |

| SS/SHDN  | 9          | Soft start, a capacitor to ground sets the slow start time/set low for shutdown function. |  |  |  |

| FB       | 10         | Feedback input                                                                            |  |  |  |

| OCSET    | 11         | Sets the converter over-current trip point                                                |  |  |  |

| SGND     | 12         | Signal Ground                                                                             |  |  |  |

| PHASE    | 13         | Input from the phase node between the MOSFETs                                             |  |  |  |

| VREF     | 14         | Reference voltage                                                                         |  |  |  |

**AP2011**

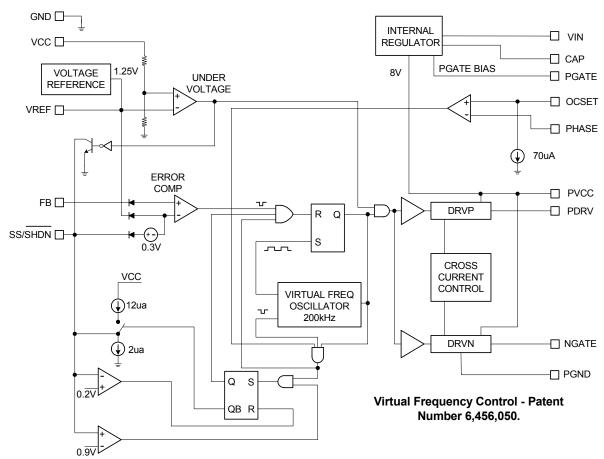

### **■** Block Diagram

**AP2011 FUNCTIONAL BLOCK DIAGRAM**

## ■ Absolute Maximum Ratings

| Symbol            | Parameter                              | Range.      | Unit |  |

|-------------------|----------------------------------------|-------------|------|--|

| V <sub>IN</sub>   | VCC to GND                             | 0 to 42     | V    |  |

| $V_{PHASE}$       | PHASE to GND                           | 0 to 42     | V    |  |

| $\Theta_{JC}$     | Thermal Resistance Junction to Case    | 60          | °C/W |  |

| $\Theta_{JA}$     | Thermal Resistance Junction to Ambient | 150         | °C/W |  |

| T <sub>OP</sub>   | Operating Temperature Range            | -40 to +85  | °C   |  |

| T <sub>ST</sub>   | Storage Temperature Range              | -65 to +150 | °C   |  |

| T <sub>LEAD</sub> | Lead Temperature (Soldering) 10 Sec.   | 300         | °C   |  |

**AP2011**

## **■** Electrical Characteristics

| Unless specified: | V20\V: CN    | JD - 0\/·\/-       | - 5\/· T 25°C    |

|-------------------|--------------|--------------------|------------------|

| Uniess specified. | VINI-ZUV. GI | <b>uD – UV.V</b> ∩ | – 3V. I I – Z3 C |

| Symbol                             | d: $V_{IN}$ =20V; GND = 0V; $V_O$ = 5V; $T_J$ = 25°C  Parameter | Conditions                                   | Min.  | Тур. | Max.  | Unit |

|------------------------------------|-----------------------------------------------------------------|----------------------------------------------|-------|------|-------|------|

| Power Sup                          | ply                                                             |                                              |       |      |       |      |

| V <sub>IN</sub>                    | Supply Voltage (Recommended)                                    |                                              | 10    | -    | 40    | V    |

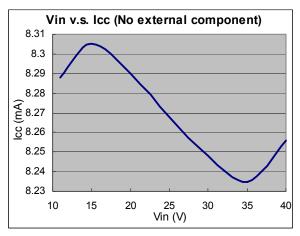

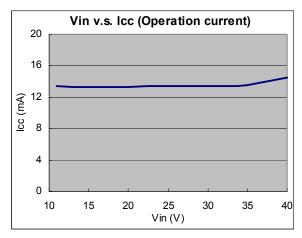

| I <sub>IN</sub>                    | Supply Current                                                  |                                              | -     | 8    | 10    | mA   |

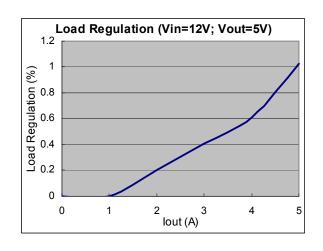

| $\Delta V_{Load}$                  | Load Regulation                                                 | 0A < I <sub>Load</sub> < 3A                  | -     | 50   | 70    | mV   |

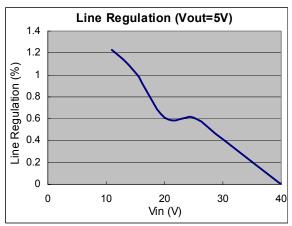

| $\Delta V_{LINE}$                  | Line Regulation                                                 | $V_{IN}$ = 10V to 40V<br>$I_{Load}$ =1A      | -     | 110  | 150   | mV   |

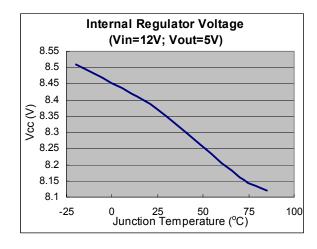

| V <sub>CC</sub>                    | Internal Regulator Voltage                                      | V <sub>IN</sub> =10V to 40V                  | 8     | 8.5  | 9     | V    |

| $V_{\text{IN}}$ - $V_{\text{CC}}$  | V <sub>CC</sub> Dropout Voltage                                 |                                              | -     | 1.5  | 3.0   | V    |

| V <sub>IN</sub> -P <sub>GATE</sub> | P-Gate to Source Voltage (Off)                                  | V <sub>IN</sub> =10V<br>V <sub>IN</sub> =40V | -0.4  | -0.2 | -     | V    |

| Error Comp                         | parator                                                         |                                              |       |      |       |      |

| $A_{OL}$                           | Gain (A <sub>OL</sub> )                                         |                                              | -     | 60   | -     | dB   |

| $I_{B}$                            | Input Bias                                                      |                                              | -     | 0.2  | 1     | uA   |

| Oscillator                         |                                                                 |                                              |       |      |       |      |

| $DC_{MAX}$                         | Oscillator Max Duty Cycle                                       |                                              | 80    | 85   | -     | %    |

| Protection                         |                                                                 |                                              |       |      |       |      |

| T <sub>DEAD</sub>                  | Dead Time                                                       |                                              | 100   | 150  | 250   | nS   |

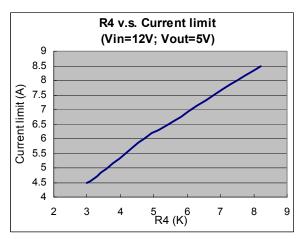

| I <sub>OCSET</sub>                 | Over Current Set Isink                                          | $V_{IN} - 1.5V \le V_{OCSET} \le V_{IN}$     | -     | 70   | -     | uA   |

| Reference                          |                                                                 |                                              |       |      |       |      |

|                                    | Reference Voltage                                               | 0°C to 70°C                                  | 1.225 | 1.25 | 1.275 | V    |

| $V_{REF}$                          | Accuracy                                                        | 10 0 10 70 0                                 | -2    | -    | + 2   | %    |

| Soft Start                         |                                                                 |                                              |       |      |       |      |

| I <sub>SSC</sub>                   | Charge Current                                                  | V <sub>SS</sub> = 1.5V                       | 8.0   | 10   | 12    | uA   |

| I <sub>SSD</sub>                   | Discharge Current                                               | V <sub>SS</sub> = 1.5V                       | 1.3   | 2    | 2.7   | uA   |

| Jnder volta                        | ge lockout (UVLO)                                               | •                                            | •     |      | •     |      |

| V <sub>UT</sub>                    | Upper Threshold Voltage (V <sub>CC</sub> )                      |                                              | -     | 6.8  | -     | V    |

| $V_{LWT}$                          | Lower Threshold Voltage (V <sub>CC</sub> )                      | T <sub>A</sub> = 25°C                        | -     | 6.5  | -     | V    |

| $V_{HT}$                           | Hysteresis (V <sub>CC</sub> )                                   |                                              | -     | 300  | -     | mV   |

|                                    | nation refers to Typical Application Circuit                    | -                                            | •     | -    | •     |      |

Note 1. Specification refers to Typical Application Circuit.

Note 2. This device is ESD sensitive. Use of standard ESD handling precautions is required.

Note 3. Abnormal condition; Ex: over-current, output over-voltage, under-voltage lockout, soft-start disappear.

Note 4. V<sub>CC</sub> pin should not be used to externally source current. It is not short protected.

**AP2011**

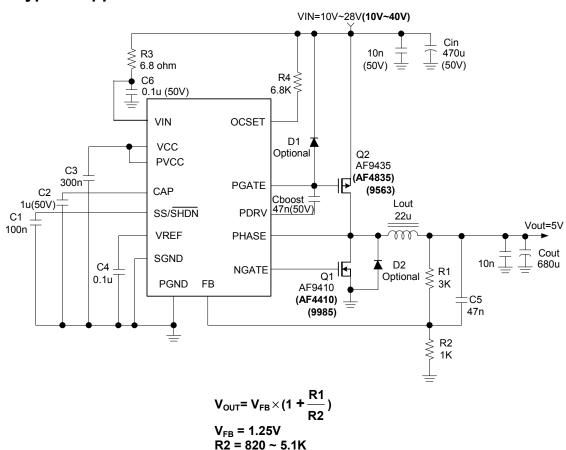

## **■** Typical Application Circuit

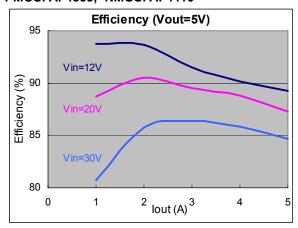

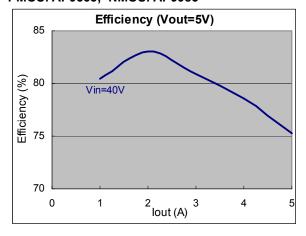

## ■ Typical Performance Characteristics

PMOS: AF4835; NMOS: AF4410

PMOS: AP9563; NMOS: AP9985

**AP2011**

## **■** Typical Performance Characteristics

**AP2011**

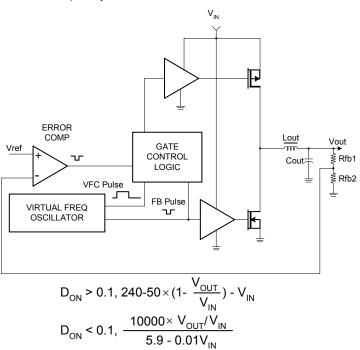

### **■ Virtual Frequency Control**

Virtual Frequency Control™ combines the advantages of constant frequency and constant off-time control in a single mode of operation. This allows fix frequency, precision switching voltage regulator control with fast transient response and the smallest solution size. Switch duty cycle can be adjusted from 0% to 100% on a pulse by pulse basis when responding to transient conditions. Both 0% and 100% duty cycle operation can be maintained for extended periods of time in response to load or line transients. Figure 1 depicts a simplified operation of the Virtual Frequency Control

technique: The VFC oscillator generates a pulse of a known duration (VFC\_Pulse). The regulator loop responds by returning a complementary feedback pulse (FB\_Pulse). The FB\_Pulse duration is a result of external conditions such as inductor size, the voltage across the inductor and the duration of the VFC\_Pulse. A VFC control loop is then formed whereby the duration of the VFC\_Pulse is modified as a result of the FB\_Pulse duration. The VFC loop arrives at a state of equilibrium, where the operating frequency remains inherently constant.

Figure 1: Virtual Frequency Control Loop-Synchronous single supply application.

Virtual frequency control is a technique that provides stable, constant frequency of operation for pulse controlled architectures such as constant off-time/on-time. This is all done internal to the IC with minimal number of components and without the need for connections to external terminals such as input and/or output. No external compensation is

required, thus providing a low cost, high performance fix frequency solution for switching voltage regulators.

Virtual Frequency Control is a trademark of PWRTEK, LLC.

**AP2011**

## **■** Function Description

#### **Synchronous Buck Converter**

Primary  $V_{\text{CORE}}$  power is provided by a synchronous, voltage-mode pulse width modulated (PWM) controller. This section has all the features required to build a high efficiency synchronous buck converter, including soft-start, shutdown, and cycle-by-cycle current limit.

Referring to the functional block diagram FIG 1, the output voltage of the synchronous converter is set and controlled by the output of the error comparator. The external resistive divider reference voltage, is derived from an internal trimmed-bandgap voltage reference. The inverting input of the error comparator receives its voltage from the FB pin.

The internal oscillator uses an on-chip capacitor and trimmed precision current sources to set the virtual oscillation frequency to 200Khz. The virtual frequency oscillator sets the PWM latch. This pulls DRVN low, turning off the low-side N MOSFET and DRVP is pulled low, turning on the high-side P-MOSFET (once the cross-current control allows it). The triangular voltage ramp at the FB pin is then compared against the reference voltage at the inverting input of the error comparator. When the FB voltage increases above the reference voltage, the comparator output goes high. This pulls DRVP high, turning off the high-side P-MOSFET, and DRVN is pulled high, turning on the low-side N-MOSFET (once the cross-current control allows it). The Virtual Frequency Oscillator then generates a programmed off time to allow the FB voltage to return to the valley voltage of the triangular ramp. At the end of the off time the PWM latch is set and the cycle repeats again.

### **Under Voltage Lockout**

The under voltage lockout circuit of the AP2011 assures that the high-side P-MOSFET driver outputs remain in the off state whenever the supply voltage drops below set parameters. Lockout occurs if  $V_{\rm CC}$  falls below 6.5V. Normal operation resumes once  $V_{\rm CC}$  rises above 6.8V.

#### R<sub>DS(ON)</sub> Current Limiting

The current limit threshold is set by connecting an external resistor from the V<sub>CC</sub> supply to OCSET. The voltage drop across this resistor is due to the 70uA internal sink sets the voltage at the pin. This voltage is compared to the voltage at the PHASE node. This comparison is made only when the high-side drive is high to avoid false current limit triggering due to uncontributing measurements from the MOSFETs off-voltage. When the voltage at PHASE is less than the voltage at OCSET, an overcurrent condition occurs and the soft start cycle is initiated. The synchronous switch turns on and SS/SHDN starts to sink 2uA. When SS/SHDN reaches 0.2V, it then starts to source 10uA and a new cycle begins. When the soft start voltage is below 0.9V the cycle is controlled with pulse by pulse current limiting.

#### Soft Start

Initially, SS/SHDN sources 10uA of current to charge an external capacitor. The inverting input of the error comparator is clamped to a voltage proportional to the voltage on SS/SHDN. This limits the on-time of the high-side P-MOSFET, thus leading to a controlled ramp-up of the output voltages.

**AP2011**

### **■** Function Description

#### **Hiccup Mode**

During power up, the SS/SHDN pin is internally pulled low until  $V_{\text{CC}}$  reaches the under-voltage lockout level of 6.8V. Once  $V_{\text{CC}}$  has reached 6.8V, the SS/SHDN pin is released and begins to source 10uA of current to the external soft-start capacitor. As the soft-start voltage rises, the inverting input of the error comparator is clamped to this voltage. When the error signal reaches the level of the internal 1.25V reference, the output voltage is to have reached its programmed voltage. If an over-current condition has not occurred the soft-start voltage will continue to rise and level off at about 2.4V.

An over-current condition occurs when the high-side drive is turned on, but the PHASE node does not reach the voltage level set at the OCSET pin. Once

an over-current occurs, the high-side drive is turned off <u>and the</u> low-side drive turns on and the SS/SHDN pin begins to sink 2uA. The soft-start voltage will begin to decrease as the 2uA of current discharge the external capacitor. When the soft-start voltage reaches 0.2V, the SS/SHDN pin will begin to source 10uA and begin to charge the external capacitor causing the soft-start voltage to rise again. If the over-current condition is no longer present, normal operation will continue. If the over-current condition is still present, the SS/SHDN pin will again begin to sink 2uA. This cycle will continue indefinitely until the over-current condition is removed.

In order to prevent substrate glitching, a small-signal diode should be placed in close proximity to the chip with cathode connected to PHASE and anode connected to GND.

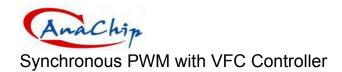

## ■ Marking Information

**AP2011**

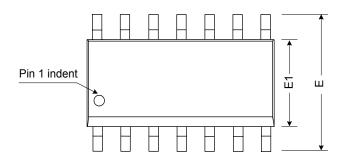

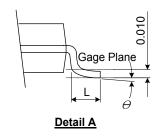

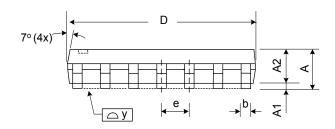

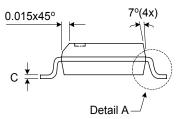

## ■ Package Information

Package Type: SOP-14L

| Cymbol | Dimensions In Millimeters |      |                | Dimensions In Inches |       |        |

|--------|---------------------------|------|----------------|----------------------|-------|--------|

| Symbol | Min.                      | Nom. | Max.           | Min.                 | Nom.  | Max.   |

| Α      | 1.47                      | 1.60 | 1.730          | 0.0580               | 0.063 | 0.0680 |

| A1     | 0.10                      | -    | 0.250          | 0.0040               | -     | 0.0100 |

| A2     | -                         | 1.45 | -              | -                    | 0.057 | -      |

| b      | 0.33                      | 0.41 | 0.510          | 0.0130               | 0.016 | 0.0200 |

| С      | 0.19                      | 0.20 | 0.250          | 0.0075               | 0.008 | 0.0098 |

| D      | 8.53                      | 8.64 | 8.740          | 0.3360               | 0.340 | 0.3440 |

| Е      | 5.80                      | 6.00 | 6.200          | 0.2283               | 0.236 | 0.2441 |

| E1     | 3.80                      | 3.90 | 3.990          | 0.1496               | 0.153 | 0.1571 |

| е      | -                         | 1.27 | -              | -                    | 0.050 | -      |

| L      | 0.38                      | 0.71 | 1.270          | 0.0150               | 0.028 | 0.0500 |

| Y      | -                         | -    | 0.076          | -                    | -     | 0.0030 |

| θ      | 0°                        | -    | 8 <sup>O</sup> | 0°                   | -     | 8°     |