# LatticeXP™ Standard Evaluation Board

User's Guide

#### Introduction

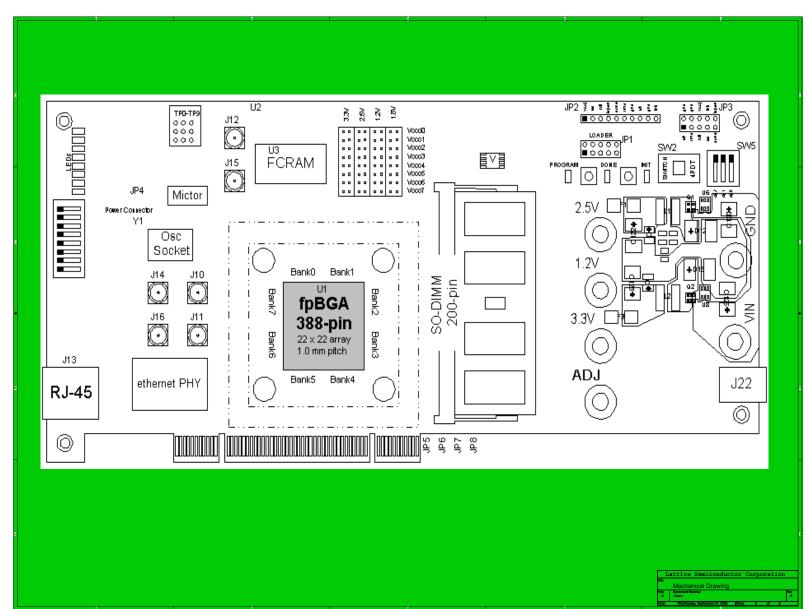

tary and ON/OFF), LEDs, SMA pads, RJ45, 0.10" headers and PCB test points and I/O connections. The LatticeXP I/Os are connected to a rich variety of interfaces including switches (momen-The board consists of a LatticeXP-10 FPGA in a 256 fpBGA package, power input jacks, a clock oscillator (33MHz) The LatticeXP Standard Evaluation Board provides a convenient platform to evaluate, test and debug user designs

The information in this document pertains to boards marked as 'Rev. A' and 'Rev. B'. This marking is located on the front of the board, beneath the Lattice logo. Any information that only applies to either the 'Rev. A' or 'Rev.B' board will be explicitly stated as such.

#### **Features**

#### Included

- LatticeXP FPGA: LFXP10C-5F256C or LFXP10E-5F256C

- On-board power supply (rev. B only)

- Prototyping area

- 188 user I/Os, grouped in eight I/O banks

- Independent voltage control for core, I/O and clock voltages

- 33MHz on-board oscillator

- Status LEDs, input switches

- Lattice ispDOWNLOAD cable

- AC adapter (rev. B only)

#### Optional

Optional SMA connectors (up to 16) for high-speed clock and data interfacing. The board includes pads for these connectors. The SMA connectors must be procured and installed separately by the user

#### Software Support

- about ispLEVER on the Lattice web site at: www.latticesemi.com/software To target your HDL design to the LatticeXP device, use the ispLEVER® design software. You can learn more

- downloaded from the Lattice web site at: www.latticesemi.com/ispvm. To download your program to the LatticeXP device, use the ispVM® System software. ispVM System can be

- $ispTRACY^{TM}$  in-system logic analysis support (ispTRACY is included with the ispLEVER design software)

Figure 1. LatticeXP Standard Evaluation Board

# Electrical, Mechanical and Environmental Specifications

The nominal board dimensions are 7 inches by 3.9 inches. The environmental specifications are as follows:

- Operating temperature: 0°C to 55°C

- Storage temperature: -40°C to 75°C

- Humidity: < 95% without condensation</li>

- VDC input (+/- 10%) up to 4A

### Additional Resources

software, sample designs, IP evaluation bitstreams, and more on the appropriate evaluation board, then follow the appropriate links for items such as updated documentation, Additional resources related to this board can be downloaded from the web at www.latticesemi.com/boards. Click

#### **LatticeXP Device**

Sheet on the Lattice web site at www.latticesemi.com. devices in the 256 fpBGA package. A complete description of this device can be found in the LatticeXP Family Data ticeXP-10 device in plastic 256-ball fpBGA (1mm pitch) package. Density migration is possible for Lattice XP This board features a LatticeXP FPGA with either a 3.3V or a 1.2V DC core. The board is populated with a Lat-

# **Device Core and I/O Voltage**

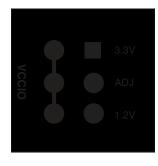

voltages. Boards shipping with a 1.2V core device will not have headers installed for core voltage selection. JP4 will Boards shipping with a 3.3V DC core device will allow operation of the core between 1.8V and 3.3V DC. Jumpers (JP4, JP5 and JP6) are available to switch between 3.3V, 1.2V and an adjustable supply between the other two be shorted on the board. Figure 2 shows the core voltage selection jumpers

Figure 2. Core Voltage Select Jumpers

allow each bank to be completely independent from the others. sysIO bank has its own I/O supply voltage (VCCIO) and two voltage reference resources, VREF1 and VREF2, that The LatticeXP device has eight syslO™ buffer banks; each is capable of supporting multiple I/O standards. Each

sheet can be downloaded from www.latticesemi.com. Please refer to the LatticeXP Family Data Sheet for additional information about supported I/O standards. This data

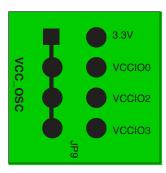

an adjustable voltage between these two voltages. Figure 3 shows a typical layout for a VCCIO select jumper block. VCCIO between 1.2V and 3.3V. The board provides jumper blocks which allow the end user to select 1.2V, 3.3V or The LatticeXP Standard Evaluation Board provides individual control of each I/O bank capable of supporting Table 1 details the VCCIO bank selection connectors.

Figure 3. VCCIO Jumper Block

Table 1. VCCIO Connectors

| JP14                    | VCCIO7     |

|-------------------------|------------|

| JP13                    | VCCIO6     |

| JP12                    | VCCIO5     |

| JP11                    | VCCIO4     |

| JP10                    | VCCIO3     |

| JP3                     | VCCIO2     |

| JP2                     | VCCIO1     |

| JP1                     | VCCIO0     |

| <b>Connector Number</b> | VCCIO Bank |

|                         |            |

#### **Device Clocks**

The LatticeXP Standard Evaluation Board provides a variety of ways to input clock signals to the LatticeXP device. These include an on-board crystal oscillator, SMA connectors and 0.1" header pins. Clock inputs connect to pri-

describes the clock connections to the LatticeXP device. mary clock inputs and device PLL inputs. Clock outputs connect to PLL outputs and external feedback pins. Table

Table 2. Lattice XP-10 Clock Pins and Connections

| -                           | 1477                                   | Connected to those pine     | Check the schematic pages for termination recitators composted to those pine | 1 Chack the schematic par |

|-----------------------------|----------------------------------------|-----------------------------|------------------------------------------------------------------------------|---------------------------|

| Z                           | N/A                                    | SMA 110                     | BCI KC8 0                                                                    | X                         |

| Z                           | N/A                                    | SMA J8                      | PCLKT6_0                                                                     | 조                         |

| Z                           | N/A                                    | Test Pad                    | PCLKC4_0                                                                     | T11                       |

| Z                           | N/A                                    | Test Pad                    | PCLKT4_0                                                                     | T10                       |

| Z                           | N/A                                    | 01-42L                      | PCLKC2_0                                                                     | J16                       |

| Z                           | N/A                                    | 6-42F                       | PCLKT2_0                                                                     | H16                       |

| Z                           | N/A                                    | Test Point                  | PCLKC0_0                                                                     | A8                        |

| Z                           | R104                                   | 080                         | PCLKT0_0                                                                     | A7                        |

| Z                           | N/A                                    | 6r yws                      | LUM0_PLLC_FB_A                                                               | D3                        |

| Ν                           | N/A                                    | 2r ams                      | LUM0_PLLT_FB_A                                                               | D2                        |

| Z                           | N/A                                    | 21r AMS                     | LUM0_PLLC_OUT_A                                                              | F4                        |

| Z                           | N/A                                    | <b>51</b> L AMS             | LUM0_PLLT_OUT_A                                                              | E3                        |

| Ν                           | N/A                                    | 12L AMS                     | LUM0_PLLC_IN_A                                                               | G2                        |

| Ν                           | N/A                                    | SMA J19                     | LUM0_PLLT_IN_A                                                               | G3                        |

| Z                           | N/A                                    | 22r yws                     | LLM0_PLLC_FB_A                                                               | M6                        |

| Z                           | N/A                                    | 02r yws                     | LLM0_PLLT_FB_A                                                               | L5                        |

| Ν                           | N/A                                    | SMA J18                     | LLM0_PLLC_OUT_A                                                              | K5                        |

| Z                           | N/A                                    | 91F YMS                     | LLM0_PLLT_OUT_A                                                              | K4                        |

| Ν                           | N/A                                    | SMA J14                     | LLM0_PLLC_IN_A                                                               | M2                        |

| Z                           | N/A                                    | 21L AMS                     | LLM0_PLLT_IN_A                                                               | M1                        |

| Z                           | N/A                                    | 4-42-L                      | RUM0_PLLC_FB_A                                                               | D15                       |

| Z                           | N/A                                    | J24-3                       | RUM0_PLLT_FB_A                                                               | C15                       |

| Z                           | N/A                                    | J24-18                      | RUM0_PLLC_OUT_A                                                              | G12                       |

| Z                           | N/A                                    | J24-17                      | RUM0_PLLT_OUT_A                                                              | F13                       |

| Z                           | N/A                                    | J24-8                       | RUM0_PLLC_IN_A                                                               | G16                       |

| ~                           | R90                                    | J24-7                       | RUM0_PLLT_IN_A                                                               | F16                       |

| Z                           | N/A                                    | J23-18                      | RLM0_PLLC_FB_A                                                               | P15                       |

| Z                           | N/A                                    | J23-17                      | RLM0_PLLT_FB_A                                                               | N15                       |

| Z                           | N/A                                    | J23-10                      | RLM0_PLLC_OUT_A                                                              | M14                       |

| Z                           | N/A                                    | J23-9                       | RLM0_PLLT_OUT_A                                                              | L13                       |

| Z                           | N/A                                    | J23-16                      | RLM0_PLLC_IN_A                                                               | M16                       |

| ~                           | R89                                    | J23-15                      | RLM0_PLLT_IN_A                                                               | N16                       |

| Buffered (Y/N) <sup>3</sup> | On-Board OSC.<br>Resistor <sup>2</sup> | PCB Connection <sup>1</sup> | XP Pin Label                                                                 | XP-10 Pin Number          |

Check the schematic pages for termination resistors connected to these pins.

0\_ resistor connecting to on-board oscillator.

The oscillator socket accepts both full-size and half-size oscillators and can route to different clock inputs, depending on installation of several 0Ω resistors. The oscillator has a 22Ω series termination resistor at the oscillator output. These inputs correspond with PCLKT0, RLM0\_PLLT\_IN\_A and RUM0\_PLLT\_IN\_A. The oscillator supply voltage is changeable, via the VCC\_OSC header, located at JP9. The onboard oscillator operates at 3.3V. It is possible to power this socket from the following supplies: 3.3V, VCCIO0, VCCIO2 or VCCIO3, depending on the I/O bank being used and the operating conditions for the chosen oscillator.

Indicates a non-inverting buffer between the oscillator and pin.

Figure 4 shows the layout and connections for JP9. There is also an optional 10K pull-up (R91) connect to pins 1 and 4 of the oscillator socket, in the event a oscillator with enable is required. The oscillator is also connected to J24-26, for use as a clock input to a logic analyzer.

Figure 4. VCC\_OSC Jumper Block

# Device I/O Banks 0 and 1

tions. Unlisted pins in banks 0 and 1 are connected to test pads on the board. nected to GND when activated (pushed or levered in the down position). LEDs are active (lit) when the device I/O is low. The RJ-45 connector is connected using paired I/O connections. Table 3 details the I/O banks 0 and 1 connector. LEDs and an RJ45 connector. The switches consist of two user defined push-button switches and an 8-position DIP switch. Both types of switches are pulled up to the associated VCCIO voltage with 10KΩ resistors and con-I/O banks 0 and 1 represent general purpose I/O banks, which connect to a combination of test pads, switches,

Table 3. Banks 0 and 1 I/O Connections

|                |                |              |              |              |              |              |              |              |              |             |             |             |             |             |             |             |             |         |         |         |         |         |         |        |        | 5                   |

|----------------|----------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------------------|

| _              | 1              | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0       | 0       | 0       | 0       | 0       | 0       | 0      | 0      | Bank                |

| 69             | 80             | E9           | B8           | B7           | C7           | E8           | D8           | A6           | 60           | F7          | D7          | A5          | B5          | A4          | B6          | B3          | D6          | D5      | А3      | В3      | B2      | A2      | B1      | F5     | C5     | XP-10 Pin<br>Number |

| Pushbutton SW1 | Pushbutton SW0 | Switch SW7 8 | Switch SW7 7 | Switch SW7 6 | Switch SW7 5 | Switch SW7 4 | Switch SW7 3 | Switch SW7 2 | Switch SW7 1 | RJ-45 J25-8 | RJ-45 J25-7 | RJ-45 J25-6 | RJ-45 J25-5 | RJ-45 J25-4 | RJ-45 J25-3 | RJ-45 J25-2 | RJ-45 J25-1 | LED D15 | LED D14 | LED D13 | LED D12 | LED D11 | LED D10 | LED D9 | LED D8 | Connection          |

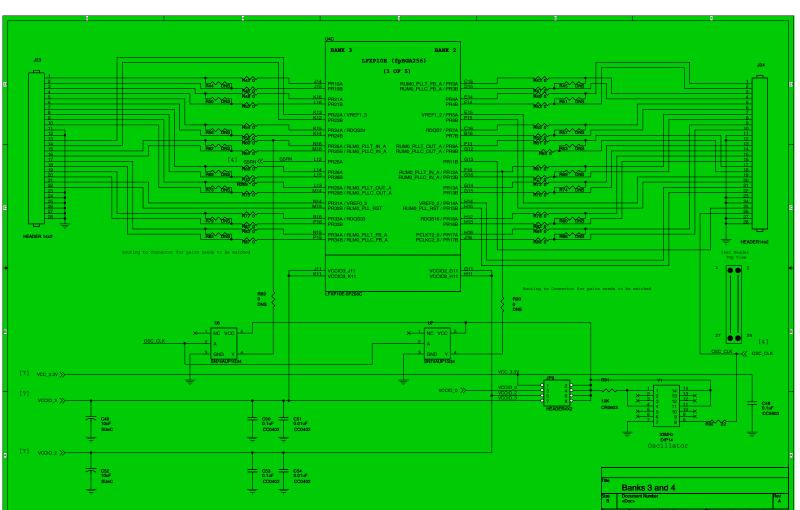

# Device I/O Banks 2 and 3

I/O banks 2 and 3 contain general purpose I/Os with LVDS transmit/receive pairs. These I/O pairs are connected to two 0.1" headers suitable for connecting to a logic analyzer or ribbon cable. Table 4 details the I/O banks 2 and 3 connections.

Table 4. Banks 2 and 3 I/O Connections

| 1                       |

|-------------------------|

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

| _atticeXP-10 Pin Number |

<sup>1.</sup> Blank cell indicated pin with no negative paired pin.

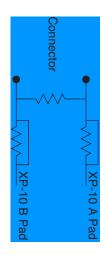

series resistors are 0805 size and the parallel resistors are 0603 size. Figure 5 shows this trace in relation to the the termination network for these differential pairs. These resistors are not installed, and the series resistors use a trace between the resistor pads. This trace can be cut to allow the installation of a series termination resistor. The resistor pads. Each I/O pair is connected to a resistor termination network, and the trace lengths are matched. Figure 5 shows

Figure 5. Differential I/O Termination Network

Figure 6. Close-up of Series/Passthrough

# Device I/O Banks 4 and 5

connected to a pull-up, pull-down and series resistor network. The resistor network is not populated. The series resistors are 0805 size, and the pull-up/pull-down resistors are 0603 size. Figure 7 shows the schematic for the I/O banks 4 and 5 consist of general purpose I/O pins. These pins connect to test pads on the board. The test pads are paired with a ground pad, which are spaced on 0.1" centers. In addition to the test pads, these I/O banks are individual I/O termination network.

Table 5. Banks 4 and 5 I/O Connections

| Position | Pin Number | <b>GND Row</b> | Pin Number | GND Row |

|----------|------------|----------------|------------|---------|

| 1        | Т3         | GND            | P5         | GND     |

| N        | R3         | GND            | R1         | GND     |

| ω        | N5         | GND            | R2         | GND     |

| 4        | R4         | GND            | Т2         | GND     |

| បា       | Т5         | GND            | R5         | GND     |

| 6        | P6         | GND            | Т4         | GND     |

| 7        | N6         | GND            | Т6         | GND     |

| 8        | M7         | GND            | R6         | GND     |

| 9        | N7         | GND            | T8         | GND     |

| 10       | M8         | GND            | P8         | GND     |

| 11       | R8         | GND            | N8         | GND     |

| 12       | T9         | GND            | P7         | GND     |

| 13       | 77         | GND            | R9         | GND     |

| 14       | R7         | GND            | P9         | GND     |

| 15       | T11        | GND            | 9N         | GND     |

| 16       | T10        | GND            | M9         | GND     |

| 17       | P13        | GND            | T13        | GND     |

| 18       | R13        | GND            | P14        | GND     |

| 19       | M11        | GND            | N10        | GND     |

| 20       | N11        | GND            | M10        | GND     |

| 21       | R10        | GND            | P11        | GND     |

| 22       | P10        | GND            | N12        | GND     |

| 23       | R12        | GND            | R11        | GND     |

| 24       | T12        | GND            | P12        | GND     |

| 25       | T15        | GND            | T14        | GND     |

| 26       | R15        | GND            | R14        | GND     |

|          |            |                |            |         |

Figure 7. Banks 4 and 5 I/O Termination Network

# Device I/O Banks 6 and 7

I/O bank 6 and 7 SMA connections. Unlisted pins are connected to test pads on the board. I/O banks 6 and 7 contain general purpose I/Os with LVDS transmit/receive pairs. The I/O pairs in these banks have been routed to test pads on the PCB and eight pairs have been routed to SMA connectors. Table 6 details the

Table 6. Bank 6 and 7 I/O Connections

| I/O Bank | Positive             | Negative <sup>1</sup> | Positive                             | Negative <sup>1</sup>                                                                                                                                                                                                     |

|----------|----------------------|-----------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | K1                   | K2                    | 38<br>8                              | J10                                                                                                                                                                                                                       |

| 6        | M1                   | M2                    | J12                                  | J14                                                                                                                                                                                                                       |

| 6        | К4                   | K5                    | J16                                  | J18                                                                                                                                                                                                                       |

| 6        | L5                   | M6                    | J20                                  | J22                                                                                                                                                                                                                       |

| 7        | D2                   | D3                    | J7                                   | 9                                                                                                                                                                                                                         |

| 7        | 펀                    | F1                    | J11                                  | J13                                                                                                                                                                                                                       |

| 7        | E3                   | F4                    | J15                                  | J17                                                                                                                                                                                                                       |

| 7        | G3                   | G2                    | J19                                  | J21                                                                                                                                                                                                                       |

|          | 1/O Bank 6 6 7 7 7 7 |                       | Fositive  K1  M1  K4  L5  D2  E1  E3 | Positive         Negative           K1         K2           M1         M2           K4         K5           L5         M6           D2         D3           E1         F1           E3         F4           G3         G2 |

Pairs routed to SMA connectors are connected with series and parallel termination resistors, similar to the network shown in Figure 5 (see Bank 2 and 3 description). The SMA connectors are not included with the LatticeXP-Standard board, and must be procured and installed separately. AMP SMA connector 221780-1 or similar is recom-

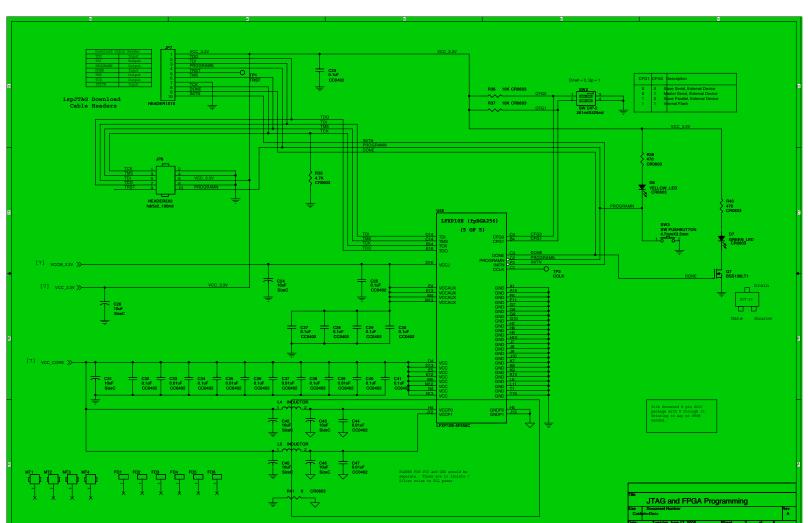

## **Programming Headers**

the headers are provided in Tables 6 and 7. Two programming headers are provided on the evaluation board, providing access to the LatticeXP JTAG port. Both 1x10 and 2x5 formats are available for compatibility with all Lattice ispDOWNLOAD® cables. The pinouts for

Important Note: The board must be un-powered when connecting, disconnecting, or reconnecting the ispDOWN-LOAD Cable. Always connect the ispDOWNLOAD Cable's GND pin (black wire), before connecting any other JTAG pins. Failure to follow these procedures can in result in damage to the LatticeXP FPGA device and render the board inoperable.

Table 7. JTAG Programming Headers Function JP8 (2x5)

| PROGRAM | TRST | GND | TDO | VCC (3.3V) | TDI | GND | TMS | GND | TCK | JTAG Programming Function |

|---------|------|-----|-----|------------|-----|-----|-----|-----|-----|---------------------------|

| 10      | 9    | 8   | 7   | 6          | 5   | 4   | 3   | 2   | 1   | JP8 Pin Number (2x5)      |

Table 8. JTAG Programming Headers Function JP7 (1x10)

| INIT | DONE | TCK | GND | TMS | TRST | PROGRAM | TDI | TDO | VCC (3.3V) | JTAG Programming Function |

|------|------|-----|-----|-----|------|---------|-----|-----|------------|---------------------------|

| 10   | 9    | 8   | 7   | 6   | 5    | 4       | 3   | 2   | 1          | JP7 Pin Number (1x10)     |

#### **Power Supply**

Power can be supplied to the LatticeXP Standard Evaluation Board via the banana jacks (J1, 2, 5, 6 - all PCB revisions), or a coaxial DC connector (J3 – Rev. B PCB only), which receive power from either a bench power supply or a brick style power supply.

when the switch is in the left position. [Rev. B Only] The output from the DC system is controlled by switch SW1. This is a small surface mount switch that enables and disables the LTC1775 DC-DC conversion chip. The output voltages from the power supply are enabled

[Rev. B Only] The 5.0V to 28.0V DC input voltage (input to either J2 or J3) is converted by DC-DC converters and switching power supplies to provide 3.3V, 1.2V, and an adjustable DC source on the board. The output from these

#### Lattice Semiconductor

supplies travels through surface mounted fuse holders. Fuses are supplied and prevent over-current conditions from damaging the components on the board (vendor: Littlefuse, make: Nano SMF Very Fast Acting, 1.5A or 3A).

Adjustable rail. J2 connects to the VIN input of the on-board power supply of the Rev. B board. J2 is unconnected on the Rev. A board. To directly connect power to the banana jacks on the Rev. B board, the SMT fuses must be boards, J4 is the GROUND connection point, J1 is the +3.3V input, J6 is the +1.2V input and J5 is the input for the Both Rev. A and Rev. B boards may be supplied with DC voltage through the banana plug connector. On both removed. SMT fuses are not installed on Rev. A boards.

#### **Ordering Information**

| Description                                                               | Ordering Part Number | China RoHS Environment-<br>Friendly Use Period (EFUP) |

|---------------------------------------------------------------------------|----------------------|-------------------------------------------------------|

| LatticeXP10C Evaluation Board - Standard (upper voltage)                  | LFXP10C-L-EV         |                                                       |

| LatticeXP10C Evaluation Board - Standard (lower voltage)                  | LFXP10E-L-EV         |                                                       |

| ispLEVER Base with LatticeXP10 Standard Development Kit LS-XP10-BASE-PC-N | LS-XP10-BASE-PC-N    |                                                       |

|                                                                           |                      |                                                       |

# **Technical Support Assistance**

Hotline: 1-800-LATTICE (North America)

+1-503-268-8001 (Outside North America)

e-mail: techsupport@latticesemi.com

Internet: www.latticesemi.com

#### Revision History

| June 2008          | April 2007                                                                             | March 2007                          | August 2006                                                       | 1                          | Date           |

|--------------------|----------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------|----------------------------|----------------|

| 02.4               | 02.3                                                                                   | 02.2                                | 02.1                                                              | l                          | Version        |

| Updated schematic. | Added important information for proper connection of ispDOWNLOAD (Programming) Cables. | Added Ordering Information section. | Changes to I/O Bank column of Bank 6 and 7 I/O Connections table. | Previous Lattice releases. | Change Summary |

© 2008 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="https://www.latticesemi.com/legal">www.latticesemi.com/legal</a>. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

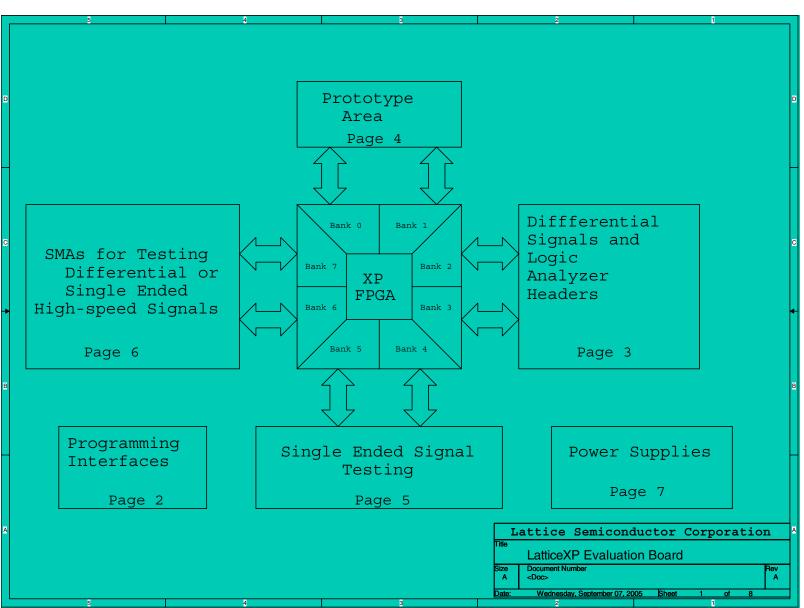

## Appendix A. Schematic

Figure 8. LatticeXP Evaluation Board

Figure 9. JTAG and FPGA Programming

Figure 10. Banks 3 and 4

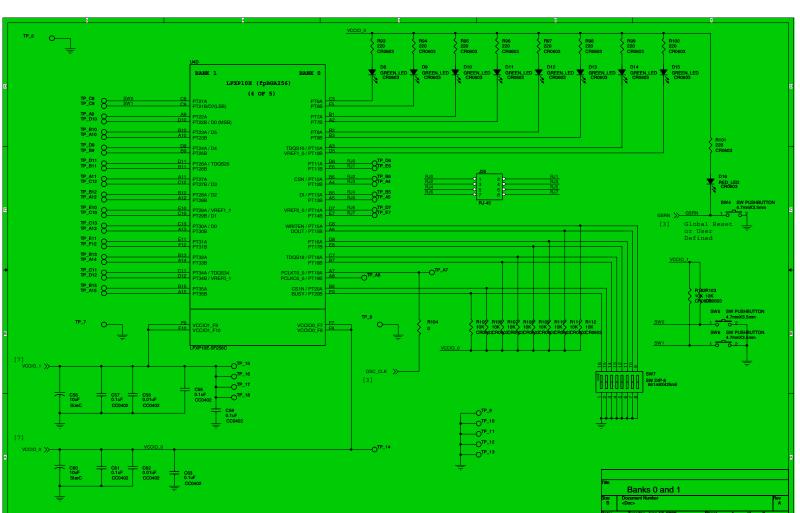

Figure 11. Banks 0 and 1

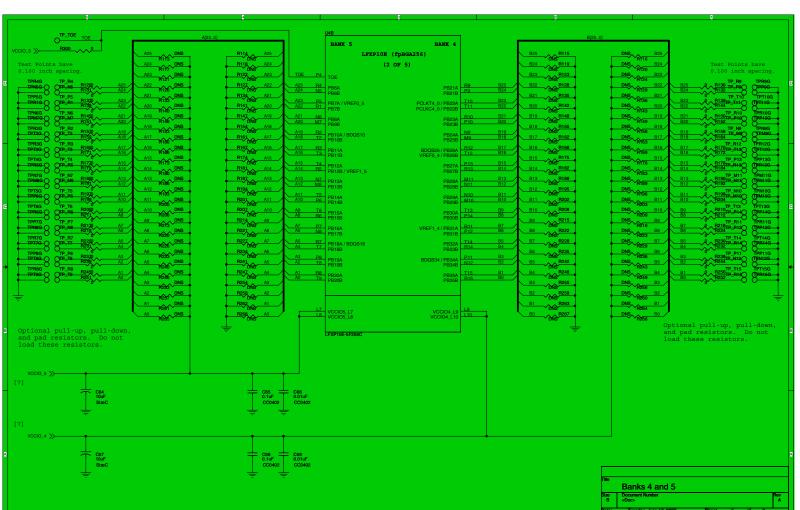

Figure 12. Banks 4 and 5

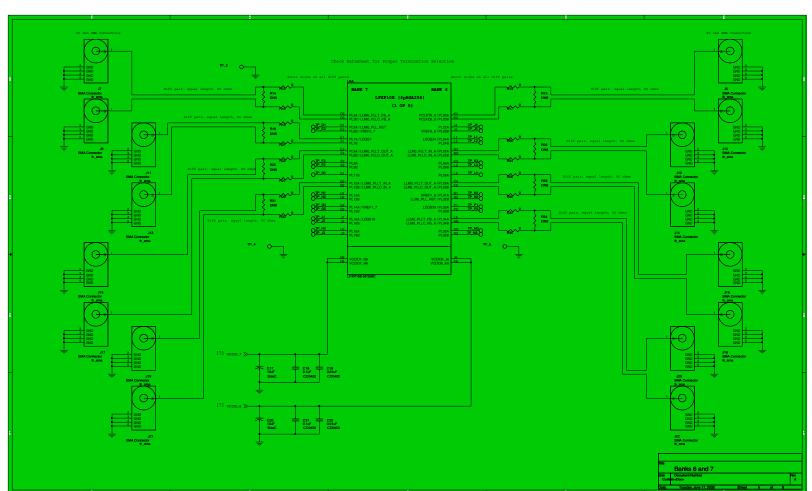

Figure 13. Banks 6 and 7

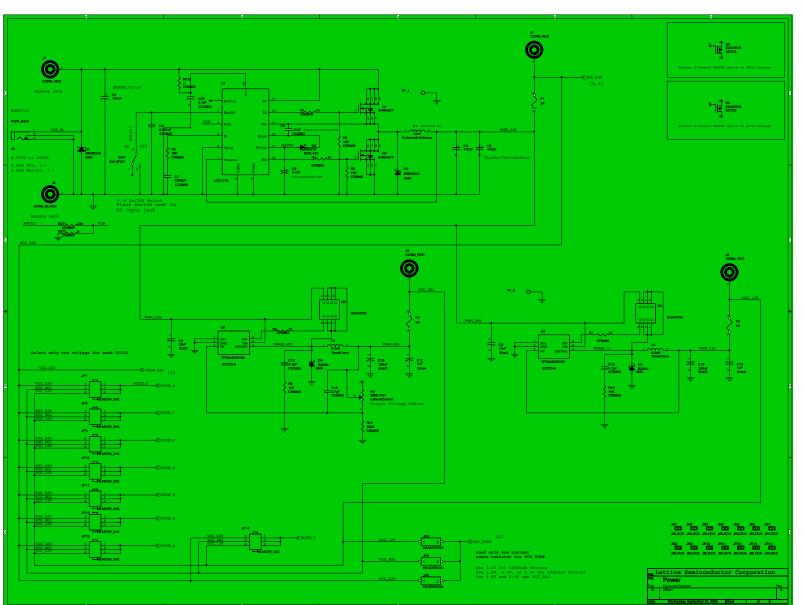

Figure 14. Power

Figure 15. Mechanical Drawing