# Audio, Power Management and Control

**Preliminary Datasheet**

## **OVERVIEW**

The **P95020** is designed to provide maximum flexibility to system designers by providing full customization and programmability. It is the first of a new generation of standardized application-specific controllers that incorporates a general purpose microcontroller, a high fidelity audio CODEC including headphone outputs and a 2.5W Class D audio amplifier, full power management functionality, a touch screen controller and a real time clock all of which are required by portable consumer devices such as cellular phone handsets, portable gaming devices, digital media players, portable navigational devices, etc.

The general purpose microcontroller controls the device power-on/power-off sequencing and can also be used for general system housekeeping.

The P95020 includes two I<sup>2</sup>C Interfaces, a master for communicating with an external EEPROM and a slave for communicating with the host.

The high fidelity audio CODEC along with headphone outputs and the 2.5 watt Class D audio speaker amplifier comprise a total audio solution for portable applications.

The switch-mode EnergyPath™ Battery Charger operates with its own high efficiency buck regulator to transmit the 2.5 watts available from a USB port to the system with minimal wasted power. It can also handle up to 2A from a wall charger.

Its power management features along with switch-mode converters and LDOs should be sufficient to provide power for even the most complex hand-held devices.

The integrated touch screen controller allows adding touch screen capability to devices at significantly reduced cost.

It also includes IDT's high quality, low power real time clock.

# **APPLICATIONS**

Smart Phones

Portable Gaming Device

Digital Media Players

Portable Navigational Devices

## **KEY FEATURES**

# **Quick Turn Customization Embedded Microcontroller**

- Master Controller during Power Up & Power-Down

- · Initialization and power sequencing

- Dynamic Power Management via I<sup>2</sup>C bus interface

- Up to 10 General Purpose I/Os available

- General house keeping for P95020 and other devices

#### **Audio Features**

- 4 Channel CODEC with 24-bit resolution and internal registers for status and control

- Integrated 2.5 Watt Mono Class D Amplifier with Filterless Operation.

- Stereo cap-less headphone driver

- Differential Analog Audio Line Inputs

- Dual Mode Microphone Inputs (Analog or DMIC)

#### **Battery Charging Circuit**

- Autonomous Li-Ion/Li-Poly charger up to 1.5A

- · Automatic Load Prioritization

- Advanced Battery Safety features

- High efficiency switch-mode \*EnergyPath™ controller

- USB or Wall-mounted Charging

- Programmable Current Limit

- Automatic end-of-charge control

- Internal 180 mΩ ideal diode with external ideal diode controller

#### **Power Management Features**

- All Converters:

- Power up/down sequence field reprogrammable with external EEPROM

- Dynamic voltage scaling

- Host or I2C output enable / disable

- Buck DC-DC PWM converters with PFM mode

- Two at 500mA, 0.75V to 3.7V

- One at 1000mA, 0.75V to 3.7V

- Boost DC-DC converters

- One at 1.5 A peak on inductor, 4.05V to 5.0V

- One LED supply with 2 W total output power

- Two programmable current sinks, @ 25mA each

- Voltage limited to rating of external FET & diode

- Linear Regulators

- Three LDOs at 150mA, 0.75V to 3.7V

- Four LDOs at 50mA, 0.7V to 3.7V

- One always-on LDO at 10mA, 3.3 or 3.0V

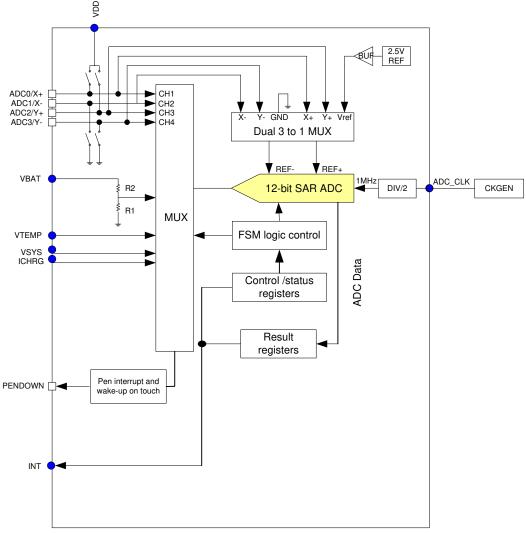

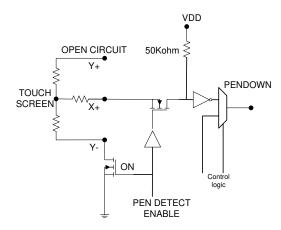

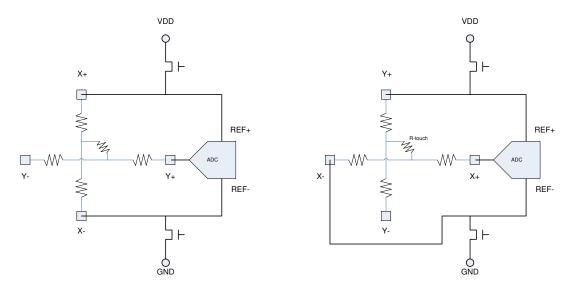

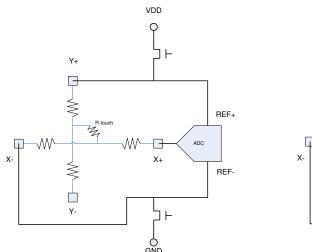

#### **ADC and Touch Screen Controller**

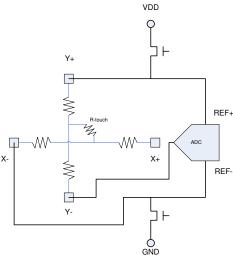

- 4-wire touch screen interface

- One direct battery measurement channel

- One direct VSYS measurement channel

- One direct charge current measurement channel

- On-Chip temperature measurement

- Four auxiliary analog input channels (shared with GPIO pins)

- Touch pressure measurement

- Sample rate: 62.5k SPS

- 12 bit resolution, DNL: -1~+2 LSB, INL: +-2

- On-chip 2.5V reference

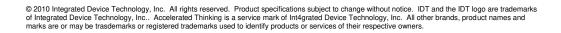

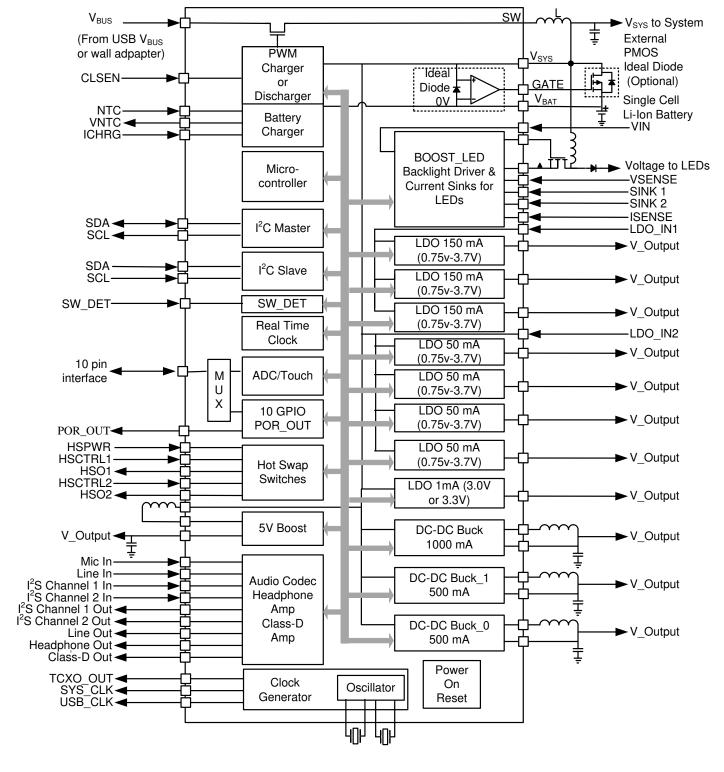

# **BLOCK DIAGRAM**

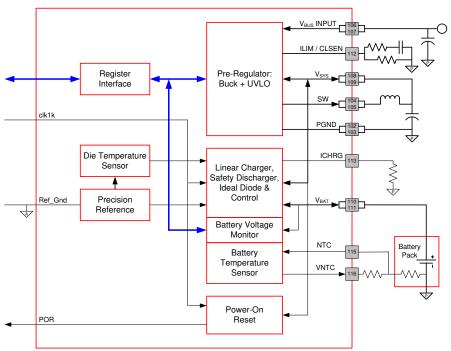

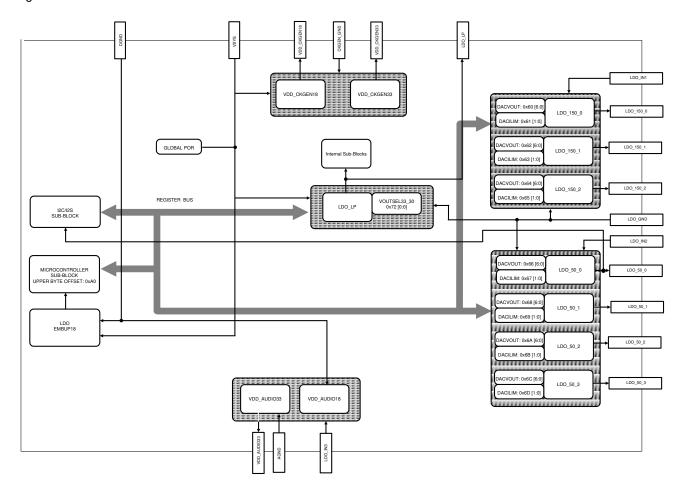

Figure 1 – P95020 Block Diagram.

# **TABLE OF CONTENTS**

|              | /IEW                                                          |    |

|--------------|---------------------------------------------------------------|----|

|              | CATIONS                                                       |    |

|              | EATURES                                                       |    |

|              | DIAGRAM                                                       |    |

|              | SIGNMENTS                                                     |    |

| PIN FU       | NCTIONS BY PIN NUMBER                                         | 9  |

| I/O LEV      | /ELS BY TYPE                                                  | 14 |

| <b>ABSOL</b> | UTE MAXIMUM RATINGS                                           | 15 |

| RECON        | MENDED OPERATING CONDITIONS                                   | 16 |

| DIGITA       | L INTERFACES - DC ELECTRICAL CHARACTERISTICS                  | 16 |

|              | STER - ELECTRICAL CHARACTERISTICS                             |    |

|              | AVE - ELECTRICAL CHARACTERISTICS                              |    |

|              | ECTRICAL CHARACTERISTICS                                      |    |

|              | ELECTRICAL CHARACTERISTICS                                    |    |

|              | POWER CONSUMPTION                                             |    |

| 1.0          | OVERVIEW                                                      |    |

| 1.1          | FUNCTIONAL MODES                                              | 10 |

| 1.2          | REGISTER MAP                                                  |    |

| 1.3          | BYTE ORDERING AND OFFSET                                      |    |

|              |                                                               |    |

| 1.4          | REGISTER ACCESS TYPES                                         |    |

| 1.5          | RESERVED BIT FIELDS                                           |    |

| 2.0          | AUDIO MODULE                                                  |    |

| 2.1          | AUDIO - PIN DEFINITIONS                                       |    |

| 2.2          | AUDIO - SECTION OVERVIEW                                      |    |

| 2.3          | AUDIO - ANALOG PERFORMANCE CHARACTERISTICS                    |    |

| 2.4          | AUDIO - MICROPHONE INPUT PORT                                 |    |

| 2.5          | AUDIO - ANALOG LINE INPUT                                     |    |

| 2.6          | AUDIO - DAC, ADC                                              |    |

| 2.7          | AUDIO - AUTOMATIC GAIN CONTROL                                |    |

| 2.8          | AUDIO - ANALOG MIXER BLOCK                                    |    |

| 2.9          | AUDIO - DIGITAL AUDIO INPUT/OUTPUT INTERFACE                  |    |

| 2.10         | AUDIO - REFERENCE VOLTAGE GENERATOR, BUFFER, & FILTERING CAPS | 31 |

| 2.11         | AUDIO - ANALOG AND CLASS D OUTPUT BLOCK                       | 31 |

| 2.12         | AUDIO - CLASS-D BTL AMPLIFIER                                 | 32 |

| 2.13         | AUDIO CLASS D - REGISTERS                                     | 32 |

| 2.14         | AUDIO CLASS D - EQUALIZER COEFFICIENT & PRESCALER RAM (EQRAM) | 39 |

| 2.15         | AUDIO – AUDIO CONTROL REGISTERS                               |    |

| 3.0          | CHARGER MODULE                                                |    |

| 3.1          | CHARGER - OVERVIEW                                            |    |

| _            | CHARGER – SUB-BLOCKS                                          |    |

| 3.3          | CHARGER – DC ELECTRICAL CHARACTERISTICS                       | 53 |

| 3.4          | CHARGER – TYPICAL PERFORMANCE CHARACTERISTICS                 |    |

|              | CHARGER - REGISTER ADDRESSES                                  |    |

| 3.6          | CHARGER - PRE-REGULATOR                                       |    |

|              | IDEAL DIODE FROM V <sub>BAT</sub> TO V <sub>SYS</sub>         |    |

| 3.8          | CHARGER - CHARGER/DISCHARGER                                  |    |

|              | CHARGER - THERMAL MONITORING                                  |    |

| 3.9          | CHARGER - THERMAL MONTORING                                   |    |

| 3.10         |                                                               |    |

| 4.0          | CLOCK GENERATOR MODULE                                        |    |

| 4.1          | CKGEN - PIN DEFINITIONS                                       | 61 |

| 4.2          | CKGEN - OSCILLATOR CIRCUIT ELECTRICAL CHARACTERISTICS         |    |

| 4.3          | CKGEN - PLL CONTROL                                           | 63 |

| 4.4          | CKGEN - OSCILLATOR CIRCUIT                                    |    |

| 4.5          | CKGEN - CKGEN POWER SOURCE                                    |    |

| 4.6          | CKGEN – CLOCK ACCURACY                                        | 63 |

| 4.7          | CKGEN – CLOCK GENERATOR REGISTERS                             | 64 |

| 5.0          | RTC MODULE                                                 |             |

|--------------|------------------------------------------------------------|-------------|

| 5.1          | RTC - GENERAL DESCRIPTION                                  | 66          |

| 5.2          | RTC - TIMEKEEPER REGISTERS                                 | 67          |

| 5.3          | RTC - DATE REGISTERS                                       |             |

| 5.4          | RTC - ALARM REGISTERS                                      |             |

| 5.5          | RTC - INTERRUPT REGISTERS                                  |             |

| 5.6          | RTC RESERVED REGISTERS                                     |             |

| 6.0          | GENERAL PURPOSE TIMERS                                     | 71          |

| 6.1          | GENERAL PURPOSE TIMERS – GENERAL DESCRIPTION               |             |

| 6.2          | GENERAL PURPOSE TIMERS – REGISTERS                         |             |

| 7.0          | DC_DC MODULE                                               |             |

| 8.0          | 2MHz, 500mA & 1000mA SYNCHRONOUS BUCK REGULATORS           |             |

| 8.1          | BUCK1000 & BUCK500 - PIN DEFINITIONS                       | 76          |

| 8.2          | BUCK1000 & BUCK500 - ELECTRICAL CHARACTERISTICS            |             |

| 8.3          | BUCK CONVERTERS – TYPICAL PERFORMANCE CHARACTERISTICS      |             |

| 8.4          | BUCK1000 & BUCK500 - REGISTER ADDRESSES                    |             |

| 8.5          | BUCK1000 & BUCK500 - ENABLING & DISABLING                  |             |

| 8.6          | BUCK1000 & BUCK500 - APPLICATIONS INFORMATION              |             |

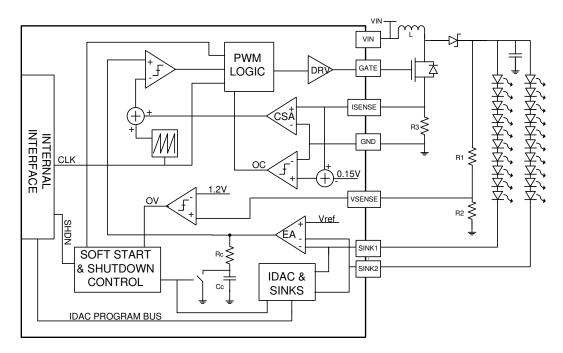

| 9.0          | HIGH EFFICIENCY 10 LED BOOST CONVERTER AND SINKS           |             |

| 9.1          | LED_BOOST - ELECTRICAL CHARACTERISTICS                     | 84          |

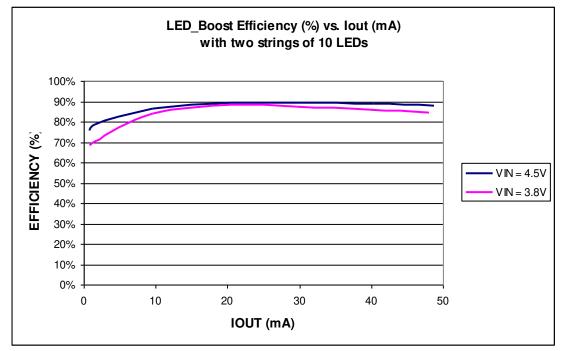

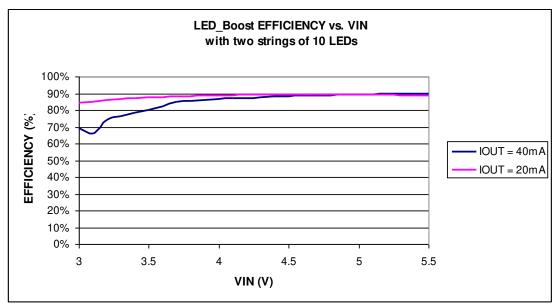

| 9.2          | LED_BOOST - TYPICAL PERFORMANCE CHARACTERISTICS            |             |

| 9.3          | LED_BOOST - REGISTER SETTINGS                              |             |

| 9.4          | LED_BOOST - ENABLING & DISABLING                           |             |

| 9.5          | LED_BOOST - Over-Voltage Protection                        |             |

| 9.6<br>9.7   | LED_BOOST – Over-Current Limiter                           |             |

| 9.7          | BOOST5 – 1.5A, SYNCHRONOUS PWM BOOST CONVERTER             |             |

| 10.0         | BOOSTS - ELECTRICAL CHARACTERISTICS                        |             |

| 10.1         |                                                            |             |

| 10.2         |                                                            |             |

| 10.4         |                                                            |             |

| 10.5         |                                                            |             |

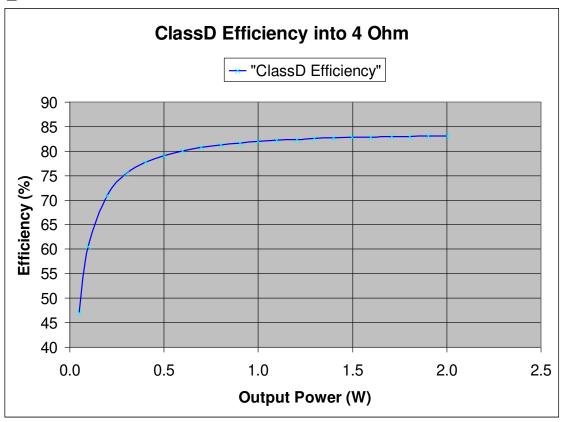

| 11.0         | CLASS D BTL POWER OUTPUT STAGE                             |             |

| 11.1         | CLASS D - ELECTRICAL CHARACTERISTICS                       |             |

| 11.2         | <del>-</del>                                               |             |

| 11.3         | CLASS D - REGISTER SETTINGS                                | 94          |

| 11.4         | CLASS D - AUDIO INTERFACE AND DECODE                       | 95          |

| 11.5         | CLASS_D - SHORT CIRCUIT PROTECTION CIRCUITRY               | 95          |

| 11.6         | CLASS_D - APPLICATIONS INFORMATION                         | 95          |

| 12.0         | TSC MODULE - ADC AND TOUCH SCREEN CONTROLLER               | 96          |

| 12.1         | ADC AND TOUCH SCREEN CONTROLLER ELECTRICAL CHARACTERISTICS |             |

| 12.2         |                                                            |             |

| 12.3         |                                                            |             |

| 12.4         |                                                            | 100         |

| 13.0         | PCON MODULE – POWER CONTROLLER AND GENERAL PURPOSE I/O     |             |

| 13.1         | GPIO PIN DEFINITIONS                                       |             |

| 13.2         | POWER STATES                                               | 107         |

| 13.3         |                                                            |             |

| 13.4         |                                                            | 108         |

| 13.5         |                                                            |             |

| 13.6         |                                                            |             |

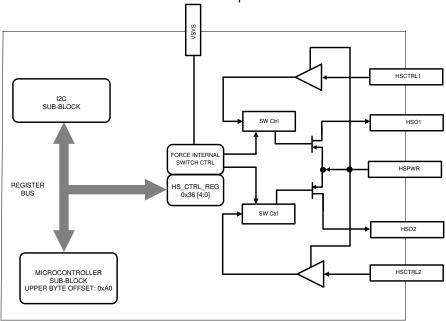

| 13.7         | HOTSWAP MODULE                                             |             |

| 14.0<br>14.1 | HOT SWAP (LOAD SWITCHES) – ELECTRICAL CHARACTERISTICS      |             |

| 14.1         |                                                            | ۱۱۵۱<br>۱۱۸ |

| 14.2         |                                                            |             |

| 14.4         |                                                            | 115         |

| 15.0         | I2C I2S MODULE                                             |             |

| 15.1         | I2C I2S - PIN DEFINITIONS                                  |             |

| 15.2         | <del>-</del>                                               |             |

| 15.3         |                                                            |             |

|              |                                                            |             |

| 15.4         |                                                                          | 117 |

|--------------|--------------------------------------------------------------------------|-----|

| 15.5         |                                                                          |     |

| 15.6         |                                                                          |     |

| 15.7         |                                                                          |     |

| 15.8         |                                                                          |     |

| 16.0         | LDO MODULE                                                               |     |

| 16.1         |                                                                          |     |

| 16.2         |                                                                          |     |

| 16.3         |                                                                          |     |

| 16.4         |                                                                          | 127 |

| 16.5         |                                                                          |     |

| 16.6         | LDO – REGISTER SETTINGS EMBUP – EMBEDDED MICROCONTROLLER SUBSYSTEM & I/O |     |

| 17.0<br>17.1 |                                                                          |     |

| 17.1         |                                                                          |     |

| 17.2         |                                                                          |     |

| 17.3         |                                                                          |     |

| 17.5         |                                                                          |     |

| 17.6         |                                                                          |     |

| 18.0         | APPLICATIONS INFORMATION                                                 |     |

| 18.1         |                                                                          |     |

| 18.2         |                                                                          |     |

| 18.3         |                                                                          |     |

| 18.4         |                                                                          |     |

| 18.5         |                                                                          |     |

| 18.6         |                                                                          |     |

| 18.7         |                                                                          |     |

| 18.8         |                                                                          |     |

| 18.9         |                                                                          |     |

| 18.10        | \ /                                                                      |     |

| 19.0         | SOLDERING PROFILE                                                        |     |

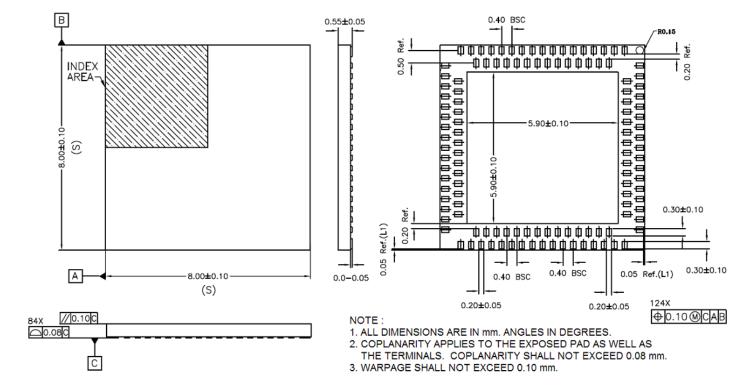

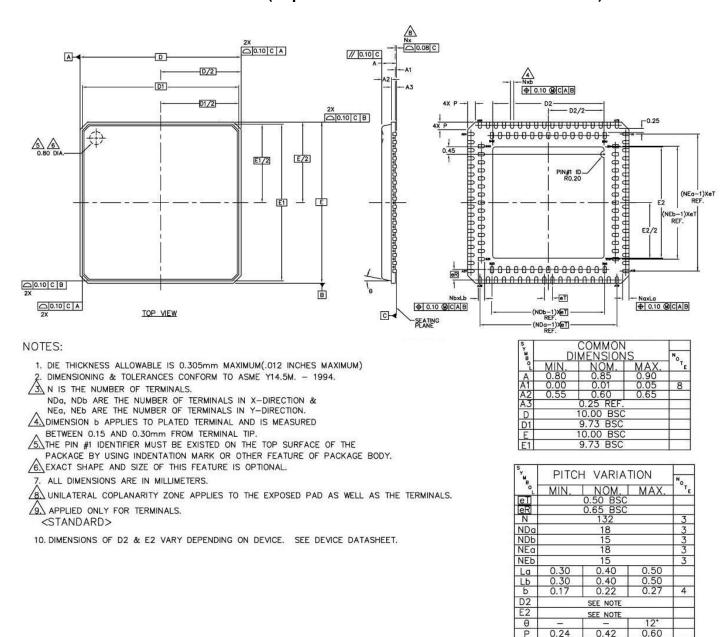

| 20.0         | PACKAGE OUTLINE DRAWING                                                  |     |

| 20.1         |                                                                          | 134 |

| 20.2<br>21.0 | ORDERING INFORMATION                                                     |     |

|              |                                                                          |     |

|              | TABLE OF FIGURES                                                         |     |

| Figure       | 1 – P95020 Block Diagram                                                 | 2   |

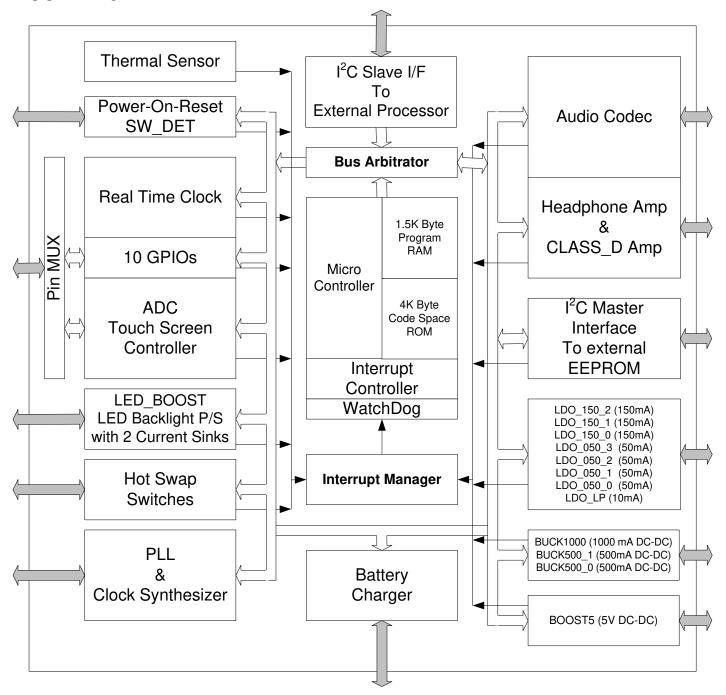

|              | 2 – P95020 Pinout Diagram (LLG124)                                       |     |

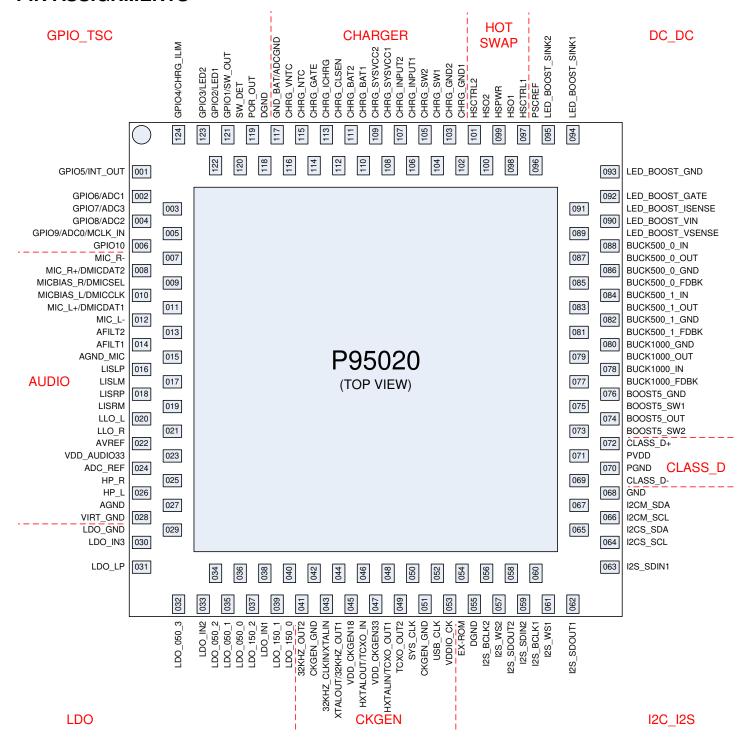

|              | 3 – P95020 Pinout (NGQ132)                                               |     |

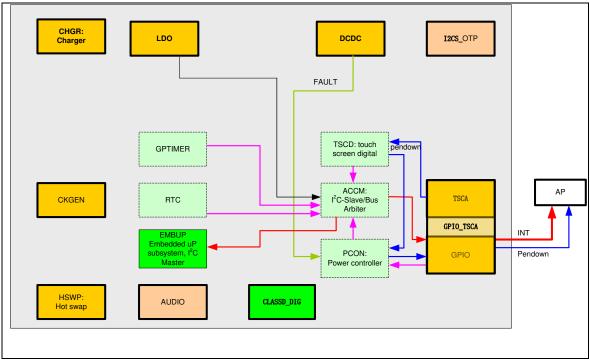

|              | 4 – Overall System Functional Diagram.                                   |     |

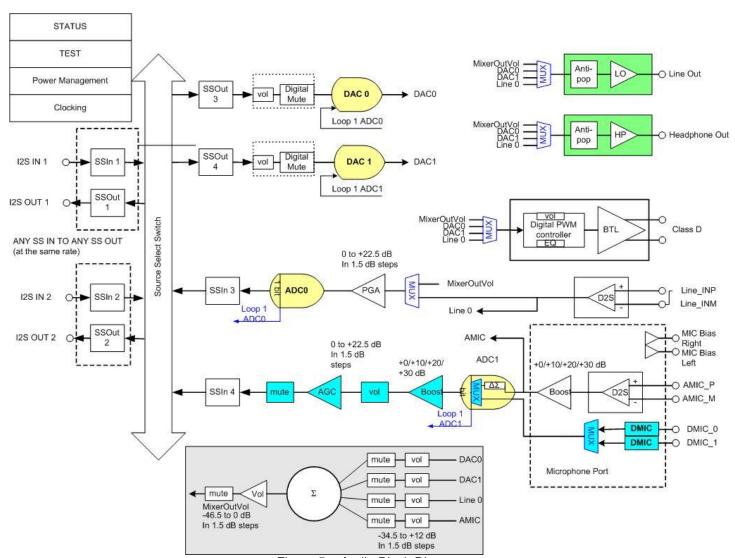

|              | 5 – Audio Block Diagram                                                  |     |

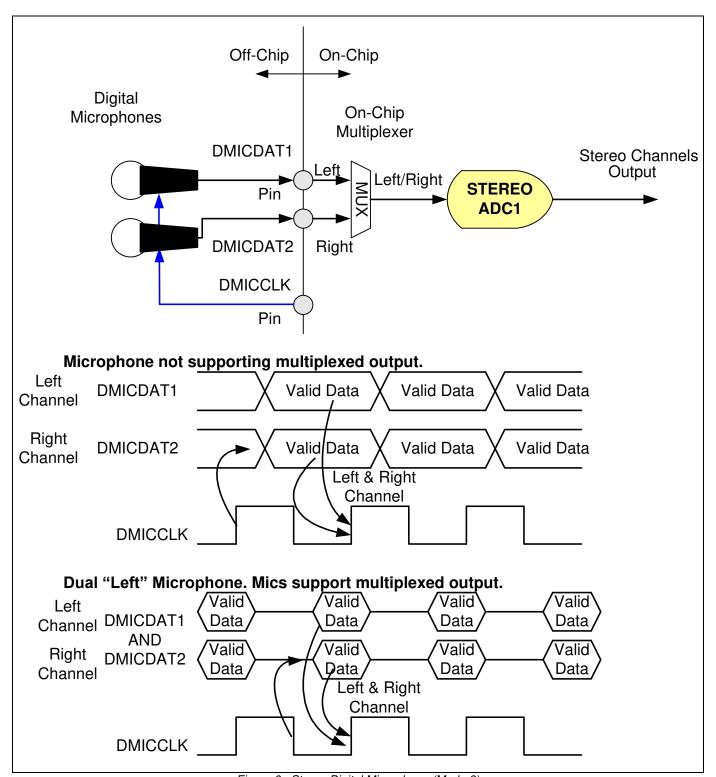

|              | 6 - Stereo Digital Microphone (Mode 3)                                   |     |

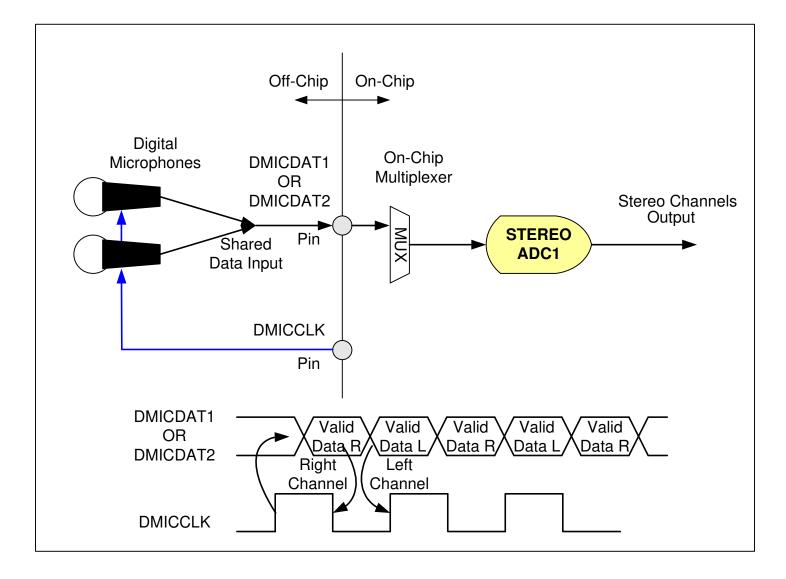

|              | 7 – Stereo Digital Microphone (Mode 1 & 2)                               |     |

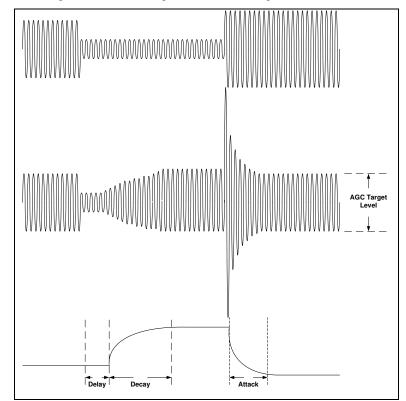

|              | 8 – Automatic Gain Control                                               |     |

|              | 9 – Charger Block Diagram                                                |     |

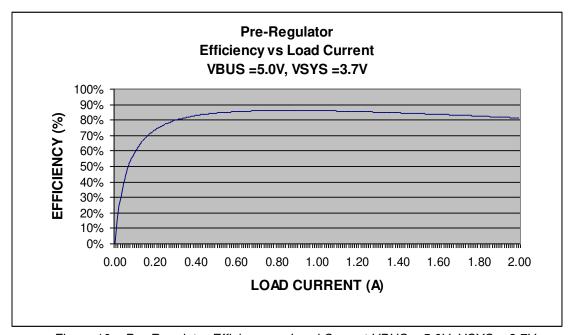

|              | 10 – Pre-Regulator Efficiency vs Load Current VBUS = 5.0V, VSYS = 3.7V   |     |

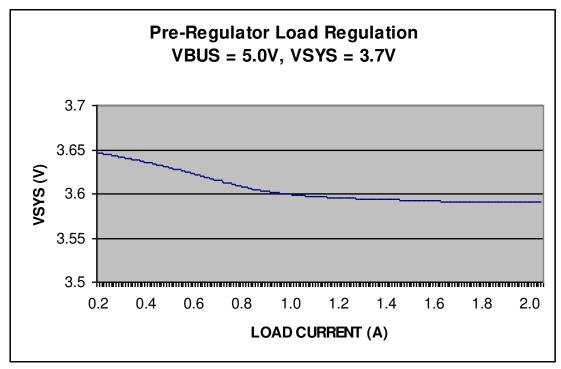

|              | 11– Pre-Regulator Load Regulation VBUS = 5.0V, VSYS = 3.7V               |     |

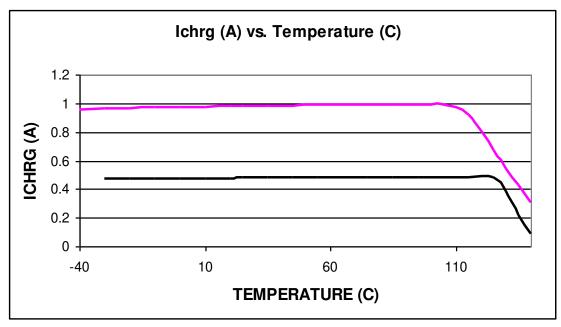

|              | 12 – Battery Charge Current vs Temperature                               |     |

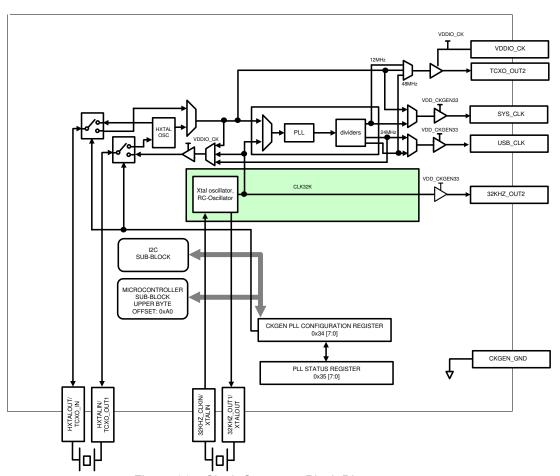

|              | 14 – Clock Generator Block Diagram                                       |     |

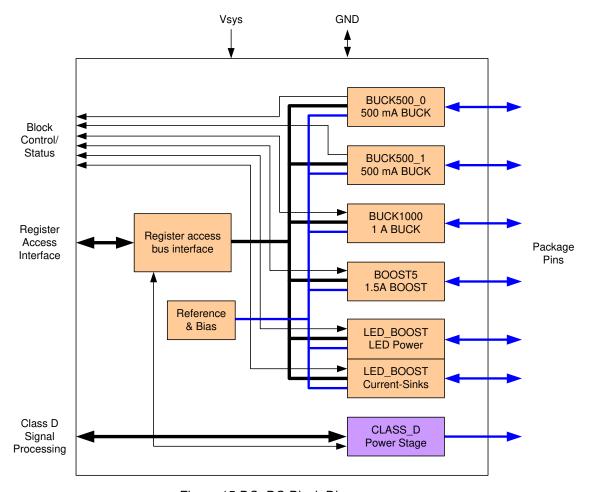

|              | 15 DC_DC Block Diagram                                                   |     |

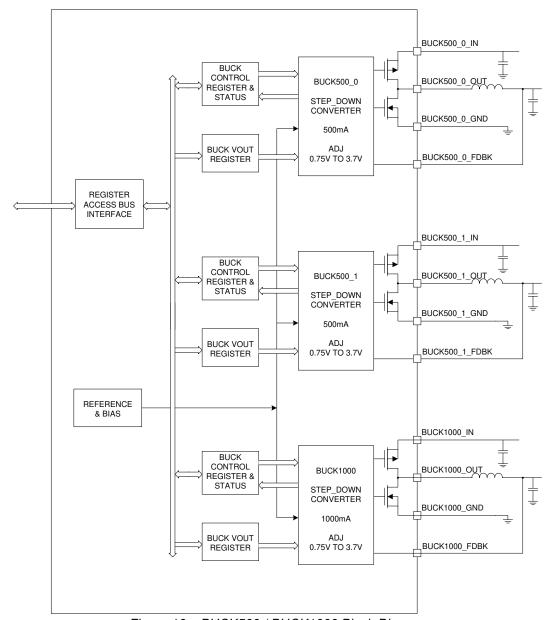

|              | 16 – BUCK500 / BUCK1000 Block Diagram                                    |     |

|              | 17 – BUCK500 DC-DC Regulator Efficiency vs Load Current PWM Mode         |     |

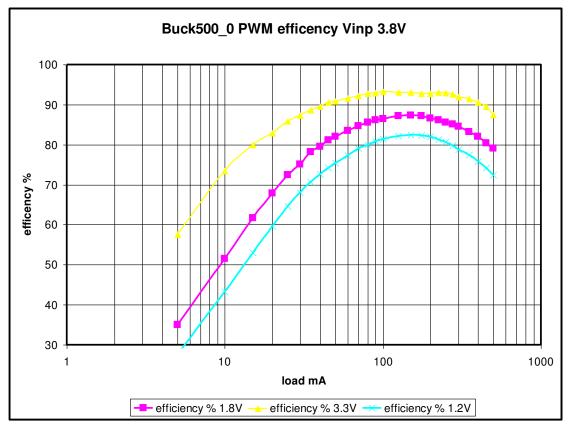

|              | 18 – BUCK1000 DC-DC Regulator Efficiency vs Load Current PWM Mode        |     |

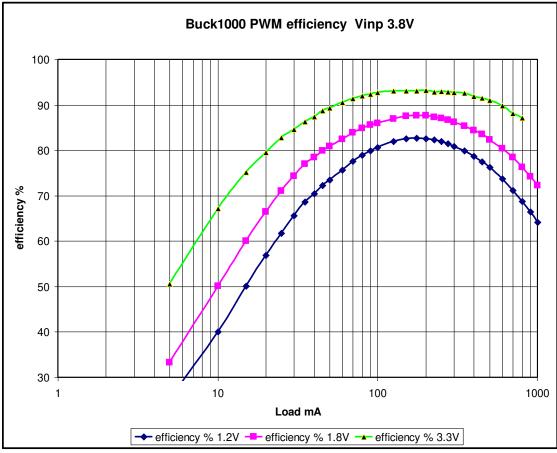

| Figure       | 19 – BUCK500 DC-DC Regulator Efficiency vs Load Current PFM Mode         | 79  |

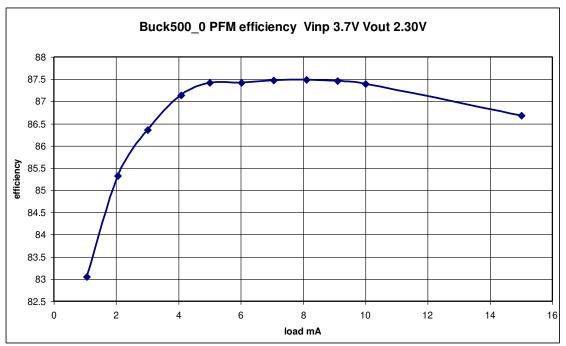

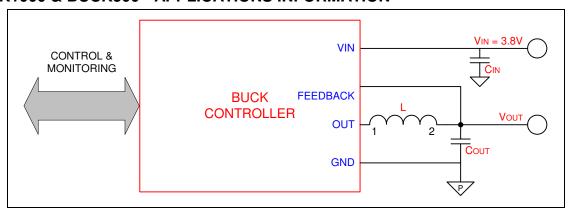

|              | 20 – BUCK500 or BUCK 1000 Applications Diagram                           |     |

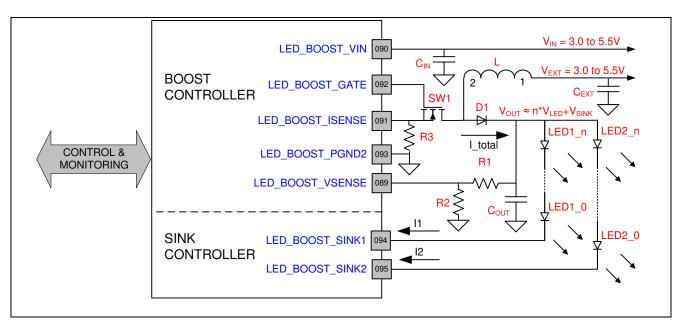

|              | 21 - White LED Boost & Sink Driver Block Diagram                         |     |

| Figure 22 – LED Boost Efficiency vs Load Current (two srings of 10 LEDs)                                                                                               | 84  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 23 – LED Boost Efficiency vs VIN (two srings of 10 LEDs)                                                                                                        |     |

| Figure 24 – LED BOOST Application Schematic                                                                                                                            |     |

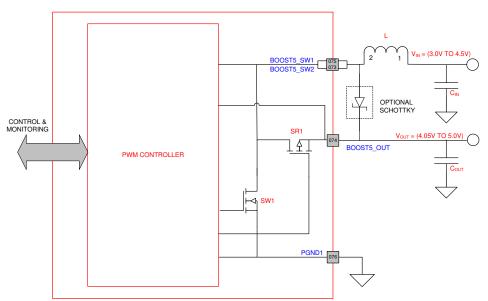

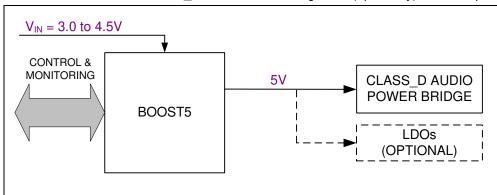

| Figure 25 – BOOST5 Block Diagram                                                                                                                                       |     |

| Figure 26 – BOOST5 Applications Diagram                                                                                                                                |     |

| Figure 27 – Clss D BTL Efficiency vs Outpout Power (4 ohm speaker)                                                                                                     |     |

| Figure 28 – ADC & Touchscreen Controller Block Diagram                                                                                                                 |     |

| Figure 29 – Hotswap Block Diagram                                                                                                                                      |     |

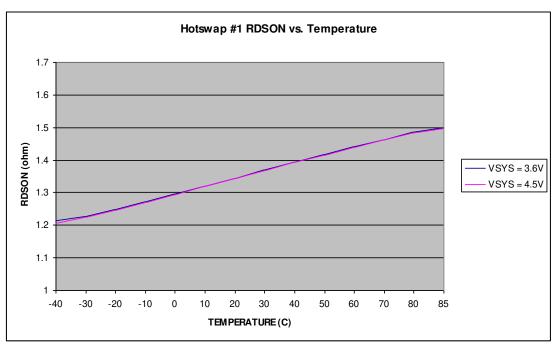

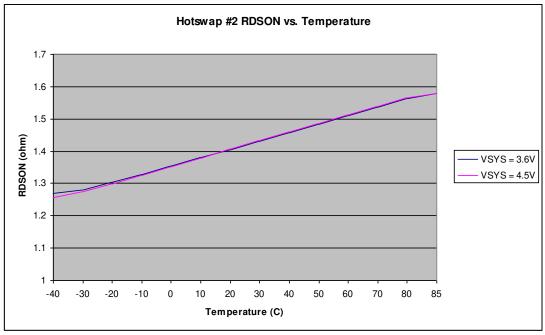

| Figure 30 – Hotswap #1 ON Resistance vs Temperature                                                                                                                    |     |

| Figure 31 – Hotswap #2 ON Resistance vs Temperature                                                                                                                    | 114 |

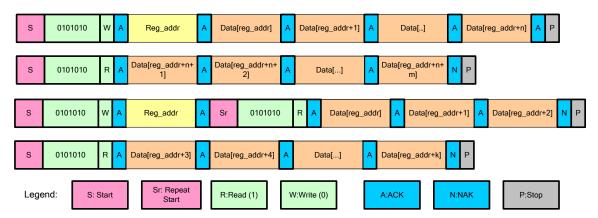

| Figure 32 – I <sup>2</sup> C Read / Write Operation                                                                                                                    | 117 |

| Figure 33 – LDO_050 / LDO_150 Block Diagram                                                                                                                            |     |

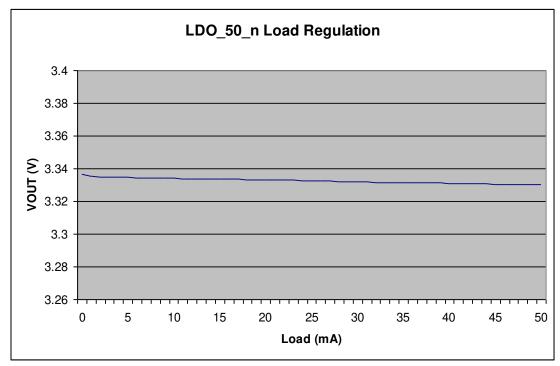

| Figure 34 – LDO_050_n 50mA LDO Load Regulation                                                                                                                         |     |

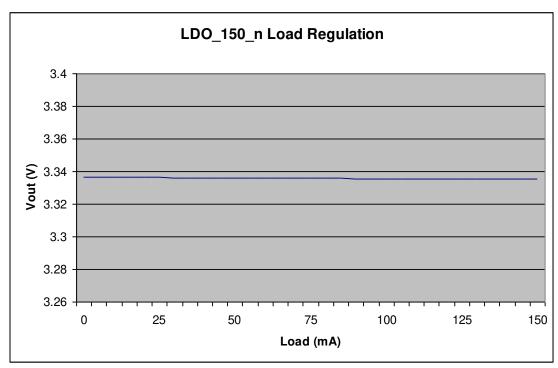

| Figure 35 – LDO_150_n 150mA LDO Load Regulation                                                                                                                        |     |

| Figure 36 - Top level Interrupt routing                                                                                                                                |     |

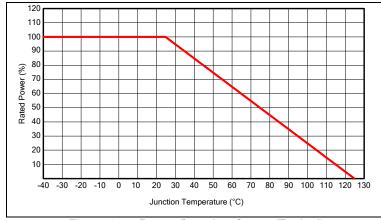

| Figure 37 – Power Derating Curve (Typical)                                                                                                                             | 133 |

| LIST OF TABLES                                                                                                                                                         |     |

| Table 1 – LLG124 Pin Functions by Pin Number (See Figure 2)                                                                                                            |     |

| Table 2 - NQG132 Pin Functions by Pin Number (see Figure 3)                                                                                                            |     |

| Table 3 – Register Address Global Mapping                                                                                                                              |     |

| Table 4 - Valid Digital Mic Configurations                                                                                                                             |     |

| Table 5 - MCLK hate selection: MCLK_DIV2: MCLK_HATE                                                                                                                    |     |

| Table 7 - EQRAM Addresses                                                                                                                                              |     |

| Table 8 – Register 0xA090 (0x90) Current Limit (I_LIM) Settings Bits [2:0]                                                                                             |     |

| Table 9 – Register 0xA091, (0x91) Charging Maximum Voltage (CHG_VOL) Settings, Bits [5:4]                                                                              |     |

| Table 10 – Register 0xA091, (0x91) Charging Current Limit via Sense Resistor (CHG CUR) Settings, Bits [3:0]                                                            |     |

| Table 11 – Register 0xA092 (0x92) Charging Termination Time (CHG_TERM) Settings Bits [1:0]                                                                             |     |

| Table 12 – Register 0xA093 (0x93) Battery Recovery Charge Current Control Settings Bits [7:5]                                                                          |     |

| Table 13 - Register 0xA093, (0x93) Battery Good Voltage Threshold Settings, Bits [4:3]                                                                                 |     |

| Table 14 - Register 0xA095, (0x95) Current Charger Mode Settings, Bits [4:3]                                                                                           |     |

| Table 15 - Crystal Specifications                                                                                                                                      |     |

| Table 16 - Alarm mask bits                                                                                                                                             |     |

| Table 17 – DC-DC Block Registers (Including the CLASS_D BTL Power Bridge)                                                                                              |     |

| Table 18 – BUCK500_0, BUCK500_1 and BUCK1000 Register Addresses                                                                                                        |     |

| Table 19 – Output Voltage Register Settings, Bits [6:0]                                                                                                                | 79  |

| Table 20 - Control Register Cycle by Cycle Current Limit (I_LIM) Settings for Bits [3:2] [Note ]                                                                       | 80  |

| Table 21 – Interoperability of enabling/disabling methods vs. loading default values.                                                                                  |     |

| Table 22 – Register 0xA086 (0x86) IOUT Current Settings for Bits [4:0], Half Scale and Full Scale                                                                      |     |

| Table 23 – Interoperability of enabling/disabling methods vs. loading default values.                                                                                  |     |

| Table 24 – Register 0xA088 Output Voltage Bit Setting [4:0]                                                                                                            | 90  |

| Table 26 – Register 0xA089 (0x89) Peak Current Limit (I_Lim) Settings Bits [3:2]  Table 26 – Interoperability of enabling/disabling methods vs. loading default values |     |

| Table 27 – Peak Short Circuit Detect Level Settings for Bits [3:2]                                                                                                     |     |

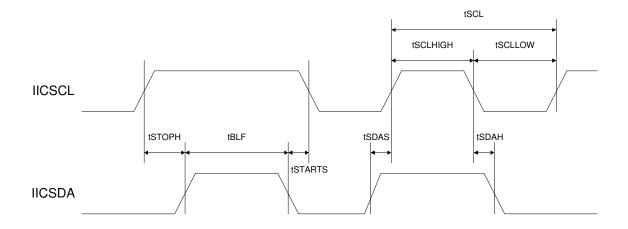

| Table 28 – I2C Interface Timing                                                                                                                                        |     |

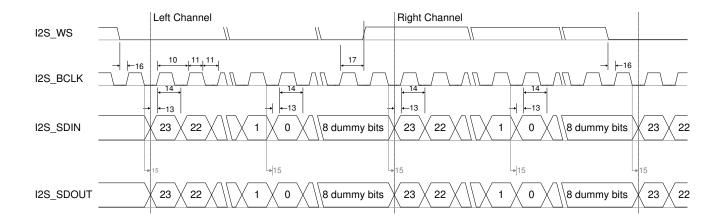

| Table 29 – I2S Interface Timing                                                                                                                                        |     |

| Table 30 - Interrupt Source Mapping                                                                                                                                    |     |

| Table 31 – Control Register Current Limit (I_LIM) Settings for Bits [1:0]                                                                                              | 128 |

# **PIN ASSIGNMENTS**

Figure 2 - P95020 Pinout Diagram (LLG124)

#### NOTES:

- 1. All the Buck Converter inputs (BUCK500\_0\_IN, BUCK500\_1\_IN, BUCK1000\_IN) must be connected to CHRG SYSVCC1 and CHRG SYSVCC2.

- 2. LLG124 package is available upon request.

Figure 3 – P95020 Pinout (NGQ132)

#### NOTES:

All the Buck Converter inputs (BUCK500\_0\_IN, BUCK500\_1\_IN, BUCK1000\_IN) must be connected to CHRG\_SYSVCC1 and CHRG\_SYSVCC2.

# PIN FUNCTIONS BY PIN NUMBER

Table 1 – LLG124 Pin Functions by Pin Number (See Figure 2)

| MODULE    | PIN#     | PIN NAME                | DESCRIPTION                                                                     | I/O TYPE    |

|-----------|----------|-------------------------|---------------------------------------------------------------------------------|-------------|

| GPIO_TSC  |          |                         | GPIO 5: General Purpose I/O # 5                                                 |             |

| (See Pins | 1        | GPIO5/INT_OUT           | INT_OUT : Interrupt Output                                                      | GPIO        |

| 117-124   |          |                         | GPIO 6: General Purpose I/O # 6                                                 |             |

| also)     | 2        | GPIO6/ADC1              | ADC1 : Auxiliary Input Channel 2 / X- pin to 4-wire resistive touch-screen      | GPIO        |

|           |          |                         | GPIO 7: General Purpose I/O # 7                                                 |             |

|           | 3        | GPIO7/ADC3              | ADC3 : Auxiliary Input Channel 4 / Y- pin to 4-wire resistive touch-screen      | GPIO        |

|           |          | ar 1077/12/00           |                                                                                 | GI 10       |

|           |          |                         | GPIO 8: General Purpose I/O # 8                                                 |             |

|           | 4        | GPIO8/ADC2              | ADC2 : Auxiliary Input Channel 3 / Y+ pin to 4-wire resistive touch-screen      | GPIO        |

|           |          |                         | GPIO 9: General Purpose I/O # 9                                                 |             |

|           |          |                         | ADC0 : Auxiliary Input Channel 1 / X+ pin to 4-wire resistive touch-screen      |             |

|           | 5        | GPIO9/ADC0/MCLK_IN      | MCLK_IN : Master Clock Input                                                    | GPIO        |

|           | 6        | GPIO10                  | GPIO 10: General Purpose I/O # 10                                               | GPIO        |

|           | 7        | MIC_R-                  | MIC_R-: Analog Microphone Differential Stereo Right Inverting Input             | A-I         |

|           |          | _                       | MIC_R+: Analog Microphone Differential Stereo Right Non-Inverting Input         | A-I         |

|           | 8        | MIC_R+/DMICDAT2         | DMICDAT2: Digital Microphone 2 Data Input                                       | D-I         |

|           |          |                         | MICBIAS : Microphone Right Bias                                                 | A-O         |

|           | 9        | MICBIAS_R/DMICSEL       | DMICSEL : Digital Microphone Select (Common to both inputs)                     | D-O         |

|           |          |                         | MICBIAS : Microphone Left Bias                                                  | A-O         |

|           | 10       | MICBIAS_L/DMICCLK       | DMICCLK: Digital Microphone Clock (Common to both inputs)                       | D-O         |

|           |          |                         | MIC_L+ : Analog Microphone Differential Stereo Left Non-Inverting Input         | A-I         |

|           | 11       | MIC_L+/DMICDAT1         | DMICDAT1 : Digital Microphone 1 Data Input                                      | D-I         |

|           | 12       | MIC_L-                  | MIC_L-: Analog Microphone Differential Stereo Left Inverting Input              | A-I         |

|           | 13       | AFILT2                  | Microphone ADC Anti-Aliasing Filter Capacitor #2                                | A-I         |

|           | 14       | AFILT1                  | Microphone ADC Anti-Aliasing Filter Capacitor #1                                | A-I         |

|           | 15       | AGND_MIC                | Microphone Ground (Analog Ground)                                               | GND         |

|           | 16       | LISLP                   | Line Input Stereo Left Non-Inverting                                            | A-I         |

|           | 17       | LISLM                   | Line Input Stereo Left Inverting                                                | A-I         |

|           | 18       | LISRP                   | Line Input Stereo Right Non-Inverting                                           | A-I         |

|           | 19       | LISRM                   | Line Input Stereo Right Inverting                                               | A-I         |

|           | 20       | LLO_L                   | Line Level Output, Left                                                         | A-O         |

|           | 21       | LLO_R                   | Line Level Output, Right                                                        | A-O         |

|           | 22       | AVREF                   | Analog Reference                                                                | A-O         |

|           | 23       | VDD_AUDIO33             | Filter Capacitor for Internal 3.3V AUDIO LDO                                    | A-O         |

|           | 24       | ADC_REF                 | ADC Reference Bypass Capacitor                                                  | A-I         |

|           | 25       | HP_R                    | Right Headphone Output                                                          | A-O         |

|           | 26       | HP_L                    | Left Headphone Output                                                           | A-O         |

|           | 27       | AGND                    | Line Out Ground (Analog Ground)                                                 | GND         |

| AUDIO     | 28       | VIRT_GND                | Virtual Ground for Cap-Less Output                                              | A-O         |

|           | 29       | LDO_GND                 | LDO Ground                                                                      | GND         |

|           | 30       | LDO_IN3                 | Input Voltage to LDOs for AUDIO Power (VDD_AUDIO33 & VDD_AUDIO18)               | AP-I        |

|           |          |                         | Always on Low Power LDO Output                                                  |             |

|           | 31       | LDO_LP                  | (Voltage Programmable to 3.0 V or 3.3 V)                                        | AP-O        |

|           | 32       | LDO_050_3               | 50mA LDO Output #3 (Voltage Range: 0.75-3.7 V)                                  | AP-O        |

|           | 33       | LDO_IN2                 | Input Voltage to LDO_050_0, LDO_050_1, LDO_050_2 & LDO_050_3                    | AP-I        |

|           | 34       | LDO_050_2               | 50mA LDO Output #2 (Voltage Range: 0.75-3.7 V)                                  | AP-O        |

|           | 35       | LDO_050_1               | 50mA LDO Output #1 (Voltage Range: 0.75-3.7 V)                                  | AP-O        |

|           |          |                         | 50mA LDO Output #0 (Voltage Range: 0.75-3.7 V)                                  |             |

|           |          |                         | Note: This LDO also serves as the internal power source for I2S1, I2S2 and      |             |

|           |          |                         | I2CS. The external function of this pin is not affected but the voltage         |             |

|           | 00       | 100 050 0               | register setting for this LDO will also govern the I/O level for I2S1, I2S2 and | 40.0        |

|           | 36       | LDO_050_0               | 12CS.                                                                           | AP-O        |

|           | 37       | LDO_150_2               | 150mA LDO Output #2 (Voltage Range: 0.75-3.7 V)                                 | AP-O        |

|           | 38       | LDO_IN1                 | Input Voltage to LDO_150_0, LDO_150_1, & LDO_050_2                              | AP-I        |

| 100       | 39       | LDO_150_1               | 150mA LDO Output #1 (Voltage Range: 0.75-3.7 V)                                 | AP-O        |

| LDO       | 40       | LDO_150_0               | 150mA LDO Output #0 (Voltage Range: 0.75-3.7 V) Buffered 32.768kHz Output #2    | AP-O<br>D-O |

|           | 41<br>42 | 32KHZ_OUT2<br>CKGEN_GND | ·                                                                               | GND         |

|           | 42       | ONGLIN_GIND             | PLL Analog Ground  32KHZ_CLKIN: External 32.768kHz Clock Input;                 | טווט        |

| CKGEN     | 43       | 30KHZ CI KINI/VTALINI   | XTALIN: Input Pin when used with an external crystal                            | Δ.          |

| ONGEN     | 40       | 32KHZ_CLKIN/XTALIN      | ATALIN . INPULTIN WHEN USED WITH AN EXTERNAL CLYSTAL                            | A-I         |

| MODULE  | PIN#     | PIN NAME                         | DESCRIPTION                                                                                                   | I/O TYPE         |

|---------|----------|----------------------------------|---------------------------------------------------------------------------------------------------------------|------------------|

|         |          |                                  | XTALOUT: Output Pin when used with an external crystal                                                        |                  |

|         |          |                                  | 32KHZ_OUT1: when XTALIN is connected to a 32kHz input this pin can be                                         |                  |

|         |          |                                  | a 32kHz Output when CKGEN_PLL_STATUS register, 32KOUT1_EN (bit                                                |                  |

|         | 44       | XTALOUT/32KHZ_OUT1               | 4) is set to 1.                                                                                               | A-O              |

|         | 45       | VDD_CKGEN18                      | Filter Capacitor for Internal 1.8V CKGEN LDO                                                                  | A-IO             |

|         | 40       | LIVEAL OUT/TOYO IN               | HXTALOUT: 12 MHz, 13 MHz, 19.2 MHz or 26 MHz crystal oscillator output                                        | TOYO D I         |

|         | 46<br>47 | HXTALOUT/TCXO_IN VDD CKGEN33     | TCXO_IN: External 12 MHz, 13 MHz, 19.2 MHz or 26 MHz Clock Input Filter Capacitor for Internal 3.3V CKGEN LDO | TCXO-D-I<br>A-IO |

|         | 47       | VDD_CRGENSS                      | HXTALIN: 12 MHz, 13 MHz, 19.2 MHz, or 26 MHz crystal oscillator input                                         | A-10             |

|         |          |                                  | TCXO_OUT1: Buffered HXTALOUT/TCXO_IN Clock Output #1, 32.7638                                                 |                  |

|         | 48       | HXTALIN/TCXO OUT1                | KHz Output, 24 MHz PLL Output                                                                                 | TCXO-D-O         |

|         | - 10     |                                  | Buffered HXTALOUT/TXCO_IN Clock Output #2, 12 MHz PLL Output,                                                 |                  |

|         | 49       | TCXO_OUT2                        | 24MHz PLL Output                                                                                              | TCXO-D-O         |

|         | 50       | SYS_CLK                          | 12MHz Output or Buffered Output of TCXO_IN                                                                    | D-O              |

|         | 51       | CKGEN_GND                        | PLL Analog Ground                                                                                             | GND              |

|         | 52       | USB_CLK                          | 24 MHz or 48 MHz Output                                                                                       | D-O              |

|         | 53       | VDDIO_CK                         | Power Supply Input for TCXO_OUT1 and TCXO_OUT2 (1.1V – 1.9V)                                                  | AP-I             |

|         |          | EV 5014                          | ROM Select. EX_ROM = 1, read contents of external ROM. EX_ROM = 0,                                            |                  |

|         | 54       | EX_ROM                           | read contents of internal ROM into internal shadow memory.                                                    | D-I              |

|         | 55<br>56 | DGND<br>I2S BCLK2                | Digital Ground  12S Bit Clock Channel 2                                                                       | GND<br>D-I       |

|         | 57       | 125_BCLK2<br>12S_WS2             |                                                                                                               | D-I              |

|         | 58       | I2S_SDOUT2                       | l <sup>2</sup> S Word Select (Left/Right) Channel 2 l <sup>2</sup> S Serial Data OUT Channel 2                | D-O              |

|         | 59       | 12S_SDIN2                        | 12S Serial Data IN Channel 2                                                                                  | D-U              |

|         | 60       | I2S BCLK1                        | I <sup>2</sup> S Bit Clock Channel 1                                                                          | D-I              |

|         | 61       | I2S WS1                          | I <sup>2</sup> S Word Select (Left/Right) Channel 1                                                           | D-I              |

|         | 62       | I2S_SDOUT1                       | I <sup>2</sup> S Serial Data OUT Channel 1                                                                    | D-O              |

|         | 63       | I2S_SDIN1                        | I <sup>2</sup> S Serial Data IN Channel 1                                                                     | D-I              |

|         | 64       | I2CS_SCL                         | I <sup>2</sup> C Slave clock                                                                                  | I2C-I/O          |

|         | 65       | I2CS SDA                         | I <sup>2</sup> C Slave data                                                                                   | I2C-O            |

|         | 66       | I2CM_SCL                         | I <sup>2</sup> C Master clock                                                                                 | I2C-O            |

|         | 67       | I2CM_SDA                         | I <sup>2</sup> C Master data                                                                                  | I2C-I/O          |

| I2C_I2S | 68       | GND                              | GND : Ground                                                                                                  | GND              |

|         | 69       | CLASS_D-                         | Class-D Inverting Output                                                                                      | A-O              |

|         | 70       | PGND                             | Ground for Class D BTL Power Stage                                                                            | GND              |

|         | 71       | PVDD                             | Input Power for CLASS_D BTL Power Stage                                                                       | A-I              |

| CLASS_D | 72       | CLASS_D+                         | Class-D Non-Inverting Output                                                                                  | A-O              |

|         |          | DO 0.075 01/10                   | BOOST5 Converter Power Switch                                                                                 |                  |

|         | 73<br>74 | BOOST5_SW2                       | Internally connected to pin 075 (BOOST_SW1)                                                                   | AP-O             |

|         | /4       | BOOST5_OUT                       | BOOST5 Converter Output BOOST5 Converter Power Switch                                                         | AP-O             |

|         | 75       | BOOST5_SW1                       | Internally connected to pin 073 (BOOST_SW2)                                                                   | AP-O             |

|         | 76       | BOOST5 GND                       | Ground for BOOST5 Power Supply                                                                                | AP-I             |

|         | 77       | BUCK1000 FDBK                    | BUCK2 Converter #2 -Feedback                                                                                  | AP-I             |

|         | 78       | BUCK1000 IN                      | BUCK2 Converter #2 - Input                                                                                    | AP-I             |

|         | 79       | BUCK1000_UT                      | BUCK2 Converter Output #2 – 1000mA                                                                            | AP-O             |

|         | 80       | BUCK1000_GND                     | Ground for BUCK2 Converter #2                                                                                 | GND              |

|         | 81       | BUCK500_1_FDBK                   | BUCK1 Converter #1 – Feedback                                                                                 | AP-I             |

|         | 82       | BUCK500_1_GND                    | Ground for BUCK1 Converter #1                                                                                 | GND              |

|         | 83       | BUCK500_1_OUT                    | BUCK1 Converter Output #1 - 500mA                                                                             | AP-O             |

|         | 84       | BUCK500_1_IN                     | BUCK1 Converter #1 Input                                                                                      | AP-I             |

|         | 85       | BUCK500_0_FDBK                   | BUCK0 Converter #0 feedback                                                                                   | AP-I             |

|         | 86       | BUCK500_0_GND                    | Ground for BUCK0 Converter #0                                                                                 | GND              |

|         | 87       | BUCK500_0_OUT                    | BUCK0 Converter Output #0 - 500mA                                                                             | AP-O             |

|         | 88       | BUCK500_0_IN                     | BUCKO Converter #0 Input                                                                                      | AP-I             |

|         | 89       | LED_BOOST_VSENSE                 | LED_BOOST Converter Output Voltage Sense Input to PWM Controller                                              | AP-I             |

|         | 90       | LED_BOOST_VIN                    | LED_BOOST Converter GATE BIAS Supply                                                                          | AP-I             |

|         | 91       | LED_BOOST_ISENSE                 | LED_BOOST Converter Output Current Sense Input to PWM Controller                                              | AP-I             |

|         | 92<br>93 | LED_BOOST_GATE  LED_BOOST_GND    | LED_BOOST Converter GATE Drive to Power FET Ground for LED BOOST                                              | AP-I<br>AP-I     |

|         | 93       | LED_BOOST_GND<br>LED_BOOST_SINK1 | LED_BOOST Converter Current Sink for LED String #1                                                            | AP-I<br>AP-I     |

|         | 95       | LED_BOOST_SINK1                  | LED_BOOST Converter Current Sink for LED String #1  LED_BOOST Converter Current Sink for LED String #2        | AP-I<br>AP-I     |

| DC_DC   | 96       | PSCREF                           | Power Supply Current Reference                                                                                | AP-0             |

|         | 97       | HSCTRL1                          | Hot Swap Control Input 1                                                                                      | D-I              |

|         | 98       | HSO1                             | Hot Swap Output 1                                                                                             | A-O              |

|         | 99       | HSPWR                            | Hot Swap Switches Power Input                                                                                 | AP-I             |

|         | 100      | HSO2                             | Hot Swap Output 2                                                                                             | A-O              |

| HOTSWAP | 101      | HSCTRL2                          | Hot Swap Control Input 2                                                                                      | D-I              |

|         |          |                                  |                                                                                                               |                  |

| MODULE    | PIN#       | PIN NAME                | DESCRIPTION                                                                                                                                           | I/O TYPE      |

|-----------|------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|           | 102        | CHRG_GND1               | Pins 102 & 103 are the Power GND Pins for the Switching Regulator in the                                                                              | A-I           |

|           |            |                         | Charger. Due to their higher current requirement they are internally tied                                                                             |               |

|           | 103        | CHRG_GND2               | together & must be connected externally at the PC board also.                                                                                         | A-I           |

|           | 104        | CHRG_SW1                | Pins 104 and 105 connect to the inductor of the switch-mode step-down                                                                                 | A-O           |

|           |            |                         | regulator for the Battery Charger. Due to their higher current requirement they are internally tied together & must be connected externally at the PC |               |

|           | 105        | CHRG SW2                | board also.                                                                                                                                           | A-O           |

|           | 106        | CHRG INPUT1             | Pins 106 and 107 provide 5V V <sub>BUS</sub> Input Power from the USB or from an                                                                      | AP-I          |

|           |            | 51.11G 51.1             | external wall mounted external supply. Due to their higher current                                                                                    | 7.1. 1        |

|           |            |                         | requirement they are internally tied together & must be connected externally                                                                          |               |

|           | 107        | CHRG_INPUT2             | at the PC board also.                                                                                                                                 | AP-I          |

|           | 108        | CHRG_SYSVCC1            | Pins 108 and 109 are System VCC Output (V <sub>SYS</sub> ). Due to their higher                                                                       | A-O           |

|           |            |                         | current requirement they are internally tied together & must be connected                                                                             |               |

|           | 109        | CHRG_SYSVCC2            | externally at the PC board also.                                                                                                                      | A-O           |

|           | 110        | CHRG_BAT1               | Pins 110 and 111 form the positive battery lead connection to a single cell Li-                                                                       | AP-I/O        |

|           | 444        | CHRG BAT2               | Ion/Li-Poly battery. Due to their higher current requirement they are internally                                                                      | A D 1/O       |

|           | 111<br>112 | CHRG_BA12<br>CHRG_CLSEN | tied together & must be connected externally at the PC board also.  Input Current Limit Sense/filtering pin for current limit detection               | AP-I/O<br>A-I |

|           | 113        | CHRG_CLSEN CHRG ICHRG   | Current setting. Connect to a current sense resistor                                                                                                  | AP-I/O        |

|           | 114        | CHRG GATE               | Gate Drive for (Optional) External Ideal Diode                                                                                                        | A-0           |

|           | 115        | CHRG NTC                | Thermal Sense, Connect to a battery's thermistor                                                                                                      | A-I           |

|           | - 110      | Gririd_IVIO             | NTC Power output. This pin provides power to the NTC resistor string.                                                                                 | 7.1           |

|           |            |                         | This output is automatically CHRG_SYSVCC level but only enabled when                                                                                  |               |

| CHARGER   | 116        | CHRG_VNTC               | NTC measurement is necessary to save power.                                                                                                           | AP-O          |

|           |            |                         | GND_BAT & ADCGND: Shared analog ground pin for battery charger and                                                                                    |               |

| GPIO_TSC  | 117        | GND_BAT/ADCGND          | ADC.                                                                                                                                                  | GND           |

| (See Pins | 118        | DGND                    | Digital Ground                                                                                                                                        | GND           |

| 001-006   | 119        | POR_OUT                 | Power-On-Reset Output, Active Low                                                                                                                     | GPIO-OUT      |

| also)     | 120        | SW_DET                  | Switch Detect Input                                                                                                                                   | GPIO          |

|           |            |                         | GPIO 1: General Purpose I/O # 1                                                                                                                       |               |

|           |            |                         | SW OUT: Switch Detect Output                                                                                                                          |               |

|           | 121        | GPIO1/SW_OUT/PENDOWN    | PENDOWN: PENDOWN Detect Output                                                                                                                        | GPIO          |

|           |            |                         | GPIO 2: General Purpose I/O # 2                                                                                                                       |               |

|           | 122        | GPIO2/LED1              | ·                                                                                                                                                     | GPIO          |

|           | 122        | GF IUZ/LED I            | LED1: Charger LED # 1 Indicates charging in progress                                                                                                  | GAIO          |

|           |            |                         | GPIO 3: General Purpose I/O # 3                                                                                                                       |               |

|           | 123        | GPIO3/LED2              | LED2: Charger LED # 2 Indicates charging complete                                                                                                     | GPIO          |

|           |            |                         | GPIO 4: General Purpose I/O # 4                                                                                                                       |               |

|           |            |                         | CHRG_ILIM: Control the current limit of the Charger Pre-Regulator.                                                                                    |               |

|           |            |                         | CHRG_ILIM = 0, limit current to 500mA; CHRG_ILIM = 1, limit current to                                                                                |               |

|           | 124        | GPIO4/CHRG_ILIM         | 1.5A                                                                                                                                                  | GPIO          |

Table 2 - NQG132 Pin Functions by Pin Number (see Figure 3)

| MODULE                 | PIN# | PIN NAME           | DESCRIPTION                                                                | I/O TYPE |

|------------------------|------|--------------------|----------------------------------------------------------------------------|----------|

|                        |      |                    | GPIO 5: General Purpose I/O # 5                                            |          |

|                        | A1   | GPIO5/INT_OUT      | INT_OUT : Interrupt Output                                                 | GPIO     |

|                        | A2   | NC                 | No Connect                                                                 | NC       |

|                        |      |                    | GPIO 7: General Purpose I/O # 7                                            |          |

| ODIO TOO               | B1   | GPIO7/ADC3         | ADC3 : Auxiliary Input Channel 4 / Y- pin to 4 wire resistive touch screen | GPIO     |

| GPIO_TSC               |      |                    | GPIO 6: General Purpose I/O # 6                                            |          |

| (See Pins<br>B57 – A71 | A3   | GPIO6/ADC1         | ADC1 : Auxiliary Input Channel 2 / X- pin to 4-wire resistive touch screen | GPIO     |

| also)                  |      |                    | GPIO 8: General Purpose I/O # 8                                            |          |

| 4/50)                  | B2   | GPIO8/ADC2         | ADC2 : Auxiliary Input Channel 3 / Y+ pin to 4-wire resistive touch screen | GPIO     |

|                        |      |                    | GPIO 9: General Purpose I/O # 9                                            |          |

|                        |      |                    | ADC0 : Auxiliary Input Channel 1 / X+ pin to 4-wire resistive touch screen |          |

|                        | A4   | GPIO9/ADC0/MCLK_IN | MCLK_IN : Master Clock Input                                               | GPIO     |

|                        | B3   | GPIO10             | GPIO 10: General Purpose I/O # 10                                          | GPIO     |

|                        | A5   | MIC_R-             | MIC_R-: Analog Microphone Differential Stereo Right Inverting Input        | A-I      |

|                        |      |                    | MIC_R+: Analog Microphone Differential Stereo Right Non-Inverting Input    | A-I      |

|                        | B4   | MIC_R+/DMICDAT2    | DMICDAT2: Digital Microphone 2 Data Input                                  | D-I      |

|                        |      |                    | MICBIAS : Microphone Right Bias                                            | A-O      |

| AUDIO                  | A6   | MICBIAS_R/DMICSEL  | DMICSEL : Digital Microphone Select (Common to both inputs)                | D-O      |

|                        |      |                    | MICBIAS : Microphone Left Bias                                             | A-O      |

|                        | B5   | MICBIAS_L/DMICCLK  | DMICCLK : Digital Microphone Clock (Common to both inputs)                 | D-O      |

|                        |      |                    | MIC_L+ : Analog Microphone Differential Stereo Left Non-Inverting Input    | A-I      |

|                        | A7   | MIC_L+/DMICDAT1    | DMICDAT1 : Digital Microphone 1 Data Input                                 | D-I      |

| MODULE  | DIN #      | DINI NIAME           | DECORIDATION                                                                                       | LO TYPE         |

|---------|------------|----------------------|----------------------------------------------------------------------------------------------------|-----------------|

| MODULE  | PIN#<br>B6 | PIN NAME MIC L-      | DESCRIPTION  MIC L-: Analog Microphone Differential Stereo Left Inverting Input                    | I/O TYPE<br>A-I |

|         | A8         | AFILT2               | Microphone ADC Anti-Aliasing Filter Capacitor #2                                                   | A-I             |

|         | B7         | AFILT1               | Microphone ADC Anti-Aliasing Filter Capacitor #2  Microphone ADC Anti-Aliasing Filter Capacitor #1 | A-I             |

|         | A9         | AGND MIC             | Microphone Ground (Analog Ground)                                                                  | GND             |

|         | B8         | LISLP                | Line Input Stereo Left Non-Inverting                                                               | A-I             |

|         | A10        | LISLM                | Line Input Stereo Left Inverting                                                                   | A-I             |

|         | B9         | LISRP                | Line Input Stereo Right Non-Inverting                                                              | A-I             |

|         | A11        | LISRM                | Line Input Stereo Right Inverting                                                                  | A-I             |

|         | B10        | LLO_L                | Line Level Output, Left                                                                            | A-O             |

|         | A12        | AVREF                | Analog Reference                                                                                   | A-O             |

|         | B11        | LLO_R                | Line Level Output, Right                                                                           | A-O             |

|         | A13        | ADC_REF              | ADC Reference Bypass Capacitor                                                                     | A-I             |

|         | B12        | VDD_AUDIO33          | Filter Capacitor for Internal 3.3V AUDIO LDO                                                       | A-O             |

|         | A14        | HP_L                 | Left Headphone Output                                                                              | A-O             |

|         | B13        | HP_R                 | Right Headphone Output                                                                             | A-O             |

|         | A15        | VIRT_GND             | Virtual Ground for Cap-Less Output                                                                 | A-O             |

|         | B14        | AGND                 | Analog Ground                                                                                      | GND             |

|         | A 1 C      | L DO INIO            | Input Voltage to LDOs for AUDIO Power                                                              | A.D. I          |

|         | A16        | LDO_IN3              | (VDD_AUDIO33 & VDD_AUDIO18) LDO Ground                                                             | AP-I            |

|         | B15<br>A17 | LDO_GND<br>NC        | No Connect                                                                                         | GND<br>NC       |

|         | A17        | NC                   | Always on Low Power LDO Output                                                                     | NC              |

|         | A18        | LDO LP               | (Voltage Programmable to 3.0 V or 3.3 V)                                                           | AP-O            |

|         | A19        | LDO 050 3            | 50mA LDO Output #3 (Voltage Range: 0.75-3.7 V)                                                     | AP-O            |

|         | A20        | NC                   | No Connect                                                                                         | NC NC           |

|         | B16        | LDO 050 2            | 50mA LDO Output #2 (Voltage Range: 0.75-3.7 V)                                                     | AP-O            |

| 1.00    | A21        | LDO IN2              | Input Voltage to LDO 050 0, LDO 050 1, LDO 050 2 & LDO 050 3                                       | AP-I            |

| LDO     | B17        | LDO 050 1            | 50mA LDO Output #1 (Voltage Range: 0.75-3.7 V)                                                     | AP-O            |

|         |            |                      | 50mA LDO Output #0 (Voltage Range: 0.75-3.7 V)                                                     |                 |

|         |            |                      | Note: This LDO also serves as the internal power source for I2S1, I2S2 and                         |                 |

|         |            |                      | I2CS. The external function of this pin is not affected but the voltage                            |                 |

|         |            |                      | register setting for this LDO will also govern the I/O level for I2S1, I2S2 and                    | 45.0            |

|         | A22        | LDO_050_0            | 12CS.                                                                                              | AP-O            |

|         | B18        | LDO_150_2            | 150mA LDO Output #2 (Voltage Range: 0.75-3.7 V)                                                    | AP-O<br>AP-I    |

|         | A23<br>B19 | LDO_IN1<br>LDO 150 1 | Input Voltage to LDO_150_0, LDO_150_1 & LDO_150_2  150mA LDO Output #1 (Voltage Range: 0.75-3.7 V) | AP-I<br>AP-O    |

|         | A24        | LDO_150_1            | 150mA LDO Output #1 (Voltage Range: 0.75-3.7 V)                                                    | AP-O            |

|         | B20        | 32KHZ OUT2           | Buffered 32.768kHz Output #2                                                                       | D-O             |

|         | A25        | CKGEN_GND            | PLL Analog Ground                                                                                  | GND             |

|         | 7120       | ORGEN_GIVE           | 32KHZ_CLKIN: External 32.768kHz Clock Input;                                                       | GIVE            |

|         | B21        | 32KHZ CLKIN/XTALIN   | XTALIN: Input Pin when used with an external crystal                                               | A-I             |

|         |            | <u> </u>             | XTALOUT: Output Pin when used with an external crystal                                             | 7               |

|         |            |                      | 32KHZ OUT1: when XTALIN is connected to a 32kHz input this pin can be                              |                 |

|         |            |                      | a 32kHz Output when CKGEN_PLL_STATUS register, 32KOUT1_EN (bit                                     |                 |

|         | A26        | XTALOUT/32KHZ_OUT1   | 4) is set to 1.                                                                                    | A-O             |

|         | B22        | VDD_CKGEN18          | Filter Capacitor for Internal 1.8V CKGEN LDO                                                       | A-IO            |

|         |            |                      | HXTALOUT: 12 MHz, 13 MHz, 19.2 MHz or 26 MHz output                                                |                 |

| CK_GEN  | A27        | HXTALOUT/TCXO_IN     | TCXO_IN: External 12 MHz, 13 MHz, 19.2 MHz or 26 MHz clock input                                   | TCXO-D-I        |

|         | B23        | VDD_CKGEN33          | Filter Capacitor for Internal 3.3V CKGEN LDO                                                       | A-IO            |

|         |            |                      | HXTALIN: 12 MHz, 13 MHz, 19.2 MHz, or 26 MHz crystal oscillator input                              |                 |

|         | 400        | LIVEALINITOVO OLITA  | TCXO_OUT1: Buffered HXTALOUT/TCXO_IN Clock Output #1, 32.7638                                      | TOYO D O        |

|         | A28        | HXTALIN/TCXO_OUT1    | KHz Output or 24 MHz PLL Output                                                                    | TCXO-D-O        |

|         | B24        | TCXO OUT2            | Buffered HXTALOUT/TXCO_IN Clock Output #2, 12 MHz PLL Output or 48 MHz PLL Output                  | TCXO-D-O        |

|         | A29        | SYS_CLK              | 12MHz Output or Buffered Output of TCXO_IN                                                         | D-O             |

|         | B25        | CKGEN_GND            | PLL Analog Ground                                                                                  | GND             |

|         | A30        | USB_CLK              | 24 MHz or 48 MHz Output                                                                            | D-O             |

|         | B26        | VDDIO_CK             | Power Supply Input for TCXO_OUT1 and TCXO_OUT2 (1.1V – 1.9V)                                       | AP-I            |

|         | 1          |                      | ROM Select. EX_ROM = 1, read contents of external ROM. EX_ROM = 0,                                 |                 |

|         | A31        | EX_ROM               | read contents of internal ROM into internal shadow memory.                                         | D-I             |

|         | B27        | DGND                 | Digital Ground (1)                                                                                 | GND             |

|         | A32        | I2S_BCLK2            | I <sup>2</sup> S Bit Clock Channel 2                                                               | D-I             |

|         | B28        | I2S_WS2              | I <sup>2</sup> S Word Select (Left/Right) Channel 2                                                | D-I             |

| I2C_I2S | A33        | I2S_SDIN2            | I <sup>2</sup> S Serial Data IN Channel 2                                                          | D-I             |

|         | B29        | I2S_SDOUT2           | I <sup>2</sup> S Serial Data OUT Channel 2                                                         | D-O             |

|         | A34        | I2S_WS1              | I <sup>2</sup> S Word Select (Left/Right) Channel 1                                                | D-I             |

|         | B30        | I2S_BCLK1            | I <sup>2</sup> S Bit Clock Channel 1                                                               | D-I             |

|         | A35        | NC                   | No Connect                                                                                         | NC              |

|         | A36        | NC                   | No Connect                                                                                         | NC              |

| MODULE  | PIN#       | PIN NAME                          | DESCRIPTION                                                                                                                                           | I/O TYPE       |

|---------|------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|         | A37        | I2S_SDOUT1                        | I <sup>2</sup> S Serial Data OUT Channel 1                                                                                                            | D-O            |

|         | A38        | I2S_SDIN1                         | I <sup>2</sup> S Serial Data IN Channel 1                                                                                                             | D-I            |

|         | B31        | I2CS_SCL                          | I <sup>2</sup> C Slave clock                                                                                                                          | I2C-I/O        |

|         | A39        | I2CS_SDA                          | I <sup>2</sup> C Slave data                                                                                                                           | I2C-O          |

|         | B32        | I2CM_SCL                          | I <sup>2</sup> C Master clock                                                                                                                         | I2C-O          |

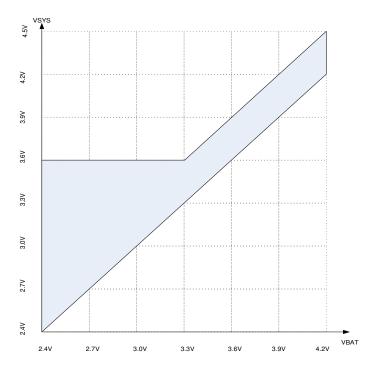

|         | A40<br>B33 | I2CM_SDA<br>GND                   | I <sup>2</sup> C Master data GND : Ground                                                                                                             | I2C-I/O<br>GND |