### Data Sheet

### July 1999 File Number 3149.2

# Precision, 4-Channel, Low-Level, Differential Multiplexer

inter<sub>sil</sub>

The Intersil HI-539 is a monolithic, 4-Channel, differential multiplexer. Two digital inputs are provided for channel selection, plus an Enable input to disconnect all channels.

Performance is guaranteed for each channel over the voltage range  $\pm 10V$ , but is optimized for low level differential signals. Leakage current, for example, which varies slightly with input voltage, has its distribution centered at zero input volts.

In most monolithic multiplexers, the net differential offset due to thermal effects becomes significant for low level signals. This problem is minimized in the HI-539 by symmetrical placement of critical circuitry with respect to the few heat producing devices.

Supply voltages are  $\pm 15\text{V}$  and power consumption is only 2.5mW.

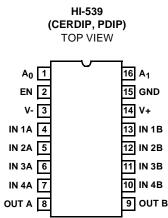

# **Ordering Information**

| PART NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE      | PKG.<br>NO. |

|-------------|----------------------------------|--------------|-------------|

| HI1-0539-5  | 0 to 75                          | 16 Ld CERDIP | F16.3       |

| HI1-0539-8  | -55 to 125                       | 16 Ld CERDIP | F16.3       |

| HI3-0539-5  | 0 to 75                          | 16 Ld PDIP   | E16.3       |

| HI4P0539-5  | 0 to 75                          | 20 Ld PLCC   | N20.35      |

# **Pinouts**

# Features

- Differential Performance, Typical:

- Wide Supply Range ..... ±5V to ±18V

- Break-Before-Make Switching

- No Latch-Up

# Applications

- Low Level Data Acquisition

- Precision Instrumentation

- Test Systems

### TRUTH TABLE

|    |                |                | ON CHANNEL TO |       |  |

|----|----------------|----------------|---------------|-------|--|

| EN | A <sub>1</sub> | A <sub>0</sub> | OUT A         | OUT B |  |

| L  | Х              | Х              | None          | None  |  |

| Н  | L              | L              | 1A            | 1B    |  |

| Н  | L              | Н              | 2A            | 2B    |  |

| Н  | Н              | L              | ЗA            | 3B    |  |

| Н  | Н              | Н              | 4A 4B         |       |  |

## Absolute Maximum Ratings

| V+ to V                                                            |

|--------------------------------------------------------------------|

| V+ or V- to GND                                                    |

| Analog Signal (V <sub>IN</sub> , V <sub>OUT</sub> ) V- to V+       |

| Digital Input Voltage (V <sub>EN</sub> , V <sub>A</sub> ) V- to V+ |

| Analog Current (IN or OUT) 20mA                                    |

## **Operating Conditions**

| Temperature Range |                                         |

|-------------------|-----------------------------------------|

| HI-539-8          | 55 <sup>0</sup> C to 125 <sup>0</sup> C |

| HI-539-5          | 0 <sup>o</sup> C to 75 <sup>o</sup> C   |

### **Thermal Information**

| Thermal Resistance (Typical, Note 1)                             | θ <sub>JA</sub> ( <sup>o</sup> C/W) | θ <sub>JC</sub> ( <sup>o</sup> C/W)    |

|------------------------------------------------------------------|-------------------------------------|----------------------------------------|

| CERDIP Package                                                   | 85                                  | 32                                     |

| PDIP Package                                                     | 90                                  | N/A                                    |

| PLCC Package                                                     | 80                                  | N/A                                    |

| Maximum Junction Temperature                                     |                                     |                                        |

| Ceramic Package                                                  |                                     | 175 <sup>0</sup> C                     |

| Plastic Package                                                  |                                     | 150 <sup>0</sup> C                     |

| Maximum Storage Temperature Range .                              | 65                                  | 5 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 1<br>(PLCC - Lead Tips Only) | 0s)                                 | 300 <sup>0</sup> C                     |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### NOTE:

1.  $\theta_{\text{JA}}$  is measured with the component mounted on an evaluation PC board in free air.

| <b>Electrical Specifications</b> | Supplies = $\pm$ 15V, V <sub>EN</sub> = 4V, V <sub>AH</sub> (Logic Level High) = 4V, V <sub>AL</sub> (Logic Level Low) = 0.8V, |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|                                  | Unless Otherwise Specified                                                                                                     |

|                                                      | TEST       | TEMP |     | -8   |       |     | -5   |       |       |

|------------------------------------------------------|------------|------|-----|------|-------|-----|------|-------|-------|

| PARAMETER                                            | CONDITIONS | (°C) | MIN | TYP  | MAX   | MIN | TYP  | MAX   | UNITS |

| DYNAMIC CHARACTERISTICS                              | I          | •    | •   |      |       |     |      |       |       |

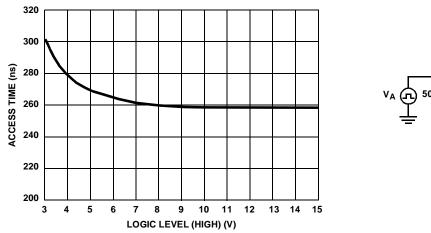

| Access Time, t <sub>A</sub>                          |            | 25   | -   | 250  | 750   | -   | 250  | 750   | ns    |

|                                                      |            | Full | -   | -    | 1,000 | -   | -    | 1,000 | ns    |

| Break-Before-Make Delay, tOPEN                       |            | 25   | 30  | 85   | -     | 30  | 85   | -     | ns    |

|                                                      |            | Full | 30  | -    | -     | 30  | -    | -     | ns    |

| Enable Delay (ON), t <sub>ON(EN)</sub>               |            | 25   | -   | 250  | 750   | -   | 250  | 750   | ns    |

|                                                      |            | Full | -   | -    | 1,000 | -   | -    | 1,000 | ns    |

| Enable Delay (OFF), t <sub>OFF(EN)</sub>             |            | 25   | -   | 160  | 650   | -   | 160  | 650   | ns    |

|                                                      |            | Full | -   | -    | 900   | -   | -    | 900   | ns    |

| Settling Time                                        | To 0.01%   | 25   | -   | 0.9  | -     | -   | 0.9  | -     | μs    |

| Charge Injection (Output)                            |            | Full | -   | 3    | -     | -   | 3    | -     | рС    |

| $\Delta$ Charge Injection (Output)                   |            | Full | -   | 0.1  | -     | -   | 0.1  | -     | рС    |

| Charge Injection (Input)                             |            | Full | -   | 10   | -     | -   | 10   | -     | рС    |

| Differential Crosstalk                               | Note 4     | 25   | -   | -124 | -     | -   | -124 | -     | dB    |

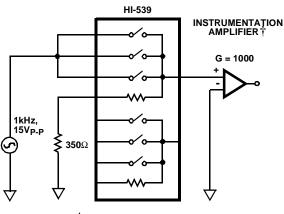

| Single Ended Crosstalk                               | Note 4     | 25   | -   | -100 | -     | -   | -100 | -     | dB    |

| Channel Input Capacitance,<br>C <sub>S(OFF)</sub>    |            | Full | -   | 5    | -     | -   | 5    | -     | pF    |

| Channel Output Capacitance,<br>C <sub>D(OFF)</sub>   |            | Full | -   | 7    | -     | -   | 7    | -     | pF    |

| Channel On Output Capacitance,<br><sup>C</sup> D(ON) |            | Full | -   | 17   | -     | -   | 17   | -     | pF    |

| Input to Output Capacitance,<br>CDS(OFF)             | Note 5     | Full | -   | 0.08 | -     | -   | 0.08 | -     | pF    |

| Digital Input Capacitance, CA                        |            | Full | -   | 3    | -     | -   | 3    | -     | pF    |

| DIGITAL INPUT CHARACTERISTIC                         | S          | 1    |     | 1    |       |     |      | 1     |       |

| Input Low Threshold, V <sub>AL</sub>                 |            | Full | -   | -    | 0.8   | -   | -    | 0.8   | V     |

| Input High Threshold, V <sub>AH</sub>                |            | Full | 4.0 | -    | -     | 4.0 | -    | -     | V     |

| Input Leakage Current (High), I <sub>AH</sub>        |            | Full | -   | -    | 1     | -   | -    | 1     | μΑ    |

| Input Leakage Current (Low), IAL                     |            | Full | -   | -    | 1     | -   | -    | 1     | μA    |

###

|                                              | TEST                 | ТЕМР              |     | -8    |      |     | -5    |      |       |

|----------------------------------------------|----------------------|-------------------|-----|-------|------|-----|-------|------|-------|

| PARAMETER                                    | CONDITIONS           | ( <sup>o</sup> C) | MIN | TYP   | MAX  | MIN | TYP   | MAX  | UNITS |

| ANALOG CHANNEL CHARACTERIS                   | TICS                 | 1                 | I   | 1     | 1    |     |       | 1    |       |

| Analog Signal Range, V <sub>IN</sub>         |                      | Full              | -10 | -     | +10  | -10 | -     | +10  | V     |

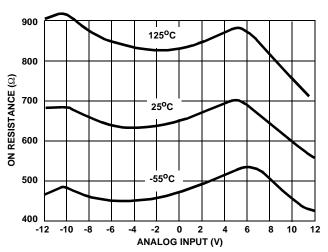

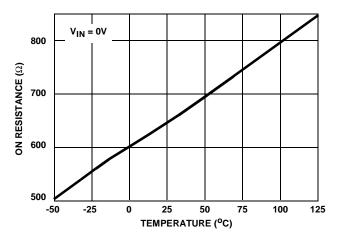

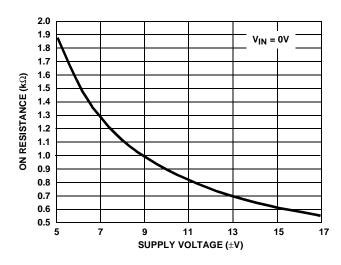

| On Resistance, r <sub>ON</sub>               | V <sub>IN</sub> = 0V | 25                | -   | 650   | 850  | -   | 650   | 850  | Ω     |

|                                              |                      | Full              | -   | 950   | 1.3K | -   | 800   | 1K   | Ω     |

|                                              | $V_{IN} = \pm 10V$   | 25                | -   | 700   | 900  | -   | 700   | 900  | Ω     |

|                                              |                      | Full              | -   | 1.1K  | 1.4K | -   | 900   | 1.1K | Ω     |

| ∆r <sub>ON,</sub> (Side A-Side B)            | $V_{IN} = 0V$        | 25                | -   | 4.0   | 24   | -   | 4.0   | 24   | Ω     |

|                                              |                      | Full              | -   | 4.75  | 28   | -   | 4.0   | 24   | Ω     |

|                                              | $V_{IN} = \pm 10V$   | 25                | -   | 4.5   | 27   | -   | 4.5   | 27   | Ω     |

|                                              |                      | Full              | -   | 5.5   | 33   | -   | 4.5   | 27   | Ω     |

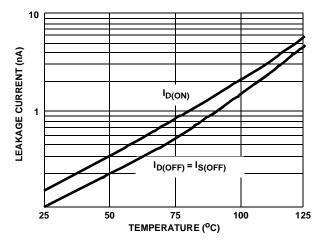

| Off Input Leakage Current, IS(OFF)           | Condition 0V         | 25                | -   | 30    | -    | -   | 30    | -    | pА    |

|                                              | (Note 2)             | Full              | -   | 2     | 10   | -   | 0.2   | 1    | nA    |

|                                              | Condition ±10V       | 25                | -   | 100   | -    | -   | 100   | -    | pА    |

|                                              | (Note 2)             | Full              | -   | 5     | 25   | -   | 0.5   | 2.5  | nA    |

| $\Delta I_{S(OFF)}$ , (Side A-Side B)        | Condition 0V         | 25                | -   | 3     | -    | -   | 3     | -    | pА    |

|                                              |                      | Full              | -   | 0.2   | 2    | -   | 0.02  |      | nA    |

|                                              | Condition ±10V       | 25                | -   | 10    | -    | -   | 10    | -    | pА    |

|                                              |                      | Full              | -   | 0.5   | 5    | -   | 0.05  | 0.5  | nA    |

| Off Output Leakage Current,                  | Condition 0V         | 25                | -   | 30    | -    | -   | 30    | -    | pА    |

| ID(OFF)                                      | (Note 2)             | Full              | -   | 2     | 10   | -   | 0.2   | 1    | nA    |

|                                              | Condition ±10V       | 25                | -   | 100   | -    | -   | 100   | -    | pА    |

|                                              | (Note 2)             | Full              | -   | 5     | 25   | -   | 0.5   | 2.5  | nA    |

| ΔI <sub>D(OFF),</sub> (Side A-Side B)        | Condition 0V         | 25                | -   | 3     | -    | -   | 3     | -    | pА    |

|                                              |                      | Full              | -   | 0.2   | 2    | -   | 0.02  | 0.2  | nA    |

|                                              | Condition ±10V       | 25                | -   | 10    | -    | -   | 10    | -    | pА    |

|                                              |                      | Full              | -   | 0.5   | 5    | -   | 0.05  | 0.5  | nA    |

| On Channel Leakage Current, ID(ON)           | Condition 0V         | 25                | -   | 50    | -    | -   | 50    | -    | pА    |

|                                              | (Note 2)             | Full              | -   | 5     | 25   | -   | 0.5   | 2.5  | nA    |

|                                              | Condition ±10V       | 25                | -   | 150   | -    | -   | 150   | -    | pА    |

|                                              | (Note 2)             | Full              | -   | 6     | 40   | -   | 0.8   | 4.0  | nA    |

| ΔI <sub>D(ON),</sub> (Side A-Side B)         | Condition 0V         | 25                | -   | 10    | -    | -   | 10    | -    | pА    |

|                                              |                      | Full              | -   | 0.5   | 5    | -   | 0.05  | 0.5  | nA    |

|                                              | Condition ±10V       | 25                | -   | 30    | -    | -   | 30    | -    | pА    |

|                                              |                      | Full              | -   | 0.6   | 6    | -   | 0.08  | 0.8  | nA    |

| Differential Offset Voltage, $\Delta V_{OS}$ | Note 3               | 25                | -   | 0.02  | -    | -   | 0.02  | -    | μV    |

|                                              |                      | Full              | -   | 0.70  | -    | -   | 0.08  | -    | μV    |

| POWER SUPPLY CHARACTERISTIC                  | :S                   | 1                 | I   | 1     | 1    |     | L     | 1    | 1     |

| Power Dissipation, PD                        |                      | 25                | -   | 2.3   | -    | -   | 2.3   | -    | mW    |

|                                              |                      | Full              | -   | -     | 45   | -   | -     | 45   | mW    |

| Current, I+                                  |                      | 25                | -   | 0.150 | -    | -   | 0.150 | -    | mA    |

|                                              |                      | Full              | -   | -     | 2.0  | -   | -     | 2.0  | mA    |

###

|                      | TEST       | ТЕМР              |     | -8    |     |     | -5    |     |       |

|----------------------|------------|-------------------|-----|-------|-----|-----|-------|-----|-------|

| PARAMETER            | CONDITIONS | ( <sup>o</sup> C) | MIN | ТҮР   | MAX | MIN | TYP   | MAX | UNITS |

| Current, I-          |            | 25                | -   | 0.001 | -   | -   | 0.001 | -   | mA    |

|                      |            | Full              | -   | -     | 1.0 | -   | -     | 1.0 | mA    |

| Supply Voltage Range |            | Full              | ±5  | ±15   | ±18 | ±5  | ±15   | ±18 | V     |

NOTES:

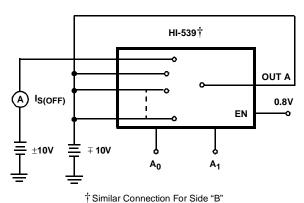

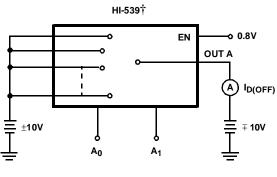

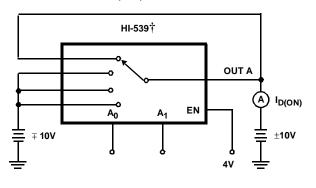

2. See Figures 2B, 2C, 2D. The condition  $\pm 10V$  means:

$I_{S(OFF)} \text{ and } I_{D(OFF)}: \\ (V_S = +10V, V_D = -10V), \text{ then } \\ (V_S = -10V, V_D = +10V) \\ I_{D(ON)}: (+10V, \text{ then } -10V)$

3.  $\Delta V_{OS}$  (Exclusive of thermocouple effects) =  $r_{ON} \Delta I_{D(ON)} + I_{D(ON)} \Delta r_{ON}$ . See Applications section for discussion of additional  $V_{OS}$  error.

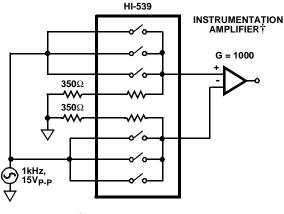

4.  $V_{IN} = 1 \text{ kHz}$ ,  $15 V_{P-P}$  on all but the selected channel. See Figure 7.

5. Calculated from typical Single-Ended Crosstalk performance.

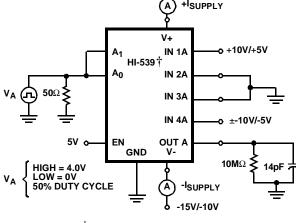

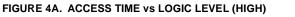

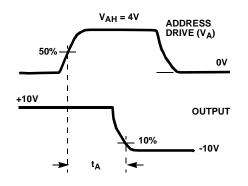

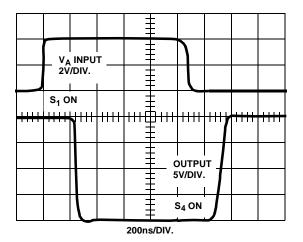

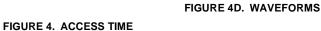

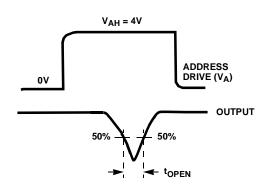

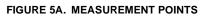

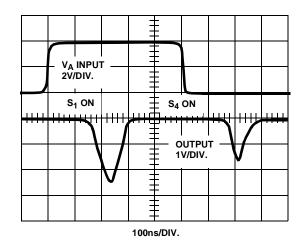

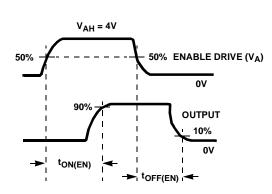

**Test Circuits and Waveforms** Unless Otherwise Specified  $T_A = 25^{\circ}C$ ,  $V_{+} = +15V$ ,  $V_{-} = -15V$ ,  $V_{AH} = 4V$  and  $V_{AL} = 0.8V$

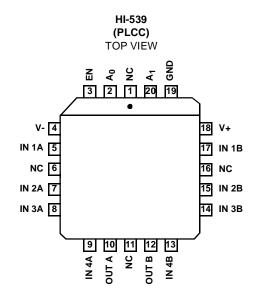

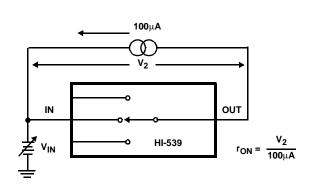

### FIGURE 1A. TEST CIRCUIT

### FIGURE 1B. ON RESISTANCE vs TEMPERATURE

FIGURE 1C. ON RESISTANCE vs ANALOG INPUT VOLTAGE

FIGURE 1D. ON RESISTANCE vs SUPPLY VOLTAGE

FIGURE 1. ON RESISTANCE

## FIGURE 2C. IS(OFF) TEST CIRCUIT (NOTE 6)

NOTE:

6. Three measurements =  $\pm 10V$ ,  $\mp 10V$ , and 0V.

† Similar Connection For Side "B"

†Similar Connection For Side "B"

## FIGURE 2D. I<sub>D(ON)</sub> TEST CIRCUIT (NOTE 6)

+15V/+10V

†Similar Connection For Side "B"

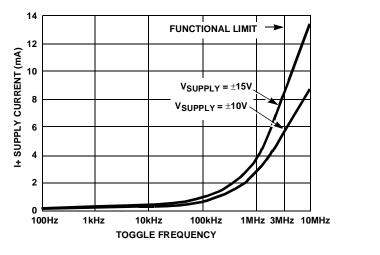

FIGURE 3B. TEST CIRCUIT

FIGURE 3. DYNAMIC SUPPLY CURRENT

**FIGURE 2. LEAKAGE CURRENT**

o +15V

FIGURE 4C. MEASUREMENT POINTS

FIGURE 5C. WAVEFORMS FIGURE 5. BREAK-BEFORE-MAKE DELAY

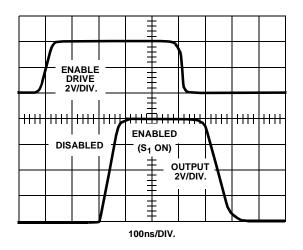

FIGURE 6A. MEASUREMENT POINTS

FIGURE 6B. TEST CIRCUIT

FIGURE 6C. WAVEFORMS FIGURE 6. ENABLE DELAYS

FIGURE 7B. DIFFERENTIAL CROSSTALK TEST CIRCUIT

FIGURE 7. CROSSTALK

# Application Information

### General

The HI-539 accepts inputs in the range -15V to +15V, with performance guaranteed over the  $\pm$ 10V range. At these higher levels of analog input voltage it is comparable to the HI-509, and is plug-in compatible with that device (as well as the HI-509A). However, as mentioned earlier, the HI-539 was designed to introduce minimum error when switching low level inputs.

Special care is required in working with these low level signals. The main concern with signals below 100mV is that noise, offset voltage, and other aberrations can represent a large percentage error. A shielded differential signal path is essential to maintain a noise level below  $50\mu V_{RMS}$ .

# Low Level Signal Transmission

The transmission cable carrying the transducer signal is critical in a low level system. It should be as short as practical and rigidly supported. Signal conductors should be tightly twisted for minimum enclosed area to guard against pickup of electromagnetic interference, and the twisted pair should be shielded against capacitively coupled (electrostatic) interference. A braided wire shield may be satisfactory, but a lapped foil shield is better since it allows only 1/10 as much leakage capacitance to ground per foot. A key requirement for the transmission cable is that it presents a balanced line to sources of noise interference. This means an equal series impedance in each conductor plus an equally distributed impedance from each conductor to ground. The result should be signals equal in magnitude but opposite in phase at any transverse plane. Noise will be coupled in phase to both conductors, and may be rejected as common-mode voltage by a differential amplifier connected to the multiplexer output.

Coaxial cable is not suitable for low level signals because the two conductors (center and shield) are unbalanced. Also, ground loops are produced if the shield is grounded at both ends by standard BNC connectors. If coax must be used, carry the signal on the center conductors of two equal-length cables whose shields are terminated only at the transducer end. As a general rule, terminate (ground) the shield at one end only, preferably at the end with greatest noise interference. This is usually the transducer end for both high and low level signals.

# Watch Small $\triangle V$ Errors

Printed circuit traces and short lengths of wire can add substantial error to a signal even after it has traveled hundreds of feet and arrived on a circuit board. Here, the small voltage drops due to current flow through connections of a few milliohms must be considered, especially to meet an accuracy requirement of 12 bits or more.

Table 1 is a useful collection of data for calculating the effect of these short connections. (Proximity to a ground plane will lower the values of inductance.)

As an example, suppose the HI-539 is feeding a 12-bit converter system with an allowable error of  $\pm^{1}/_{2}$  LSB ( $\pm^{1.22}$ mV). If the interface logic draws 100mA from the 5V supply, this current will produce 1.28mV across 6 inches of #24 wire; more than the error budget. Obviously, this digital current must not be routed through any portion of the analog ground return network.

| EQUIVALENT WIDTH OF |                              |                           |                        | IMPEDANCE PER FOOT |         |  |  |

|---------------------|------------------------------|---------------------------|------------------------|--------------------|---------|--|--|

| WIRE GAGE           | P.C. CONDUCTOR<br>(2 oz. Cu) | DC RESISTANCE<br>PER FOOT | INDUCTANCE PER<br>FOOT | 60Hz               | 10kHz   |  |  |

| 18                  | 0.47"                        | 0.0064Ω                   | 0.36μΗ                 | 0.0064Ω            | 0.0235Ω |  |  |

| 20                  | 0.30"                        | 0.0102Ω                   | 0.37µH                 | 0.0102Ω            | 0.0254Ω |  |  |

| 22                  | 0.19"                        | 0.0161Ω                   | 0.37µH                 | 0.0161Ω            | 0.0288Ω |  |  |

| 24                  | 0.12"                        | 0.0257Ω                   | 0.40μΗ                 | 0.0257Ω            | 0.0345Ω |  |  |

| 26                  | 0.075"                       | 0.041Ω                    | 0.42µH                 | 0.041Ω             | 0.0488Ω |  |  |

| 28                  | 0.047"                       | 0.066Ω                    | 0.45µH                 | 0.066Ω             | 0.0718Ω |  |  |

| 30                  | 0.029"                       | 0.105Ω                    | 0.49µH                 | 0.105Ω             | 0.110Ω  |  |  |

| 32                  | 0.018"                       | 0.168Ω                    | 0.53µH                 | 0.168Ω             | 0.171Ω  |  |  |

TABLE 1.

# Provide Path For IBIAS

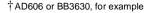

The input bias current for any DC-coupled amplifier must have an external path back to the amplifier's power supply. No such path exists in Figure 8A, and consequently the amplifier output will remain in saturation.

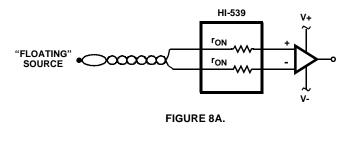

A single large resistor (1M $\Omega$  to 10M $\Omega$ ) from either signal line to power supply common will provide the required path, but a resistor on each line is necessary to preserve accuracy. A single pair of these bias current resistors on the HI-539 output may be used if their loading effect can be tolerated (each forms a voltage divider with r<sub>ON</sub>). Otherwise, a resistor pair on each input channel of the multiplexer is required.

The use of bias current resistors is acceptable only if one is confident that the sum of signal plus common-mode voltage will remain within the input range of the multiplexer/amplifier combination.

Another solution is to simply run a third wire from the low side of the signal source, as in Figure 8B. This wire assures a low common-mode voltage as well as providing the path for bias currents. Making the connection near the multiplexer will save wire, but it will also unbalance the line and reduce the amplifier's common-mode rejection.

# Differential Offset, ΔVOS

There are two major sources of  $\Delta V_{OS}$ . That part due to the expression ( $r_{ON} \Delta I_{D(ON)} + I_{D(ON)} \Delta r_{ON}$ ) becomes significant with increasing temperature, as shown in the Electrical Specifications tables. The other source of offset is the thermocouple effects due to dissimilar materials in the signal path. These include silicon, aluminum, tin, nickel-iron and (often) gold, just to exit the package.

For the thermocouple effects in the package alone, the constraint on  $\Delta V_{OS}$  may be stated in terms of a limit on the difference in temperature for package pins leading to any channel of the HI-539. For example, a difference of 0.13<sup>o</sup>C produces a 5 $\mu$ V offset. Obviously, this  $\Delta$ T effect can dominate the  $\Delta V_{OS}$  parameter at any temperature unless care is taken in mounting the HI-539 package.

Temperature gradients across the HI-539 package should be held to a minimum in critical applications. Locate the HI-539 far from heat producing components, with any air currents flowing lengthwise across the package.

NOTE: The amplifier in Figure 8A is unusable because its bias currents cannot return to the power supply. Figure 8B shows two alternative paths for these bias currents: either a pair of resistors, or (better) a third wire from the low side of the signal source.

FIGURE 8B.

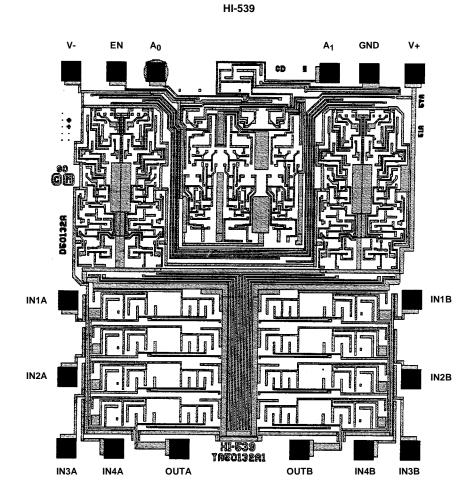

# **Die Characteristics**

### DIE DIMENSIONS:

92 mils x 100 mils

### **METALLIZATION:**

Type: AlCu Thickness: 16kÅ ±2kÅ

### SUBSTRATE POTENTIAL (NOTE):

-VSUPPLY

### PASSIVATION:

Type: Nitride Over Silox Nitride Thickness: 3.5kÅ ±1kÅ Silox Thickness: 12kÅ ±2.0kÅ

### WORST CASE CURRENT DENSITY:

2.54 x 10<sup>5</sup> A/cm<sup>2</sup> at 20mA

### TRANSISTOR COUNT:

236

# PROCESS:

CMOS-DI

NOTE: The substrate appears resistive to the -V<sub>SUPPLY</sub> terminal, therefore it may be left floating (Insulating Die Mount) or it may be mounted on a conductor at -V<sub>SUPPLY</sub> potential.

# Metallization Mask Layout

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com