# DS1033 3-in-1 Low Voltage Silicon Delay Line

#### www.dalsemi.com

### **FEATURES**

- All-silicon timing circuit

- Three independent buffered delays

- Initial delay tolerance  $\pm 1.5$  ns

- Stable and precise over temperature and voltage

- Leading and trailing edge precision preserves the input symmetry

- Standard 8-pin DIP, 8-pin SOIC

- Vapor phasing, IR and wave solderable

- Available in Tape and Reel

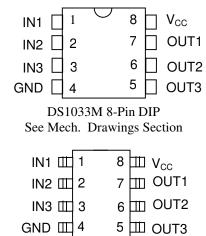

## **PIN ASSIGNMENT**

DS1033Z 8-Pin SOIC (150-mil) See Mech. Drawings Section

#### PIN DESCRIPTION

$\begin{array}{ccc} \text{IN1-IN3} & -\text{Input Signals} \\ \text{OUT1-OUT3} & -\text{Output Signals} \\ \text{NC} & -\text{No Connection} \\ \text{V}_{\text{CC}} & -\text{Supply Voltage} \\ \text{GND} & -\text{Ground} \\ \end{array}$

(Sub) - Internal substrate

connection, do not make any external connections to these pins

#### DESCRIPTION

The DS1033 series is a low-power +3.3 Volt version of the DS1035. It is characterized for operation over the range of 2.7V to 3.6V.

The DS1033 series of delay lines have three independent logic buffered delays in a single package. It is available in a standard 8-pin DIP, 150-mil 8-pin mini-SOIC.

The device features precise leading and trailing edge accuracies. It has the inherent reliability of an all-silicon delay line solution. The DS1033's nominal tolerance is  $\pm 1.5$  ns and an additional tolerance over temperature and voltage of  $\pm 1.0$  ns for the faster delays. Detailed specifications are shown in Table 1.

Standard delay values are indicated in Table 1. Customers may contact Dallas Semiconductor at (972) 371-4348 for further information.

1 of 6 111799

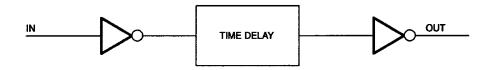

# **LOGIC DIAGRAM** Figure 1

ONE OF THREE

# PART NUMBER DELAY TABLE (t<sub>PLH</sub>, t<sub>PHL</sub>) Table 1

| PART NUMBER | DELAY PER<br>OUTPUT (ns) | INITIAL<br>TOLERANCE | TOLERANCE OVER TEMPERATURI<br>AND VOLTAGE (note 2) |                   |  |

|-------------|--------------------------|----------------------|----------------------------------------------------|-------------------|--|

| PARI NUMBER | (note 1)                 | (note 1)             | $V_{CC}$ =3.3 $V \pm 0.3V$                         | $V_{CC}$ =2.7 $V$ |  |

| DS1033-8    | 8/8/8                    | ±1.5 ns              | ±1.0 ns                                            | ±1.5 ns           |  |

| DS1033-10   | 10/10/10                 | ±1.5 ns              | ±1.0 ns                                            | ±1.5 ns           |  |

| DS1033-12   | 12/12/12                 | ±1.5 ns              | ±1.0 ns                                            | ±1.5 ns           |  |

| DS1033-15   | 15/15/15                 | ±1.5 ns              | ±1.5 ns                                            | ±2.0 ns           |  |

| DS1033-20   | 20/20/20                 | ±1.5 ns              | ±1.5 ns                                            | ±2.5 ns           |  |

| DS1033-25   | 25/25/25                 | ±2.0 ns              | ±2.0 ns                                            | ±3.5 ns           |  |

| DS1033-30   | 30/30/30                 | ±2.0 ns              | ±2.0 ns                                            | ±5.0 ns           |  |

## **NOTES:**

- 1. Nominal conditions are  $+25^{\circ}$ C and  $V_{CC}=+3.3$  volts.

- 2. Temperature range of 0°C to 70°C.

- 3. Delay accuracy is for both leading and trailing edges.

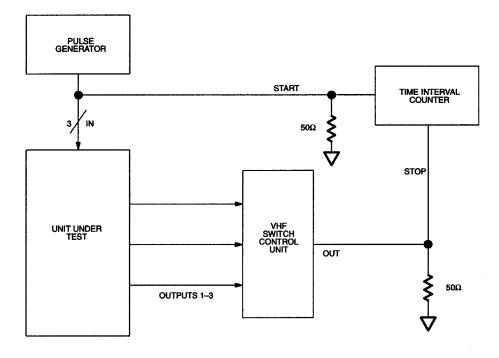

## **TEST SETUP DESCRIPTION**

Figure 2 illustrates the hardware configuration used for measuring the timing parameters of the DS1033. The input waveform is produced by a precision pulse generator under software control. Time delays are measured by a time interval counter (20 ps resolution) connected to the output. The DS1033 output taps are selected and connected to the interval counter by a VHF switch control unit. All measurements are fully automated with each instrument controlled by the computer over an IEEE 488 bus.

# **DS1033 TEST CIRCUIT** Figure 2

## **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Any Pin Relative to Ground

-1.0V to +6.0V

Operating Temperature

O°C to 70°C

Storage Temperature

-55°C to +125°C

Soldering Temperature

260°C for 10 seconds

Short Circuit Output Current

50 mA for 1 second

### DC ELECTRICAL CHARACTERISTICS

$(T_{\Delta} = 0^{\circ}C \text{ to } 70^{\circ}C)$

|                           |                 | ( A                                            |      |     |                         |       |

|---------------------------|-----------------|------------------------------------------------|------|-----|-------------------------|-------|

| PARAMETER                 | SYMBOL          | TEST                                           | MIN  | TYP | MAX                     | UNITS |

|                           |                 | CONDITION                                      |      |     |                         |       |

| Supply Voltage            | $V_{CC}$        |                                                | 2.7  | 3.3 | 3.6                     | V     |

| Active Current            | $I_{CC}$        | V <sub>CC</sub> =3.6V<br>Period=1μs            |      |     | 25                      | mA    |

| High Level Input Voltage  | $V_{ m IH}$     |                                                | 2.0  |     | V <sub>CC</sub><br>+0.5 | V     |

| Low Level Input Voltage   | $ m V_{IL}$     |                                                | -0.5 |     | 0.8                     | V     |

| Input Leakage             | $I_L$           | $0V \le V_I \le V_{CC}$                        | -1.0 |     | 1.0                     | μΑ    |

| High Level Output Current | І <sub>ОН</sub> | $V_{\text{CC}}$ =2.7V<br>$V_{\text{OH}}$ =2V   |      |     | -1.0                    | mA    |

| Low Level Output Current  | $I_{OL}$        | V <sub>CC</sub> =2.7V<br>V <sub>OL</sub> =0.4V | 8    |     |                         | mA    |

### **AC ELECTRICAL CHARACTERISTICS**

$(T_A = +25^{\circ}C)$

| PARAMETER                 | SYMBOL                              | MIN                  | TYP        | MAX        | UNITS    | NOTES  |

|---------------------------|-------------------------------------|----------------------|------------|------------|----------|--------|

| Period                    | t <sub>PERIOD</sub>                 | 2 (t <sub>WI</sub> ) |            |            | ns       | 2      |

| Input Pulse Width         | $t_{ m WI}$                         | 100% of<br>Tap Delay |            |            | ns       | 2      |

| Input-to-Tap Output Delay | t <sub>PLH</sub> , t <sub>PHL</sub> |                      | Table 1    |            | ns       |        |

| Output Rise or Fall Time  | t <sub>OR</sub> , t <sub>OF</sub>   |                      | 2.0<br>3.0 | 2.5<br>3.5 | ns<br>ns | 3<br>4 |

| Power-up Time             | $t_{\mathrm{PU}}$                   |                      |            | 100        | ms       | _      |

### **CAPACITANCE**

$(T_A = +25^{\circ}C)$

| PARAMETER         | SYMBOL   | MIN | TYP | MAX | UNITS | NOTES |

|-------------------|----------|-----|-----|-----|-------|-------|

| Input Capacitance | $C_{IN}$ |     |     | 10  | pF    |       |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

### **TEST CONDITIONS**

Ambient Temperature:  $25^{\circ}\text{C} \pm 3^{\circ}\text{C}$ Supply Voltage (V<sub>CC</sub>):  $3.3\text{V} \pm 0.1\text{V}$

Input Pulse:

$\begin{aligned} & \text{High: } 3.0\text{V} \pm 0.1\text{V} \\ & \text{Low: } 0.0\text{V} \pm 0.1\text{V} \\ & \text{Source Impedance: } 50\Omega \text{ max.} \end{aligned}$

Rise and Fall Time: 3.0 ns max. - Measured between 0.6V and 2.4V.

Pulse Width: 500 ns Pulse Period: 1 µs

Output Load Capacitance: 15 pF

Output: Each output is loaded with the equivalent of one 74F04 input gate.

Data is measured at the 1.5V level on the rising and falling edges.

**Note:** The above conditions are for test only and do not restrict the devices under other data sheet conditions.

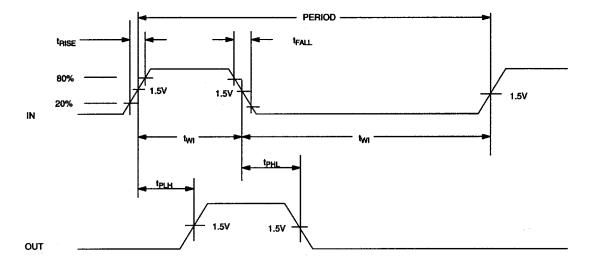

### **TIMING DIAGRAM**

#### **NOTES:**

- 1. All voltages are referenced to ground.

- 2. Pulse width and duty cycle specifications may be exceeded; however, accuracy will be application-sensitive with respect to de-coupling, layout, etc.

- 3.  $V_{CC}=3.3V \pm 10\%$ .

- 4.  $V_{CC}=2.7V$ .

#### **TERMINOLOGY**

**Period:** The time elapsed between the leading edge of the first pulse and the leading edge of the following pulse.

**t**<sub>Wl</sub>(Pulse Width): The elapsed time on the pulse between the 1.5 volt point on the leading edge and the 1.5 volt point on the trailing edge, or the 1.5 volt point on the trailing edge and the 1.5 volt point on the leading edge.

**t**<sub>RISE</sub>(Input Rise Time): The elapsed time between the 20% and the 80% point on the leading edge of the input pulse.

**t**<sub>FALL</sub>(Input Fall Time): The elapsed time between the 80% and the 20% point on the trailing edge on the input pulse.

**t**<sub>PLH</sub>(Time Delay, Rising): The elapsed time between the 1.5 volt point on the leading edge of the input pulse and the 1.5 volt point on the leading edge of the output pulse.

**t**<sub>PHL</sub>(Time Delay, Falling): The elapsed time between the 1.5 volt point on the falling edge of the input pulse and the 1.5 volt point on the falling edge of the output pulse.