**DRV2604** SLOS824C - DECEMBER 2012-REVISED MARCH 2018

# DRV2604 Haptic Driver for ERM and LRA With Internal Memory and Smart-Loop Architecture

### **Features**

- Flexible Haptic/Vibra Driver

- LRA (Linear Resonance Actuator)

- ERM (Eccentric Rotating Mass)

- I<sup>2</sup>C Controlled Digital Playback Engine

- Internal RAM for Waveform Storage

- Real-Time Playback Mode through I<sup>2</sup>C

- Smart-Loop Architecture<sup>(1)</sup>

- Automatic Overdrive/Braking (ERM/LRA)

- Automatic Resonance Tracking (LRA)

- Automatic Actuator Diagnostic (ERM/LRA)

- Automatic Level Calibration (ERM/LRA)

- Immersion TouchSense® 3000 Compatible

- Optional PWM Input with 0% to 100% Duty Cycle Control Range

- **Optional Analog Input Control**

- Optional Hardware Trigger Pin

- Efficient Output Drive

- Fast Startup Time

- Constant Acceleration Over Supply Voltage

- 1.8-V Compatible, V<sub>DD</sub>-Tolerant Digital Pins

- Patent pending control algorithm

# **Applications**

- Mobile Phones

- **Tablets**

### Description

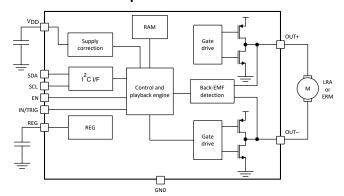

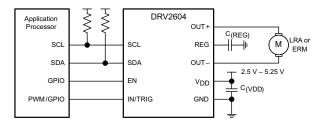

The DRV2604 device is designed to provide extremely flexible haptic control of ERM and LRA actuators over a shared I<sup>2</sup>C compatible bus. This control relieves the host processor from ever generating pulse-width modulated (PWM) signals, saving both costly timer interrupts and hardware pins.

The DRV2604 device includes enough integrated RAM to allow the user to pre-load over 100 customized waveforms. These waveforms can be instantly played back through I2C or optionally triggered through a hardware trigger pin. Additionally, the real-time playback mode allows the host processor to bypass the library playback engine and play waveforms directly from the host through I<sup>2</sup>C.

The DRV2604 device also contains a smart-loop architecture, which allows effortless auto resonant drive for LRA as well as feedback-optimized ERM drive. This feedback gives automatic overdrive and braking, which creates a simplified input waveform paradigm as well as reliable motor control and consistent motor performance.

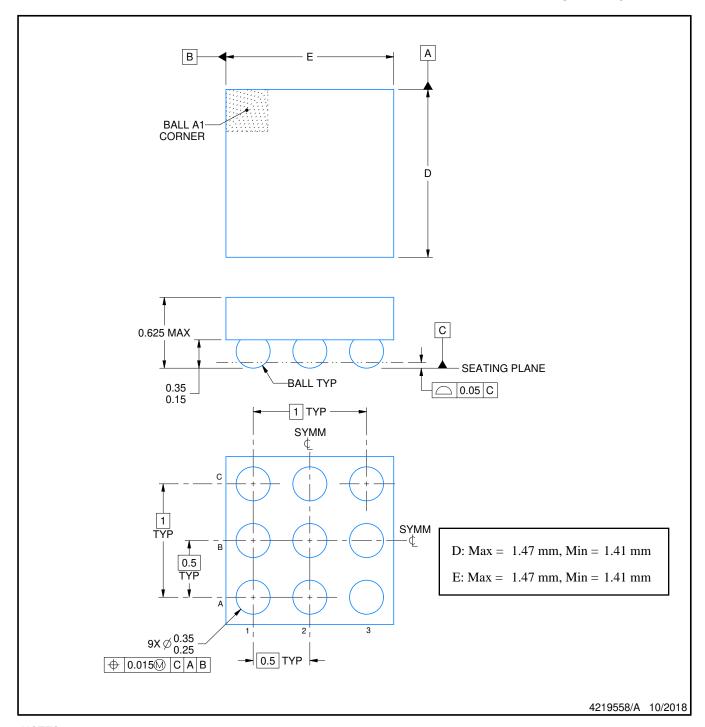

The DRV2604 device features a trinary-modulated output stage, providing greater efficiency than linearbased output drivers. The 9-ball WCSP footprint, flexible operation, and low component count make the DRV2604 device the ideal choice for portable and touch-enabled vibratory and haptic applications.

#### Device Information(1)

| PART NUMBER | BER PACKAGE BODY SIZE (MAX) |                   |

|-------------|-----------------------------|-------------------|

| DRV2604     | DSBGA (9)                   | 1.50 mm × 1.50 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

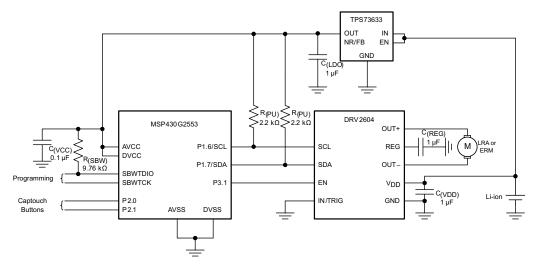

### Simplified Schematic

# **Table of Contents**

| 1 | Features 1                           |    | 7.5 Programming                                      | 20   |

|---|--------------------------------------|----|------------------------------------------------------|------|

| 2 | Applications 1                       |    | 7.6 Register Map                                     | 33   |

| 3 | Description 1                        | 8  | Application and Implementation                       | . 48 |

| 4 | Revision History2                    |    | 8.1 Application Information                          | 48   |

| 5 | Pin Configuration and Functions      |    | 8.2 Typical Application                              |      |

| 6 | Specifications4                      |    | 8.3 Initialization Setup                             | 52   |

| • | 6.1 Absolute Maximum Ratings 4       | 9  | Power Supply Recommendations                         | . 53 |

|   | 6.2 ESD Ratings                      | 10 | Layout                                               | . 54 |

|   | 6.3 Recommended Operating Conditions |    | 10.1 Layout Guidelines                               | 54   |

|   | 6.4 Thermal Information              |    | 10.2 Layout Example                                  | 55   |

|   | 6.5 Electrical Characteristics       | 11 | Device and Documentation Support                     | . 56 |

|   | 6.6 Timing Requirements              |    | 11.1 Documentation Support                           | 56   |

|   | 6.7 Switching Characteristics        |    | 11.2 Receiving Notification of Documentation Updates | s 56 |

|   | 6.8 Typical Characteristics          |    | 11.3 Community Resources                             | 56   |

| 7 | Detailed Description9                |    | 11.4 Trademarks                                      | 56   |

| • | 7.1 Overview                         |    | 11.5 Electrostatic Discharge Caution                 | 56   |

|   | 7.2 Functional Block Diagram9        |    | 11.6 Glossary                                        | 56   |

|   | 7.3 Feature Description              | 12 | 3, 1 1 1 3 3, 1 1 1 1 1 1 1 1 1 1 1 1 1              |      |

|   | 7.4 Device Functional Modes 16       |    | Information                                          | . 56 |

|   |                                      |    |                                                      |      |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cn     | nanges from Revision B (December 2015) to Revision C                                                                           | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------|------|

| •      | Changed the DEFAULT value for bit 5-4 of Table 19 From: 1 To 3                                                                 | 44   |

| •      | Changed the DEFAULT value for bit 3-2 of Table 19 From: 2 To 1                                                                 | 44   |

| •      | Changed the DEFAULT value for bit 1-0 of Table 19 From: 2 To 1                                                                 | 44   |

| •      | Changed the typical value of $C_{(VDD)}$ in Table 27 From: 0.1 $\mu F$ To: 1 $\mu F$                                           | 48   |

| •<br>_ | Changed the input-voltage supply range From: 2 V to 5.2 V To: 2.5 V to 5.5 V in the <i>Power Supply Recommendations</i> secton | 53   |

| Ch     | nanges from Revision A (July 2015) to Revision B                                                                               | Page |

| •      | Changed t <sub>h(1)</sub> Hold time, SCL to SDA from 10 ns to 50 ns in Timing Requirements                                     | 5    |

| •      | Changed the default value of NG_THRESH[1:0] from 1 to 2 in the Register Map                                                    | 45   |

| Cha | anges from Original (December 2012) to Revision A                                | Page |

|-----|----------------------------------------------------------------------------------|------|

| •   | Added Feature bullet Immersion TouchSense 3000 Compatible                        | 1    |

| •   | Updated document to new data sheet style                                         | 1    |

| •   | Full specification release                                                       | 1    |

| •   | Changed simplified schematic                                                     | 1    |

|     | Changed minimum supported resonant frequency from 50 Hz to 125 Hz                | 4    |

|     | Added digital pulldown resistance parameter to <i>Electrical Characteristics</i> | 5    |

| •   | Changed calibration diagram to include DRIVE_TIME into ERM requirements          | 24   |

|     | Changed bitfield name from "LRA_DRIVE_MODE" to "OTP_STATUS"                      |      |

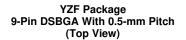

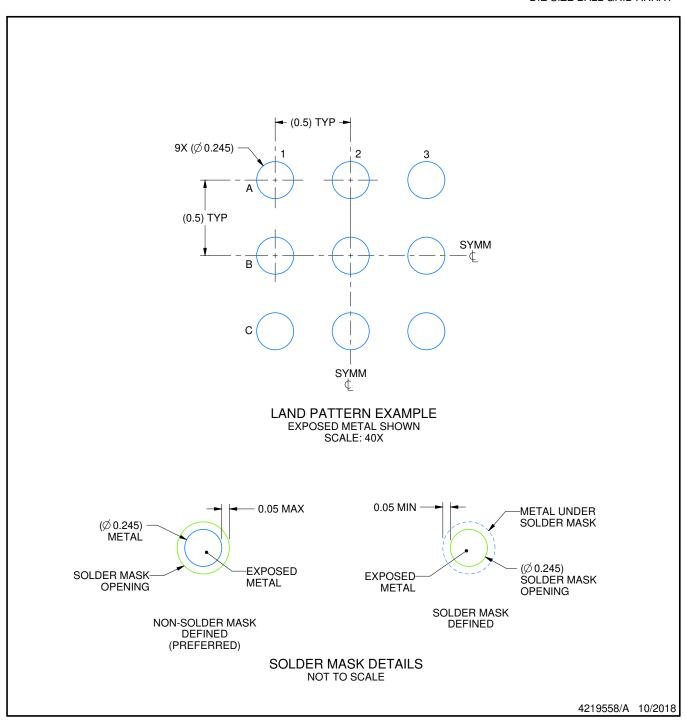

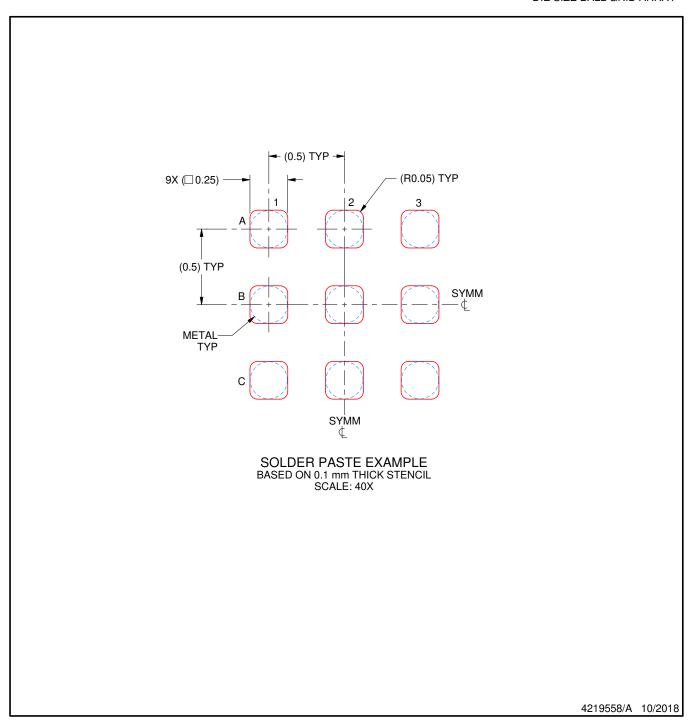

# **5 Pin Configuration and Functions**

### **Pin Functions**

| PIN |          | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                |  |  |  |

|-----|----------|---------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME     | I TPE\ /            | DESCRIPTION                                                                                                                |  |  |  |

| A1  | EN       | 1                   | Device enable                                                                                                              |  |  |  |

| A2  | REG      | 0                   | The REG pin is the 1.8-V regulator output. A 1-µF capacitor is required.                                                   |  |  |  |

| A3  | OUT+     | 0                   | Positive haptic driver differential output                                                                                 |  |  |  |

| B1  | IN/TRIG  | I                   | Multi-mode Input. I <sup>2</sup> C selectable as PWM, analog, or trigger. If not used, this pin should be connected to GND |  |  |  |

| B2  | SDA      | I/O                 | I <sup>2</sup> C data                                                                                                      |  |  |  |

| B3  | GND      | Р                   | Supply ground                                                                                                              |  |  |  |

| C1  | SCL      | I                   | I <sup>2</sup> C clock                                                                                                     |  |  |  |

| C3  | OUT-     | 0                   | Negative haptic-driver differential output                                                                                 |  |  |  |

| C2  | $V_{DD}$ | Р                   | Supply input (2.5 to 5.5 V). A 0.1-μF capacitor is required.                                                               |  |  |  |

<sup>(1)</sup> I = input, O = output, I/O = input and output, P = power

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range, T<sub>A</sub> = 25°C (unless otherwise noted)

|                        |                           | MIN  | MAX            | UNIT |

|------------------------|---------------------------|------|----------------|------|

|                        | $V_{DD}$                  | -0.3 | 6              | ٧    |

|                        | EN                        | -0.3 | $V_{DD} + 0.3$ | ٧    |

| Input voltage          | SDA                       | -0.3 | $V_{DD} + 0.3$ | V    |

|                        | SCL                       | -0.3 | $V_{DD} + 0.3$ | V    |

|                        | IN/TRIG                   | -0.3 | $V_{DD} + 0.3$ | ٧    |

| Operating free-air ten | nperature, T <sub>A</sub> | -40  | 85             | Ô    |

| Operating junction te  | mperature, T <sub>J</sub> | -40  | 150            | °C   |

| Storage temperature,   | T <sub>stg</sub>          | -65  | 150            | °C   |

### 6.2 ESD Ratings

|                    |                         |                                                                               | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±2000 V may actually have higher performance.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                    |                         | MIN | MAX | UNIT |

|-----------------|------------------------------------|-------------------------|-----|-----|------|

| $V_{DD}$        | Supply voltage                     | $V_{DD}$                | 2.5 | 5.5 | V    |

| $f_{(PWM)}$     | PWM input frequency (1)            | IN/TRIG Pin             | 10  | 250 | kHz  |

| Z <sub>L</sub>  | Load impedance <sup>(1)</sup>      | V <sub>DD</sub> = 5.2 V | 8   |     | Ω    |

| V <sub>IL</sub> | Digital low-level input voltage    | EN, IN/TRIG, SDA, SCL   |     | 0.5 | V    |

| $V_{IH}$        | Digital high-level input voltage   | EN, IN/TRIG, SDA, SCL   | 1.3 |     | V    |

| $V_{I(ANA)}$    | Input voltage (analog mode)        | IN/TRIG                 | 0   | 1.8 | V    |

| $f_{(LRA)}$     | LRA Frequency Range <sup>(1)</sup> |                         | 125 | 300 | Hz   |

<sup>(1)</sup> Ensured by design. Not production tested.

### 6.4 Thermal Information

|                        |                                              | DRV2604     |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | YZF (DSBGA) | UNIT |

|                        |                                              | (9-PINS)    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 145.2       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 0.9         | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 105         | °C/W |

| ФЈТ                    | Junction-to-top characterization parameter   | 5.1         | °C/W |

| ФЈВ                    | Junction-to-board characterization parameter | 103.3       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ±500 V may actually have higher performance.

### 6.5 Electrical Characteristics

$T_A = 25$ °C,  $V_{DD} = 3.6 \text{ V}$  (unless otherwise noted)

|                         | PARAMETER                                           | TEST CONDITIONS                                                                                                                | MIN | TYP  | MAX  | UNIT |

|-------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| V <sub>(REG)</sub>      | Voltage at the REG pin                              |                                                                                                                                |     | 1.84 |      | ٧    |

| I <sub>IL</sub>         | Digital low-level input current                     | EN $V_{DD} = 5.5 \text{ V}$ , $V_I = 0 \text{ V}$                                                                              |     |      | 1    | μΑ   |

|                         | Digital high level input current                    | IN/TRIG, SDA, SCL $V_{DD} = 5.5 \text{ V}, V_{I} = V_{DD}$                                                                     |     |      | 1    |      |

| l <sub>IH</sub>         | Digital high-level input current                    | EN VDD = 5.5 V, VI = VDD                                                                                                       |     |      | 3.5  | μΑ   |

| $V_{OL}$                | Digital low-level output voltage                    | SDAI <sub>OL</sub> = 4 mA                                                                                                      |     |      | 0.4  | V    |

| R <sub>(EN-GND)</sub>   | Digital pull-down resistance                        | $\begin{array}{l} \text{EN} \\ \text{V}_{\text{DD}} = 5.5 \text{ V} \text{ , V}_{\text{I}} = \text{V}_{\text{DD}} \end{array}$ |     | 2    |      | ΜΩ   |

| I <sub>(SD)</sub>       | Shutdown current                                    | V <sub>(EN)</sub> = 0 V                                                                                                        |     | 1.75 | 4    | μΑ   |

| I <sub>I(standby)</sub> | Standby current                                     | V <sub>(EN)</sub> = 1.8 V, STANDBY = 1                                                                                         |     | 1.9  | 5    | μΑ   |

| lα                      | Quiescent current                                   | V <sub>(EN)</sub> = 1.8 V, STANDBY = 0, no signal                                                                              |     | 0.6  | 1    | mA   |

| Z <sub>I</sub>          | Input impedance                                     | IN/TRIG to V <sub>(CM_ANA)</sub>                                                                                               |     | 100  |      | kΩ   |

| V <sub>(CM_ANA)</sub>   | IN/TRIG common-mode voltage (AC-coupled)            | AC_COUPLE = 1                                                                                                                  |     | 0.9  |      | V    |

| $Z_{O(SD)}$             | Output impedance in shutdown                        | OUT+ to GND, OUT- to GND                                                                                                       |     | 15   |      | kΩ   |

| Z <sub>L(th)</sub>      | Load impedance threshold for over-current detection | OUT+ to GND, OUT- to GND                                                                                                       |     | 4    |      | Ω    |

| 1                       | Average battery current during                      | Duty cycle = 90%, LRA mode, no load                                                                                            |     | 2.5  | 3.25 | Л    |

| I(BAT_AV)               | operation                                           | Duty cycle = 90%, ERM mode, no load                                                                                            |     | 2.5  | 3.25 | mA   |

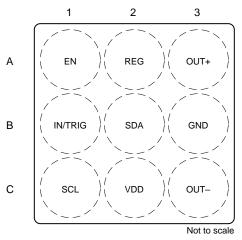

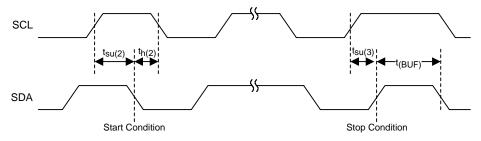

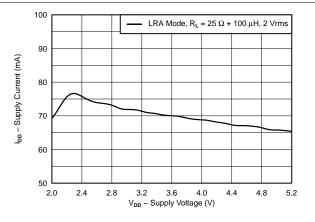

# 6.6 Timing Requirements

$T_A = 25$ °C,  $V_{DD} = 3.6 \text{ V}$  (unless otherwise noted)

|                    |                                                |               | MIN | NOM | MAX | UNIT |

|--------------------|------------------------------------------------|---------------|-----|-----|-----|------|

| $f_{(SCL)}$        | Frequency at the SCL pin with no wait sta      | ates          |     |     | 400 | kHz  |

| t <sub>w(H)</sub>  | Pulse duration, SCL high                       |               | 0.6 |     |     | μs   |

| $t_{w(L)}$         | Pulse duration, SCL low                        | Coo Figure 1  | 1.3 |     |     | μs   |

| t <sub>su(1)</sub> | Setup time, SDA to SCL                         | See Figure 1. | 100 |     |     | ns   |

| t <sub>h(1)</sub>  | Hold time, SCL to SDA                          |               | 50  |     |     | ns   |

| t <sub>(BUF)</sub> | Bus free time between stop and start condition |               | 1.3 |     |     | μs   |

| t <sub>su(2)</sub> | Setup time, SCL to start condition             | See Figure 2. | 0.6 |     |     | μs   |

| t <sub>h(2)</sub>  | Hold time, start condition to SCL              |               | 0.6 |     |     | μs   |

| t <sub>su(3)</sub> | Setup time, SCL to stop condition              |               | 0.6 |     |     | μs   |

# 6.7 Switching Characteristics

$T_A = 25$ °C,  $V_{DD} = 3.6 \text{ V}$  (unless otherwise noted)

|              | PARAMETER            | TEST CONDITIONS                                                   | MIN  | TYP  | MAX  | UNIT |

|--------------|----------------------|-------------------------------------------------------------------|------|------|------|------|

|              | Ctart up time        | Time from the GO bit or external trigger command to output signal |      | 0.7  |      |      |

| I(start)     | Start-up time        | Time from EN high to output signal (PWM/Analog Modes)             |      | 1.5  |      | ms   |

| $f_{O(PWM)}$ | PWM Output Frequency |                                                                   | 19.5 | 20.5 | 21.5 | kHz  |

Figure 1. SCL and SDA Timing

Figure 2. Timing for Start and Stop Conditions

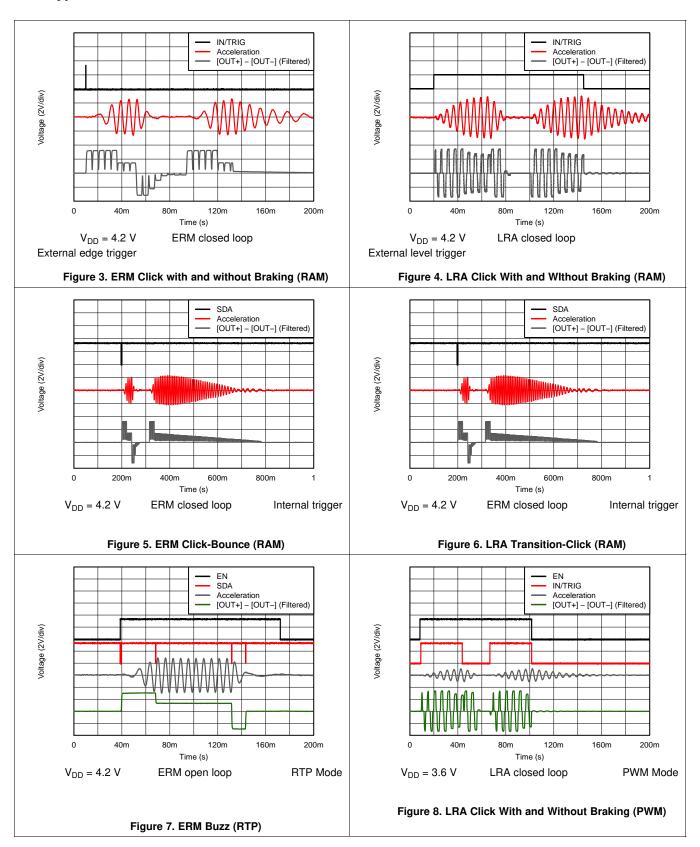

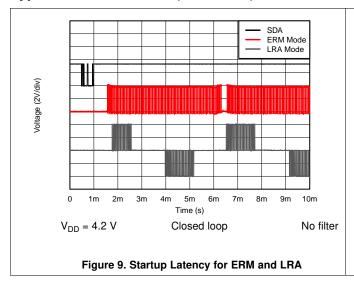

### 6.8 Typical Characteristics

Submit Documentation Feedback

# **Typical Characteristics (continued)**

Figure 10. Supply Current vs Supply Voltage (Full Vibration)

Submit Documentation Feedback

### 7 Detailed Description

#### 7.1 Overview

The DRV2604 device is a haptic driver that relies on the back-EMF produced by an actuator to provide a closed-loop system that offers extremely flexible control of LRA and ERM actuators over a shared I<sup>2</sup>C-compatible bus or PWM input signal. This schema helps improve actuator performance in terms of acceleration consistency, start time, and brake time.

The improved smart-loop architecture inside the DRV2604 device provides effortless auto-resonant drive for LRA, as well as feedback-optimized ERM drive allowing for automatic overdrive and braking. These features create a simplified input waveform paradigm as well as reliable motor control and consistent motor performance. The DRV2604 device also allows for open-loop driving by using internally-generated PWM.

The DRV2604 device includes enough integrated RAM to allow the user to preload over 100 customized waveforms. The waveforms can be instantly played back through an I<sup>2</sup>C or can be triggered through a hardware trigger pin. Additionally, the real-time playback mode allows the host processor to bypass the memory playback engine and play waveforms directly from the host through the I<sup>2</sup>C.

The DRV2604 device features a trinary-modulated output stage that provides more efficiency than linear-based output drivers.

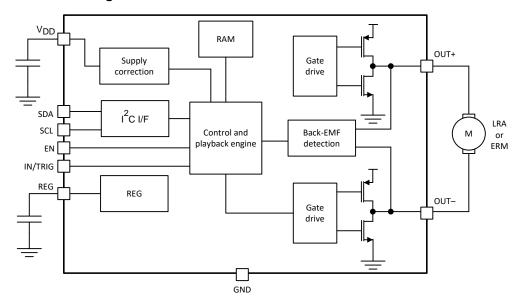

### 7.2 Functional Block Diagram

### 7.3 Feature Description

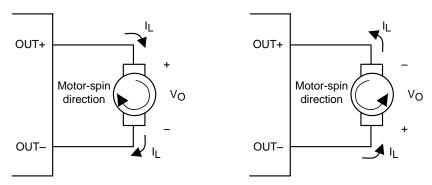

### 7.3.1 Support for ERM and LRA Actuators

The DRV2604 device supports both ERM and LRA actuators. The ERM\_LRA bit in register 0x1A must be configured to select the type of actuator that the device uses.

#### 7.3.2 Smart-Loop Architecture

The smart-loop architecture is an advanced closed-loop system that optimizes the performance of the actuator and allows for failure detection. The architecture consists of automatic resonance tracking and reporting (for an LRA), automatic level calibration, accelerated startup and braking, diagnostics routines, and other proprietary algorithms.

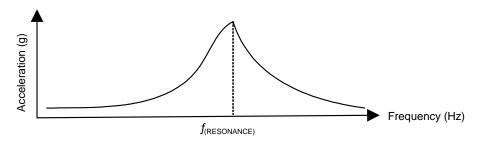

#### 7.3.2.1 Auto-Resonance Engine for LRA

The DRV2604 auto-resonance engine tracks the resonant frequency of an LRA in real time, effectively locking onto the resonance frequency after half of a cycle. If the resonant frequency shifts in the middle of a waveform for any reason, the engine tracks the frequency from cycle to cycle. The auto-resonance engine accomplishes the tracking by constantly monitoring the back-EMF of the actuator. The auto-resonance engine is not affected by the auto calibration process, which is only used for level calibration. No calibration is required for the auto resonance engine. See the *Auto-Resonance Engine Programming for the LRA* section for auto-resonance engine programming information.

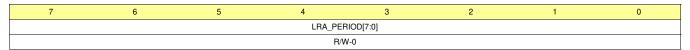

### 7.3.2.2 Real-Time Resonance-Frequency Reporting for LRA

The smart-loop architecture makes the resonant frequency of the LRA available through I<sup>2</sup>C (see the *LRA Resonance Period (Address: 0x22)* section). Because frequency reporting occurs in real time, the frequency must be polled while the DRV2604 device synchronizes with the LRA. The data should not be polled when the actuator is idle or braking.

#### 7.3.2.3 Automatic Overdrive and Braking

A key feature of the DRV2604 is the smart-loop architecture which employs actuator feedback control for both ERMs and LRAs. The feedback control desensitizes the input waveform from the motor-response behavior by providing automatic overdrive and automatic braking.

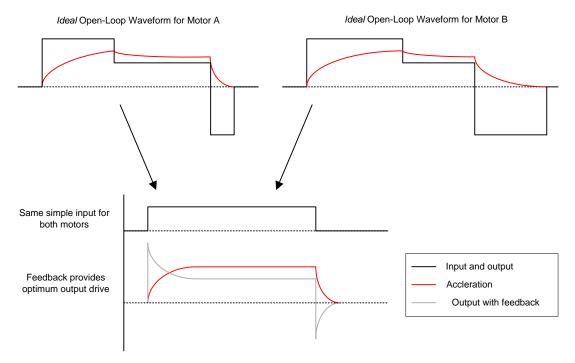

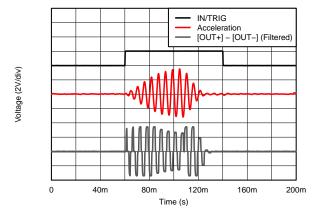

An open-loop haptic system typically drives an overdrive voltage at startup that is higher than the steady-state rated voltage of the actuator to decrease the startup latency of the actuator. Likewise, a braking algorithm must be employed for effective braking. When using an open-loop driver, these behaviors must be contained in the input waveform data. Figure 11 shows how two different ERMs with different startup behaviors (Motor A and Motor B) can both be driven optimally by the smart-loop architecture with a simple input for both motors. The smart-loop architecture works equally well for LRAs with a combination of feedback control and an autoresonance engine.

Figure 11. Waveform Simplification With Smart Loop

#### 7.3.2.3.1 Startup Boost

To reduce the actuator start-time performance, the DRV2604 device has an overdrive boost feature that applies higher loop gain to transient response of the actuator. The STARTUP\_BOOST bit enables the feature.

#### 7.3.2.3.2 Brake Factor

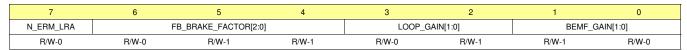

To reduce the actuator brake-time performance, the DRV2604 device provides a means to increase the gain ratio between braking and driving gain. Higher feedback-gain ratios reduce the brake time, however, the gain ratios also reduce the stability of the closed-loop system. The FB\_BRAKE\_FACTOR[2:0] bits can be adjusted to set the brake factor.

#### 7.3.2.3.3 Brake Stabilizer

To improve brake stability at high brake-factor gain ratios, the DRV2604 device has a brake-stabilizer mechanism that automatically reduces the loop gain when the braking is near completion. The BRAKE STABILIZER bit enables the feature.

#### 7.3.2.4 Automatic Level Calibration

The smart-loop architecture uses actuator feedback by monitoring the back-EMF behavior of the actuator. The level of back-EMF voltage can vary across actuator manufacturers because of the specific actuator construction. Auto calibration compensates for the variation and also performs scaling for the desired actuator according to the specified rated voltage and overdrive clamp-register settings. When auto calibration is performed, a 100% signal level at any of the DRV2604 input interfaces supplies the rated voltage to the actuator at steady-state. The feedback allows the output level to increase above the rated voltage level for automatic overdrive and braking, but without allowing the output level to exceed the programmable overdrive clamp voltage.

In the event where the automatic level-calibration routine fails, the DIAG\_RESULT bit in register 0x00 is asserted to flag the problem. Calibration failures are typically fixed by adjusting the registers associated with the automatic level-calibration routine or, for LRA actuators, the registers associated with the automatic-resonance detection engine. See the *Automatic-Level Calibration Programming* section for automatic-level calibration programming.

#### 7.3.2.4.1 Automatic Compensation for Resistive Losses

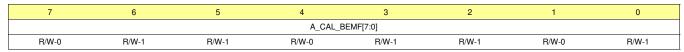

The DRV2604 device automatically compensates for resistive losses in the driver. During the automatic level-calibration routine, the impedance of the actuator is checked and the compensation factor is determined and stored in the A\_CAL\_COMP[7:0] bit.

#### 7.3.2.4.2 Automatic Back-EMF Normalization

The DRV2604 device automatically compensates for differences in back-EMF magnitude between actuators. The compensation factor is determined during the automatic level-calibration routine and the factor is stored in the A\_CAL\_BEMF[7:0] bit.

#### 7.3.2.4.3 Calibration Time Adjustment

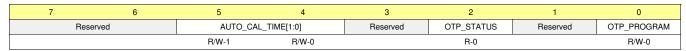

The duration of the automatic level-calibration routine has an impact on accuracy. The impact is highly dependent on the start-time characteristic of the actuator. The auto-calibration routine expects the actuator to have reached a steady acceleration before the calibration factors are calculated. Because the start-time characteristic can be different for each actuator, the AUTO\_CAL\_TIME[1:0] bit can change the duration of the automatic level-calibration routine to optimize calibration performance.

#### 7.3.2.4.4 Loop-Gain Control

The DRV2604 device allows the user to control how fast the driver attempts to match the back-EMF (and thus motor velocity) and the input signal level. Higher loop-gain (or faster settling) options result in less-stable operation than lower loop gain (or slower settling). The LOOP GAIN[1:0] bit controls the loop gain.

#### 7.3.2.4.5 Back-EMF Gain Control

The BEMF\_GAIN[1:0] bit sets the analog gain for the back-EMF amplifier. The auto-calibration routine automatically populates the bit with the most appropriate value for the actuator.

Modifying the SAMPLE\_TIME[1:0] bit also adjusts the back-EMF gain. The higher the sample time, the higher the gain.

By default, the back-EMF is sampled once during a period. In the event that a twice per-period sampling is desired, assert the LRA\_DRIVE\_MODE bit.

#### 7.3.2.5 Actuator Diagnostics

The DRV2604 device is capable of determining whether the actuator is not present (open) or shorted. If a fault is detected during the diagnostic process, the DIAG\_RESULT bit is asserted.

#### 7.3.3 Open-Loop Operation for LRA

When using the PWM input in open-loop mode, the DRV2604 device employs a fixed divider that observes the PWM signal and commutates the output drive signal at the PWM frequency divided by 128. To accomplish LRA drive, the host should drive the PWM frequency at 128 times the desired operating frequency.

#### 7.3.4 Open-Loop Operation for ERM

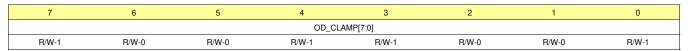

The DRV2604 device offers ERM open-loop operation through the PWM input. The output voltage is based on the duty cycle of the provided PWM signal, where the OD\_CLAMP[7:0] bit in register 0x17 sets the full-scale amplitude. For details see the *Rated Voltage Programming* section.

#### 7.3.5 Flexible Front-End Interface

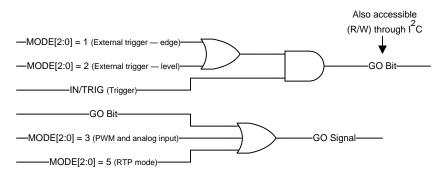

The DRV2604 device offers multiple ways to launch and control haptic effects. The MODE[2:0] bit in register 0x01 is used to select the interface mode.

#### 7.3.5.1 PWM Interface

When the DRV2604 device is in PWM interface mode, the device accepts PWM data at the IN/TRIG pin. The DRV2604 device drives the actuator continuously in PWM interface mode until the user sets the device to standby mode or to enter another interface mode. In standby mode, the strength of vibration is determined by the duty cycle.

For the LRA, the DRV2604 device automatically tracks the resonance frequency unless the LRA\_OPEN\_LOOP bit in register 0x1D is set. If the LRA\_OPEN\_LOOP bit is set, the LRA is driven according to the frequency of the PWM input signal. Specifically, the driving frequency is the PWM frequency divided by 128.

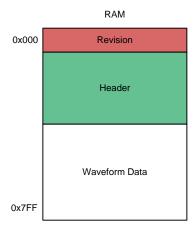

### 7.3.5.2 Internal Memory Interface

The DRV2604 device is designed with 2 kB of integrated RAM for waveform storage used by the playback engine. The data is stored in an efficient way (voltage-time pairs) to maximize the number of waveforms that can be carried. The playback engine also has the ability to generate smooth ramps (up or down) by relying on the start-waveform and end-waveform points and by using linear interpolation techniques.

Storing waveforms on the DRV2604 device instead of the host processor has several advantages including:

- · Offloading processing requirements, such as PWM generation, from the host processor or micro-controller

- · Improving latency by storing the waveforms on the DRV2604 device and only requiring a trigger signal

- Reducing I<sup>2</sup>C traffic by eliminating the requirement to transfer waveform data

#### 7.3.5.2.1 Waveform Sequencer

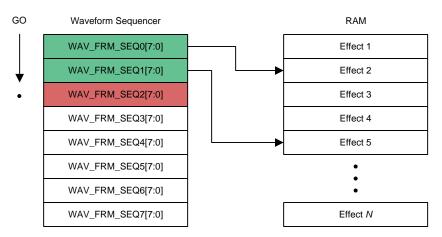

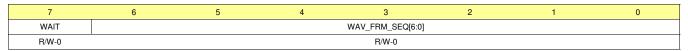

The waveform sequencer queues waveform identifiers for playback. Eight sequence registers queue up to eight waveforms for sequential playback. A waveform identifier is an integer value referring to the index position of a waveform in the RAM library. Playback begins at register address 0x04 when the user asserts the GO bit (register 0x0C). When playback of that waveform ends, the waveform sequencer plays the waveform identifier held in register 0x05 if the next waveform is non-zero. The waveform sequencer continues in this way until it reaches an identifier value of zero or until all eight identifiers are played (register addresses 0x04 through 0x0B), whichever scenario is reached first.

The waveform identifier range is 1 to 127. The MSB of each sequence register can implement a delay between sequence waveforms. When the MSB is high, bits [6:0] indicate the length of the wait time. The wait time for that step then becomes WAV FRM SEQ[6:0] × 10 ms.

### 7.3.5.2.2 Library Parameterization

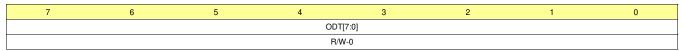

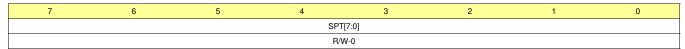

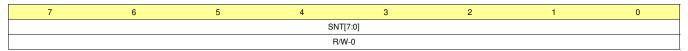

The RAM waveforms are augmented by the time offset registers (registers 0x0D to 0x10). The augmentation occurs only for the waveforms and not for the other interfaces (such as PWM and RTP). The purpose of the functionality is to add  $time\ stretching$  (or time shrinking) to the waveform. This functionality is useful for customizing the entire library of waveforms for a specific actuator rise time and fall time.

The time parameters that can be stretched or shrunk include:

**ODT** Overdrive time

SPT Sustain positive timeSNT Sustain Negative Time

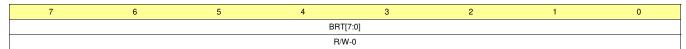

**BRT** Brake Time

The time values are additive offsets and are 8-bit signed values. The default offset of the time values is 0. Positive values add and negative values subtract from the time value of the effect that is currently played. The most positive value in the waveform is automatically interpreted as the overdrive time, and the most negative value in the waveform is automatically interpreted as the brake time. The time-offset parameters are applied to both voltage-time pairs and linear ramps. For linear ramps, linear interpolation is stretched (or shrunk) over the two operative points for the period (see Equation 1).

$t + t_{(ofs)}$ where

$t_{(ofs)}$  is the time offset (1)

#### 7.3.5.3 Real-Time Playback (RTP) Interface

The real-time playback mode is a simple, single 8-bit register interface that holds an amplitude value. When real-time playback is enabled, the real-time playback register is sent directly to the playback engine. The amplitude value is played until the user sends the device to standby mode or removes the device from RTP mode. The RTP mode operates exactly like the PWM mode except that the user enters a register value over the I<sup>2</sup>C rather than a duty cycle through the input pin. Therefore, any API (application-programming interface) designed for use with a PWM generator in the host processor can write the data values over the I<sup>2</sup>C rather than writing the data values to the host timer. This ability frees a timer in the host while retaining compatibility with the original software.

For the LRA, the DRV2604 device automatically tracks the resonance frequency.

### 7.3.5.4 Analog Input Interface

When the DRV2604 device is in analog-input interface mode, the device accepts an analog voltage at the IN/TRIG pin. The DRV2604 device drives the actuator continuously in analog-input interface mode until the user sets the device to standby mode or to enter another interface mode. The reference voltage in standby mode is 1.8 V. Therefore, the 1.8-V reference voltage is interpreted as a 100% input value. A reference voltage of 0.9 V is interpreted as a 50% input value and a reference voltage of 0 V is interpreted as a 0% input value. The input value in standby mode is analogous to the duty-cycle percentage in PWM mode.

For the LRA, the DRV2604 automatically tracks the resonance frequency.

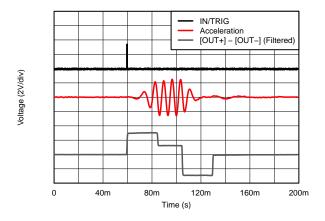

#### 7.3.5.5 Input Trigger Option

The DRV2604 device includes continuous haptic modes (such as PWM and RTP mode) as well as triggered modes (such as the internal memory interface). The haptic effects in the continuous haptic modes begin as soon as the device enters the mode and stop when the device goes into standby mode or exits the continuous haptic mode. For the triggered mode, the DRV2604 device has a variety of trigger options that are explained in this section.

In the continuous haptic modes, the IN/TRIG pin provides external trigger control of the GO bit, which allows GPIO control to fire RAM waveforms. The external trigger control can provide improved latencies in systems where a significant delay exists between the desired effect time and the time a GO command can be sent over the I<sup>2</sup>C interface.

#### **NOTE**

The triggered effect must already be selected to take advantage of the lower latency. This option works best for accelerating a pre-queued high-priority effect (such as a button press) or for the repeated firing of the same effect (such as scrolling).

#### 7.3.5.5.1 I<sup>2</sup>C Trigger

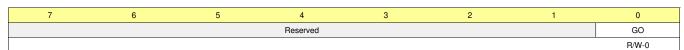

Setting the GO bit (in register 0x0C) launches the waveform. The user can cancel the launching of the waveform by clearing the GO bit.

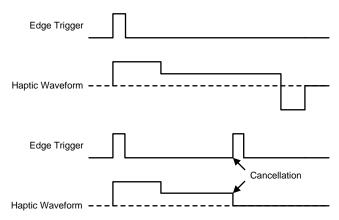

### 7.3.5.5.2 Edge Trigger

A low-to-high transition on the IN/TRIG pin sets the GO bit. The playback sequence indicated in the waveform sequencer plays as normal. The user can cancel the transaction by clearing the GO bit. An additional low-to-high transition while the GO bit is high also cancels the transaction which clears and resets the GO bit. Clearing the trigger pin (high-to-low transition) does nothing, therefore the user can send a short pulse without knowing how long the waveform is. The pulse width should be at least 1 µs to ensure detection.

Product Folder Links: DRV2604

Copyright © 2012-2018, Texas Instruments Incorporated

Figure 12. Edge Trigger Mode

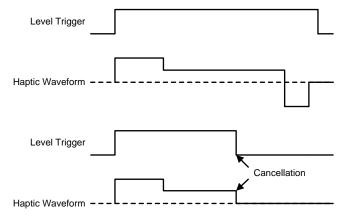

#### 7.3.5.5.3 Level Trigger

The actions of the GO bit directly follow the IN/TRIG pin. When the IN/TRIG pin is high, the GO bit is high. When the IN/TRIG pin goes low, the GO bit clears. Therefore, a falling edge cancels the transaction. The level trigger can implement a GPIO-controlled buzz on-off controller if an appropriately long waveform is selected. The user must hold the IN/TRIG high for the entire duration of the waveform to complete the effect.

Figure 13. Level Trigger Mode

#### 7.3.5.6 Noise Gate Control

When an actuator is driven with an analog or PWM signal, noise in the line can cause the actuator to vibrate unintentionally. For that reason, the DRV2604 device features a noise gate that filters out any voltage smaller than a particular threshold. The NG\_THRESH[1:0] bit in register 0x1D controls the threshold.

### 7.3.6 Edge Rate Control

The DRV2604 output driver implements edge rate control (ERC). The ERC ensures that the rise and fall characteristics of the output drivers do not emit levels of radiation that could interfere with other circuitry common in mobile and portable platforms. Because of ERC most system do not require external output filters, capacitors, or ferrite beads.

#### 7.3.7 Constant Vibration Strength

The DRV2604 PWM input uses a digital level-shifter. Therefore, as long as the input voltage meets the  $V_{IH}$  and  $V_{IL}$  levels, the vibration strength remains the same even if the digital levels vary. The DRV2604 device also features power-supply feedback. If the supply voltage drifts over time (because of battery discharge, for example), the vibration strength remains the same as long as enough supply voltage is available to sustain the required output voltage.

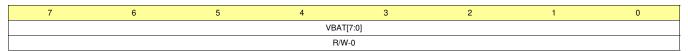

### 7.3.8 Battery Voltage Reporting

During playback, the DRV2604 device provides real-time voltage measurement of the  $V_{DD}$  pin. The VBAT[7:0] bit located in register 0x21 provides this information.

### 7.3.9 One-Time Programmable (OTP) Memory for Configuration

The DRV2604 device contains nonvolatile, on-chip, OTP memory for specific configuration parameters. When written, the DRV2604 device retains the device settings in registers 0x16 through 0x1A including after power cycling. This retention allows the user to account for small variations in actuator manufacturing from unit to unit as well as to shorten the device-initialization process for device-specific parameters such as actuator type, actuator-rated voltage, and other parameters. An additional benefit of OTP is that the DRV2604 memory can be customized at the device-test level without driving changes in the device software.

### 7.3.10 Low-Power Standby

Setting the device to standby reduces the idle power consumption without resetting the registers. In Low-Power Standby mode, the DRV2604 device features a fast turnon time when it is requested to play a waveform.

#### 7.3.11 Device Protection

#### 7.3.11.1 Thermal Protection

The DRV2604 device has thermal protection that causes the device to shut down if it becomes too hot. In the event where the thermal protection kicks in, the DRV2604 device asserts a flag (bit OVER\_TEMP in register 0x00) to notify the host processor.

#### 7.3.11.2 Overcurrent Protection of the Actuator

If the impedance at the output pin of the DRV2604 device is too low, the device latches the over-current flag (OC\_DETECT bit in register 0x00) and shuts down. The device periodically monitors the status of the short and remains in this condition until the short is removed. When the short is removed, the DRV2604 device restarts in the default state.

#### 7.4 Device Functional Modes

#### 7.4.1 Power States

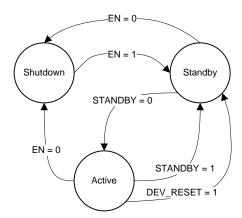

The DRV2604 device has three different power states which allow for different power-consumption levels and functions. Figure 14 shows the transition in to and out of each state.

### **Device Functional Modes (continued)**

Figure 14. Power-State Transition Diagram

#### 7.4.1.1 Operation With $V_{DD}$ < 2.5 V (Minimum $V_{DD}$ )

Operating the device with a V<sub>DD</sub> value below 2 V is not recommended.

### 7.4.1.2 Operation With $V_{DD} > 6 V$ (Absolute Maximum $V_{DD}$ )

The DRV2604 device is designed to operate at up to 5.5 V, with an absolute maximum voltage of 6 V. If exposed to voltages above 6 V, the device can suffer permanent damage.

### 7.4.1.3 Operation With EN Control

The EN pin of the DRV2604 device gates the active operation. When the EN pin is logic high, the DRV2604 device is active. When the EN pin is logic low, the device enters the shutdown state, which is the lowest power state of the device. The device registers are not reset. The EN pin operation is particularly useful for constant-source PWM and analog input modes to maintain compatibility with non-I<sup>2</sup>C device signaling. The EN pin must be high to write I<sup>2</sup>C device registers. However, if the EN pin is low the DRV2604 device can still acknowledge (ACK) during an I<sup>2</sup>C transaction, however, no read or write is possible. To completely reset the device to the powerup state, set the DEV\_RESET bit in register 0x01.

#### 7.4.1.4 Operation With STANDBY Control

The STANDBY bit in register 0x01 forces the device in an out of the standby state. The STANDBY bit is asserted by default. When the STANDBY bit is asserted, the DRV2604 device goes into a low-power state. In the standby state the device retains register values and the ability to have I<sup>2</sup>C communication. The properties of the standby state also feature a fast turn, wake up, and play, on-time. Asserting the STANDBY bit has an immediate effect. For example, if a waveform is played, it immediately stops when the STANDBY bit is asserted.

Clear the STANDBY bit to exit the standby state (and go to the ready state).

#### 7.4.1.5 Operation With DEV\_RESET Control

The DEV\_RESET bit in register 0x01 performs the equivalent of power cycling the device. Any playback operations are immediately interrupted, and all registers are reset to the default values. The Dev\_Reset bit automatically-clears after the reset operation is complete.

### 7.4.1.6 Operation in the Active State

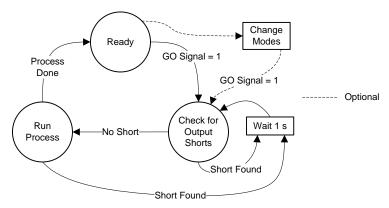

In the active state, the DRV2604 device has I<sup>2</sup>C communication and is capable of playing waveforms, running calibration, and running diagnostics. These operations are referred to as *processes*. Figure 15 shows the flow of starting, or *firing*, a process. Notice that the GO signal fires the processes. Note that the GO signal is not the same as the GO bit. Figure 16 shows a diagram of the GO-signal behavior.

### **Device Functional Modes (continued)**

Note: If an output short is present before a waveform is played, changing modes (with the MODE[2:0] bit in register 0x01) is required to resume normal playback.

Figure 15. Diagram of Active States

#### 7.4.2 Changing Modes of Operation

The DRV2604 has multiple modes for playing waveforms, as well as a calibration mode and a diagnostic mode. Table 1 lists the available modes.

MODE MODE[2:0] N PWM ANALOG Internal trigger mode Χ External Trigger mode (edge) 1 Χ External trigger mode (level) 2 Χ 3 0 Analog input mode PWM mode 3 1 RTP mode 5 Χ Diagnostics mode 6 Χ Calibration mode 7 Χ

**Table 1. Mode Selection Table**

### 7.4.3 Operation of the GO Bit

The GO bit is the primary way to assert the GO signal, which fires processes in the DRV2604 device. The primary purpose of the GO bit is to fire the playback of the waveform identifiers in the waveform sequencer (registers 0x04 to 0x0B). However, The GO bit can also fire the calibration or diagnostics processes.

When using the GO bit to play waveforms in internal trigger mode, the GO bit is asserted by writing 0x01 to register 0x0C. In this case, the GO bit can be thought of as a *software trigger* for haptic waveforms. The GO bit remains high until the playback of the haptic waveform sequence is complete. Clearing the GO bit during waveform playback cancels the waveform sequence. The GO bit can also be asserted by the external trigger when in external trigger mode. The GO bit in register 0x0C mirrors the state of the external trigger.

Setting RTP mode or PWM mode also sets the GO bit. However, setting the GO bit in this way has no impact on the GO bit located in register 0x0C.

Figure 16. GO-Signal Logic

### 7.4.4 Operation During Exceptional Conditions

This section lists different exceptional conditions and the ways that the DRV2604 device operates during these conditions. This section also describes how the device goes into and out of these states.

### 7.4.4.1 Operation With No Actuator Attached

In LRA closed-loop mode, if a waveform is played without an actuator connected to the OUT+ and OUT- pins, the output pins toggle. However, the toggling frequency is not predictable. In LRA open-loop mode, the output pins toggle at the specified open-loop frequency.

#### 7.4.4.2 Operation With a Short at REG Pin

Copyright © 2012-2018, Texas Instruments Incorporated

If the REG pin is shorted to GND, the device automatically shuts down. When the short is removed, the device starts in the default condition.

### 7.4.4.3 Operation With a Short at OUT+, OUT-, or Both

If any of the output pins (OUT+ or OUT-) is shorted to  $V_{DD}$ , GND, or to each other while the device is playing a waveform, the OC\_DETECT bit is asserted and remains asserted until the short is removed. A current-protection circuit automatically enables to shutdown the current through the short.

If the driver is playing a waveform the DRV2604 device checks for shorts in the output through either a haptic-playback, auto-calibration, or diagnostics process. If the short occurs when the device is idle, the short is not detected until the device attempts to run a waveform.

### 7.5 Programming

### 7.5.1 Auto-Resonance Engine Programming for the LRA

#### 7.5.1.1 Drive-Time Programming

The resonance frequency of each LRA actuator varies based on many factors and is generally dominated by mechanical properties. The auto-resonance engine-tracking system is optimized by providing information about the resonance frequency of the actuator. The DRIVE\_TIME[4:0] bit is used as an initial guess for the half-period of the LRA. The drive time is automatically and quickly adjusted for optimum drive. For example, if the LRA has a resonance frequency of 200 Hz, then the drive time should be set to 2.5 ms.

For ERM actuators, the DRIVE\_TIME[4:0] bit controls the rate for back-EMF sampling. Lower drive times imply higher back-EMF sampling frequencies which cause higher peak-to-average ratios in the output signal, and requires more supply headroom. Higher drive times imply lower back-EMF sampling frequencies which cause the feedback to react at a slower rate.

### 7.5.1.2 Current-Dissipation Time Programming

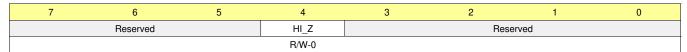

To sense the back-EMF of the actuator, the DRV2604 device goes into high impedance mode. However, before the device enters high impedance mode, the device must dissipate the current in the actuator. The DRV2604 device controls the time allocated for dissipation-current through the IDISS\_TIME[1:0] bit.

#### 7.5.1.3 Blanking Time Programming

After the current in the actuator dissipates, the DRV2604 device waits for a blanking time of the signal to settle before the back-EMF analog-to-digital (AD) conversion converts. The BLANKING TIME[1:0] bit controls this time.

#### 7.5.2 Automatic-Level Calibration Programming

#### 7.5.2.1 Rated Voltage Programming

The rated voltage is the driving voltage that the driver will output during steady state. However, in closed-loop drive mode, temporarily having an output voltage that is higher than the rated voltage is possible. See the *Overdrive Voltage-Clamp Programming* section for details.

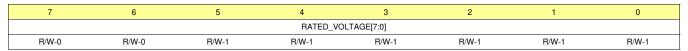

The RATED\_VOLTAGE[7:0] bit in register 0x16 sets the rated voltage for the closed-loop drive modes. For the ERM, Equation 2 calculates the average steady-state voltage when a full-scale input signal is provided. For the LRA, Equation 3 calculates the root-mean-square (RMS) voltage when driven to steady state with a full-scale input signal.

$$V_{(ERM-CL\_AV)} = 21.33 \times 10^{-3} RATED\_VOLTAGE[7:0]$$

(2)

$$V_{(LRA-CL\_RMS)} = \frac{20.71 \times 10^{-3} \times RATED\_VOLTAGE[7:0]}{\sqrt{1 - (4 \times t_{(SAMPLE\_TIME)} + 300 \times 10^{-6}) \times f_{(LRA)}}}$$

(3)

In open-loop mode, the RATED\_VOLTAGE[7:0] bit is ignored. Instead, the OD\_CLAMP[7:0] bit (in register 0x17) is used to set the rated voltage for the open-loop drive modes. For the ERM, Equation 4 calculates the rated voltage with a full-scale input signal. For the LRA, Equation 5 calculates the RMS voltage with a full-scale input signal.

$$V_{(ERM-OL_AV)} = 21.96 \times 10^{-3} \text{ OD\_CLAMP}[7:0]$$

(4)

$$V_{(LRA-OL\_RMS)} = 21.33 \times 10^{-3} \times OD\_CLAMP[7:0] \times \sqrt{1 - f_{(LRA)} \times 800 \times 10^{-6}}$$

(5)

The auto-calibration routine uses the RATED\_VOLTAGE[7:0] and OD\_CLAMP[7:0] bits as inputs and therefore these registers must be written before calibration is performed. Any modification of this register value should be followed by calibration to appropriately set A\_CAL\_BEMF[7:0].

#### 7.5.2.2 Overdrive Voltage-Clamp Programming

During closed-loop operation, the actuator feedback allows the output voltage go above the rated voltage during the automatic overdrive and automatic braking periods. The OD\_CLAMP[7:0] bit (in Register 0x17) sets a clamp so that the automatic overdrive is bounded. The OD\_CLAMP[7:0] bit also serves as the full-scale reference voltage for open-loop operation. The OD\_CLAMP[7:0] bit always represents the maximum *peak voltage* that is allowed, regardless of the mode.

#### NOTE

If the supply voltage  $(V_{DD})$  is less than the overdrive clamp voltage, the output driver is unable to reach the clamp voltage value because the output voltage cannot exceed the supply voltage. If the rated voltage exceeds the overdrive clamp voltage, the overdrive clamp voltage has priority over the rated voltage.

In ERM mode, use Equation 6 to calculate the allowed maximum voltage. In LRA mode, use Equation 7 to calculate the maximum peak voltage.

$$V_{(ERM\_clamp)} = \frac{21.33 \times 10^{-3} \times OD\_CLAMP[7:0] \times (t_{(DRIVE\_TIME)} - 300 \times 10^{-6})}{t_{(DRIVE\_TIME)} + t_{(IDISS\_TIME)} + t_{(BLANKING\_TIME)}}$$

(6)

$$V_{(LRA\_clamp)} = 21.96 \times 10^{-3} \times OD\_CLAMP[7:0]$$

(7)

#### 7.5.3 I<sup>2</sup>C Interface

### 7.5.3.1 TI Haptic Broadcast Mode

The DRV2604 device features the TI haptic broadcast mode where the DRV2604 responds to the slave address 0x58 (7-bit) or 1011000. Haptic broadcast mode is useful in the event that multiple drivers implementing the TI haptic broadcast mode are installed in the system. In such a scenario, writing the GO bit to the TI haptic broadcast slave address will cause all haptic drivers to trigger the process at the same time.

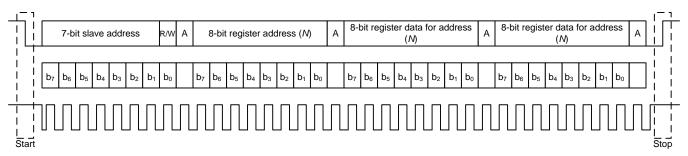

#### 7.5.3.2 General PC Operation

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. The bus transfers data serially, one bit at a time. The 8-bit address and data bytes are transferred with the most-significant bit (MSB) first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data pin (SDA) while the clock is at logic high to indicate start and stop conditions. A high-to-low transition on the SDA signal indicates a start, and a low-to-high transition indicates a stop. Normal data-bit transitions must occur within the low time of the clock period. Figure 17 shows a typical sequence. The master device generates the 7-bit slave address and the read-write (R/W) bit to start communication with a slave device. The master device then waits for an acknowledge condition. The slave device holds the SDA signal low during the acknowledge clock period to indicate acknowledgment. When this acknowledgment occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus a R/W bit (1 byte). All compatible devices share the same signals through a bidirectional bus using a wired-AND connection.

The number of bytes that can be transmitted between start and stop conditions is not limited. When the last word transfers, the master generates a stop condition to release the bus. Figure 17 shows a generic data-transfer sequence.

Use external pullup resistors for the SDA and SCL signals to set the logic-high level for the bus. Pullup resistors with values between 660  $\Omega$  and 4.7 k $\Omega$  are recommended. Do not allow the SDA and SCL voltages to exceed the DRV2604 supply voltage,  $V_{DD}$ .

#### NOTE

The DRV2604 slave address is 0x5A (7-bit), or 1011010 in binary.

Copyright © 2012–2018, Texas Instruments Incorporated

Product Folder Links: DRV2604

Figure 17. Typical I<sup>2</sup>C Sequence

The DRV2604 device operates as an  $I^2$ C-slave 1.8-V logic thresholds, but can operate up to the V<sub>DD</sub> voltage. The device address is 0x5A (7-bit), or 1011010 in binary which is equivalent to 0xB4 (8-bit) for writing and 0xB5 (8-bit) for reading.

#### 7.5.3.3 Single-Byte and Multiple-Byte Transfers

The serial control interface supports both single-byte and multiple-byte R/W operations for all registers.

During multiple-byte read operations, the DRV2604 device responds with data one byte at a time and beginning at the signed register. The device responds as long as the master device continues to respond with acknowledges.

The DRV2604 supports sequential I<sup>2</sup>C addressing. For write transactions, a sequential I<sup>2</sup>C write transaction has taken place if a register is issued followed by data for that register as well as the remaining registers that follow. For I<sup>2</sup>C sequential-write transactions, the register issued then serves as the starting point and the amount of data transmitted subsequently before a stop or start is transmitted determines how many registers are written.

#### 7.5.3.4 Single-Byte Write

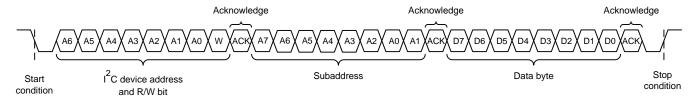

As shown in Figure 18, a single-byte data-write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read-write bit. The read-write bit determines the direction of the data transfer. For a write-data transfer, the read-write bit must be set to 0. After receiving the correct I<sup>2</sup>C device address and the read-write bit, the DRV2604 responds with an acknowledge bit. Next, the master transmits the register byte corresponding to the DRV2604 internal-memory address that is accessed. After receiving the register byte, the device responds again with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single-byte data-write transfer.

Figure 18. Single-Byte Write Transfer

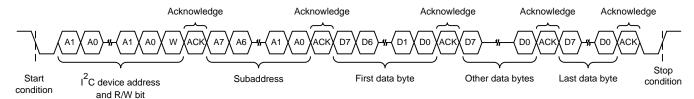

#### 7.5.3.5 Multiple-Byte Write and Incremental Multiple-Byte Write

A multiple-byte data write transfer is identical to a single-byte data write transfer except that multiple data bytes are transmitted by the master device to the DRV2604 device as shown in Figure 19. After receiving each data byte, the DRV2604 device responds with an acknowledge bit.

Figure 19. Multiple-Byte Write Transfer

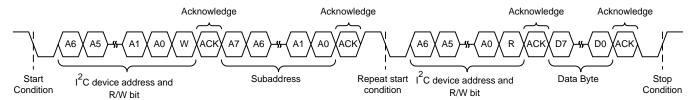

### 7.5.3.6 Single-Byte Read

Figure 20 shows that a single-byte data-read transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read-write bit. For the data-read transfer, both a write followed by a read actually occur. Initially, a write occurs to transfer the address byte of the internal memory address to be read. As a result, the read-write bit is set to 0.

After receiving the DRV2604 address and the read-write bit, the DRV2604 device responds with an acknowledge bit. The master then sends the internal memory address byte, after which the device issues an acknowledge bit. The master device transmits another start condition followed by the DRV2604 address and the read-write bit again. This time, the read-write bit is set to 1, indicating a read transfer. Next, the DRV2604 device transmits the data byte from the memory address that is read. After receiving the data byte, the master device transmits a not-acknowledge followed by a stop condition to complete the single-byte data read transfer. See the note in the *General I<sup>2</sup>C Operation* section.

Figure 20. Single-Byte Read Transfer

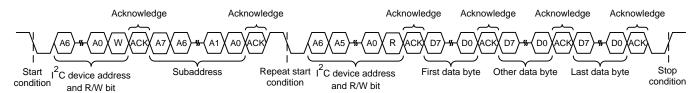

### 7.5.3.7 Multiple-Byte Read

A multiple-byte data-read transfer is identical to a single-byte data-read transfer except that multiple data bytes are transmitted by the DRV2604 device to the master device as shown in Figure 21. With the exception of the last data byte, the master device responds with an acknowledge bit after receiving each data byte.

Figure 21. Multiple-Byte Read Transfer

#### 7.5.4 Programming for Open-Loop Operation

The DRV2604 device can be used in open-loop mode and closed-loop mode. If open-loop operation is desired, the first step is to determine which actuator type is to use, either ERM or LRA.

#### 7.5.4.1 Programming for ERM Open-Loop Operation

To configure the DRV2604 device in ERM open-loop operation, the ERM must be selected by writing the N ERM LRA bit to 0 (in register 0x1A), and the ERM OPEN LOOP bit to 1 in register 0x1D.

### 7.5.4.2 Programming for LRA Open-Loop Operation

To configure the DRV2604 device in LRA open-loop operation, the LRA must be selected by writing the N\_ERM\_LRA bit to 1 in register 0x1A, and the LRA\_OPEN\_LOOP bit to 1 in register 0x1D.

### 7.5.5 Programming for Closed-Loop Operation

For closed-loop operation, the device must be calibrated according to the actuator selection. When calibrated accordingly, the user is only required to provide the desired waveform. The DRV2604 device automatically adjusts the level and, for the LRA, automatically adjusts the driving frequency.

#### 7.5.6 Auto Calibration Procedure

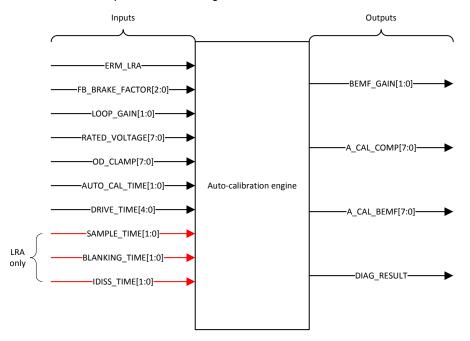

The calibration engine requires a number of bits as inputs before the engine can be executed (see Figure 22). When the inputs are configured, the calibration routine can be executed. After calibration execution occurs, the output parameters are written over the specified register locations. Figure 22 shows all of the required inputs and generated outputs. To ensure proper auto-resonance operation, the LRA actuator type requires more input parameters than the ERM. The LRA parameters are ignored when the device is in ERM mode.

Figure 22. Calibration-Engine Functional Diagram

Variation occurs between different actuators even if the actuators are of the same model. To ensure optimal results, TI recommends that the calibration routine be run at least once for each actuator. The OTP feature of the DRV2604 device can store the calibration values. Because of the stored values, the calibration procedure does not have run every time. Having a single set of calibration register values that can be loaded during the system initialization is possible.

The following instructions list the step-by-step register configuration for auto-calibration. For additional details see the *Register Map* section.

- 1. Apply the supply voltage to the DRV2604 device, and pull the EN pin high. The supply voltage should allow for adequate drive voltage of the selected actuator.

- 2. Write a value of 0x07 to register 0x01. This value moves the DRV2604 device out of STANDBY and places the MODE[2:0] bits in auto-calibration mode.

- 3. Populate the input parameters required by the auto-calibration engine:

- a. ERM LRA selection will depend on desired actuator.

- b. FB BRAKE FACTOR[2:0] A value of 2 is valid for most actuators.

- c. LOOP\_GAIN[1:0] A value of 2 is valid for most actuators.

- d. RATED\_VOLTAGE[7:0] See the *Rated Voltage Programming* section for calculating the correct register value.

- e. OD\_CLAMP[7:0] See the *Overdrive Voltage-Clamp Programming* section for calculating the correct register value.

- f. AUTO\_CAL\_TIME[1:0] A value of 3 is valid for most actuators.

- g. DRIVE\_TIME[3:0] See the *Drive-Time Programming* for calculating the correct register value.

- h. SAMPLE TIME[1:0] A value of 3 is valid for most actuators.

- i. BLANKING\_TIME[1:0] A value of 1 is valid for most actuators.

- j. IDISS\_TIME[1:0] A value of 1 is valid for most actuators.

- 4. Set the GO bit (write 0x01 to register 0x0C) to start the auto-calibration process. When auto calibration is complete, the GO bit automatically clears. The auto-calibration results are written in the respective registers as shown in Figure 22.

- 5. Check the status of the DIAG\_RESULT bit (in register 0x00) to ensure that the auto-calibration routine is complete without faults.

- 6. Evaluate system performance with the auto-calibrated settings. Note that the evaluation should occur during the final assembly of the device because the auto-calibration process can affect actuator performance and behavior. If any adjustment is required, the inputs can be modified and this sequence can be repeated. If the performance is satisfactory, the user can do any of the following:

- a. Repeat the calibration process upon subsequent power ups.

- b. Store the auto-calibration results in host processor memory and rewrite them to the DRV2604 device upon subsequent power ups. The device retains these settings when in STANDBY mode or when the EN pin is low.

- c. Program the results permanently in nonvolatile, on-chip OTP memory. Even when a device power cycle occurs, the device retains the auto-calibration settings. See the *Programming On-Chip OTP Memory* section for additional information.

#### 7.5.7 Programming On-Chip OTP Memory

The OTP memory can only be written once. To permanently program the OTP memory in registers 0x16 through 0x1A, use the following steps:

- 1. Write registers 0x16 through 0x1A with the desired configuration and calibration values which provide satisfactory performance.

- 2. Ensure that the supply voltage  $(V_{DD})$  is between 4 V and 4.4 V. This voltage is required for the nonvolatile memory to program properly.

- 3. Set the OTP\_PROGRAM bit by writing a value of 0x01 to register 0x1E. When the OTP memory is written which can only occur once in the device, the OTP\_STATUS bit (in register 0x1E) only reads 1.

- 4. Reset the device by power cycling the device or setting the DEV\_RESET bit in register 0x01, and then read registers 0x16 to 0x1A to ensure that the programmed values were retained.

### 7.5.8 Waveform Playback Programming

#### 7.5.8.1 Data Formats for Waveform Playback

The DRV2604 smart-loop architecture has three modes of operation. Each of the modes can drive either ERM or LRA devices.

- 1. Open-loop mode

- 2. Closed-loop mode (unidirectional)

- 3. Closed-loop mode (bidirectional)

Each mode has different advantages and disadvantages. The DRV2604 device brings new cutting-edge actuator control with closed-loop operation around the back-EMF for automatic overdrive and braking. However, some existing haptic implementations already include overdrive and braking that are embedded in the waveform data. Open-loop mode is used to preserve compatibility with such systems.

The following sections show how the input data for each DRV2604 interface is translated to the output drive signal.

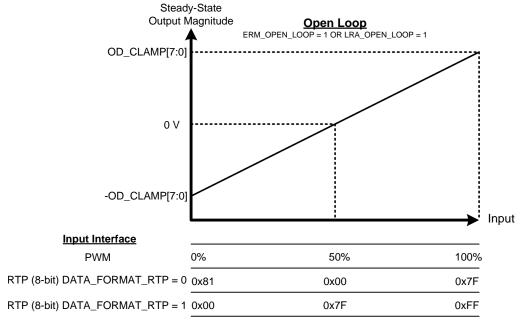

#### 7.5.8.1.1 Open-Loop Mode

In open-loop mode, the reference level for full-scale drive is set by the OD\_CLAMP[7:0] bit in Register 0x17. A mid-scale input value gives no drive signal, and a less-than mid-scale gives a negative drive value. For an ERM, a negative drive value results in counter-rotation, or braking. For an LRA, a negative drive value results in a 180-degree phase shift in commutation.

The RTP mode has 8 bits of resolution over the I<sup>2</sup>C bus. The RTP data can either be in a signed (2s complement) or unsigned format as defined by the DATA FORMAT RTP bit.

Figure 23.

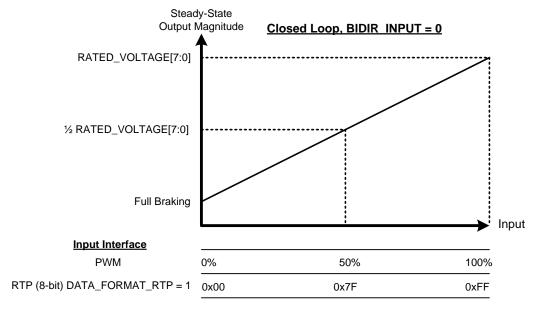

#### 7.5.8.1.2 Closed-Loop Mode, Unidirectional

In closed-loop unidirectional mode, the DRV2604 device provides automatic overdrive and braking for both ERM and LRA actuators. Closed-loop unidirectional mode is the easiest mode to use and understand. Closed-loop unidirectional mode uses the full 8-bit resolution of the driver. Closed-loop unidirectional mode offers the best performance; however, the data format is not physically compatible with the open-loop mode data that can be used in some existing systems

The reference level for steady-state full-scale drive is set by the RATED\_VOLTAGE[7:0] bit (when auto-calibration is performed). The output voltage can momentarily exceed the rated voltage for automatic overdrive and braking, but does not exceed the OD\_CLAMP[7:0] voltage. Braking occurs automatically based on the input signal when the back-EMF feedback determines that braking is necessary.

Because the system is unidirectional in closed-loop unidirectional mode, only unsigned data should be used. The RTP mode has 8 bits of resolution over the I<sup>2</sup>C bus. Setting the DATA\_FORMAT\_RTP bit to 0 (signed) is not recommended for closed-loop unidirectional mode.

Figure 24.

For the RTP interface, set the DATA FORMAT RTP bit to 1 (unsigned).

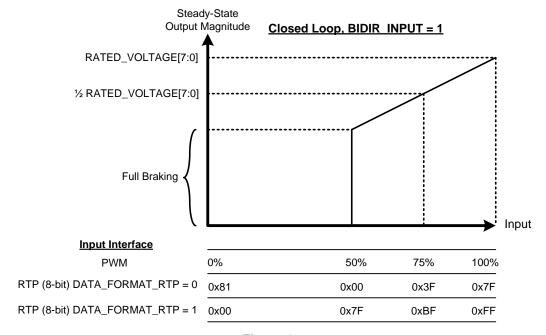

#### 7.5.8.1.3 Closed-Loop Mode, Bidirectional

In closed-loop bidirectional mode, the DRV2604 device provides automatic overdrive and braking for both ERM and LRA devices. Closed-loop bidirectional mode preserves compatibility with data created in open-loop signaling by maintaining zero drive-strength at the mid-scale value. When input values less than the mid-scale value are given, the DRV2604 device interprets them as the same as the mid-scale with zero drive.

The reference level for steady-state full-scale drive is set by the RATED\_VOLTAGE[7:0] bit (when auto calibration is performed). The output voltage can momentarily exceed the rated voltage for automatic overdrive and braking, but does not exceed the OD\_CLAMP[7:0] voltage. Braking occurs automatically based on the input signal when the back-EMF feedback determines that braking is necessary. Although the Closed-Loop mode preserves compatibility with existing device data formats, it provides closed loop benefits and is the default configuration at power up.

The RTP mode has 8 bits of resolution over the I<sup>2</sup>C bus. The RTP data can either be in signed (2s complement) or unsigned format as defined by the DATA\_FORMAT\_RTP bit.

Figure 25.

#### 7.5.8.2 Waveform Setup and Playback

Playback of a haptic effect can occur in multiple ways. Using the PWM mode, RTP mode, and analog-input mode can provide the waveform in real time. The waveforms can also be played from the RAM in which case the waveform playback engine is used and the waveform is either played by an internal GO bit (register 0x0C), or by an external trigger.

#### 7.5.8.2.1 Waveform Playback Using RTP Mode

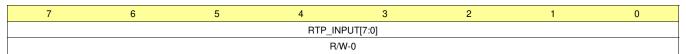

The user can enter the RTP mode by writing the MODE[2:0] bit to 5 in register 0x01. When in RTP mode, the DRV2604 device drives the actuator continuously with the amplitude specified in the RTP\_INPUT[7:0] bit (in register 0x02). Because the amplitude tracks the value specified in the RTP\_INPUT[7:0] bit, the I<sup>2</sup>C bus can stream waveforms.

### 7.5.8.2.2 Waveform Playback Using the Analog-Input Mode

The user can enter the analog-input mode by setting the MODE[2:0] bit to 3 in register 0x01 and by setting the N\_PWM\_ANALOG bit to 1 in register 0x1D. When in analog-input mode, the DRV2604 device accepts an analog voltage at the IN/TRIG pin. The DRV2604 device drives the actuator continuously in analog-input mode until the user sets the device into STANDBY mode or enters another interface mode. The reference voltage in analog-input mode is 1.8 V. Therefore a 1.8-V reference voltage is interpreted as a 100% input value, a 0.9-V reference voltage is interpreted as 50%, and a 0-V reference voltage is interpreted as 0%. The input value is analogous to the duty-cycle percentage in PWM mode. The interpretation of these percentages varies according to the selected mode of operation. See the *Data Formats for Waveform Playback* section for details.

#### 7.5.8.2.3 Waveform Playback Using PWM Mode

The user can enter the PWM mode by setting the MODE[2:0] bit to 3 in register 0x01 and by setting the N\_PWM\_ANALOG bit to 0 in register 0x1D. When in PWM mode, the DRV2604 device accepts PWM data at the IN/TRIG pin. The DRV2604 device drives the actuator continuously in PWM mode until the user sets the device to STANDBY mode or to enter another interface mode. The interpretation of the duty-cycle information varies according to the selected mode of operation. See the *Data Formats for Waveform Playback* section for details.

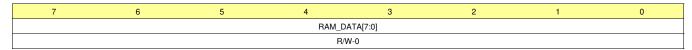

#### 7.5.8.2.4 Loading Data to RAM

The DRV2604 device contains 2 kB of integrated RAM to store customer waveforms. The waveforms are represented as time-amplitude pairs. Using the playback engine, the waveforms can be recalled, sequenced, and played through the I<sup>2</sup>C or an external GPIO trigger.

A library consists of a revision byte (should be set to 0), a header section, and the waveform data content. The library header defines the data boundaries for each effect ID in the data field, and the waveform data contains a sequence of time-value pairs that define the effects.

Figure 26. RAM Memory Structure

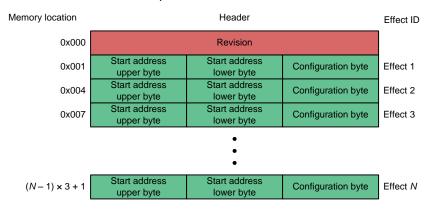

#### 7.5.8.2.4.1 Header Format

The header block consist of *N*-boundary definition blocks of 3 bytes each. *N* is the number of effects stored in the RAM. Each of the boundary definition blocks contain the start address (2 bytes) and a configuration byte.

The start address contains the location in the memory where the waveform data associated with this effect begins. The position of the effect pointer in the header becomes the effect ID. The first effect boundary definition points to the ID for effect 1, the second definition points to the ID for effect 2, and so on. This resulting effect ID is the effect ID that is used in the waveform sequencer.

Figure 27. Header Structure

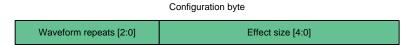

The configuration byte contains the following two parameters:

- The effect size contains the amount of bytes that define the waveform data. An effect size of 0 is an error state. Any odd-number effect size is an error state because the waveform data is defined as time-value (2 bytes). Therefore, the effect size must be an even number between 2 and 30.

- The WAVEFORM\_REPEATS[2:0] bit is used to select the number of times the complete waveform is be

played when it is called by the waveform sequencer. A value of 0 is no repeat and the waveform is played

once. A value of 1 means 1 repeat and the waveform is played twice. A value of 7 means infinite repeat until

the GO bit is cleared.

During waveform design, ensure that the appropriate amount of drive time is at zero amplitude on the end of the waveform so that the waveform stored in the RAM is repeated smoothly.

Figure 28. Header Configuration Byte Structure

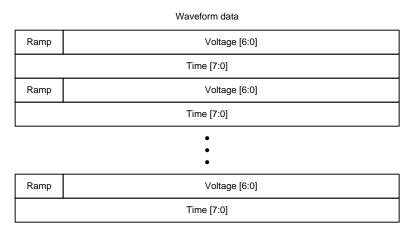

#### 7.5.8.2.4.2 RAM Waveform Data Format

The library data contents can take two forms which are voltage-time pair and linear ramp. The voltage-time pair method implements a *set and wait* protocol, which is an efficient method of actuator control for most types of waveforms. This method becomes inefficient when ramping waveforms is desired, therefore a linear ramp method is also supported which linearly interpolates a set of voltages between two amplitude values. Both methods require only two bytes of data per set point. The linear ramp method uses a minimum of four bytes so that linear interpolation can be done to the next set point. The most significant bit of the voltage value is reserved to indicate the linear ramping mode.

Figure 29. Waveform Data Structure

Data is stored as interleaved voltage-time pairs. *Voltage* in the voltage-time pair is a 7-bit signed number with range –63 to 63 when in bidirectional mode (BIDIR\_INPUT = 1), and a 7-bit unsigned number with a range of 0 to 127 when in unidirectional mode (BIDIR\_INPUT = 0). The MSB of the voltage byte is reserved for the linear ramping mode.

The *Time* value is the number of ticks that the Voltage will last, the absolute time is number of ticks × 5 ms.

When the most significant bit of the Voltage is high, the engine interprets a linear interpolation between that voltage and the following voltage point. The following voltage point can either be a part of a regular voltage-time pair, or a subsequent ramp. The following lists the sequence of bytes:

- 1. Byte1 Voltage1 (MSB High)

- 2. Byte2 Time1

- Byte3 Voltage2

- 4. Byte4 Time2

The engine creates a linear interpolation between Voltage1 and Voltage2 over the time period Time1, where Time1 is a number of 5-ms ticks. The start value for the ramp is the 7-bit value contained in Voltage1. The end amplitude is the 7-bit value contained in Voltage2. The MSB in Voltage2 can indicate a following voltage-time pair or the starting point in a subsequent ramp.

#### 7.5.8.2.5 Waveform Sequencer

If the user uses pre-stored effects, the effects must first be loaded into the waveform sequencer, and then the effects can be launched by using any of the trigger options (see the *Waveform Triggers* section for details).

The waveform sequencer (see the *Waveform Sequencer (Address: 0x04 to 0x0B)* section) queues waveform-library identifiers for playback. Eight sequence registers queue up to eight library waveforms for sequential playback. A waveform identifier is an integer value referring to the index position of a waveform in the RAM library. Playback begins at register address 0x04 when the user asserts the GO bit (register 0x0C). When playback of that waveform ends, the waveform sequencer plays the next waveform identifier held in register 0x05, if the next waveform is non-zero. The waveform sequencer continues in this way until the sequencer reaches an identifier value of zero or until all eight identifiers are played (register addresses 0x04 through 0x0B), whichever comes first.

The waveform identifier range is 1 to 127. The MSB of each sequence register can be used to implement a delay between sequence waveforms. When the MSB is high, bits 6-0 indicate the length of the wait time. The wait time for that step then becomes WAV\_FRM\_SEQ[6:0] × 10 ms.

Figure 30. Waveform Sequencer Programming

### 7.5.8.2.6 Waveform Triggers

When the waveform sequencer has the effect (or effects) loaded, the waveform sequencer can be triggered by an internal trigger, external trigger (edge), or external trigger (level). To trigger using the internal trigger set the MODE[2:0] bit to 0 in register 0x01. To trigger using the external trigger (edge), set the MODE[2:0] bit to 1 and then follow the trigger instructions listed in the *Edge Trigger* section. To trigger using the external trigger (level), set the MODE[2:0] bit to 2 and then follow the trigger instructions listed in the *Level Trigger* section.

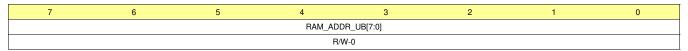

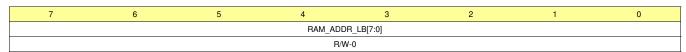

# 7.6 Register Map

# **Table 2. Register Map Overview**

| REG<br>NO. | DEFAULT | BIT 7            | BIT 6                                                                | BIT 5                | BIT 4           | BIT 3             | BIT 2           | BIT 1        | BIT 0         |  |

|------------|---------|------------------|----------------------------------------------------------------------|----------------------|-----------------|-------------------|-----------------|--------------|---------------|--|

| 0x00       | 0x80    |                  | DEVICE_ID[2:0]                                                       |                      | ILLEGAL_ADDR    | DIAG_RESULT       | FB_STS          | OVER_TEMP    | OC_DETECT     |  |