#### Not Recommended for New Designs

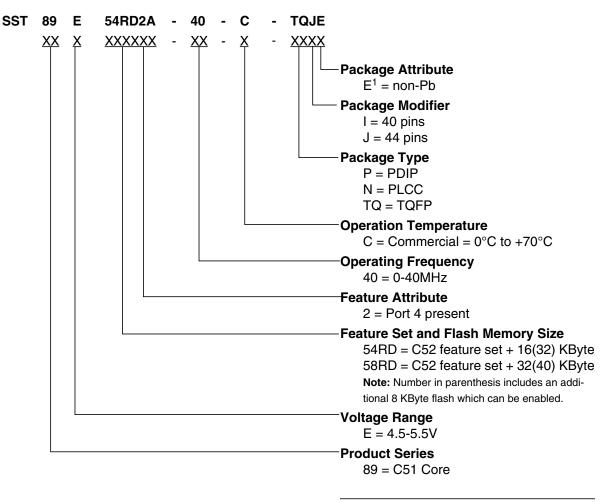

The SST89E54RD2A/RDA and SST89E58RD2A/RDA are members of the Flash-Flex family of 8-bit microcontroller products designed and manufactured with SST patented and proprietary SuperFlash CMOS semiconductor process technology. The split-gate cell design and thick-oxide tunneling injector offer significant cost and reliability benefits for SST customers. The devices use the 8051 instruction set and are pin-for-pin compatible with standard 8051 microcontroller devices.

## **Features**

- 8-bit 8051-Compatible Microcontroller (MCU) with Embedded SuperFlash Memory

- Fully Software Compatible

- Development Toolset Compatible

- Pin-For-Pin Package Compatible

- SST89E5xRD2A Operation

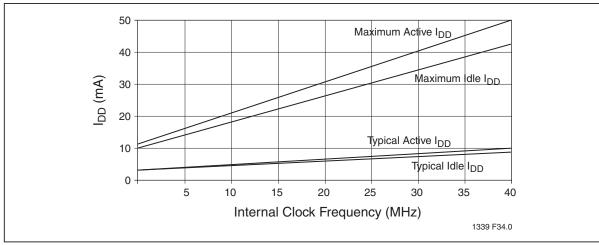

- 0 to 40 MHz at 5V

#### • 1 KByte Internal RAM

#### • Dual Block SuperFlash EEPROM

- 16/32 KByte primary block +

8 KByte secondary block

(100 Bits contary size for both

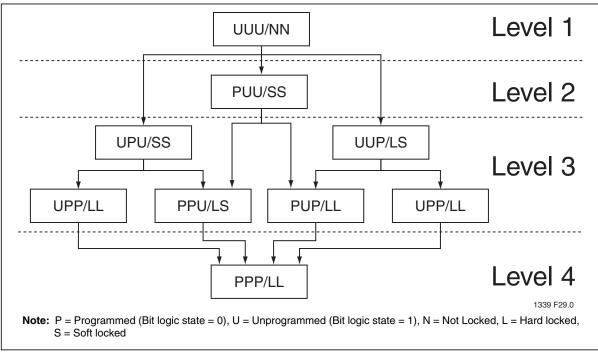

- (128-Byte sector size for both blocks) – Individual Block Security Lock with SoftLock

- Concurrent Operation during

- In-Application Programming (IAP)

- Memory Overlay for Interrupt Support during IAP

- Support External Address Range up to 64 KByte of Program and Data Memory

- Three High-Current Drive Ports (16 mA each)

- Three 16-bit Timers/Counters

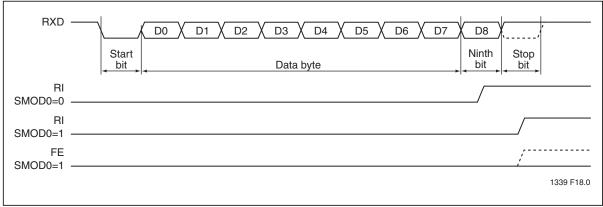

- Full-Duplex, Enhanced UART

- Framing Error Detection

- Automatic Address Recognition

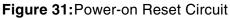

- Ten Interrupt Sources at 4 Priority Levels

- Four External Interrupt Inputs

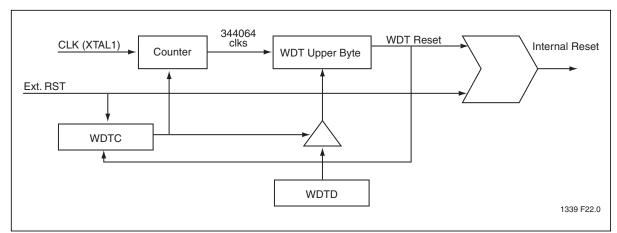

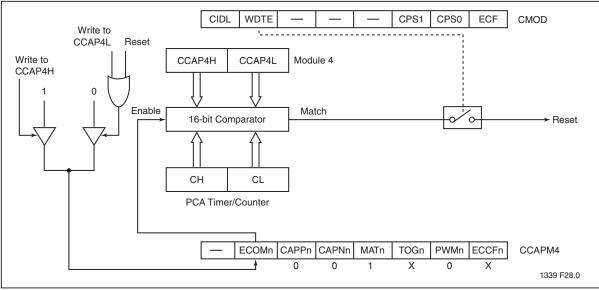

- Programmable Watchdog Timer (WDT)

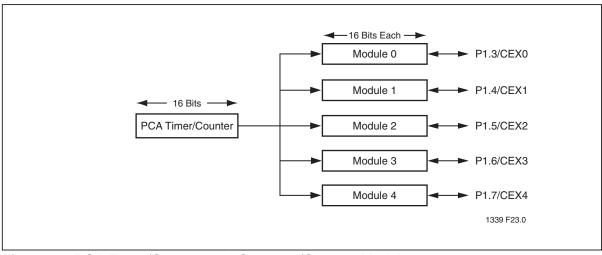

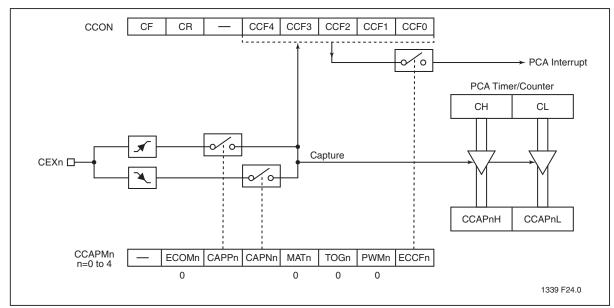

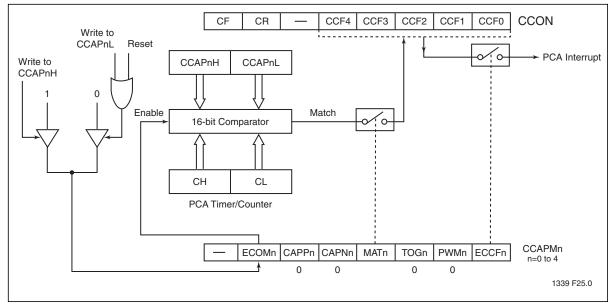

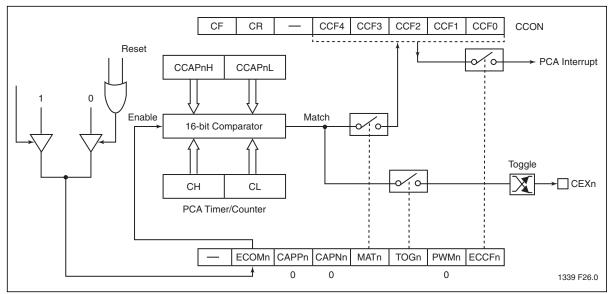

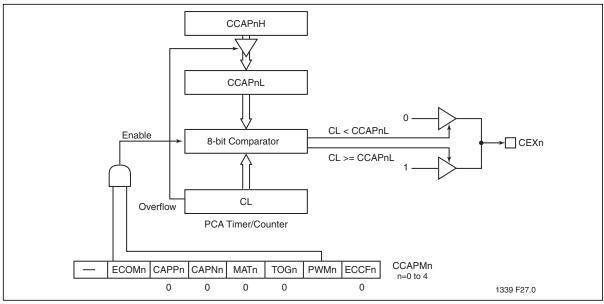

- Programmable Counter Array (PCA)

- Four 8-bit I/O Ports (32 I/O Pins) and One 4-bit Port

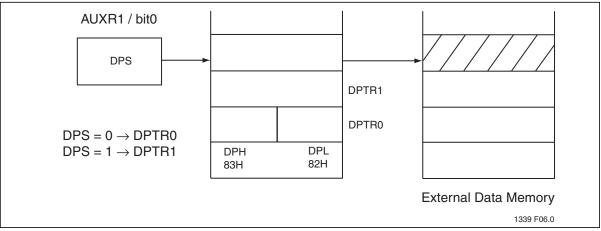

- Second DPTR register

- Low EMI Mode (Inhibit ALE)

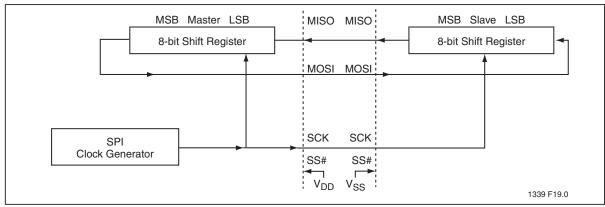

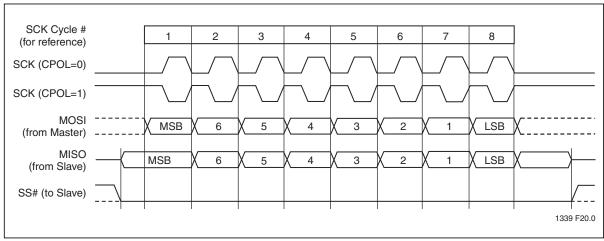

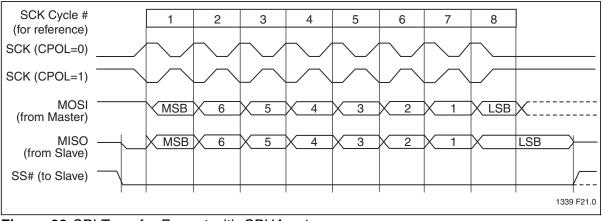

- SPI Serial Interface

- Standard 12 Clocks per cycle, the device has an option to double the speed to 6 clocks per cycle.

- TTL- and CMOS-Compatible Logic Levels

- Brown-out Detection

- Low Power Modes

- Power-down Mode with External Interrupt Wake-up

Idle Mode

- Temperature Ranges:

- Commercial (0°C to +70°C)

- Packages Available

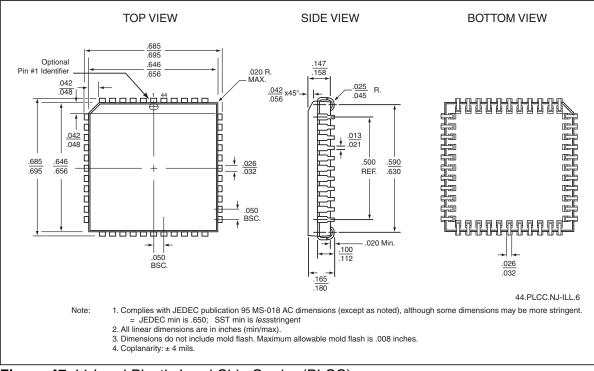

- 44-lead PLCC

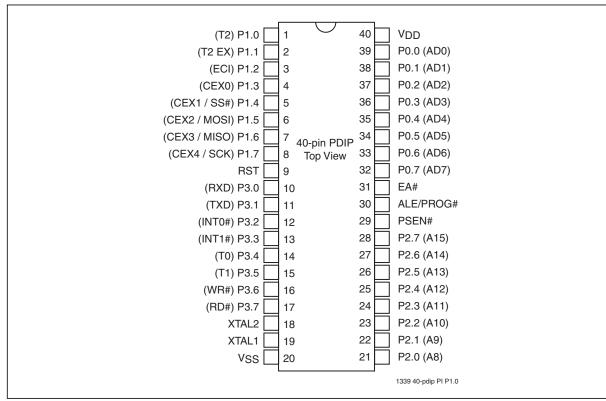

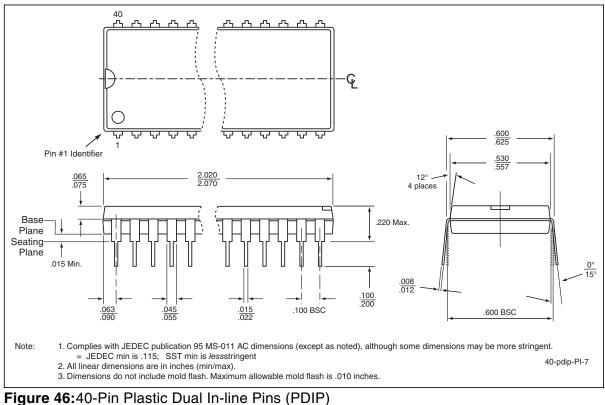

- 40-pin PDIP (Port 4 feature not available)

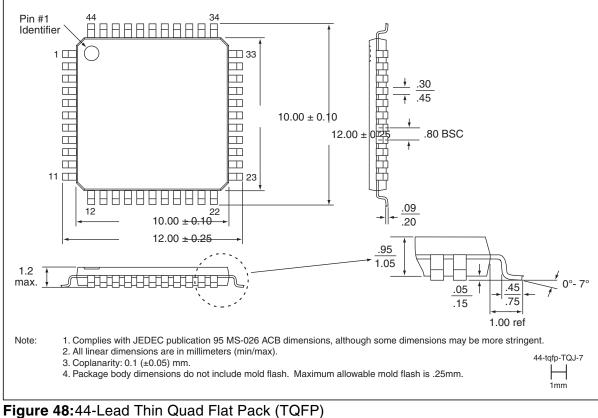

44-lead TQFP

- All non-Pb (lead-free) devices are RoHS compliant

## **Product Description**

The SST89E54RD2A/RDA and SST89E58RD2A/RDA are members of the FlashFlex family of 8-bit microcontroller products designed and manufactured with SST patented and proprietary SuperFlash CMOS semiconductor process technology. The split-gate cell design and thick-oxide tunneling injector offer significant cost and reliability benefits for SST customers. The devices use the 8051 instruction set and are pin-for-pin compatible with standard 8051 microcontroller devices.

The devices come with 24/40 KByte of on-chip flash EEPROM program memory which is partitioned into 2 independent program memory blocks. The primary Block 0 occupies 16/32 KByte of internal program memory space and the secondary Block 1 occupies 8 KByte of internal program memory space.

The 8-KByte secondary block can be mapped to the lowest location of the 16/32 KByte address space; it can also be hidden from the program counter and used as an independent EEPROM-like data memory.

In addition to the 24/40 KByte of EEPROM program memory on-chip and 1024 x8 bits of on-chip RAM, the devices can address up to 64 KByte of external program memory and up to 64 KByte of external RAM.

The flash memory blocks can be programmed via a standard 87C5x OTP EPROM programmer fitted with a special adapter and the firmware for SST devices. During power-on reset, the devices can be configured as either a slave to an external host for source code storage or a master to an external host for an in-application programming (IAP) operation. The devices are designed to be programmed in-system and in-application on the printed circuit board for maximum flexibility. The devices are pre-programmed with an example of the bootstrap loader in the memory, demonstrating the initial user program code loading or subsequent user code updating via the IAP operation. The sample bootstrap loader is available for the user's reference and convenience only; SST does not guarantee its functionality or usefulness. Chip-Erase or Block-Erase operations will erase the pre-programmed sample code.

Not Recommended for New Designs

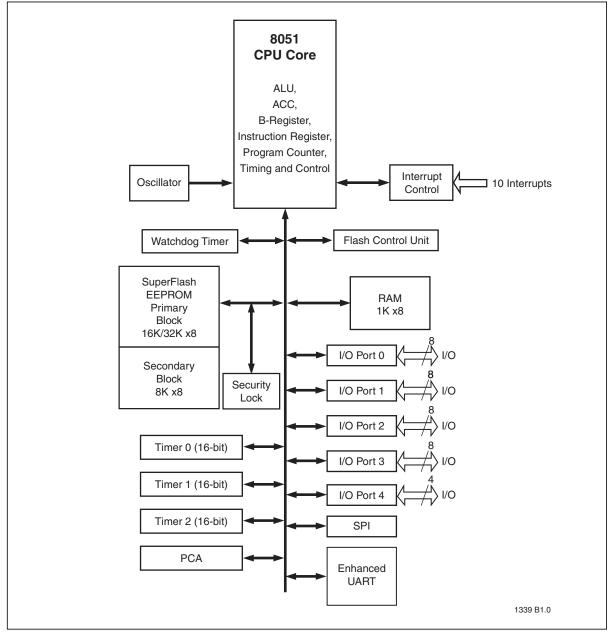

## **Functional Blocks**

Figure 1: Functional Block Diagram

## **Pin Assignments**

Figure 2: Pin Assignments for 40-pin PDIP

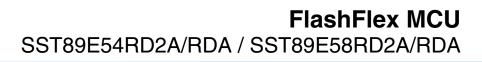

Figure 3: Pin Assignments for 44-lead TQFP

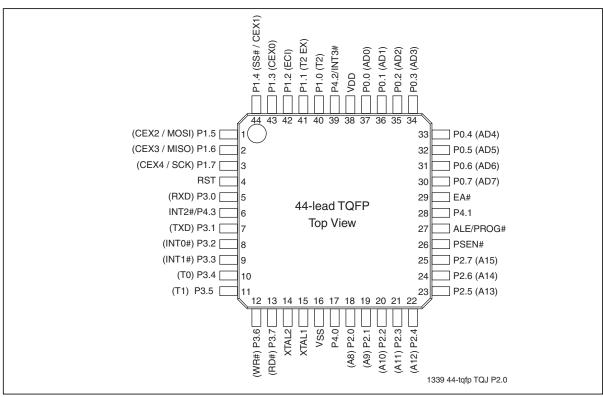

Figure 4: Pin Assignments for 44-lead PLCC

Not Recommended for New Designs

## **Pin Descriptions**

| Symbol  | Type <sup>1</sup>             | Name and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|---------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| P0[7:0] | I/O                           | <b>Port 0:</b> Port 0 is an 8-bit open drain bi-directional I/O port. As an output por each pin can sink several LS TTL inputs. Port 0 pins float that have '1's writ to them, and in this state can be used as high-impedance inputs. In this approximation, it uses strong internal pull-ups when transitioning to $V_{OH}$ . Port 0 als receives the code bytes during the external host mode programming, and puts the code bytes during the external host mode verification. External pull-ups are required during program verification.                                                                                                                                                                                   |  |  |  |  |  |

| P1[7:0] | I/O with internal<br>pull-ups | <b>Port 1:</b> Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. The Port 1 output buffers can drive LS TTL inputs. Port 1 pins are pulled high by the internal pull-ups when "1"s are written to them and can be used as inputs in this state. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pull-ups. P1[5, 6, 7] have high current drive of 16 mA. Port 1 also receives the low-order address bytes during the external host mode programming and verification.                                                                                                                                                                                         |  |  |  |  |  |

| P1[0]   | I/O                           | T2: External count input to Timer/Counter 2 or Clock-out from Timer/Counter 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| P1[1]   | I                             | T2EX: Timer/Counter 2 capture/reload trigger and direction control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| P1[2]   | I                             | <b>ECI:</b> PCA Timer/Counter External Input:<br>This signal is the external clock input for the PCA timer/counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| P1[3]   | I/O                           | <b>CEX0:</b> Compare/Capture Module External I/O<br>Each compare/capture module connects to a Port 1 pin for external I/O. When<br>not used by the PCA, this pin can handle standard I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| P1[4]   | I/O                           | SS#: Master Input or Slave Output for SPI.<br>OR<br>CEX1: Compare/Capture Module External I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| P1[5]   | I/O                           | MOSI: Master Output line, Slave Input line for SPI<br>OR<br>CEX2: Compare/Capture Module External I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| P1[6]   | I/O                           | MISO: Master Input line, Slave Output line for SPI<br>OR<br>CEX3: Compare/Capture Module External I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| P1[7]   | I/O                           | SCK: Master clock output, slave clock input line for SPI<br>OR<br>CEX4: Compare/Capture Module External I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| P2[7:0] | I/O with internal<br>pull-up  | <b>Port 2:</b> Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins are pulled high by the internal pull-ups when "1"s are written to them and can be used as inputs in this state. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 sends the high-order address byte during fetches from external Program memory and during accesses to external Data Memory that use 16-bit address (MOVX@DPTR). In this application, it uses strong internal pull-ups when transitioning to V <sub>OH</sub> . Port 2 also receives some control signals and high-order address bits during the external host mode programming and verification. |  |  |  |  |  |

Table 1: Pin Descriptions (1 of 3)

| Symbol               | Type <sup>1</sup>            | Name and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3[7:0]              | I/O with internal<br>pull-up | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can drive LS TTL inputs. Port 3 pins are pulled high by the internal pull-ups when "1"s are written to them and can be used as inputs in this state. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also receives some control signals and high-order address bits during the external host mode programming and verification.                                                                                                 |

| P3[0]                | I                            | RXD: Universal Asynchronous Receiver/Transmitter (UART) - Receive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P3[1]                | 0                            | TXD: UART - Transmit output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P3[2]                | I                            | INT0#: External Interrupt 0 Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P3[3]                | I                            | INT1#: External Interrupt 1 Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P3[4]                | I                            | T0: External count input to Timer/Counter 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P3[5]                | I                            | T1: External count input to Timer/Counter 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P3[6]                | 0                            | WR#: External Data Memory Write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P3[7]                | 0                            | RD#: External Data Memory Read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PSEN#                | I/O                          | <b>Program Store Enable:</b> PSEN# is the Read strobe to External Program Store. When the device is executing from Internal Program Memory, PSEN# is inactive (V <sub>OH</sub> ). When the device is executing code from External Program Memory, PSEN# is activated twice each machine cycle, except when access to External Data Memory while one PSEN# activation is skipped in each machine cycle. A forced high-to-low input transition on the PSEN# pin while the RST input is continually held high for more than 20 machine cycles will cause the device to enter External Host mode for programming. |

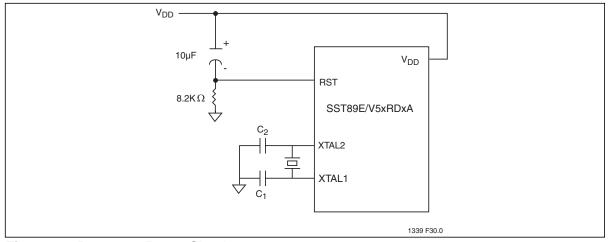

| RST                  | I                            | <b>Reset:</b> While the oscillator is running, a high logic state on this pin for two machine cycles will reset the device. After a reset, if the PSEN# pin is driven by a high-to-low input transition while the RST input pin is held high, the device will enter the External Host mode, otherwise the device will enter the Normal operation mode.                                                                                                                                                                                                                                                        |

| EA#                  | I                            | <b>External Access Enable:</b> EA# must be driven to $V_{IL}$ in order to enable the device to fetch code from the External Program Memory. EA# must be driven to $V_{IH}$ for internal program execution. However, Security lock level 4 will disable EA#, and program execution is only possible from internal program memory.                                                                                                                                                                                                                                                                              |

| ALE/PROG#            | I/O                          | <b>Address Latch Enable:</b> ALE is the output signal for latching the low byte of the address during an access to external memory. This pin is also the programming pulse input (PROG#) for flash programming. Normally the ALE <sup>2</sup> is emitted at a constant rate of 1/6 the crystal frequency <sup>3</sup> and can be used for external timing and clocking. One ALE pulse is skipped during each access to external data memory. However, if AO is set to 1, ALE is disabled.                                                                                                                     |

| P4[3:0] <sup>4</sup> | I/O with internal pull-ups   | <b>Port 4:</b> Port 4 is an 4-bit bi-directional I/O port with internal pull-ups. The port 4 output buffers can drive LS TTL inputs. Port 4 pins are pulled high by the internal pull-ups when '1's are written to them and can be used as inputs in this state. As inputs, port 4 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                  |

| P4[0]                | I/O                          | Bit 0 of port 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P4[1]                | I/O                          | Bit 1 of port 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P4[2] / INT3#        | I/O                          | Bit 2 of port 4 / INT3# External interrupt 3 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P4[3] / INT2#        | I/O                          | Bit 3 of port 4 / INT2# External interrupt 2 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Symbol          | Type <sup>1</sup> | Name and Functions                                                                                                |

|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------------|

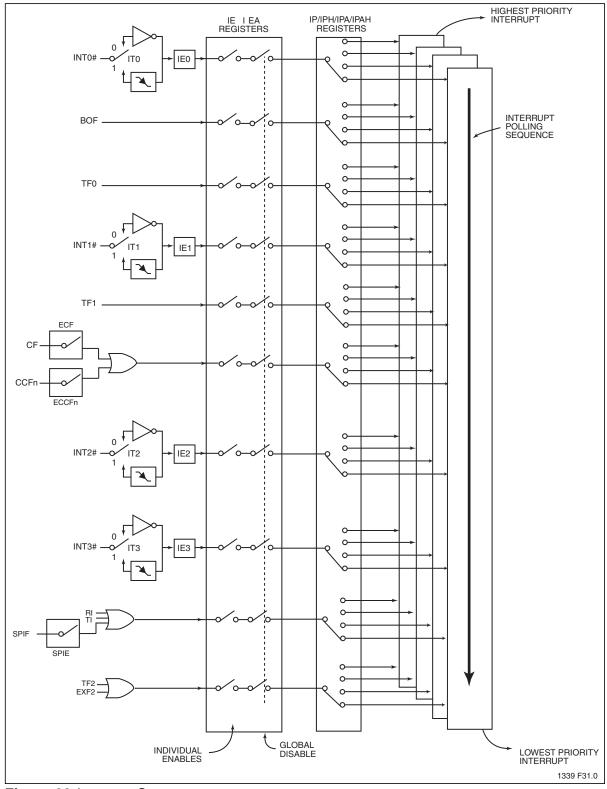

| XTAL1           | I                 | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits. |

| XTAL2           | 0                 | Crystal 2: Output from the inverting oscillator amplifier                                                         |

| V <sub>DD</sub> | I                 | Power Supply                                                                                                      |

| V <sub>SS</sub> | I                 | Ground                                                                                                            |

|                 |                   | T0-0.0 2511                                                                                                       |

#### Table 1: Pin Descriptions (Continued) (3 of 3)

1. I = Input; O = Output

2.ALE loading issue: When ALE pin experiences higher loading (>30pf) during the reset, the MCU may accidentally enter into modes other than normal working mode. The solution is to add a pull-up resistor of 3-50 K $\Omega$  to V<sub>DD</sub>, e.g. for ALE pin.

3. For 6 clock mode, ALE is emitted at 1/3 of crystal frequency.

4. Port 4 is not present on the PDIP package.

## **Memory Organization**

The device has separate address spaces for program and data memory.

## **Program Flash Memory**

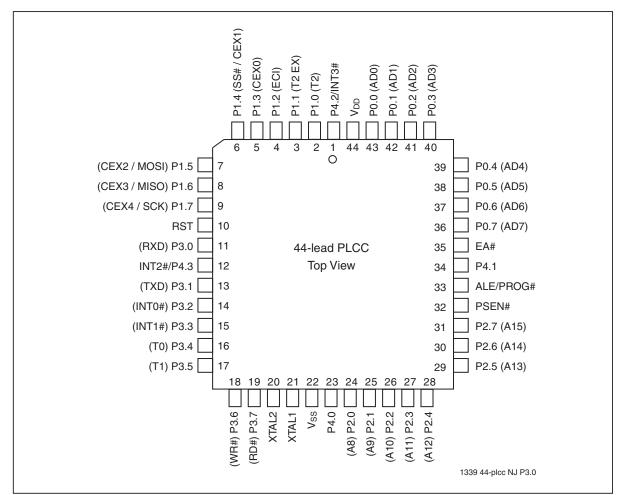

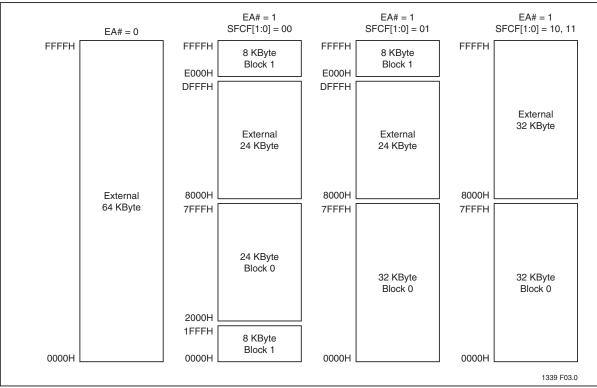

There are two internal flash memory blocks in the device. The primary flash memory block (Block 0) has 16/32 KByte. The secondary flash memory block (Block 1) has 8 KByte. Since the total program address space is limited to 64 KByte, the SFCF[1:0] bit are used to control program bank selection. Please refer to Figures 5 and 6 for the program memory configuration. Program bank selection is described in the next section.

The 16K/32K x8 primary SuperFlash block is organized as 128/256 sectors, each sector consists of 128 Bytes.

The 8K x8 secondary SuperFlash block is organized as 64 sectors, each sector consists also of 128 Bytes.

For both blocks, the 7 least significant program address bits select the byte within the sector. The remainder of the program address bits select the sector within the block.

#### Not Recommended for New Designs

Figure 6: Program Memory Organization for 32 KByte SST89E58RDxA

## **Program Memory Block Switching**

The program memory block switching feature of the device allows either Block 1 or the lowest 8 KByte of Block 0 to be used for the lowest 8 KByte of the program address space. SFCF[1:0] controls program memory block switching.

| Table 2: | SFCF | Values | for Program | Memory | y Block Switching |  |

|----------|------|--------|-------------|--------|-------------------|--|

|----------|------|--------|-------------|--------|-------------------|--|

| SFCF[1:0] | Program Memory Block Switching                                                                                                                                                                                                                                                                                                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10, 11    | Block 1 is not visible to the PC;<br>Block 1 is reachable only via in-application programming from E000H - FFFFH.                                                                                                                                                                                                                                                    |

| 01        | Both Block 0 and Block 1 are visible to the PC.<br>Block 0 is occupied from 0000H - 7FFFH. Block 1 is occupied from E000H - FFFFH.                                                                                                                                                                                                                                   |

| 00        | Block 1 is overlaid onto the low 8K of the program address space; occupying address locations<br>0000H - 1FFFH.<br>When the PC falls within 0000H - 1FFFH, the instruction will be fetched from Block 1 instead of<br>Block 0.<br>Outside of 0000H - 1FFFH, Block 0 is used. Locations 0000H - 1FFFH of Block 0 are reachable<br>through in-application programming. |

### **Reset Configuration of Program Memory Block Switching**

Program memory block switching is initialized after reset according to the state of the Start-up Configuration bit SC0 and/or SC1. The SC0 and SC1 bits are programmed via an external host mode command or an IAP Mode command. See Table 13.

Once out of reset, the SFCF[0] bit can be changed dynamically by the program for desired effects. Changing SFCF[0] will not change the SC0 bit.

Caution must be taken when dynamically changing the SFCF[0] bit. Since this will cause different physical memory to be mapped to the logical program address space. The user must avoid executing block switching instructions within the address range 0000H to 1FFFH.

|                  |                  | State of SFCF[1:0] after:     |                                 |                |  |  |  |  |  |  |

|------------------|------------------|-------------------------------|---------------------------------|----------------|--|--|--|--|--|--|

| SC1 <sup>1</sup> | SC0 <sup>1</sup> | Power-on or External<br>Reset | WDT Reset or Brown-out<br>Reset | Software Reset |  |  |  |  |  |  |

| U (1)            | U (1)            | 00 (default)                  | x0                              | 10             |  |  |  |  |  |  |

| U (1)            | P (0)            | 01                            | x1                              | 11             |  |  |  |  |  |  |

| P (0)            | U (1)            | 10                            | 10                              | 10             |  |  |  |  |  |  |

| P (0)            | P (0)            | 11                            | 11                              | 11             |  |  |  |  |  |  |

|                  | •                | •                             | · · · · ·                       | T0-0.0 25      |  |  |  |  |  |  |

#### **Table 3:** SFCF Values Under Different Reset Conditions

1. P = Programmed (Bit logic state = 0),

U = Unprogrammed (Bit logic state = 1)

## Data RAM Memory

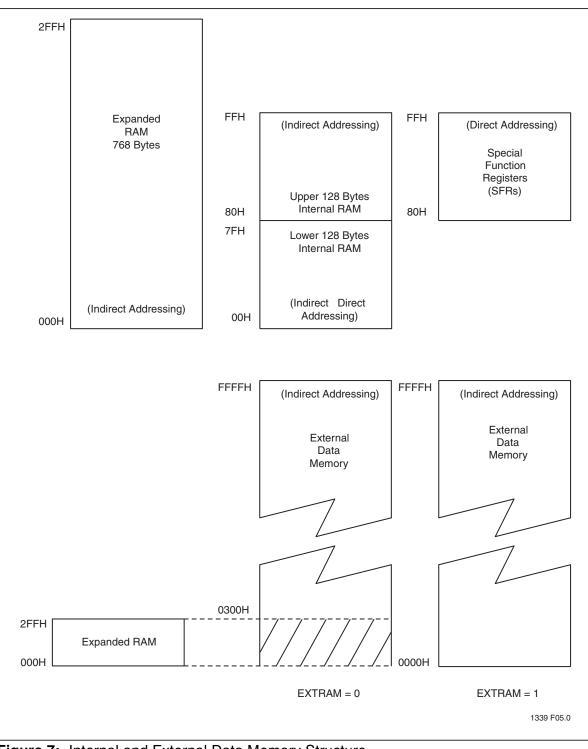

The data RAM has 1024 bytes of internal memory. The RAM can be addressed up to 64KB for external data memory.

## Expanded Data RAM Addressing

The SST89E/V5xRDxA both have the capability of 1K of RAM. See Figure 7.

The device has four sections of internal data memory:

- 1. The lower 128 Bytes of RAM (00H to 7FH) are directly and indirectly addressable.

- 2. The higher 128 Bytes of RAM (80H to FFH) are indirectly addressable.

- 3. The special function registers (80H to FFH) are directly addressable only.

- 4. The expanded RAM of 768 Bytes (00H to 2FFH) is indirectly addressable by the move external instruction (MOVX) and clearing the EXTRAM bit. (See "Auxiliary Register (AUXR)" in Section , "Special Function Registers")

Since the upper 128 bytes occupy the same addresses as the SFRs, the RAM must be accessed indirectly. The RAM and SFRs space are physically separate even though they have the same addresses.

When instructions access addresses in the upper 128 bytes (above 7FH), the MCU determines whether to access the SFRs or RAM by the type of instruction given. If it is indirect, then RAM is accessed. If it is direct, then an SFR is accessed. See the examples below.

#### Indirect Access:

MOV@R0, #data; R0 contains 90H

Register R0 points to 90H which is located in the upper address range. Data in "#data" is written to RAM location 90H rather than port 1.

#### **Direct Access:**

MOV90H, #data; write data to P1

Data in "#data" is written to port 1. Instructions that write directly to the address write to the SFRs.

To access the expanded RAM, the EXTRAM bit must be cleared and MOVX instructions must be used. The extra 768 bytes of memory is physically located on the chip and logically occupies the first 768 bytes of external memory (addresses 000H to 2FFH).

When EXTRAM = 0, the expanded RAM is indirectly addressed using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. Accessing the expanded RAM does not affect ports P0, P3.6 (WR#), P3.7 (RD#), or P2. With EXTRAM = 0, the expanded RAM can be accessed as in the following example.

#### Expanded RAM Access (Indirect Addressing only):

MOVX@DPTR, A; DPTR contains 0A0H

DPTR points to 0A0H and data in "A" is written to address 0A0H of the expanded RAM rather than external memory. Access to external memory higher than 2FFH using the MOVX instruction will access external memory (0300H to FFFFH) and will perform in the same way as the standard 8051, with P0 and P2 as data/address bus, and P3.6 and P3.7 as write and read timing signals.

When EXTRAM = 1, MOVX @Ri and MOVX @DPTR will be similar to the standard 8051. Using MOVX @Ri provides an 8-bit address with multiplexed data on Port 0. Other output port pins can be used to output higher order address bits. This provides external paging capabilities. Using MOVX

@DPTR generates a 16-bit address. This allows external addressing up the 64K. Port 2 provides the high-order eight address bits (DPH), and Port 0 multiplexes the low order eight address bits (DPL) with data. Both MOVX @Ri and MOVX @DPTR generates the necessary read and write signals (P3.6 - WR# and P3.7 - RD#) for external memory use. Table 4 shows external data memory RD#, WR# operation with EXTRAM bit.

The stack pointer (SP) can be located anywhere within the 256 bytes of internal RAM (lower 128 bytes and upper 128 bytes). The stack pointer may not be located in any part of the expanded RAM.

|            | MOVX @DPTR, A or       | MOVX @Ri, A or MOVX A, @Ri |                                     |

|------------|------------------------|----------------------------|-------------------------------------|

| AUXR       | ADDR < 0300H           | ADDR >= 0300H              | ADDR = Any                          |

| EXTRAM = 0 | RD# / WR# not asserted | RD# / WR# asserted         | RD# / WR# not asserted <sup>1</sup> |

| EXTRAM = 1 | RD# / WR# asserted     | RD# / WR# asserted         | RD# / WR# asserted                  |

#### Table 4: External Data Memory RD#, WR# with EXTRAM bit

1. Access limited to ERAM address within 0 to 0FFH; cannot access 100H to 02FFH.

A Microchip Technology Company

## **Dual Data Pointers**

The device has two 16-bit data pointers. The DPTR Select (DPS) bit in AUXR1 determines which of the two data pointers is accessed. When DPS=0, DPTR0 is selected; when DPS=1, DPTR1 is selected. Quickly switching between the two data pointers can be accomplished by a single INC instruction on AUXR1. (See Figure 8)

Figure 8: Dual Data Pointer Organization

## **Special Function Registers**

Most of the unique features of the FlashFlex microcontroller family are controlled by bits in special function registers (SFRs) located in the SFR memory map shown in Table 5. Individual descriptions of each SFR are provided and reset values indicated in Tables 6 to 10.

|     | 8 BYTES            |       |        |        |        |        |        |      |  |  |  |  |

|-----|--------------------|-------|--------|--------|--------|--------|--------|------|--|--|--|--|

| F8H | IP1 <sup>1</sup>   | СН    | CCAP0H | CCAP1H | CCAP2H | ССАРЗН | CCAP4H |      |  |  |  |  |

| F0H | B <sup>1</sup>     |       |        |        |        |        |        | IP1H |  |  |  |  |

| E8H | IEA <sup>1</sup>   | CL    | CCAP0L | CCAP1L | CCAP2L | CCAP3L | CCAP4L |      |  |  |  |  |

| E0H | ACC <sup>1</sup>   |       |        |        |        |        |        |      |  |  |  |  |

| D8H | CCON <sup>1</sup>  | CMOD  | CCAPM0 | CCAPM1 | CCAPM2 | CCAPM3 | CCAPM4 |      |  |  |  |  |

| D0H | PSW <sup>1</sup>   |       |        |        |        | SPCR   |        |      |  |  |  |  |

| C8H | T2CON <sup>1</sup> | T2MOD | RCAP2L | RCAP2H | TL2    | TH2    |        |      |  |  |  |  |

| C0H | WDTC <sup>1</sup>  |       |        |        |        |        |        |      |  |  |  |  |

| B8H | IP <sup>1</sup>    | SADEN |        |        |        |        |        |      |  |  |  |  |

| B0H | P3 <sup>1</sup>    | SFCF  | SFCM   | SFAL   | SFAH   | SFDT   | SFST   | IPH  |  |  |  |  |

| A8H | IE <sup>1</sup>    | SADDR | SPSR   |        |        |        | XICON  |      |  |  |  |  |

| A0H | P2 <sup>1</sup>    |       | AUXR1  |        |        | P4     |        |      |  |  |  |  |

| 98H | SCON <sup>1</sup>  | SBUF  |        |        |        |        |        |      |  |  |  |  |

| 90H | P1 <sup>1</sup>    |       |        |        |        |        |        |      |  |  |  |  |

| 88H | TCON <sup>1</sup>  | TMOD  | TL0    | TL1    | TH0    | TH1    | AUXR   |      |  |  |  |  |

| 80H | P0 <sup>1</sup>    | SP    | DPL    | DPH    |        | WDTD   | SPDR   | PCON |  |  |  |  |

Table 5:

FlashFlex SFR Memory Map

1. Bit addressable SFRs

#### Not Recommended for New Designs

### Table 6: CPU related SFRs

| <b>.</b> .         |                                  | Direct | ,,,,,,,,  |           |      |         |       |      |        |                |            |  |  |

|--------------------|----------------------------------|--------|-----------|-----------|------|---------|-------|------|--------|----------------|------------|--|--|

| Symb<br>ol         |                                  |        |           |           |      |         |       |      | LSB    | Reset<br>Value |            |  |  |

| ACC <sup>1</sup>   | Accumulator                      | E0H    |           | ACC[7:0]  |      |         |       |      |        |                |            |  |  |

| B <sup>1</sup>     | B Register                       | F0H    |           |           |      | B[      | 7:0]  |      |        |                | 00H        |  |  |

| PSW <sup>1</sup>   | Program Status<br>Word           | D0H    | CY        | AC        | F0   | RS1     | RS0   | OV   | F1     | Р              | 00H        |  |  |

| SP                 | Stack Pointer                    | 81H    |           |           |      | SP      | [7:0] |      |        |                | 07H        |  |  |

| DPL                | Data Pointer<br>Low              | 82H    |           | DPL[7:0]  |      |         |       |      |        |                |            |  |  |

| DPH                | Data Pointer<br>High             | 83H    |           | DPH[7:0]  |      |         |       |      |        |                |            |  |  |

| IE <sup>1</sup>    | Interrupt Enable                 | A8H    | EA        | EC        | ET2  | ES      | ET1   | EX1  | ET0    | EX0            | 00H        |  |  |

| IEA <sup>1</sup>   | Interrupt<br>Enable A            | E8H    | -         | -         | -    | -       | EBO   | -    | -      | -              | xxxx0xxxb  |  |  |

| IP <sup>1</sup>    | Interrupt Priority<br>Reg        | B8H    | -         | PPC       | PT2  | PS      | PT1   | PX1  | PT0    | PX0            | x0000000k  |  |  |

| IPH                | Interrupt Priority<br>Reg High   | B7H    | -         | PPCH      | PT2H | PSH     | PT1H  | PX1H | PT0H   | PX0H           | x0000000k  |  |  |

| IP1 <sup>1</sup>   | Interrupt Priority<br>Reg A      | F8H    | -         | -         | -    | -       | PBO   | PX3  | PX2    | -              | xxxx0xxxb  |  |  |

| IP1H               | Interrupt Priority<br>Reg A High | F7H    | -         | -         | -    | -       | PBOH  | PX3H | PX3    | -              | xxxx0xxxb  |  |  |

| PCON               | Power Control                    | 87H    | SMOD<br>1 | SMOD<br>0 | BOF  | PO<br>F | GF1   | GF0  | PD     | IDL            | 00010000k  |  |  |

| AUXR               | Auxiliary Reg                    | 8EH    | -         | -         | -    | -       | -     | -    | EXTRAM | AO             | xxxxxxx00k |  |  |

| AUXR1              | Auxiliary Reg 1                  | A2H    | -         | -         | -    | -       | GF2   | 0    | -      | DPS            | xxxx00x0b  |  |  |

| XICON <sup>2</sup> | External<br>Interrupt Control    | AEH    | х         | EX3       | IE3  | IT3     | 0     | EX2  | IE2    | IT2            | 00H        |  |  |

1. Bit Addressable SFRs

2. X = Don't care

|        |                             | Direct  | E     | Bit Address, Symbol, or Alternative Port Function                                         |       |   |       |            |     | Reset |           |  |  |

|--------|-----------------------------|---------|-------|-------------------------------------------------------------------------------------------|-------|---|-------|------------|-----|-------|-----------|--|--|

| Symbol | Description                 | Address | MSB   | MSB LSB                                                                                   |       |   |       |            |     |       |           |  |  |

| SFCF   | SuperFlash<br>Configuration | B1H     | -     | IAPEN                                                                                     | -     | - | -     | -          | SWR | BSEL  | x0xxxx00b |  |  |

| SFCM   | SuperFlash<br>Command       | B2H     | FIE   | FIE FCM[6:0]                                                                              |       |   |       |            |     |       |           |  |  |

| SFAL   | SuperFlash<br>Address Low   | B3H     | Super | SuperFlash Low Order Byte Address Register - $A_7$ to $A_0$ (SFAL)                        |       |   |       |            |     |       |           |  |  |

| SFAH   | SuperFlash<br>Address High  | B4H     | Su    | SuperFlash High Order Byte Address Register - A <sub>15</sub> to A <sub>8</sub><br>(SFAH) |       |   |       |            |     |       |           |  |  |

| SFDT   | SuperFlash<br>Data          | B5H     |       | SuperFlash Data Register                                                                  |       |   |       |            |     |       |           |  |  |

| SFST   | SuperFlash<br>Status        | B6H     | SB1_i | SB2_i                                                                                     | SB3_i | - | EDC_i | FLASH_BUSY | -   | -     | 000x00xxb |  |  |

### Table 7: Flash Memory Programming SFRs

T0-0.0 25114

### Table 8: Watchdog Timer SFRs

|                   |                               | Direct  | В   | Bit Address, Symbol, or Alternative Port Function |   |       |      |      |     |      |           |  |

|-------------------|-------------------------------|---------|-----|---------------------------------------------------|---|-------|------|------|-----|------|-----------|--|

| Symbol            | Description                   | Address | MSB |                                                   |   |       |      |      |     | LSB  | Value     |  |

| WDTC <sup>1</sup> | Watchdog Timer<br>Control     | C0H     | -   | -                                                 | - | WDOUT | WDRE | WDTS | WDT | SWDT | xxx00x00b |  |

| WDTD              | Watchdog Timer<br>Data/Reload | 85H     |     | Watchdog Timer Data/Reload                        |   |       |      |      |     |      |           |  |

1. Bit Addressable SFRs

Not Recommended for New Designs

|                              | Direct                                                                                                                                                                                                                                            | В                                                                                                                                                                                                                                                                | it Addro                                                                                                                                                                                                                                    | ess, Sy                                                                                                                                                                                                                            | mbol, c                                                                                                                                                                                                                                                          | or Alterna                                                                                                                                                                                                                                                                       | ative P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ort Fun                                                                                                                              | ction                                                                                                                                                              | Reset                                                                                                    |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Description                  | Address                                                                                                                                                                                                                                           | MSB                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                      | LSB                                                                                                                                                                | Value                                                                                                    |

| Timer/Counter                | 89H                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                  | Tim                                                                                                                                                                                                                                         | er 1                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                  | Tir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | mer 0                                                                                                                                |                                                                                                                                                                    | 00H                                                                                                      |

| Mode Control                 |                                                                                                                                                                                                                                                   | GATE                                                                                                                                                                                                                                                             | C/T#                                                                                                                                                                                                                                        | M1                                                                                                                                                                                                                                 | MO                                                                                                                                                                                                                                                               | GATE                                                                                                                                                                                                                                                                             | C/T#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | M1                                                                                                                                   | MO                                                                                                                                                                 |                                                                                                          |

| Timer/Counter<br>Control     | 88H                                                                                                                                                                                                                                               | TF1                                                                                                                                                                                                                                                              | TR1                                                                                                                                                                                                                                         | TF0                                                                                                                                                                                                                                | TR0                                                                                                                                                                                                                                                              | IE1                                                                                                                                                                                                                                                                              | IT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IE0                                                                                                                                  | IT0                                                                                                                                                                | 00H                                                                                                      |

| Timer 0 MSB                  | 8CH                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                  | TH0[7:0]                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                      |                                                                                                                                                                    | 00H                                                                                                      |

| Timer 0 LSB                  | 8AH                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                  | TL0[7:0]                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                      |                                                                                                                                                                    | 00H                                                                                                      |

| Timer 1 MSB                  | 8DH                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                  | TH1[7:0]                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                      | 00H                                                                                                                                                                |                                                                                                          |

| Timer 1 LSB                  | 8BH                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                  | TL1[7:0]                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                      | 00H                                                                                                                                                                |                                                                                                          |

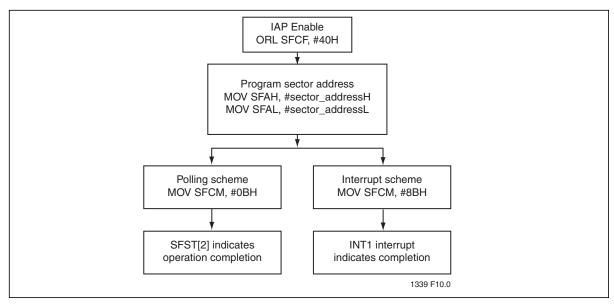

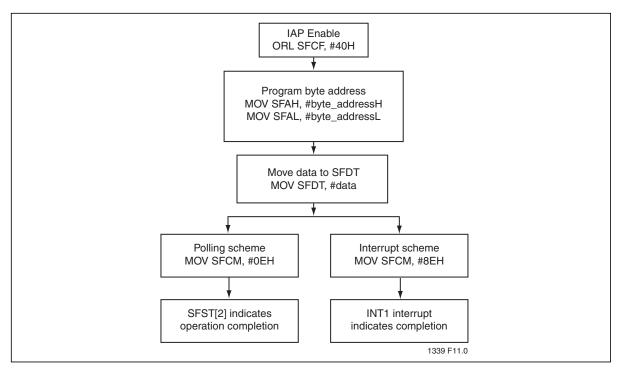

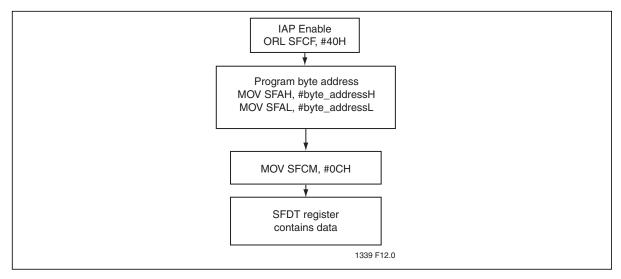

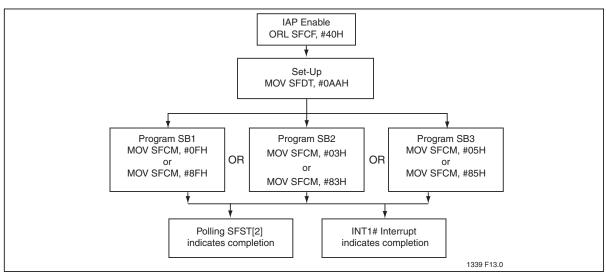

| Timer / Counter 2<br>Control | C8H                                                                                                                                                                                                                                               | TF2                                                                                                                                                                                                                                                              | EXF2                                                                                                                                                                                                                                        | RCLK                                                                                                                                                                                                                               | TCLK                                                                                                                                                                                                                                                             | EXEN2                                                                                                                                                                                                                                                                            | TR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C/T2#                                                                                                                                | CP/RL2#                                                                                                                                                            | 00H                                                                                                      |