LITE-ON SEMICONDUCTOR

LSP5523

# **3A 27V Synchronous Buck Converter**

## **General Description**

The DIODES™ LSP5523 is a monolithic synchronous buck regulator. The device integrates 90mΩ MOSFETS that provide 3A continuous load current over a wide operating input voltage of 4.5V to 27V. Current mode control provides fast transient response and cycle-by-cycle current limit. An adjustable soft-start prevents inrush current at turn on.

#### **Features**

- 3A Output Current

- Wide 4.5V to 27V Operating Input Range

- Fixed 340KHZ Frequency

- Integrated Power MOSFET Switches

- Output Adjustable from 0.925V to 0.8Vin

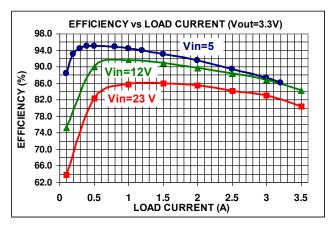

- Up to 93% Efficiency

- Programmable Soft-Start

- Stable with Low ESR Ceramic Output Capacitors

- Cycle by Cycle Over Current Protection

- Short Circuit Protection

- Input Under Voltage Lockout

- Package: ESOP-8L

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

#### **Applications**

- Distributed power systems

- Networking systems

- FPGA, DSP, ASIC power supplies

- Green electronics/ appliances

- Notebook computers

Notes:

- No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

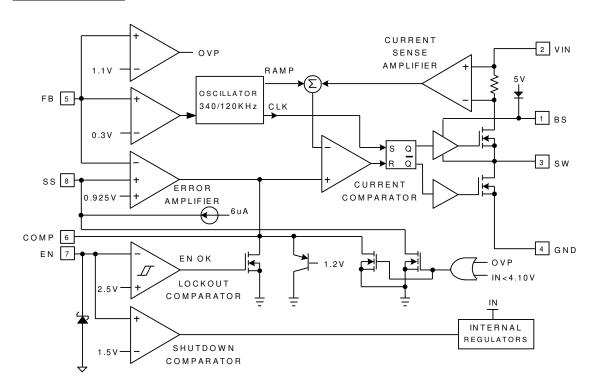

## **Block Diagram**

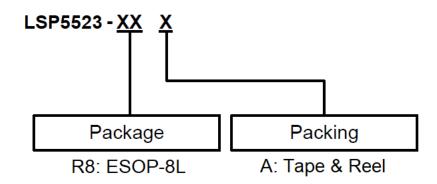

# **Ordering Information**

| Part Number | Packago | Package Code | Packing  |             |  |

|-------------|---------|--------------|----------|-------------|--|

| Part Number | Package | Fackage Code | Qty.     | Carrier     |  |

| LSP5523-R8A | ESOP-8L | R8           | 2,500pcs | Tape & Reel |  |

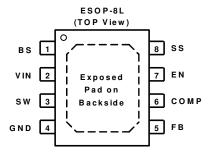

# **Pin Assignment**

# **Pin Descriptions**

| Pin Name | Name        | Pin Description                                                                                                                                                                                                                                                                 |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | BS          | Bootstrap. This pin acts as the positive rail for the high-side switch's gate driver. Connect a 0.01uF capacitor between BS and SW.                                                                                                                                             |

| 2        | VIN         | Input Supply. Bypass this pin to GND with a low ESR capacitor. See Input Capacitor in the Application Information section.                                                                                                                                                      |

| 3        | SW          | Switch Output. Connect this pin to the switching end of the inductor.                                                                                                                                                                                                           |

| 4        | GND         | Ground.                                                                                                                                                                                                                                                                         |

| 5        | FB          | Feedback Input. The voltage at this pin is regulated to 0.925V. Connect to the resistor divider between output and ground to set output voltage.                                                                                                                                |

| 6        | COMP        | Compensation Pin. See Stability Compensation in the Application Information section.                                                                                                                                                                                            |

| 7        | EN          | Enable Input. When higher than 2.7V, this pin turns the IC on. When lower than 1.1V, this pin turns the IC off. Output voltage is discharged when the IC is off. This pin should not be left open. Recommend to put a $200 \text{K}\Omega$ pull-up resistor to Vin for startup. |

| 8        | SS          | Soft-Start Control Input. SS controls the soft-start period. Connect a capacitor from SS to GND to set the soft-start period. A 0.1uF capacitor sets the soft-start period to 13ms. To disable the soft-start feature, leave SS unconnected.                                    |

| _        | Exposed Pad | Exposed Pad. Need to connect to GND pin.                                                                                                                                                                                                                                        |

## Absolute Maximum Ratings (at T<sub>A</sub>=25°C) (Note 4)

Note: Operate over the "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to such conditions for extended time may still affect the reliability of the device.

| Characteristics                                 | Value                                                   | Unit                                                               |  |  |

|-------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------|--|--|

| Input Supply Voltage                            | -0.3 to 30                                              | V                                                                  |  |  |

| SW Voltage                                      | -0.3 to V <sub>IN</sub> + 0.3                           | V                                                                  |  |  |

| BS Voltage                                      | $V_{SW} - 0.3$ to $V_{SW} + 6$                          | V                                                                  |  |  |

| EN                                              | -0.3 to 8                                               | V                                                                  |  |  |

| FB, COMP Voltage                                | -0.3 to 5                                               | V                                                                  |  |  |

| Continuous SW Current                           | Internally limited                                      | А                                                                  |  |  |

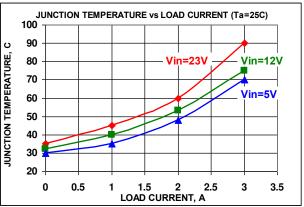

| Maximum Junction Temperature                    | 150                                                     | °C                                                                 |  |  |

| Storage Temperature Range                       | -65 to 150                                              | °C                                                                 |  |  |

| ESOP-8L Thermal Resistance(Junction to Case)    | 19                                                      | °C/W                                                               |  |  |

| ESOP-8L Thermal Resistance(Junction to Ambient) | 84                                                      | °C/W                                                               |  |  |

| ESOP-8L Power dissipation                       | 1450                                                    | mW                                                                 |  |  |

| Moisture Sensitivity (MSL)                      | Please refer the MSL label on the bag/carton for detail | Please refer the MSL label on the IC package bag/carton for detail |  |  |

Note 4: Ratings apply to ambient temperature at 25°C.

## **Recommended Operating Conditions**

| Characteristics                | Min | Max      | Unit |

|--------------------------------|-----|----------|------|

| Input Supply Voltage           | 4.5 | 27 (5)   | V    |

| Operating Junction Temperature | -20 | +125 (6) | °C   |

Note 5: Operating the IC over this voltage is very easy to cause over voltage condition to VIN pin, SW pin, BS pin & EN pin. Note 6: If the IC experienced OTP, then the temperature may need to drop to < 125 degree C to let the IC recover.

# **Electrical Characteristics**

(T<sub>A</sub>=25°C, unless otherwise specified)

| Characteristics                                | Symbol                  | Conditions                   | Min   | Тур   | Max   | Unit |

|------------------------------------------------|-------------------------|------------------------------|-------|-------|-------|------|

| Feedback Voltage                               | <b>V</b> FB             | 4.5V ≤ VIN ≤ 27V             | 0.900 | 0.925 | 0.950 | V    |

| Feedback Overvoltage Threshold                 | _                       | _                            | _     | 1.1   | _     | V    |

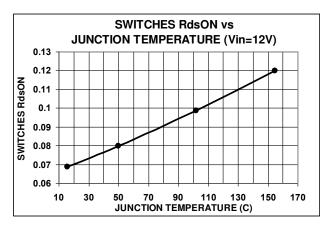

| High-Side Switch-On Resistance*                | _                       | _                            |       | 90    | _     | mΩ   |

| Low-Side Switch-On Resistance*                 | _                       | _                            | _     | 70    | _     | mΩ   |

| High-Side Switch Leakage                       | _                       | $V_{EN} = 0V, V_{SW} = 0V$   | _     | 0.1   | 10    | uA   |

| Upper Switch Current Limit                     | _                       | Minimum Duty Cycle           | 3.8   | 4.5   | _     | Α    |

| Lower Switch Current Limit                     | _                       | From Drain to Source         | _     | 1.2   | _     | Α    |

| COMP to Current SenseLimit<br>Transconductance | G <sub>CS</sub>         | _                            | _     | 5.2   | _     | A/V  |

| Error Amplifier Transconductance               | <b>G</b> EA             | $\Delta I_{COMP} = \pm 10uA$ | _     | 900   | _     | uA/V |

| Error Amplifier DC Gain*                       | A <sub>VEA</sub>        | _                            | _     | 400   | _     | V/V  |

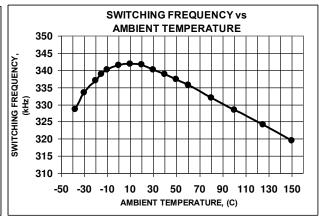

| Switching Frequency                            | f <sub>SW</sub>         | _                            | 300   | 340   | 380   | KHz  |

| Short Circuit Switching Frequency              |                         | $V_{FB} = 0$                 | _     | 100   | _     | KHz  |

| Minimum Duty Cycle*                            | D <sub>min</sub>        | _                            | 7.5   | _     | _     | %    |

| Maximum Duty Cycle                             | <b>D</b> <sub>max</sub> | _                            | _     | 92    | _     | %    |

| EN Shutdown Threshold Voltage                  | _                       | V <sub>EN</sub> Rising       | 1.1   | 1.4   | 2     | V    |

| EN Shutdown Threshold Voltage<br>Hysteresis    | _                       | _                            | _     | 180   | _     | mV   |

| EN Lockout Threshold Voltage                   |                         | _                            | 2.2   | 2.5   | 2.7   | V    |

| EN Lockout Hysteresis                          | _                       | _                            | _     | 150   | _     | mV   |

| Supply Current in Shutdown                     |                         | V <sub>EN</sub> = 0          | _     | 0.3   | 3.0   | uA   |

| IC Supply Current in Operation                 |                         | $V_{EN} = 3V, V_{FB} = 1.0V$ | _     | 1.3   | 1.5   | mA   |

| Input UVLO Threshold Rising                    | UVLO                    | V <sub>EN</sub> Rising       | 3.8   | 4.0   | 4.5   | V    |

| Input UVLO Threshold Hysteresis                | _                       | _                            | _     | 150   | _     | mV   |

| Soft-start Current                             | _                       | V <sub>SS</sub> = 0V         | _     | 6     | _     | uA   |

| Soft-start Period                              | _                       | C <sub>SS</sub> = 0.1uF      | _     | 13    | _     | mS   |

| Thermal Shutdown Temperature*                  | _                       | Hysteresis =25°C             | _     | 155   | _     | °C   |

Note: \* Guaranteed by design, not tested.

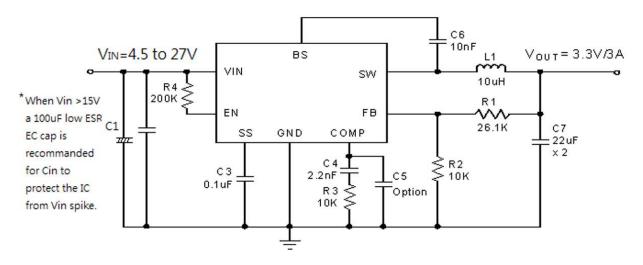

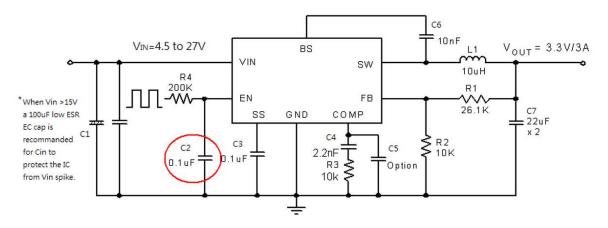

# **Application Circuit**

LSP5523 application circuit, 3.3V/3A output.

LSP5523 application circuit, 3.3V/3A output with EN function Note: C2 is required for separate EN signal.

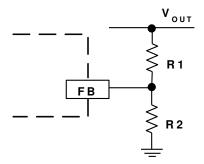

#### **Output Voltage Setting**

Figure 1. Output Voltage Setting

Figure 1 shows the connections for setting the output voltage. Select the proper ratio of the two feedback resistors R1 and R2 based on the output voltage. Typically, use R2  $\approx$  10K $\Omega$  and determine R1 from the following equation:

$R1 = R2 \left( \frac{V_{OUT}}{0.925 \text{V}} - 1 \right) \tag{1}$

Table1 - Recommended Resistance Values

| VOUT | R1      | R2    |

|------|---------|-------|

| 1.0V | 1.0 ΚΩ  | 12 KΩ |

| 1.2V | 3.0 ΚΩ  | 10 KΩ |

| 1.8V | 9.53 ΚΩ | 10 KΩ |

| 2.5V | 16.9 ΚΩ | 10 KΩ |

| 3.3V | 26.1 ΚΩ | 10 KΩ |

| 5V   | 44.2 KΩ | 10 KΩ |

| 12V  | 121 KΩ  | 10 KΩ |

#### **Inductor Selection**

The inductor maintains a continuous current to the output load. This inductor current has a ripple that is dependent on the inductance value: higher inductance reduces the peak-to-peak ripple current. The trade off for high inductance value is the increase in inductor core size and series resistance, and the reduction in current handling capability. In general, select an inductance value L based on the ripple current requirement:

$$L = \frac{V_{OUT} \cdot (V_{IN} - V_{OUT})}{V_{IN} f_{SW} I_{OUTMAX} K_{RIPPLE}}$$

(2)

where  $V_{IN}$  is the input voltage,  $V_{OUT}$  is the output voltage,  $f_{SW}$  is the switching frequency,  $I_{OUTMAX}$  is the maximum output current, and  $K_{RIPPLE}$  is the ripple factor. Typically, choose  $K_{RIPPLE}$  = ~ 30% to correspond to the peak-to-peak ripple current being ~30% of the maximum output current.

With this inductor value, the peak inductor current is I<sub>OUT</sub> • (1 + K<sub>RIPPLE</sub> / 2). Make sure that this peak inductor current is less than the upper switch current limit. Finally, select the inductor core size so that it does not saturate at the current limit. Typical inductor values for various output voltages are shown in Table 2.

| Ī | Vout | 1.0V  | 1.2V  | 1.5V | 1.8V | 2.5V | 3.3V | 5V   | 9V   |

|---|------|-------|-------|------|------|------|------|------|------|

| Ī | L    | 4.7uH | 4.7uH | 10uH | 10uH | 10uH | 10uH | 10uH | 22uH |

**Table 2. Typical Inductor Values**

#### **Input Capacitor**

The input capacitor needs to be carefully selected to maintain sufficiently low ripple at the supply input of the converter. A low ESR **Electrolytic (EC) capacitor** is highly recommended. Since large current flows in and out of this capacitor during switching, its ESR also affects efficiency.

When EC cap is used, the input capacitance needs to be equal to or higher than 100uF. The RMS ripple current rating needs to be higher than 50% of the output current. The input capacitor should be placed close to the VIN and GND pins of the IC, with the shortest traces possible. The input capacitor can be placed a little bit away if a small parallel 0.1uF ceramic capacitor is placed right next to the IC.

When Vin is >15V, pure ceramic Cin (\* no EC cap) is not recommended. This is because the ESR of a ceramic cap is often too small, Pure ceramic Cin will work with the parasite inductance of the input trace and forms a Vin resonant tank. When Vin is hot plug in/out, this resonant tank will boost the Vin spike to a very high voltage and damage the IC.

### **Output Capacitor**

The output capacitor also needs to have low ESR to keep low output voltage ripple. In the case of ceramic output capacitors,  $R_{\text{ESR}}$  is very small and does not contribute to the ripple. Therefore, a lower capacitance value can be used for ceramic capacitors. In the case of tantalum or electrolytic capacitors, the ripple is dominated by  $R_{\text{ESR}}$  multiplied by the ripple current. In that case, the output capacitor is chosen to have sufficiently low ESR.

For ceramic output capacitors, typically choose two capacitors of about 22uF. For tantalum or electrolytic capacitors, choose a capacitor with less than  $50m\Omega$  ESR.

#### **Optional Schottky Diode**

During the transition between high-side switch and low-side switch, the body diode of the low side power MOSFET conducts the inductor current. The forward voltage of this body diode is high. An optional Schottky diode may be paralleled between the SW pin and GND pin to improve overall efficiency. Table 3 lists example Schottky diodes and their Manufacturers.

Table 3-Diode Selection Guide

| Vin max | Part Number | Voltage/Current<br>Rating | Vendor              |

|---------|-------------|---------------------------|---------------------|

| <20V    | B130        | 30V, 1A                   | Diodes Incorporated |

| <20V    | SK13        | 30V, 1A                   | Diodes Incorporated |

| >20V    | B140        | 40V, 1A                   | Diodes Incorporated |

| >20V    | SK14        | 40V, 1A                   | Diodes Incorporated |

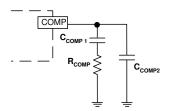

#### **Stability Compensation**

C<sub>COMP2</sub> is needed only for high ESR output capacitor Figure 2. Stability Compensation

The feedback loop of the IC is stabilized by the components at the COMP pin, as shown in Figure 2. The DC loop gain of the system is determined by the following equation:

$$A_{VDC} = \frac{0.925 \ V}{I_{OUT}} A_{VEA} \ G \ comp$$

(4)

The dominant pole P1 is due to  $C_{COMP1}$ :

$$f_{P1} = \frac{G_{EA}}{2\pi A_{VEA} C_{COMP-1}}$$

(5)

The second pole P2 is the output pole:

$$f_{P2} = \frac{I_{OUT}}{2\pi V_{OUT} C_{OUT}}$$

(6)

The first zero Z1 is due to R<sub>COMP</sub> and C<sub>COMP1</sub>:

$$f_{z1} = \frac{1}{2\pi R_{comp} C_{comp-1}}$$

(7)

And finally, the third pole is due to RCOMP and CCOMP2 (if CCOMP2 is used):

$$f_{P3} = \frac{1}{2\pi R_{COMP} C_{COMP2}}$$

(8)

The following steps should be used to compensate the IC:

STEP1. Set the crossover frequency at 1/10 of the switching frequency via RCOMP:

$$R_{COMP} = \frac{2\pi V_{OUT} C_{OUT} f_{SW}}{10 G_{EA} G_{COMP} \bullet 0.925 V}$$

(9)

But limit  $R_{COMP}$  to  $10K\Omega$  maximum. More than 10  $K\Omega$  is easy to cause overshoot at power on.

### **Stability Compensation (Continued)**

STEP2. Set the zero fZ1 at 1/4 of the crossover frequency. If  $R_{COMP}$  is less than  $10K\Omega$ , the equation for  $C_{COMP}$  is:

$$C_{COMP-1} = \frac{0.637}{R_{COMP} \times fc}$$

(F) (10)

STEP3. If the output capacitor's ESR is high enough to cause a zero at lower than 4 times the crossover frequency, an additional compensation capacitor  $C_{\text{COMP2}}$  is required. The condition for using  $C_{\text{COMP2}}$  is:

$$\pi \times C_{OUT} \times R_{ESR} \times fs \ge 1 \tag{11}$$

And the proper value for CCOMP2 is:

$$C_{COMP2} = \frac{C_{OUT}R_{ESRCOUT}}{R_{COMP}}$$

(12)

Though C<sub>COMP2</sub> is unnecessary when the output capacitor has sufficiently low ESR, a small value C<sub>COMP2</sub> such as 100pF may improve stability against PCB layout parasitic effects.

**Table 4 Component Selection Guide for Stability Compensation**

| Vin Range<br>(V) | Vout,<br>(V) | Cout               | Rcomp,<br>(kΩ) | Ccomp,<br>(nF) | Ccomp2,<br>(pF) | Inductor,<br>(uH) |

|------------------|--------------|--------------------|----------------|----------------|-----------------|-------------------|

| 5 – 12           | 1.0          |                    | 2.4            | 6.8            | none            | 4.7               |

| 5 – 15           | 1.2          |                    | 3              | 6.2            | none            | 4.7               |

| 5 – 15           | 1.8          | 22uF x2            | 6.2            | 3              | none            | 10                |

| 5 – 15           | 2.5          | Ceramic            | 8              | 2.2            | none            | 10                |

| 5 – 15           | 3.3          |                    | 10             | 2.2            | none            | 10                |

| 7 – 15           | 5            |                    | 10             | 2.2            | none            | 10                |

| 5 – 12           | 1.0          | 470                |                |                |                 |                   |

| 5 – 15           | 1.2          | 470uF/<br>6.3V/    |                |                |                 |                   |

| 5 – 23           | 1.8          | 6.3V/<br>120<br>mΩ | 10             | 10             | 680             | 10                |

| 5 – 27           | 2.5          |                    |                |                |                 |                   |

| 5 – 27           | 3.3          |                    |                |                |                 |                   |

| 7 – 27           | 5            |                    |                |                |                 |                   |

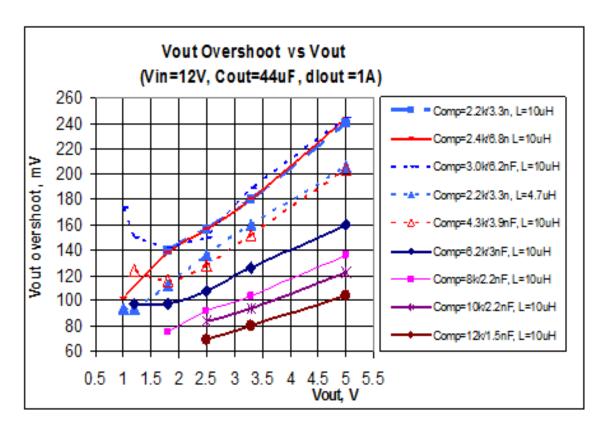

## **Stability Compensation** (Continued)

Figure 3. Load Transient Testing VS Compensation Value

## **Typical Characteristics**

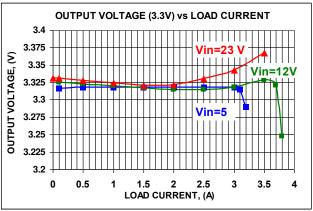

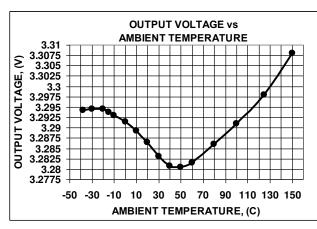

(Vin=12V, Io=0mA, Temperature = 25°C, unless otherwise specified)

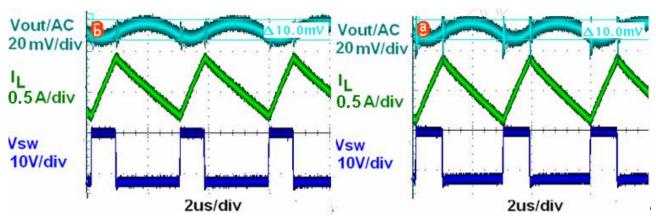

Light Load Operation (No load) Vin=12V, lin=8.2 mA, Vout=3,3V **Heavy Load Operation (3A Load)**

Vin=12V, Vout=3,3V

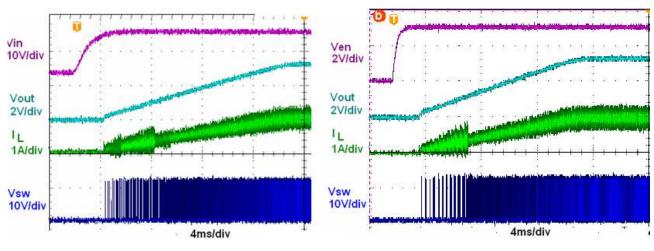

Startup Vin=12V, Vout=3.3V, lout=1A

through Vin.

#### through Enable.

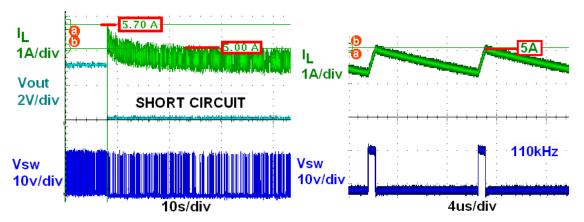

Short Circuit Protection Vin=12V

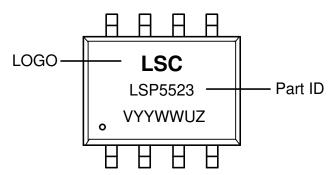

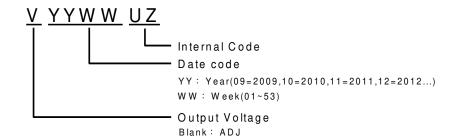

# **Marking Information**

#### ESOP-8L

# **Mechanical Information**

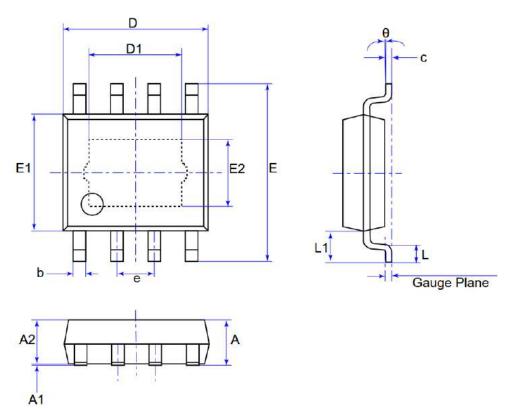

## (1) Package type: ESOP-8L

Unit:mm

| Symbol      | Min       | Max  |  |  |

|-------------|-----------|------|--|--|

| Α           | -         | 1.70 |  |  |

| A1          | -         | 0.15 |  |  |

| A2          | 1.30      | 1.55 |  |  |

| b           | 0.33      | 0.51 |  |  |

| С           | 0.17      | 0.25 |  |  |

| D           | 4.70 5.10 |      |  |  |

| D1          | 3.10 REF  |      |  |  |

| E           | 5.80      | 6.20 |  |  |

| E1          | 3.70      | 4.10 |  |  |

| E2          | 2.21      | REF  |  |  |

| е           | 1.27      | BSC  |  |  |

| L           | 0.40 1.27 |      |  |  |

| L1          | 1.00 1.10 |      |  |  |

| Gauge Plane | 0.25 BSC  |      |  |  |

| θ           | 0°        | 8°   |  |  |

#### MSL (Moisture Sensitive Level) Information

#### IPC/JEDEC J-STD-020D.1 Moisture Sensitivity Levels Table

|       |                        |                   |                           | S                | OAK REQUIR      | EMENTS          |                        |  |

|-------|------------------------|-------------------|---------------------------|------------------|-----------------|-----------------|------------------------|--|

|       | FLOOR LIFE             |                   |                           |                  | Α               | ccelerated Ed   | quivalent <sup>7</sup> |  |

| LEVEL | PLOOP                  | . 2001. 2 2       |                           | andard           | eV<br>0.40-0.48 | eV<br>0.30-0.39 | COMPITION              |  |

|       | TIME                   | CONDITION         | TIME<br>(hours)           | CONDITION        | TIME<br>(hours) | TIME<br>(hours) | CONDITION              |  |

| 1     | Unlimited              | ≤30 °C /85%<br>RH | 168<br>+5/-0              | 85 °C /85%<br>RH | NA              | NA              | NA                     |  |

| 2     | 1 year                 | ≤30 °C /60%<br>RH | 168<br>+5/-0              | 85 °C /60%<br>RH | NA              | NA              | NA                     |  |

| 2a    | 4 weeks                | ≤30 °C /60%<br>RH | 696 <sup>8</sup><br>+5/-0 | 30 °C /60%<br>RH | 120<br>-1/+0    | 168<br>-1/+0    | 60 °C/ 60% RH          |  |

| 3     | 168 hours              | ≤30 °C /60%<br>RH | 192 <sup>8</sup><br>+5/-0 | 30 °C /60%<br>RH | 40<br>-1/+0     | 52<br>-1/+0     | 60 °C/ 60% RH          |  |

| 4     | 72 hours               | ≤30 °C /60%<br>RH | 96 <sup>8</sup><br>+2/-0  | 30 °C /60%<br>RH | 20<br>+0.5/-0   | 24<br>+0.5/-0   | 60 °C/ 60% RH          |  |

| 5     | 48 hours               | ≤30 °C /60%<br>RH | 72 <sup>8</sup><br>+2/-0  | 30 °C /60%<br>RH | 15<br>+0.5/-0   | 20<br>+0.5/-0   | 60 °C/ 60% RH          |  |

| а     | 24 hours               | ≤30 °C /60%<br>RH | 48 <sup>8</sup><br>+2/-0  | 30 °C /60%<br>RH | 10<br>+0.5/-0   | 13<br>+0.5/-0   | 60 °C/ 60% RH          |  |

| 6     | Time on Label<br>(TOL) | ≤30 °C /60%<br>RH | TOL                       | 30 °C /60%<br>RH | NA              | NA              | NA                     |  |

- Note 7: CAUTION To use the "accelerated equivalent" soak conditions, correlation of damage response (including electrical, after soak and reflow), should be established with the "standard" soak conditions. Alternatively, if the known activation energy for moisture diffusion of the package materials is in the range of 0.40 0.48 eV or 0.30 0.39 eV, the "accelerated equivalent" may be used. Accelerated soak times may vary due to material properties (e.g. mold compound, encapsulant, etc.). JEDEC document JESD22-A120 provides a method for determining the diffusion coefficient.

- Note 8: The standard soak time includes a default value of 24 hours for semiconductor manufacturer's exposure time (MET) between bake and bag and includes the maximum time allowed out of the bag at the distributor's facility. If the actual MET is less than 24 hours the soak time may be reduced. For soak conditions of 30 °C/60% RH, the soak time is reduced by 1 hour for each hour the MET is less than 24 hours. For soak conditions of 60 °C/60% RH, the soak time is reduced by 1 hour for each 5 hours the MET is less than 24 hours. If the actual MET is greater than 24 hours the soak time must be increased. If soak conditions are 30 °C/60% RH, the soak time is increased 1 hour for each hour that the actual MET exceeds 24 hours. If soak conditions are 60 °C/60% RH, the soak time is increased 1 hour for each 5 hours that the actual MET exceeds 24 hours.

### **Mechanical Data**

- Moisture Sensitivity: Level 3 per J-STD-020

- Terminals: Finish Matte Tin Plated Leads, Solderable per MIL-STD-202, Method 208 (3)

- Weight: 0.081 grams (Approximate)

# A Product Line of Diodes Incorporated

# LITE-ON SEMICONDUCTOR

LSP5523

#### IMPORTANT NOTICE

- 1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- 2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- 3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

- 4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- subject 5. Diodes' products provided Diodes' Standard Terms Conditions οf are to and Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- 6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- 7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- 8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

- 9. This Notice may be periodically updated with the most recent version available at <a href="https://www.diodes.com/about/company/terms-and-conditions/important-notice">https://www.diodes.com/about/company/terms-and-conditions/important-notice</a>

DIODES is a trademark of Diodes Incorporated in the United States and other countries. The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. © 2022 Diodes Incorporated. All Rights Reserved.

www.diodes.com