### **General Description**

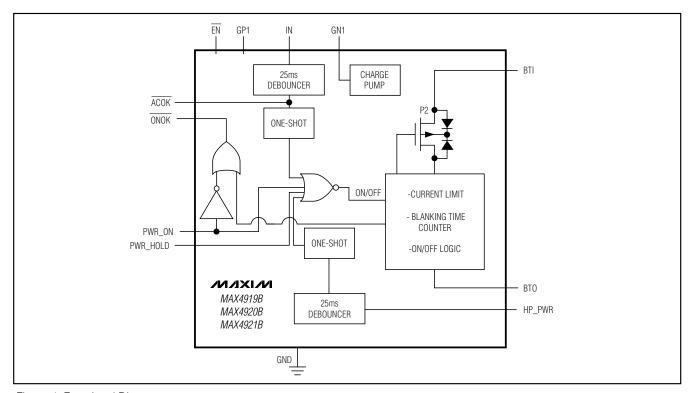

The MAX4919B/MAX4920B/MAX4921B overvoltage protection controllers protect low-voltage systems against high-voltage faults up to +28V. An internal 1.8A (min) pFET with low Ron (100m $\Omega$ ) switches a battery to the load and also protects the battery against short-circuit faults. When a short circuit occurs, the current through the internal pFET is limited for a blanking period. If the short condition is present after the blanking period, the switch is latched off and remains off until one of the input signals (IN, HP\_PWR, PWR\_ON) is cycled. The pFET is turned on by a logic-high voltage at PWR\_HOLD, HP\_PWR, PWR\_ON, or IN.

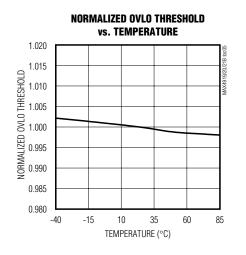

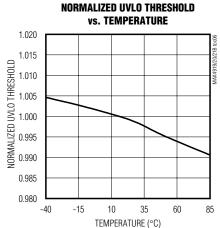

The overvoltage thresholds (OVLO) are preset to +6.38V (MAX4919B), +5.80V (MAX4920B), and +4.65V (MAX4921B). When the input voltage drops below the undervoltage lockout (UVLO) threshold, the devices enter a low-current standby mode. In shutdown mode, the current is reduced to 0.4µA. The MAX4919B/MAX4920B have a +4.27V UVLO threshold, and the MAX4921B has a +2.35V UVLO threshold.

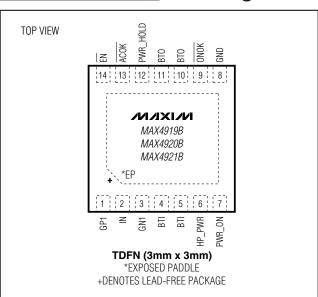

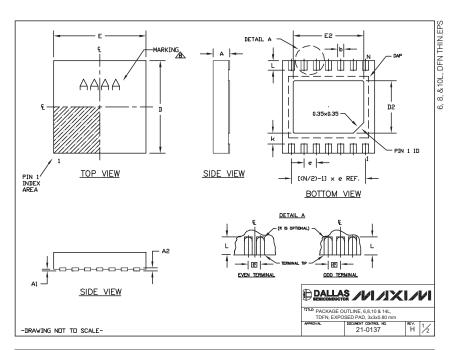

The MAX4919B/MAX4920B/MAX4921B are offered in a small 14-pin TDFN package (3mm x 3mm) with an exposed paddle and are specified over the extended -40°C to +85°C temperature range.

### **Applications**

Cell Phones Digital Still Cameras PDAs and Palmtop Devices MP3 Players

#### **Features**

- ♦ Input Overvoltage Protection Up to +28V

- ♦ Preset Overvoltage Protection Trip Level 6.38V (MAX4919B) 5.80V (MAX4920B) 4.65V (MAX4921B)

- ♦ Adapter/Car-Kit Auto-Selector

- **♦ Low-Current Undervoltage Lockout Mode**

- ♦ Internal 1.8A (min) Battery Switchover FET

- **♦ Integrated Low-Battery Detect**

- **♦** Battery Short-Circuit Protection

- ♦ Low-Cost External nMOS Overvoltage FET

- ◆ 14-Pin TDFN Package (3mm x 3mm)

### Pin Configuration

### **Ordering Information/Selector Guide**

| PART          | PIN-<br>PACKAGE | OVLO (V) | UVLO (V) | TOP MARK | PKG CODE |

|---------------|-----------------|----------|----------|----------|----------|

| MAX4919BETD+T | 14 TDFN-EP*     | 6.38     | 4.27     | ABY      | T1433-2  |

| MAX4920BETD+T | 14 TDFN-EP*     | 5.80     | 4.27     | ABZ      | T1433-2  |

| MAX4921BETD+T | 14 TDFN-EP*     | 4.65     | 2.35     | ACA      | T1433-2  |

Note: All devices are specified over the -40°C to +85°C operating temperature range.

MIXIM

<sup>+</sup>Denotes lead-free package.

<sup>\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| IN to GND                      | 0.3V to +30V  |

|--------------------------------|---------------|

| GP1, GN1 to GND                | 0.3V to +12V  |

| IN to GP1                      | 0.3V to +20V  |

| BTO to GND                     | 0.3V to +6.1V |

| BTI to BTO                     | 0.3V to +6V   |

| BTI, ACOK, PWR_ON, EN to GND   | 0.3V to +6V   |

| HP_PWR, ONOK, PWR_HOLD to GND. | 0.3V to +6V   |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                |

|-------------------------------------------------------|----------------|

| 14-Pin TDFN (derate 18.5mW/°C above +70               | °C)1482mW      |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 5V \text{ (MAX4919B/MAX4920B)})$  or  $V_{IN} = 4.2V \text{ (MAX4921B)}$ ,  $V_{BTI} = 4V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                             | SYMBOL                           | COI                                       | NDITIONS                                      | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------|----------------------------------|-------------------------------------------|-----------------------------------------------|------|------|------|-------|

| Input Voltage Range                   | VIN                              |                                           |                                               | 1.2  |      | 28   | V     |

| Janut Cunnly Current                  | lu.                              | MAX4919B/MAX492                           | 20B                                           |      | 77   | 120  |       |

| Input Supply Current                  | I <sub>IN</sub>                  | MAX4921B                                  |                                               |      | 75   | 110  | - μΑ  |

| 111/1000                              | ,                                | $V_{\overline{EN}} = 0V$ ; $V_{IN} = 3.9$ | V; MAX4919B/MAX4920B                          |      | 10   | 22   |       |

| UVLO Supply Current                   | luvL                             | $V_{\overline{EN}} = 0V$ ; $V_{IN} = 2.1$ | V; MAX4921B                                   |      | 8    | 18   | μΑ    |

| Shutdown Supply Current               | I <sub>SHDN</sub>                | $V_{\overline{EN}} = 1.6V, V_{IN} = 3$    | .6V                                           |      | 0.4  | 2    | μΑ    |

| IN I landom roltomo I polico et       | V                                | V falling                                 | MAX4919B/MAX4920B                             | 4.00 | 4.27 | 4.54 | V     |

| IN Undervoltage Lockout               | $V_{\text{UVLO}}$                | V <sub>IN</sub> falling                   | MAX4921B                                      | 2.20 | 2.35 | 2.50 | V     |

| IN Undervoltage Lockout<br>Hysteresis |                                  |                                           |                                               |      | 1    |      | %     |

|                                       |                                  |                                           | MAX4919B                                      | 6.00 | 6.38 | 6.76 |       |

| Overvoltage Trip Level                | Vovlo                            | V <sub>IN</sub> rising                    | MAX4920B                                      | 5.44 | 5.80 | 6.17 | V     |

|                                       |                                  |                                           | MAX4921B                                      | 4.35 | 4.65 | 4.95 |       |

| IN Overvoltage Lockout<br>Hysteresis  |                                  |                                           |                                               |      | 1    |      | %     |

| BATTERY SWITCHOVER                    |                                  | l                                         |                                               |      |      |      |       |

| BTI Input Range                       | V <sub>BTI</sub>                 |                                           |                                               | 2.30 |      | 5.50 | V     |

| BTI UVLO                              | V <sub>U</sub> VBTI              | V <sub>BTI</sub> falling                  |                                               | 2.0  | 2.15 | 2.3  | V     |

| BTI UVLO Hysteresis                   |                                  |                                           |                                               |      | 1.5  |      | %     |

| BTI Low-Battery Threshold             | V <sub>L</sub> V <sub>B</sub> TI | V <sub>BTI</sub> falling                  |                                               | 2.65 | 2.82 | 3    | V     |

| BTI Low-Battery Hysteresis            |                                  |                                           |                                               |      | 1.5  |      | %     |

| BTI Supply Current                    |                                  | Adapter out, V <sub>PWR</sub> _EN = high  | HOLD = high,                                  |      |      | 7    | μΑ    |

| DTI Chartelesses Occurs at            |                                  |                                           | T <sub>A</sub> = +25°C                        |      |      | 2    |       |

| BTI Shutdown Current                  |                                  | V <sub>BTO</sub> = 0V                     | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |      | 2.8  | μΑ    |

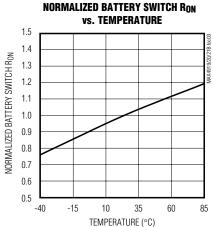

| INTERNAL pFET                         |                                  |                                           |                                               |      |      |      |       |

| Switch On-Resistance                  | Pov                              | $V_{BTI} = 2.7V$ , $I_{BTI to}$           | T <sub>A</sub> = +25°C                        |      |      | 100  | mΩ    |

| - Switch On-Hesistance                | Ron                              | BTO = 0.5A                                | $T_A = -40$ °C to $+85$ °C                    |      |      | 120  | 11122 |

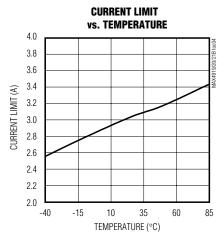

| Forward-Overload Current Limit        | I <sub>LIM</sub>                 | BTO shorted to GNI                        | )                                             | 1.8  |      |      | А     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 5V \text{ (MAX4919B/MAX4920B)} \text{ or } V_{IN} = 4.2V \text{ (MAX4921B)}, V_{BTI} = 4V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                             | SYMBOL              | CONDITIONS                                                                                                                     | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| GATE DRIVERS                          |                     |                                                                                                                                |      |      |      |       |

| CNI Tura On Voltage                   | Varia               | V <sub>GN1</sub> referenced to GND, I <sub>GN1</sub> sourcing 1μA; MAX4919B/MAX4920B                                           | 9    |      | 10   | V     |

| GN1 Turn-On Voltage                   | VGN1                | V <sub>GN1</sub> referenced to GND, I <sub>GN1</sub> sourcing 1μA; MAX4921B                                                    | 7.8  |      | 8.4  | V     |

| GN1 Pulldown Current                  | IGPD                | $V_{IN} > OVLO$ , $V_{GN1} = 5.5V$                                                                                             |      | 30   |      | mA    |

| GP1 Clamp Voltage                     | VCLAMP              | V <sub>IN</sub> - V <sub>GP1</sub> when V <sub>IN</sub> = 28V                                                                  | 12.5 | 16.5 | 19.5 | V     |

| GP1 Pulldown Resistor                 | RGPD                |                                                                                                                                | 31   | 51.5 | 72   | kΩ    |

| LOGIC INPUTS (PWR_HOLD, HP            | _PWR, PWF           | R_ON, <del>EN</del> )                                                                                                          |      |      |      |       |

| Input-High Voltage                    | VIH                 | V <sub>BTI</sub> = 5.50V                                                                                                       | 1.5  |      |      | V     |

| Input-Low Voltage                     | V <sub>IL</sub>     | $V_{BTI} = 2.3V$ for PWR_HOLD, HP_PWR and $\overline{EN}$ ; $V_{BTI} = 3V$ for PWR_ON                                          |      |      | 0.4  | V     |

| PWR_HOLD, EN Input Leakage<br>Current | llkg                | EN, PWR_HOLD = GND or 5.5V                                                                                                     | -1   |      | +1   | μΑ    |

| PWR_ON, HP_PWR Pulldown<br>Resistance | R <sub>IPD</sub>    |                                                                                                                                | 200  |      |      | kΩ    |

| LOGIC OUTPUTS (ACOK, ONOK             | )                   |                                                                                                                                |      |      |      |       |

| Output-Low Voltage                    | V <sub>OL</sub>     | I <sub>SINK</sub> = 1mA                                                                                                        |      |      | 0.4  | V     |

| Output-High Leakage Current           |                     |                                                                                                                                |      |      | 1    | μΑ    |

| TIMING                                |                     |                                                                                                                                |      |      |      |       |

| IN Debounce Time                      | t <sub>INDBC</sub>  | Time from UVLO < V <sub>IN</sub> < OVLO to V <sub>GN1</sub> > 0.3V, C <sub>GN1</sub> = 500pF                                   | 10   | 25   | 40   | ms    |

| ACOK Blanking Time                    | t <sub>BLNKAC</sub> | Time from $V_{GN1} > 0.3V$ to $\overline{ACOK}$ low, $C_{GN1} = 500pF$                                                         | 10   | 25   | 40   | ms    |

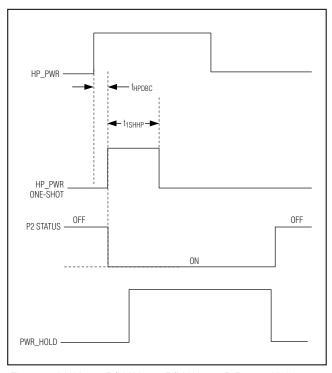

| HP_PWR Debounce Time                  | tHPDBC              | Time for internal pFET to turn on after VHP_PWR > VIH                                                                          | 10   | 25   | 40   | ms    |

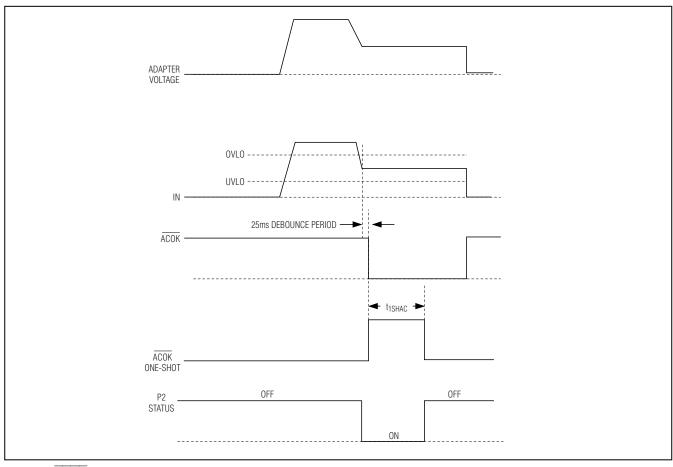

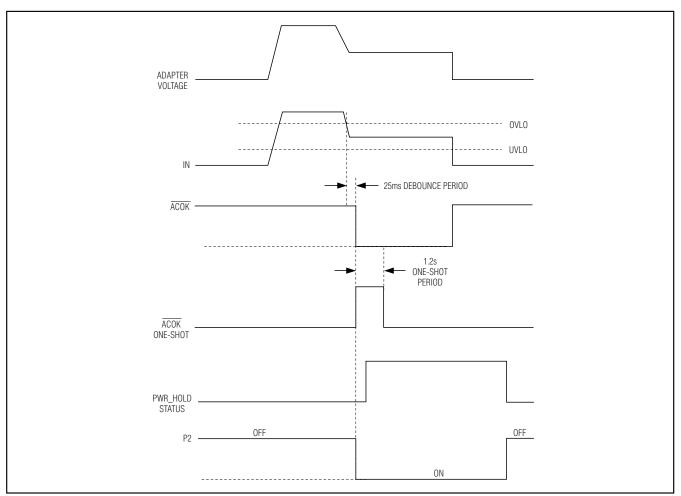

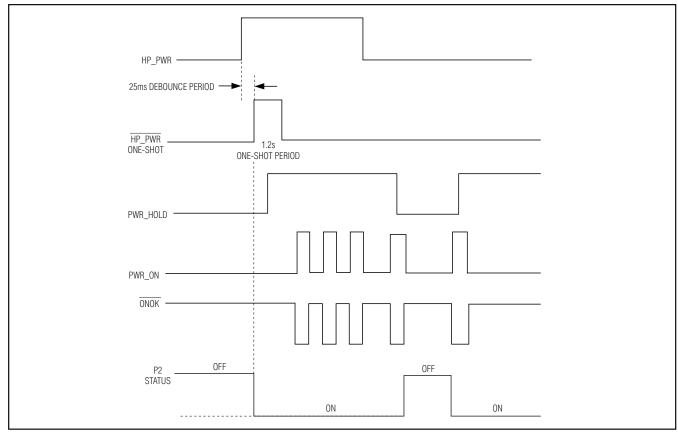

| ACOK One-Shot Time                    | t <sub>1SHAC</sub>  | VPWR_HOLD = 0V; time for internal pFET to turn off after ACOK < V <sub>OL</sub> (Figure 1)                                     | 488  | 1220 | 1952 | ms    |

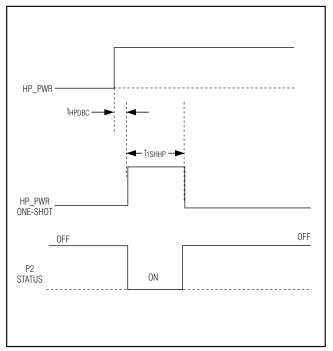

| HP_PWR One-Shot Time                  | t <sub>1SHHP</sub>  | V <sub>PWR_HOLD</sub> = 0V; time for internal pFET to turn off after V <sub>HP_PWR</sub> > V <sub>IH</sub> (Figure 2)          | 488  | 1220 | 1952 | ms    |

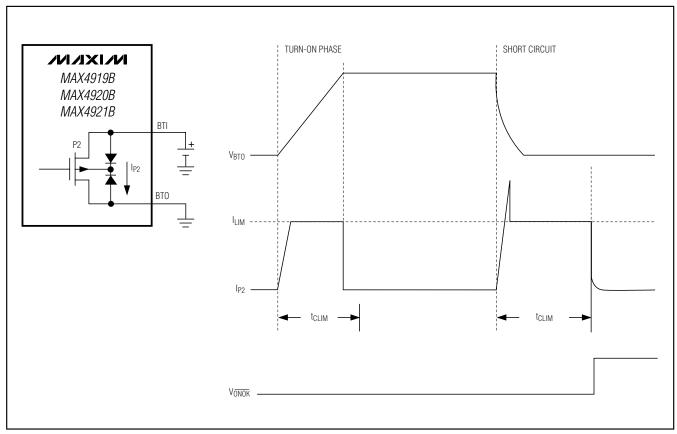

| Current-Limit Blanking Time           | tCLIM               | V <sub>BTI</sub> = 2.7V; V <sub>BTO</sub> shorted to GND; time for internal pFET current to reduce to 10mA                     | 4    | 10   | 16   | ms    |

| GN1 Turn-On Time                      | tgon                | V <sub>GN1</sub> = 0.3V to 8V<br>(MAX4919B/MAX4920B),<br>V <sub>GN1</sub> = 0.3V to 7V (MAX4921B),<br>C <sub>GN1</sub> = 500pF |      | 10   |      | ms    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 5V \text{ (MAX4919B/MAX4920B)})$  or  $V_{IN} = 4.2V \text{ (MAX4921B)}$ ,  $V_{BTI} = 4V$ ,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                       | SYMBOL           | CONDITIONS                                                                                                                                                                          | MIN | TYP | MAX | UNITS |

|---------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| GN1 Turn-Off Time               | tgoff            | V <sub>IN</sub> rising at 1V/µs from 5V to 8V<br>(MAX4919B/MAX4920B), or from 4V to 7V<br>(MAX4921B); V <sub>GN1</sub> = 0.3V,<br>C <sub>GN1</sub> = 500pF                          |     | 6   | 20  | μs    |

| Initial Overvoltage Fault Delay | tovLo            | $V_{IN}$ rising at 1V/µs from 0V to 9V, time from $V_{IN} = 5V$ to $I_{GN1} = 80\%$ of $I_{GPD}$                                                                                    |     | 1.5 |     | μs    |

| ACOK Deassertion Delay          | t <u>acok</u>    | $V_{IN}$ rising at 1V/µs from 5V to 8V (MAX4919B/MAX4920B), or from 4V to 7V (MAX4921B); $V_{\overline{ACOK}}$ pullup voltage = 3V; $\overline{R_{ACOK}}$ = 10k $\Omega$ (Figure 3) |     | 5.8 |     | μs    |

| Disable Time                    | t <sub>DIS</sub> | VEN = 2.4V, V <sub>GN1</sub> = 0.3V, C <sub>GN1</sub> = 500pF                                                                                                                       |     | 2   |     | μs    |

Note 1: All specifications are 100% production tested at T<sub>A</sub> = +25°C, unless otherwise noted. Specifications over T<sub>A</sub> = -40°C to +85°C are guaranteed by design.

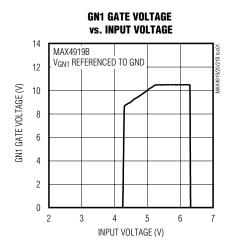

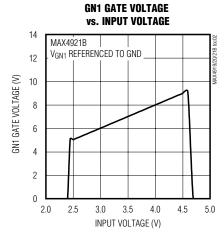

### Typical Operating Characteristics

( $V_{BTI} = 4V$ ,  $T_A = +25$ °C, unless otherwise noted.)

Typical Operating Characteristics (continued)

$(V_{BTI} = 4V, T_A = +25^{\circ}C, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(V_{BTI} = 4V, T_A = +25^{\circ}C, unless otherwise noted.)$

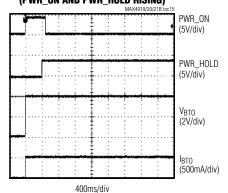

### BATTERY-SWITCH TURN-ON RESPONSE (PWR\_ON RISING)

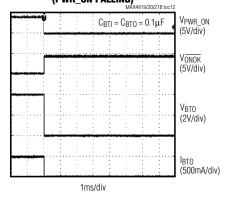

#### BATTERY-SWITCH TURN-OFF RESPONSE (PWR\_ON FALLING)

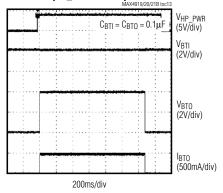

BATTERY-SWITCH TURN-ON RESPONSE (HP\_PWR RISING)

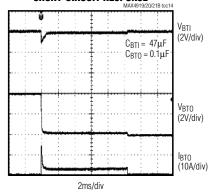

#### SHORT-CIRCUIT RESPONSE

BATTERY SWITCH TURN-ON RESPONSE (PWR\_ON AND PWR\_HOLD RISING)

### **Pin Description**

| PIN    | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | GP1      | p-Channel MOSFET Gate-Drive Output. GP1 pulls the external pFET gate down when the input is above ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2      | IN       | Voltage Input. IN powers the charge pump required to turn on GN1. When the correct adapter is plugged in, a one-shot turns on the internal pFET for 1.2s, allowing time for the microprocessor ( $\mu$ P) to power-up and drive PWR_HOLD high. Bypass IN with a minimum 1 $\mu$ F ceramic capacitor as close as possible to the device for ±15kV ESD protection. When operating the MAX4919B/MAX4920B/MAX4921B with an external pFET at GP1, place the 1 $\mu$ F capacitor to GND as close to the drain of the pFET as possible for the ±15kV ESD protection. If ±15kV ESD protection is not required, place a minimum 0.1 $\mu$ F capacitor at IN to GND. |

| 3      | GN1      | n-Channel MOSFET Gate-Drive Output. GN1 is the output of an on-chip charge pump. When $V_{UVLO} < V_{IN} < V_{OVLO}$ , GN1 is driven above the source voltage to turn on the external n-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4, 5   | BTI      | Battery Switch Input. BTI powers the internal circuitry. Bypass BTI with a 0.1µF capacitor. Both BTI inputs must be externally connected together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6      | HP_PWR   | Car-Kit Detection Input. When a car kit is plugged into HP_PWR, a one-shot turns on the internal pFET for 1.2s, allowing time for the µP to power-up and drive PWR_HOLD high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7      | PWR_ON   | Power-On Input. Drive PWR_ON high to turn on the internal pFET. The inverse of the PWR_ON logic state is represented at the ONOK logic output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8      | GND      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

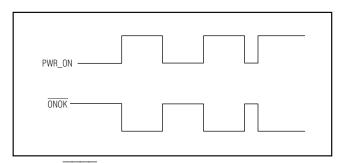

| 9      | ONOK     | Open-Drain PWR_ON Indicator Output. ONOK is a logic output with the inverse state of the PWR_ON input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10, 11 | BTO      | Battery Switch Output. Both BTO outputs must be externally connected together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12     | PWR_HOLD | Power-Hold Input. Drive PWR_HOLD high to turn on internal pFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13     | ACOK     | Open-Drain Adapter Voltage Indicator Output. ACOK pulls low when the adapter voltage is stable between UVLO and OVLO for 25ms. Connect a pullup resistor from ACOK to a logic supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 14     | ĒN       | Enable Input. Drive EN low for normal operation. Drive EN high to turn off the external MOSFETs and enter shutdown mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EP     | _        | Exposed Paddle. Connect EP to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### **Detailed Description**

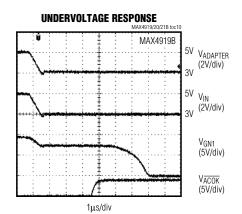

#### **Undervoltage Lockout (UVLO)**

The MAX4919B/MAX4920B have a 4.27V (typ) undervoltage threshold (UVLO), while the MAX4921B has 2.35V (typ) UVLO threshold. When V<sub>IN</sub> is less than UVLO, GN1 is held low and  $\overline{ACOK}$  is high impedance.

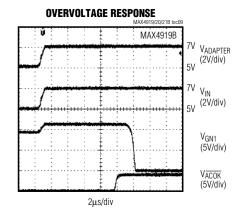

#### Overvoltage Lockout Thresholds (OVLO)

The MAX4919B has a 6.38V (typ) overvoltage threshold (OVLO), the MAX4920B has a 5.8V (typ) typical OVLO, and the MAX4921B has a 4.65V (typ) OVLO. When  $V_{\rm IN}$  is greater than OVLO, GN1 is held low and  $\overline{\rm ACOK}$  is high impedance.

#### Powering the MAX4919B/ MAX4920B/MAX4921B

BTI powers the MAX4919B/MAX4920B/MAX4921B internal circuitry. BTI also connects internally to a 1.8A (min) pFET that conducts an external load to the battery using the BTO output. See the *Battery Switchover* section.

#### **GP1** Driver

When the input voltage goes above ground, GP1 pulls low and turns on the pFET. An internal clamp protects the pFET by insuring that the GP1 to IN voltage does not exceed 19.5V when the input (IN) rises to 28V.

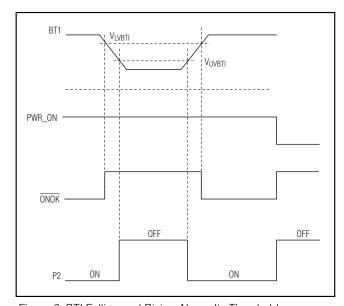

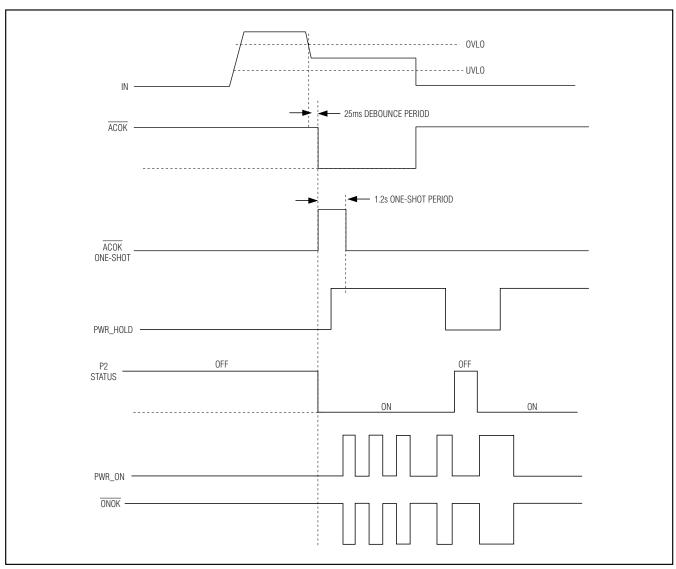

Figure 1. ACOK One-Shot Timing Diagram

#### **GN1 Driver**

An internal 5.5V supply powers the on-chip charge pump used to drive GN1 above IN, allowing the use of a low-cost nFET. The GN1 voltage is approximately two times V<sub>IN</sub> until V<sub>IN</sub> exceeds 5.5V, at which point, GN1 clamps to 9.5V (MAX4919B/MAX4920B) or 8.1V (MAX4921B).

#### ACOK

ACOK is an active-low open-drain output that asserts when V<sub>UVLO</sub> <V<sub>IN</sub> < V<sub>OVLO</sub> for the 25ms debounce period. ACOK deasserts immediately to overvoltage and undervoltage faults. Connect a pullup resistor from ACOK to the logic I/O voltage of the host system.

#### PWR\_ON

PWR\_ON is one of the logic inputs that enables the internal 1.8A switch. Drive PWR\_ON high to turn on the internal switch. PWR\_ON also controls the logic output

ONOK. The ONOK open-drain output is the inverse of the PWR\_ON input state (see Figure 5). Note that ONOK is high impedance when V<sub>IN</sub> < V<sub>UVLO</sub>, and V<sub>BTI</sub> < 2.82V (typ). If V<sub>BTI</sub> is greater than 2.15V (typ), but less than 2.82V (typ), PWR\_ON and ONOK are disabled and ONOK pulls high. When BTI rises above 2.82V (typ) again, PWR\_ON is again enabled and ONOK goes back to its previous logic level before a low condition at BTI (see Figure 6).

#### **Battery Switchover**

An internal 1.8A (min) pFET with a  $100m\Omega$  (typ) R<sub>ON</sub> connects BTI to the load at BTO. The internal battery switchover FET turns on when either HP\_PWR, PWR\_ON, or PWR\_HOLD is high. Note that when BTI < 2.15V, the internal switch remains inactive, regardless of the logic control signals.

IN

Vovlo

tGOFF

tACOK

80% OF ACOK

PULLUP VOLTAGE

Figure 2. HP\_PWR One-Shot Timing Diagram

Figure 3. ACOK Assertion Delay Timing Diagram

Figure 4. Functional Diagram

#### **PWR HOLD**

PWR\_HOLD controls the turn-on of the 1.8A (min) current-limit switch (P2). When a voltage is present at IN, and  $V_{UVLO} < V_{IN} < V_{OVLO}$  for 25ms,  $\overline{ACOK}$  pulls low and issues an internal one-shot pulse that turns on P2 temporarily for 1.2s (typ). During the 1.2s one-shot period, the MAX4919B/MAX4920B/MAX4921B must see a low-to-high transition at PWR\_HOLD (and PWR\_HOLD must remain high), for P2 to remain on (see Figure 7). P2 turns off when PWR\_HOLD and PWR\_ON are low, and when the HP\_PWR and  $\overline{ACOK}$  internal one-shot timers have expired.

When a voltage at IN is not present, HP\_PWR controls the turn-on of P2. Upon a low-to-high transition at HP\_PWR (and HP\_PWR remaining high), the MAX4919B/MAX4920B/MAX4921B issue an internal HP\_PWR one-shot signal that turns on P2 temporarily for 1.2s (typ). During the 1.2s one-shot period, the MAX4919B/MAX4920B/MAX4921B must see a low-to-high transition at PWR\_HOLD (and PWR\_HOLD must remain high) for P2 to remain on. P2 turns off when PWR\_HOLD and PWR\_ON are low, and when the HP\_PWR and ACOK internal one-shot timers have expired (see Figure 8).

#### **Current Limiting**

The MAX4919B/MAX4920B/MAX4921B feature an internal 1.8A (min) current-limiting switch (P2) at BTO. The current limit remains in effect throughout BTI's input supply-voltage range.

The current limit takes care of two situations: when P2 is initially turned on, and when P2 is already on and a short circuit occurs (see Figure 9). When P2 is turned on, the current can be high because BTO = 0 and a large load capacitor needs to be charged. The protection circuit prevents the load current from exceeding the 1.8A (min) current-limit value, and BTO will have a smooth turn-on (the larger the capacitor, the slower the turn-on). The 10ms blanking time avoids a false fault assertion. At the end of the blanking time, if the device is still limiting, a fault is asserted and P2 immediately turns off. When the switch is already on and a short-circuit condition occurs at BTO, the device limits the current. If the fault condition duration is greater than the blanking time, P2 turns off.

Before P2 turns on again, any condition that is attempting to turn it on must be first removed, i.e. the one-shot (from IN or HP\_PWR) must be completed, and PWR\_ON and PWR\_HOLD must be low. If the three conditions are satisfied, P2 turns on again only if either IN or PWR\_HOLD is cycled OFF and ON.

Figure 5. ONOK Timing Diagram

Figure 6. BTI Falling and Rising Above Its Thresholds

#### **Low-Battery Operation**

The MAX4919B/MAX4920B/MAX4921B operate in low-battery mode when the battery voltage at BTI is greater than 2.15V but less than 2.8V (typ). In low-battery operation, PWR\_ON does not influence the behavior of the internal switch.

When an adapter and car kit are not present, the internal switch is typically controlled by PWR\_HOLD. If PWR\_ON is high (ONOK is low) and BTI falls below 2.8V, ONOK pulls high, but the internal switch remains on since PWR\_HOLD is high. If PWR\_ON is high and PWR\_HOLD is low when VBTI falls below the 2.8V threshold, the internal switch turns off immediately. Upon BTI rising above 2.8V again, PWR\_ON is again enabled and ONOK goes back to its previous logic level before a low condition at BTI occurred.

Figure 7. MAX4919B/MAX4920B/MAX4921B Power Hold Waveform When Voltage at IN is Present

Note that upon V<sub>BTI</sub> falling below the 2.15V (min) threshold, the internal switch remains off, irrespective of the control signals at HP\_PWR, PWR\_ON, or PWR\_HOLD.

#### **Thermal Shutdown**

The MAX4919B/MAX4920B/MAX4921B feature thermal shutdown circuitry. The internal 1.8A (min) switch turns off when the junction temperature exceeds +135°C and immediately goes into a fault mode. The device can be reset upon the junction temperature dropping below +125°C. Before P2 can be turned on again, any condition that is attempting to turn it on must be first removed, i.e., the one-shot (from IN or HP\_PWR) must be completed, and PWR\_ON and PWR\_HOLD must be low. If the three conditions are satisfied, P2 turns on again only if either IN or PWR\_HOLD is cycled OFF and ON.

### Applications Information

#### **MOSFET Configuration**

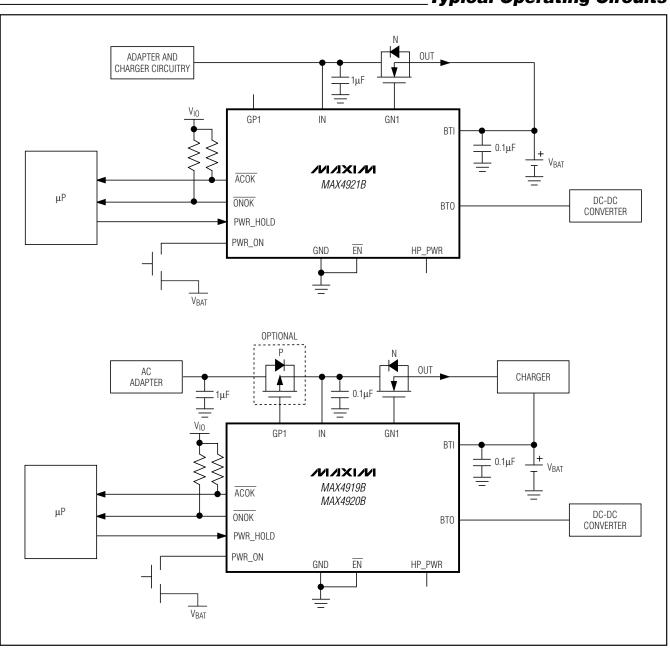

The MAX4919B/MAX4920B/MAX4921B can drive either a single n-channel or back-to-back n-channel MOSFET (Figure 10). The back-to-back configuration will have almost zero reverse current when the adapter is not present or when the adapter voltage is below the undervoltage lockout threshold.

If reverse-current leakage is not a concern, a single n-channel MOSFET can be used. This approach has half the loss of the back-to-back configuration when used with similar MOSFET types and is a lower cost solution. Note that if the input is actually pulled low, the output will be pulled low as well due to the parasitic body diode in the MOSFET. If this is a concern, then use the back-to-back configuration.

### **Table 1. MOSFET Suggestions**

| PART      | CONFIGURATION/<br>PACKAGE | V <sub>GS</sub> (MAX)<br>(V) | V <sub>DS</sub> (MAX)<br>(V) | R <sub>ON</sub> at 4.5V (mΩ) | MANUFACTURER                       |

|-----------|---------------------------|------------------------------|------------------------------|------------------------------|------------------------------------|

| Si5504DC  | Complementary             | ±20                          | 30                           | 143<br>(N-FET)               |                                    |

| 310004DC  | MOSFET/1206-8             | ±20                          | -30                          | 290<br>(P-FET)               |                                    |

| Si5902DC  | Dual/1206-8               | ±20                          | 30                           | 143<br>(N-FET)               | Vishay Siliconix<br>www.vishay.com |

| Si1426DH  | Single/µDFN-6             | ±20                          | 30                           | 115<br>(N-FET)               |                                    |

| Si5435DC  | Single/1206-8             | ±20                          | -30                          | 80<br>(P-FET)                |                                    |

| FDC6561AN | Dual/SSOT-6               | ±20                          | 30                           | 145<br>(N-FET)               |                                    |

| FDG315N   | Single/µDFN-6             | ±20                          | 30                           | 160<br>(N-FET)               | Fairchild Semiconductor            |

| FDC658P   | Single/SSOT-6             | ±20                          | -30                          | 75<br>(P-FET)                | www.fairchildsemi.com              |

| FDC654P   | Single/SSOT-6             | ±20                          | -30                          | 125<br>(P-FET)               |                                    |

#### **MOSFET Selection**

The MAX4919B/MAX4920B/MAX4921B are designed for use with a complementary MOSFET or single p-channel and dual back-to-back n-channel MOSFETS. In most situations, MOSFETs with RDS(ON) specified for a VGS of 4.5V will work well. Also, the VDS should be 30V in order for the MOSFET to withstand the full 28V IN range of the MAX4919B/MAX4920B/MAX4921B. Table 1 shows a selection of MOSFETs which are appropriate for use.

#### **IN Bypass Considerations**

For most applications, bypass IN to GND with a 1 $\mu$ F ceramic capacitor to enable  $\pm 15$ kV ESD protection (when GP1 is not utilized). If  $\pm 15$ kV is not required, place a minimum 0.1 $\mu$ F capacitor at IN to GND. If the power source has significant inductance due to long lead length, take care to prevent overshoots due to the LC tank circuit and provide protection if necessary to prevent exceeding the  $\pm 30$ V absolute maximum rating at IN.

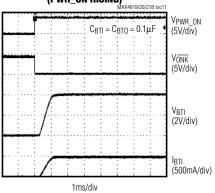

#### **BTO Bypass Capacitor Considerations**

In order to guarantee a successful startup of the internal p-channel MOSFET, use a capacitance lower than CBTO(MAX). If the load capacitance is too large, then current may not have enough time to charge the capacitance and the device assumes that there is a faulty load condition. The maximum capacitive-load value that can be driven by BTO is obtained by the following formula:

$$C_{BTO(MAX)} \le \frac{I_{LIM} \times t_{CLIM}}{V_{BTI}}$$

where CBTO is the output capacitor at BTO, VBTI is the battery voltage, tCLIM is the minimum current-limit blanking time, and ICLIM is the minimum forward current-limit value.

Figure 8. MAX4919B/MAX4920B/MAX4921B Power\_Hold Waveform When Voltage IN is Not Present

### Additional Applications Information Adapter Application

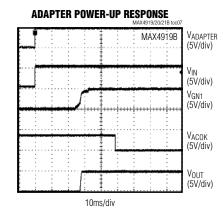

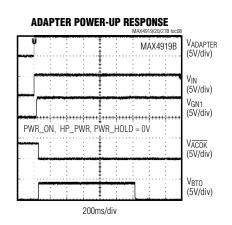

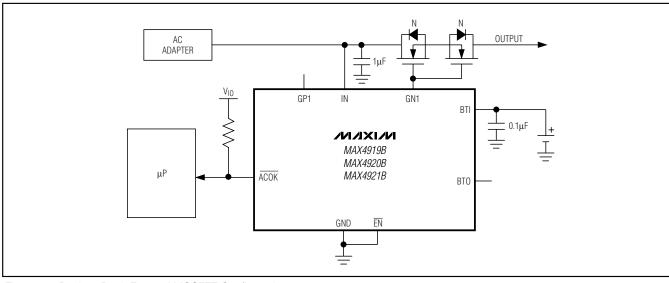

Figures 11 and 12 depict the MAX4919B/MAX4920B being utilized in an application where the AC adapter supplies the input voltage and the car adapter is not plugged in. In this case, when the AC adapter (5V) is plugged in, the voltage at IN initially makes sure that a negative voltage is not present.

If V<sub>IN</sub> remains above the UVLO and below the OVLO ranges for more than 25ms (debouncer), the n-channel MOSFET (N1) turns on and after 25ms,  $\overline{ACOK}$  asserts low, then a one-shot timer starts that turns P2 on for 1.2s. During this duration, the  $\mu P$  needs to issue a PWR\_HOLD to keep P2 on before the one-shot period expires. The adapter then powers the charger to charge the battery and the battery supports the load.

#### Reverse-Polarity Protection

Figure 11 shows an application where the external p-channel MOSFET is added for reverse-polarity protection. The reverse-polarity protection works by turning off the p-channel MOSFET when the adapter voltage is below ground. The p-channel MOSFET only turns off if the voltage at IN is less than the threshold voltage of the p-channel MOSFET. Due to the body diode leakage path through the external n-channel MOSFET, the reverse-polarity protection operation requires a reverse current-limited load. Figure 11 shows a battery charger as the load connected to the source of n-channel MOS-FET. If the voltage at the load connection (source of the n-channel MOSFET) is greater than the drop across the n-channel MOSFET's body diode plus the p-channel MOSFET threshold voltage, then the p-channel MOSFET remains on if the adapter voltage is below ground. If the load has reverse-current protection, the voltage at the load pulls down and the p-channel MOSFET turns off limiting reverse current. If the load allows a large reverse current, then this current flows out of the adapter input and the reverse-polarity protection is defeated.

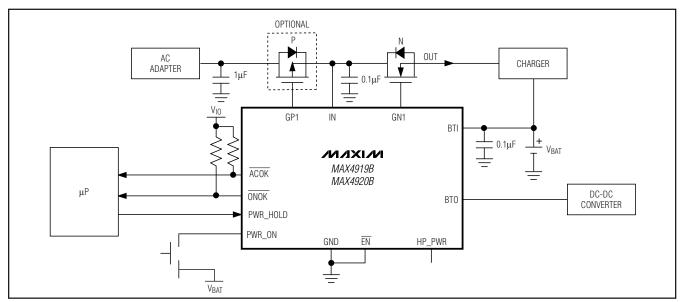

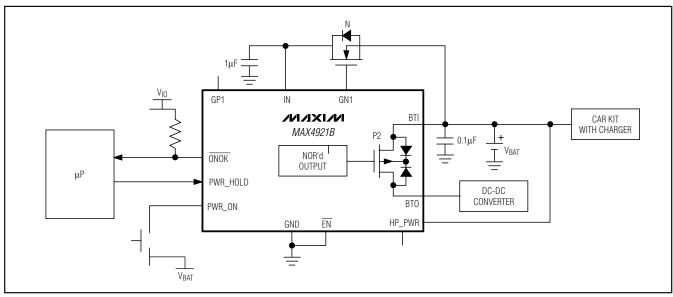

#### Car-Kit Application

Figures 13 and 14 illustrate the MAX4921B being utilized when the car-kit adapter, with built-in charger, is plugged in and connected directly to the battery. HP\_PWR goes through a 25ms debounce period and then a 1.2s one-shot is issued.

During this one-shot period, the  $\mu P$  needs to issue a PWR\_HOLD to keep P2 on before the one-shot period expires. The car kit then charges the battery and the battery supports the load. Note that the reverse-polarity protection p-channel MOSFET cannot be used in this application due to the direct connection of the battery to the source of the n-channel MOSFET.

Figure 9. MAX4919B/MAX4920B/MAX4921B Current-Limit Diagram

\_\_\_\_\_Chip Information

PROCESS: BiCMOS

Figure 10. Back-to-Back External MOSFET Configuration

Figure 11. MAX4919B/MAX4920B Always Powered From Battery (Car-Kit Adapter Never Plugged In)

Figure 12. MAX4919B/MAX4920B Timing Diagram For Non-Car-Kit Adapter Application

16 \_\_\_\_\_\_\_\_\_\_/II/XI/VI

Figure 13. MAX4920B With Car-Kit Adapter and Built-In Charger Connected

Figure 14. Timing Diagram For Car-Kit Adapter Application

### **Typical Operating Circuits**

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

| COMMON                                                           | DIMEN                                                     | SIONS                                 |                                                           | PACKAGE V                                                | ARIAT                               | TIONS                                 |                      |             |                |           |               |  |

|------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|-------------------------------------|---------------------------------------|----------------------|-------------|----------------|-----------|---------------|--|

| SYMBOL                                                           | MIN.                                                      | MAX.                                  |                                                           | PKG. CODE                                                | N                                   | D2                                    | E2                   | е           | JEDEC SPEC     | b         | [(N/2)-1] x e |  |

| Α                                                                | 0.70                                                      | 0.80                                  |                                                           | T633-1                                                   | 6                                   | 1.50-0.10                             | 2.30-0.10            | 0.95 BSC    | MO229 / WEEA   | 0.40-0.05 | 1.90 REF      |  |

| D                                                                | 2.90                                                      | 3.10                                  |                                                           | T633-2                                                   | 6                                   | 1.50-0.10                             | 2.30-0.10            | 0.95 BSC    | MO229 / WEEA   | 0.40-0.05 | 1.90 REF      |  |

| E.                                                               | 2.90                                                      | 3.10                                  |                                                           | T833-1                                                   | 8                                   | 1.50-0.10                             | 2.30-0.10            | 0.65 BSC    | MO229 / WEEC   | 0.30-0.05 | 1.95 REF      |  |

| A1                                                               | 0.00                                                      | 0.05                                  |                                                           | T833-2                                                   | 8                                   | 1.50-0.10                             | 2.30-0.10            | 0.65 BSC    | MO229 / WEEC   | 0.30-0.05 | 1.95 REF      |  |

| L                                                                | 0.20                                                      | 0.40                                  |                                                           | T833-3                                                   | 8                                   | 1.50-0.10                             | 2.30-0.10            | 0.65 BSC    | MO229 / WEEC   | 0.30-0.05 | 1.95 REF      |  |

| k                                                                | 0.25                                                      | MIN.                                  |                                                           | T1033-1                                                  | 10                                  | 1.50-0.10                             | 2.30-0.10            | 0.50 BSC    | MO229 / WEED-3 | 0.25-0.05 | 2.00 REF      |  |

| A2                                                               | 0.20                                                      | REF.                                  |                                                           | T1033-2                                                  | 10                                  | 1.50-0.10                             | 2.30-0.10            | 0.50 BSC    | MO229 / WEED-3 | 0.25-0.05 | 2.00 REF      |  |

|                                                                  |                                                           |                                       |                                                           | T1433-1                                                  | 14                                  | 1.70-0.10                             | 2.30-0.10            | 0.40 BSC    |                | 0.20-0.05 | 2.40 REF      |  |

|                                                                  |                                                           |                                       |                                                           | T1433-2                                                  | 14                                  | 1.70-0.10                             | 2.30-0.10            | 0.40 BSC    |                | 0.20-0.05 | 2.40 RFF      |  |

| NOTES:                                                           |                                                           |                                       |                                                           | 11433*2                                                  |                                     | 1.10 0.10                             | 2.55 6.15            | 0.10 300    |                | 0.20-0.00 | Z.40 NEF      |  |

| 2. COPL<br>3. WARP<br>4. PACK<br>5. DRAW<br>6. "N" II<br>7. NUME | ANARITY<br>AGE SH<br>AGE LEI<br>ING CO<br>S THE<br>BER OF | SHALL NO NGTH/P. NFORMS TOTAL N LEADS | NOT EXC<br>T EXCEE<br>ACKAGE TO JED<br>UMBER O<br>SHOWN A | . ANGLES IN<br>CEED 0.08 m<br>O 0.10 mm.<br>WIDTH ARE CC | DEGF<br>m.<br>DNSID<br>XCEP<br>EREN | REES.  BERED AS S T DIMENSIO CE ONLY. | PECIAL CHANS "D2" AN | ARACTERISTI |                |           | 2.40 NET      |  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600