# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

# Continuity of document content

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# Continuity of ordering part numbers

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

# CY8CKIT-050

# PSoC<sup>®</sup> 5LP Development Kit Guide

Doc. # 001-65816 Rev. \*J

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 http://www.cypress.com

#### Copyrights

© Cypress Semiconductor Corporation, 2011-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PUR-POSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# Contents

| 1. | Introdu | ction   |                                          | 5  |

|----|---------|---------|------------------------------------------|----|

|    | 1.1     |         | ontents                                  | 5  |

|    | 1.1     |         | Creator                                  |    |

|    | 1.2     |         | onal Learning Resources                  |    |

|    | 1.5     | 1.3.1   | Beginner Resources                       |    |

|    |         | 1.3.1   | 8                                        |    |

|    |         |         | Learning from Peers                      |    |

|    |         |         | More Code Examples                       |    |

|    | 1.4     |         | mentation Conventions                    |    |

|    | 1.4     | Docui   |                                          | 0  |

| 2. | Getting | Starte  | ed                                       | 9  |

|    | 2.1     | DVD I   | Installation                             | 9  |

|    | 2.2     | Install | I Hardware                               | 10 |

|    | 2.3     | Install | l Software                               | 10 |

|    | 2.4     | Unins   | tall Software                            | 10 |

|    | 2.5     | Verify  | r Kit Version                            | 10 |

|    |         |         |                                          |    |

| 3. | Kit Ope |         |                                          | 11 |

|    | 3.1     | Progra  | amming PSoC 5LP Device                   | 11 |

|    |         |         |                                          |    |

| 4. | Hardwa  |         |                                          | 15 |

|    | 4.1     | •       | m Block Diagram                          |    |

|    | 4.2     |         | ional Description                        |    |

|    |         | 4.2.1   | Power Supply                             |    |

|    |         |         | 4.2.1.1 Power Supply Jumper Settings     |    |

|    |         |         | 4.2.1.2 Grounding Scheme                 |    |

|    |         |         | 4.2.1.3 Low-Power Functionality          |    |

|    |         |         | 4.2.1.4 AC/DC Adaptor Specifications     |    |

|    |         |         | 4.2.1.5 Battery Specifications           |    |

|    |         | 4.2.2   | 0 0                                      |    |

|    |         |         | 4.2.2.1 Onboard Programming Interface    |    |

|    |         |         | 4.2.2.2 JTAG/SWD Programming             |    |

|    |         | -       |                                          |    |

|    |         | 4.2.4   |                                          |    |

|    |         | 4.2.5   | 32-kHz and 24-MHz Crystal                |    |

|    |         | 4.2.6   |                                          |    |

|    |         |         | 4.2.6.1 Functional Description           |    |

|    |         | 4.2.7   | PSoC 5LP Development Kit Expansion Ports |    |

|    |         |         | 4.2.7.1 Port D                           |    |

|    |         |         | 4.2.7.2 Port E                           |    |

|    |         | 4.2.8   | RS-232 Interface                         |    |

|    |         | 4.2.9   | Prototyping Area                         | 27 |

|    |         | 4.2.10 Character LCD                | 28 |

|----|---------|-------------------------------------|----|

|    |         | 4.2.11 CapSense Sensors             |    |

|    |         |                                     |    |

| 5. | Code Ex | amples                              | 31 |

|    | 5.1     | Introduction                        | 31 |

|    |         | 5.1.1 Programming the Code Examples |    |

|    | 5.2     | Project: VoltageDisplay_SAR_ADC     |    |

|    |         | 5.2.1 Project Description           | 32 |

|    |         | 5.2.2 Hardware Connections          | 32 |

|    |         | 5.2.3 SAR ADC Configuration         | 32 |

|    |         | 5.2.4 Verify Output                 |    |

|    | 5.3     | Project: VoltageDisplay_DelSigADC   |    |

|    |         | 5.3.1 Project Description           |    |

|    |         | 5.3.2 Hardware Connections          |    |

|    |         | 5.3.3 DelSig ADC Configuration      |    |

|    |         | 5.3.4 Verify Output                 |    |

|    | 5.4     | Project: IntensityLED               |    |

|    |         | 5.4.1 Project Description           |    |

|    |         | 5.4.2 Hardware Connections.         |    |

|    |         | 5.4.3 Verify Output                 |    |

|    | 5.5     | Project: LowPowerDemo               |    |

|    |         | 5.5.1 Project Description           |    |

|    |         | 5.5.2 Hardware Connections          |    |

|    | 5.6     | 5.5.3 Verify Output                 |    |

|    | 5.0     | Project: CapSense                   |    |

|    |         | 5.6.2 Hardware Connections          |    |

|    |         | 5.6.3 Verify Output                 |    |

|    | 5.7     | Project: ADC_DAC                    |    |

|    | 0.7     | 5.7.1 Project Description           |    |

|    |         | 5.7.2 Hardware Connections          |    |

|    |         | 5.7.3 Verify Output                 |    |

|    |         |                                     |    |

| Α. | Appendi | x                                   | 41 |

|    | A.1     | Schematic                           | 41 |

|    | A.2     | Board Layout                        |    |

|    | 7.1.2   | A.2.1 PDC-09356 Top                 |    |

|    |         | A.2.2 PDC-09356 Power               |    |

|    |         | A.2.3 PDC-09356 Ground              |    |

|    |         | A.2.4 PDC-09356 Bottom              |    |

|    | A.3     | Bill of Materials (BOM)             |    |

|    | A.4     | Pin Assignment Table                |    |

|    |         | -                                   |    |

| Revision History          | 60 |

|---------------------------|----|

| Document Revision History | 60 |

Thank you for your interest in the CY8CKIT-050 PSoC<sup>®</sup> 5LP Development Kit. This kit allows you to develop precision analog and low-power designs using PSoC 5LP. You can design your own projects with PSoC Creator™ or alter the sample projects provided with this kit.

The CY8CKIT-050 PSoC 5LP Development Kit is based on the PSoC 5LP family of devices. PSoC 5LP is a Programmable System-on-Chip<sup>™</sup> platform for 8-bit, 16-bit, and 32-bit applications. It combines precision analog and digital logic with a high-performance CPU. With PSoC, you can create the exact combination of peripherals and integrated proprietary IP to meet your application requirements.

# 1.1 Kit Contents

The PSoC 5LP Development Kit contains:

- Development board

- Kit DVD

- Quick start guide

- USB A to mini-B cable

- 3.3-V LCD module

- Jumper wires and jumper shunts

Inspect the contents of the kit; if you find any part missing, contact your nearest Cypress sales office for help.

# 1.2 **PSoC Creator**

Cypress's PSoC Creator software is a state-of-the-art, easy-to-use integrated development environment (IDE) that introduces a hardware and software design environment based on classic schematic entry and revolutionary embedded design methodology.

With PSoC Creator, you can:

- Create and share user-defined, custom peripherals using hierarchical schematic design.

- Automatically place and route select components and integrate simple glue logic, normally located in discrete muxes.

- Trade off hardware and software design considerations allowing you to focus on what matters and getting to market faster.

PSoC Creator also enables you to tap into an entire tools ecosystem with integrated compiler tool chains, RTOS solutions, and production programmers to support both PSoC 3 and PSoC 5LP.

# 1.3 Additional Learning Resources

Visit http://www.cypress.com/go/psoc5 for additional learning resources in the form of datasheets, application notes, and technical reference manual.

1.3.1 Beginner Resources

AN77759 - Getting Started with PSoC 5

PSoC Creator Training

# 1.3.2 Engineers Looking for More

AN54460 - PSoC 3, PSoC 4, and PSoC 5LP Interrupts

AN52705 - PSoC 3 and PSoC 5LP - Getting Started with DMA

AN52701 - PSoC 3 and PSoC 5LP - Getting Started with Controller Area Network (CAN)

AN54439 - PSoC 3 and PSoC 5LP External Crystal Oscillators

AN52927 - PSoC 3 and PSoC 5LP - Segment LCD Direct Drive

Cypress continually strives to provide the best support. Click here to view a growing list of application notes for PSoC 3, PSoC 4, and PSoC 5LP.

## 1.3.3 Learning from Peers

Cypress Developer Community Forums

# 1.3.4 More Code Examples

PSoC Creator provides several example projects that make code development fast and easy. To access these example projects, click on **Find Example Project...** under the **Example and Kits** section in the **Start Page** of PSoC Creator or navigate to **File > Open > Example Project...**

Figure 1-1. Find Example Project

| Start Page                                      |   | File | Edit         | ⊻iew | <u>D</u> ebug | Project | Build | l <u>T</u> ools    | <u>W</u> indow | He |

|-------------------------------------------------|---|------|--------------|------|---------------|---------|-------|--------------------|----------------|----|

| PSoC <sup>®</sup> Creator™                      |   |      | <u>N</u> ew  |      |               | •       |       | BX                 | 50             | -  |

| See creator                                     |   |      | <u>O</u> pen |      |               | •       | â     | Project/V          | Vorkspace      |    |

| Recent Projects                                 | * |      | <u>A</u> dd  |      |               | Þ       | 2     | <u>F</u> ile       | Ctrl+O         | I  |

| Create New Project<br>Open Existing Project     |   |      | ⊆lose        |      | C             | trl+F4  |       | Exa <u>m</u> ple I | Project        |    |

| Getting Started                                 |   |      |              |      |               |         |       |                    |                |    |

| PSoC Creator Start Page<br>Quick Start Guide    |   |      |              |      |               |         |       |                    |                |    |

| Intro to PSoC<br>Intro to PSoC Creator          |   |      |              |      |               |         |       |                    |                |    |

| PSoC Creator Training                           | E |      |              |      |               |         |       |                    |                |    |

| Design Tutorials<br>Getting Started With PSoC 3 |   |      |              |      |               |         |       |                    |                |    |

| Getting Started With PSoC 4                     |   |      |              |      |               |         |       |                    |                |    |

| Getting Started With PSoC 5LP                   |   |      |              |      |               |         |       |                    |                |    |

| Examples and Kits                               |   |      |              |      |               |         |       |                    |                |    |

| Find Example Project                            |   |      |              |      |               |         |       |                    |                |    |

| 🖽 Kits 🤤                                        |   |      |              |      |               |         |       |                    |                |    |

The Find Example Project section has various filters that help you locate the most relevant project. PSoC Creator provides several starter designs. These designs highlight features that are unique to PSoC devices. They allow you to create a design with various components, instead of creating an empty design; the code is also provided. To use a starter design for your project, navigate to **File > New > Project** and select the design required.

| Figure 1 | -2. | New | Project |

|----------|-----|-----|---------|

|          |     |     |         |

| Empty T  | emplates                  |                                                                                                                                                                                         |   |

|----------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|          | Empty PSoC 3 Design       | Creates a PSoC 3, 8 bit, design project.                                                                                                                                                |   |

|          | Empty PSoC 4 Design       | Creates a PSoC 4, 32 bit, design project.                                                                                                                                               |   |

|          | Empty PSoC 5LP Design     | Creates a PSoC 5LP, 32 bit, design project.                                                                                                                                             | = |

| PSoC 3   | Starter Designs           |                                                                                                                                                                                         |   |

| 50       | ADC_DMA_VDAC              | Shows how to transfer data from an ADC to a DAC using DMA with no CPU intervention.                                                                                                     |   |

| Pa       | DelSig_16Channel          | Shows a 16-channel, 12-bit Delta Sigma ADC in PSoC 3 sequenced in hardware; samples are<br>transferred from ADC to SRAM using DMA - without processor intervention.                     |   |

| 50       | DelSig_l2CM               | Shows the 16-bit differential ADC, hardware multiplexed into 8 channels and transported over<br>I2C.                                                                                    |   |

| ъ        | DelSig_I2CS               | Shows the 16-bit differential ADC, hardware multiplexed into 8 channels and transported over<br>I2C.                                                                                    |   |

| РЗ       | DelSig_SPIM               | Shows the 16-bit differential ADC, hardware multiplexed into 8 channels and transported over<br>SPI.                                                                                    |   |

| Pa       | Filter_ADC_VDAC           | Shows how to filter an analog input all in hardware, and provides all the DMA setup to transfer the<br>data from the ADC directly to the Digital Filter Block, bypassing the processor. | в |

| 50       | HW_Fan_Control_with_Alert | Shows how performing fan control in hardware completely frees up the CPU.                                                                                                               |   |

| B PSoC 4 | Starter Designs           |                                                                                                                                                                                         |   |

| lame:    | Design01                  |                                                                                                                                                                                         |   |

| ocation: | C:\Program Files\Cypress  |                                                                                                                                                                                         |   |

| Advance  | ed                        |                                                                                                                                                                                         |   |

The example projects and starter designs are designed for the CY8CKIT-001 PSoC Development Kit. However, these projects can be converted for use with the CY8CKIT-030 PSoC 3 Development Kit or CY8CKIT-050 PSoC 5LP Development Kit by following the procedure in the knowledge base article Migrating Project from CY8CKIT-001 to CY8CKIT-030 or CY8CKIT-050.

# **1.4** Documentation Conventions

## Table 1-1. Document Conventions for Guides

| Convention         | Usage                                                                                                                                  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Courier New        | Displays file locations, user entered text, and source code:<br>C:\cd\icc\                                                             |

| Italics            | Displays file names and reference documentation:<br>Read about the <i>sourcefile.hex</i> file in the <i>PSoC Designer User Guide</i> . |

| [Bracketed, Bold]  | Displays keyboard commands in procedures:<br>[Enter] or [Ctrl] [C]                                                                     |

| File > Open        | Represents menu paths:<br>File > Open > New Project                                                                                    |

| Bold               | Displays commands, menu paths, and icon names in procedures:<br>Click the <b>File</b> icon and then click <b>Open</b> .                |

| Times New Roman    | Displays an equation:<br>2+2=4                                                                                                         |

| Text in gray boxes | Describes cautions or unique functionality of the product.                                                                             |

This chapter describes how to install and configure the PSoC 5LP Development Kit. Kit Operation chapter on page 11 describes the kit operation. It explains how to program a PSoC 5LP device with PSoC Programmer and use the kit with the help of a code example. To reprogram the PSoC device with PSoC Creator, see the installation instructions for PSoC Creator. Hardware chapter on page 15 details the hardware operation. Code Examples chapter on page 31 provides instructions to create a simple code example. The Appendix on page 41 provides the Schematic on page 41 and Bill of Materials (BOM) on page 51 associated with the PSoC 5LP Development Kit.

# 2.1 DVD Installation

Follow these steps to install the PSoC 5LP Development Kit software:

1. Insert the kit DVD into the DVD drive of your PC. The DVD is designed to auto-run and the kit menu appears.

Figure 2-1. Kit Menu

Note If auto-run does not execute, double-click cyautorun.exe on the root directory of the DVD.

### Figure 2-2. DVD Root Directory

After the installation is complete, the kit contents are available at the following location: <Install\_Directory>\Cypress\PSoC 5LP Development Kit\<version>

# 2.2 Install Hardware

No hardware installation is required for this kit.

# 2.3 Install Software

When installing the PSoC 5LP Development Kit, the installer checks if your system has the required software. These include PSoC Creator, PSoC Programmer, Windows Installer, .NET, and Keil Complier. If these applications are not installed, the installer installs them in your PC before installing the kit. If Acrobat Reader application is not installed in your PC, then the installer provides the link to install the same and this does not prevent kit installation. Note that Adobe reader is required to view the kit documents.

Install the following software from the kit DVD:

- PSoC Creator 3.0 or later

- PSoC Programmer 3.19.1 or later

Note When installing PSoC Programmer, select Typical on the Installation Type page.

- Code examples (provided in the Firmware folder)

# 2.4 Uninstall Software

The software can be uninstalled using one of the following methods:

- Go to Start > Control Panel > Add or Remove Programs; select the Remove button.

- Go to Start > All Programs > Cypress > Cypress Update Manager > Cypress Update Manager; select the Uninstall button.

- Insert the installation DVD and click Install PSoC 5LP Development Kit button. In the Cylnstaller for PSoC 5LP Development Kit 2.1 window, select Remove from the Installation Type drop-down menu. Follow the instructions to uninstall.

# 2.5 Verify Kit Version

To know the kit revision, look for the white sticker on the bottom left, on the reverse of the kit box. If the revision reads CY8CKIT-050B, then, you own the latest version.

To upgrade CY8CKIT-050/CY8CKIT-050A to CY8CKIT-050B, you can purchase our latest kits at http://www.cypress.com/go/CY8CKIT-050.

The code examples in the PSoC 5LP Development Kit help you develop precision analog applications using the PSoC 5LP family of devices. The board also has hooks to enable low-power measurements for low-power application development and evaluation.

# 3.1 **Programming PSoC 5LP Device**

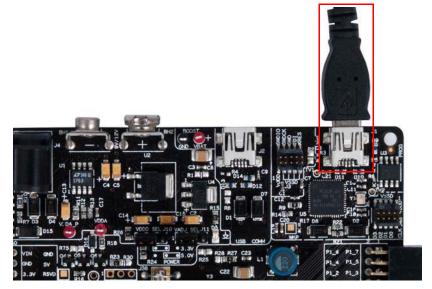

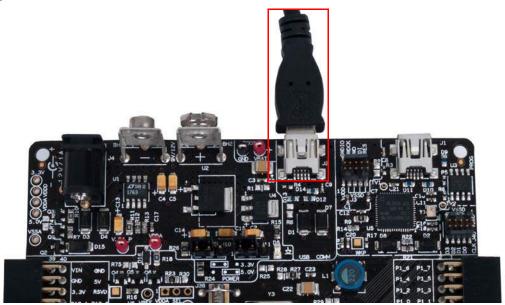

The default programming interface for the board is a USB-based onboard programming interface. To program the device, plug the USB cable to the programming USB connector J1, as shown in Figure 3-1.

Figure 3-1. Connect USB Cable to J1

When plugged in, the board enumerates as DVKProg5. After enumeration, initiate, build, and then program using PSoC Creator.

When using onboard programming, it is not necessary to power the board from the 12-V or 9-V DC supply or a battery. You can use the USB power to the programming section.

If the board is already powered from another source, plugging in the programming USB does not damage the board.

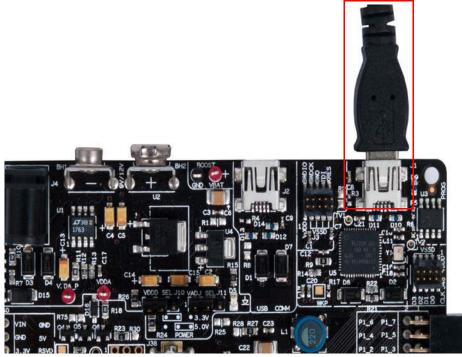

The PSoC 5LP device on the board can also be programmed using a MiniProg3 (CY8CKIT-002). To use MiniProg3 for programming, use the connector J3 on the board, as shown in Figure 3-2.

**Note** The MiniProg3 (CY8CKIT-002) is not part of the PSoC 5LP Development Kit contents. It can be purchased from the Cypress Online Store.

Figure 3-2. Connect MiniProg3

With the MiniProg3, programming is similar to the onboard programmer; however, the setup enumerates as a MiniProg3.

The Select Debug Target window may be displayed, as shown in the following figure.

Figure 3-3. Select Debug Target

| L ← PSoC 5LP CY8C5868AXI-LP035 | POWER = 3<br>FREQUENCY = 1500000<br>PROTOCOL = SWD<br>DVKProg5 version 1.19 |

|--------------------------------|-----------------------------------------------------------------------------|

| Show all targets               | Port Setting Port Acquire                                                   |

Click Port Acquire. The window appears as follows. Click Connect to start programming.

# Figure 3-4. Click Connect

| Select Debug Target | 8 ×                                                                                                                     |

|---------------------|-------------------------------------------------------------------------------------------------------------------------|

| E⊢                  | PSoC 5LP CY8C5868AXI-LP035<br>PSoC 5LP (ARM CM3)<br>Silicon ID: 0x2BA01477<br>Revision: PRODUCTION<br>Target unacquired |

| Show all targets    | <u>C</u> onnect     OK                                                                                                  |

# 4. Hardware

# 4.1 System Block Diagram

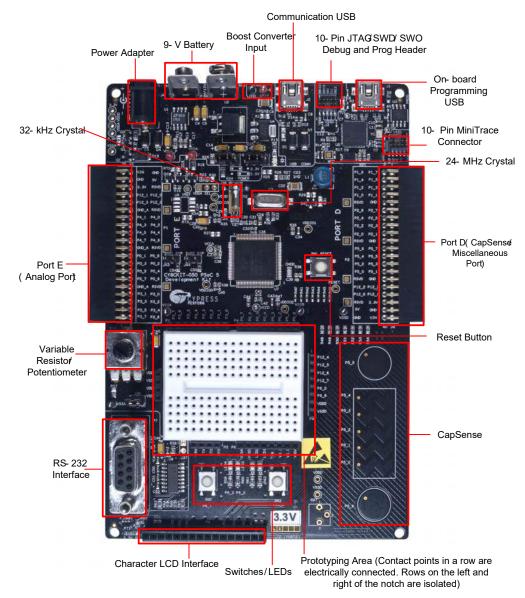

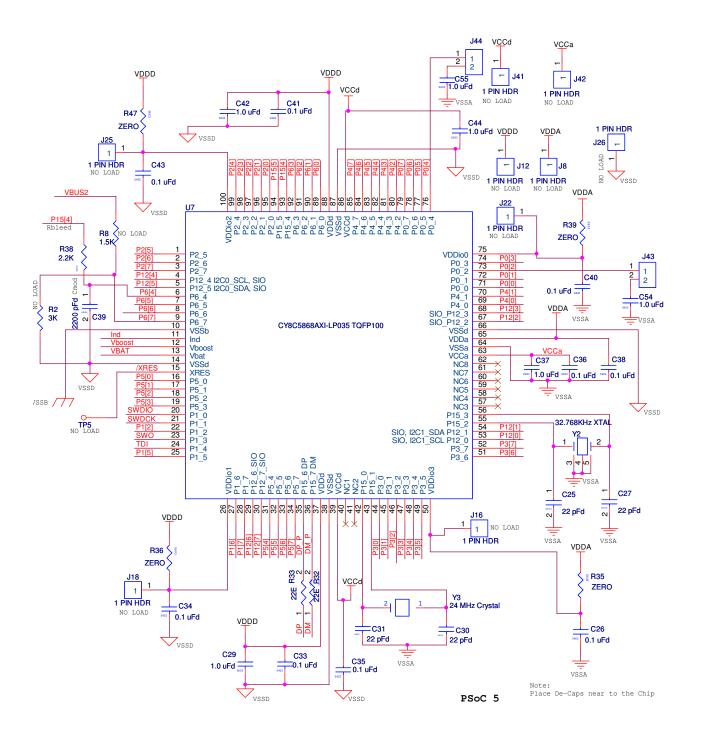

The PSoC 5LP Development Kit has the following sections:

- Power supply system

- Programming interface

- USB communications

- Boost convertor

- PSoC 5LP and related circuitry

- 32-kHz crystal

- 24-MHz crystal

- Port E (analog performance port) and port D (CapSense<sup>®</sup> or generic port)

- RS-232 communications interface

- Prototyping area

- Character LCD interface

- CapSense buttons and sliders

**Note** P0[2] is connected to the SAR bypass capacitor C40, which can be selected by shorting jumper J43. P0[4] is connected to the SAR bypass capacitor C55, which can be selected by shorting jumper J44.

Hardware

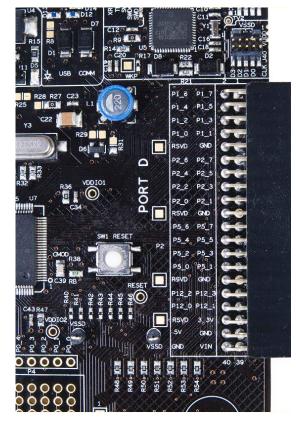

# Figure 4-1. PSoC 5LP Development Kit Details

# 4.2 Functional Description

# 4.2.1 Power Supply

The power supply system on this board is versatile; input supply can be from the following sources:

- 9-V or 12-V wall wart supply using connector J4

- 9-V battery connector using connectors BH1 and BH2

- USB power from communications section using connector J2

- USB power from the onboard programming section using connector J1

- Power from JTAG/SWD programming interface using connector J3

- Power through boost convertor that uses the input test points VBAT and GND

The board power domain has five rails:

- Vin rail: This is where the input of the onboard regulators are connected. This domain is powered through protection diodes.

- **5-V rail**: This is the output of the 5-V regulator U2. The rail has a fixed 5-V output regardless of jumper settings. The voltage in this rail can be less than 5 V only when the board is powered by the USB. This 5-V rail powers the circuits that require fixed 5-V supply.

- 3.3-V rail: This is the output of the 3.3-V regulator U4. This rail remains 3.3 V regardless of jumper settings or power source changes. It powers the circuits requiring fixed 3.3-V supply such as the onboard programming section.

- Vddd rail: This rail provides power to the digital supply for the PSoC device. It can be derived from either the 5-V or 3.3-V rail. The selection is made using J10 (3-pin jumper).

- Vdda rail: This rail provides power to the analog supply of the PSoC device. It is the output of a low-noise regulator U1. The regulator is a variable output voltage and can be either 3.3 V or 5 V. This is done by changing the position on J11 (3-pin jumper).

The following block diagram shows the structure of the power system on the board.

USB 3.3 V 5 V Programming USB Vin Communication 3.3-V Regulator Power Vddd Vddd Selection (J10) 9-V Battery 5 V 5-V Regulator 12-V/9-V Wall Vdda Vdda wart 5-V/3.3-V Analog Selection Regulator (J11)

Figure 4-2. Power System Structure

4.2.1.1 Power Supply Jumper Settings

Figure 4-3. Jumper Settings

Two jumpers govern the power rails on the board. J10 is responsible for the selection of Vddd (digital power) and J11 selects the VADJ of Vdda (analog power).

The jumper settings for each power scheme are as follows.

| Powering Scheme            | Jumper Settings                                                                                             |

|----------------------------|-------------------------------------------------------------------------------------------------------------|

| Vdda = 5 V, Vddd = 5 V     | J10 in 5-V setting and J11 in 5-V setting.                                                                  |

| Vdda = 3.3 V, Vddd = 3.3 V | J10 in 3.3-V setting and J11 in 3.3-V setting.                                                              |

| Vdda = 5 V, Vddd = 3.3 V   | J10 in 3.3-V setting and J11 in 5-V setting.                                                                |

| Vdda = 3.3 V, Vddd = 5 V   | Can be achieved, but is an invalid condition because the PSoC 5LP silicon performance cannot be guaranteed. |

#### Warning:

- The PSoC device performance is guaranteed when Vdda is greater than or equal to Vddd. Failure to meet this condition can have implications on the silicon performance.

- The power supply of the I/Os, Vddio, is connected to Vddd. Therefore, any input voltage to the PSoC I/Os must not exceed the Vddd.

- When USB power is used, ensure a 3.3-V setting on both analog and digital supplies. This is because the 5-V rail of the USB power is not accurate and is not recommended. If you require 5-V operation, it is recommended to use an external power supply adapter or a 9-V battery.

- If separate analog and digital power supplies are used, the analog supply ramp rate may be slower than that of the digital supply. This may cause I/Os to be in an indeterminate state until the power supplies stabilize.

## 4.2.1.2 Grounding Scheme

The board design considers analog designs as major target applications. Therefore, the grounding scheme in the board is unique to ensure precision analog performance.

The board has three types of ground:

- GND This is the universal ground where all the regulators are referred. Both Vssd and Vssa connect to this ground through a star connection.

- Vssd This is the digital ground and covers the digital circuitry on the board, such as RS-232 and LCD.

- Vssa This is the analog ground and covers the grounding for analog circuitry present on the board, such as the reference block.

When creating custom circuitry in the prototyping area provided on the board, remember to use the Vssa for the sensitive analog circuits and Vssd for the digital ones.

Port E on the board is the designated analog expansion connector. This connector brings out ports 0, 3, and 4, which are the best performing analog ports on PSoC 3 and PSoC 5 devices. Port E has two types of grounds. One is the analog ground (GND\_A in the silkscreen, Vssa in the schematic), which connects directly to the analog ground on the board. The other ground, known as GND, is used for the digital and high-current circuitry on the expansion board. This differentiation on the connector grounds helps the expansion board designer to separate the analog and digital ground on any high-precision analog boards being designed for port E.

## 4.2.1.3 Low-Power Functionality

The kit also facilitates application development, which requires low power consumption. Low-power functions require a power measurement capability, also available in this kit.

The analog supply is connected to the device through the  $0-\Omega$  resistor (R23). By removing this resistor and connecting an ammeter in series using the test points, Vdda\_p and Vdda, you can measure the analog power used by the system.

The digital supply can be monitored by removing the connection on jumper J10 and connecting an ammeter in place of the short. This allows to measure the digital power used by the system.

The board provides the ability to measure analog and digital power separately. To measure power at a single point, rather than at analog and digital separately, remove resistor R23 to disconnect the analog regulator from powering the Vdda and short Vdda and Vddd through R30. The net power can now be measured at jumper J10 similar to the digital power measurement. To switch repeatedly between R23 and R30, moving around the 0- $\Omega$  resistors can be discomforting. Hence, a J38 (unpopulated) is provided to populate a male 3-pin header and have a shorting jumper in the place of R23/R30.

While measuring device power, make the following changes in the board to avoid leakage through other components that are connected to the device power rails.

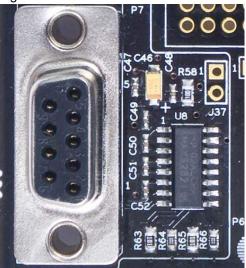

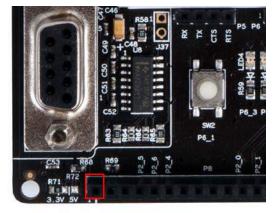

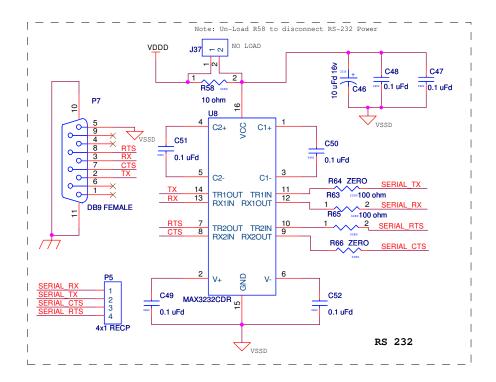

- Disconnect the RS-232 power by disconnecting R58. An additional jumper capability is available as J37 if you populate it with a 2-pin male header.

- Disconnect the potentiometer by disconnecting J30.

- Ground the boost pins if boost operation is not used by populating R1, R28, and R29. Also make sure R25 and R31 are not populated.

## 4.2.1.4 AC/DC Adaptor Specifications

Use adaptors with the following specifications:

- Input voltage: 100 to 240 VAC, 50 Hz to 60 Hz, 1A

- Output voltage: 12 VDC, 1A

- Power output: 12 W

- Polarization: Positive center

- Certification: CE certified

Some recommended part numbers include EPSA120100U-P5P-EJ (CUI Inc.) and LTE12W-S2 (Li Tone Electronics Co. Ltd).

## 4.2.1.5 Battery Specifications

Use batteries with the following specifications:

- Battery size: 6LR61 (9 V)

- Output voltage: 9 VDC

- Type: Non-rechargeable alkaline consumer batteries

- RoHS status: RoHS compliant

- Lead free status: Pb-free

Some recommended part numbers include 6LR61XWA/1SB (Panasonic), MN1604 (Duracell), and 6LR61 (Energizer).

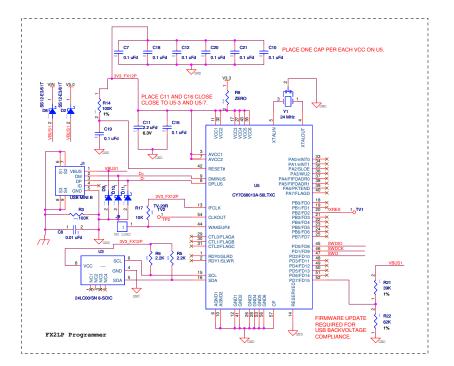

# 4.2.2 Programming Interface

This kit allows programming in two modes:

- Using the onboard programming interface

- Using the JTAG/SWD programming interface with a MiniProg3

## 4.2.2.1 Onboard Programming Interface

The onboard programmer interfaces with your PC through a USB connector, as shown in Figure 4-4.

Figure 4-4. Onboard Programming Interface

When the USB programming is plugged into the PC, it enumerates as DVKProg5 and you can use the normal programming interface from PSoC Creator to program this board through the onboard programmer. Pins P1[0] and P1[1] are connected to the onboard programmer. If you are using the onboard programmer, these pins should not be used for any other function.

A  $0-\Omega$  resistor R9 is provided on the board to disconnect power to the onboard programmer.

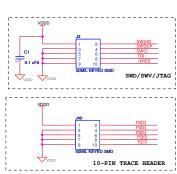

## 4.2.2.2 JTAG/SWD Programming

Apart from the onboard programming interface, the board also provides the option of using the MiniProg3. This interface is much faster than the onboard program interface. The JTAG/SWD programming is done through the 10-pin connector, J3.

#### Figure 4-5. JTAG/SWD Programming

The JTAG/SWD programming using J3 requires the MiniProg3 programmer, which can be purchased from http://www.cypress.com/go/CY8CKIT-002.

Note While using MiniProg3, only the Reset mode is supported with this kit.

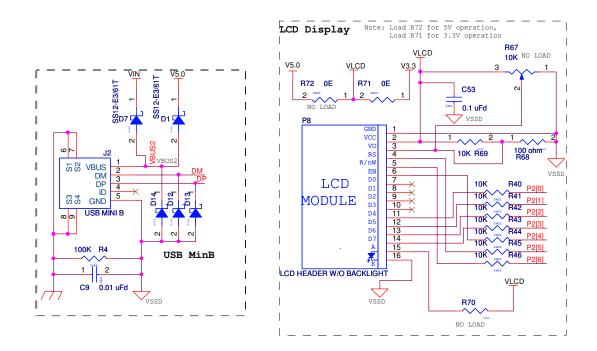

# 4.2.3 USB Communication

The board has a USB communications interface that uses the connector, as shown in Figure 4-6. The USB connector connects to the D+ and D– lines on the PSoC to enable development of USB applications using the board. This USB interface can also supply power to the board, as discussed in Power Supply on page 16.

Figure 4-6. USB Interface

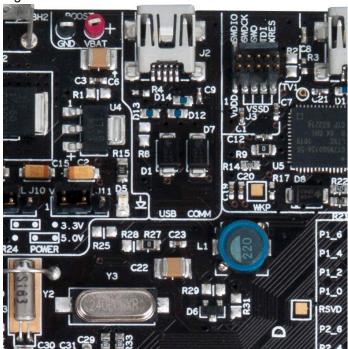

# 4.2.4 Boost Convertor

The PSoC 5LP device has the unique capability of working from a voltage supply as low as 0.5 V. This is possible using the boost convertor. The boost convertor uses an external inductor and a diode. These components are prepopulated on the board. Figure 4-7 shows the boost convertor.

To enable the boost convertor functionality, make the following hardware changes on the board.

- Populate resistors R25, R27 (populated by default), R29, and R31 with 0-Ω resistors.

Note See the Bill of Materials (BOM) on page 51 for the manufacturer part number.

- Ensure that R1 and R28 are not populated

After making these changes, you can configure the project to create a boost convertor-based design. The input power supply to the boost convertor must be provided through the test points marked Vbat and GND.

Figure 4-7. Boost Converter

# 4.2.5 32-kHz and 24-MHz Crystal

PSoC 5LP has an on-chip real time clock (RTC), which can function in sleep. This requires an external 32-kHz crystal, which is provided on the board to facilitate RTC-based designs. The PSoC 5LP also has an external MHz crystal option in applications where the IMO tolerance is not satisfactory. In these applications, the board has a 24-MHz crystal to provide an accurate main oscillator.

# 4.2.6 Protection Circuit

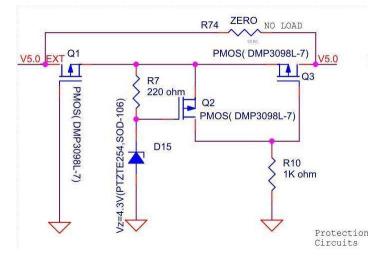

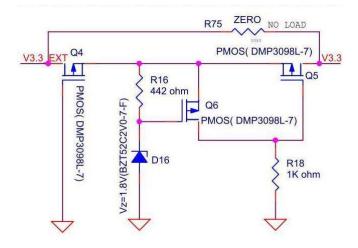

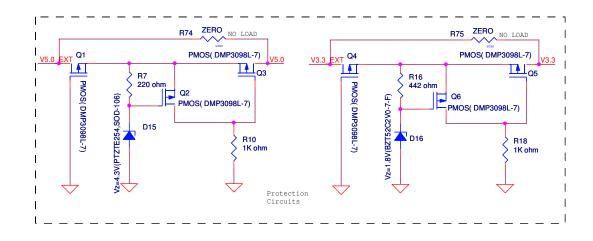

A reverse-voltage and over-voltage protection circuit is added to the expansion port on the 5-V and 3.3-V lines.

The protection circuit consists of two P-channel MOSFET on the power line, allowing the current to flow from input to output depending on the voltages applied at the external board connector. Figure 4-8 and Figure 4-9 are protection circuits placed between EBK and the onboard components on the 5-V and 3.3-V lines.

Figure 4-8. Schematic for Protection Circuit on 5-V Power Line

Figure 4-9. Schematic for Protection Circuit on 3.3-V Power Line

## 4.2.6.1 Functional Description

The protection circuit will protect from a maximum over-voltage or reverse-voltage of 12 V. The cutoff voltage on the 5-V line is 5.7 V and on the 3.3-V line is 3.6 V. This means, if you apply more than this voltage level from the external board connector side, the p-MOS Q5 will turn off, thus protecting PSoC and other onboard components. The current consumption of these protection circuits is less than 6 mA.

When voltage from the external connector is between 1.8 V and 3.3 V, the p-MOS Q4 conducts. Because the voltage across R16 is less than the threshold voltage (Vth) of p-MOS Q6, it will turn off and the p-MOS Q5 conducts, allowing voltage supply to the DVK.

When the external power supply exceeds 3.3 V, the p-MOS Q5 starts conducting. This eventually turns off p-MOS Q6 at 3.6 V, protecting the DVK from over-voltage.

When a reverse voltage is applied across the protection circuit from the external connector side, Q4 P-MOS will turn off, thus protecting the components on the board from reverse voltage.

If you are using the regulator power supply from the board to power the external modules, both the P-MOS Q4 and Q5 will always be in the On state, allowing the flow of current with a maximum of 22 mV drop across the circuit when the current consumed by the external module is 150 mA.

**Note** The working of protection circuit on the 3.3-V and 5-V lines is as described. For the purpose of explanation, the annotation of 3.3-V protection circuitry (Figure 4-9) is used.

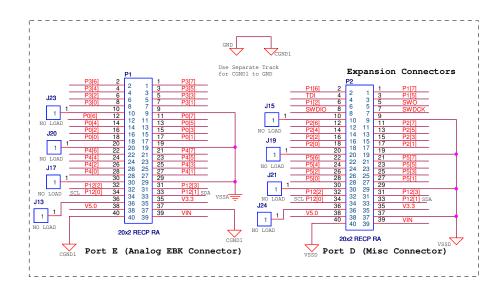

## 4.2.7 PSoC 5LP Development Kit Expansion Ports

The PSoC 5LP Development Kit has two expansion ports, port D and port E, each with their own unique features.

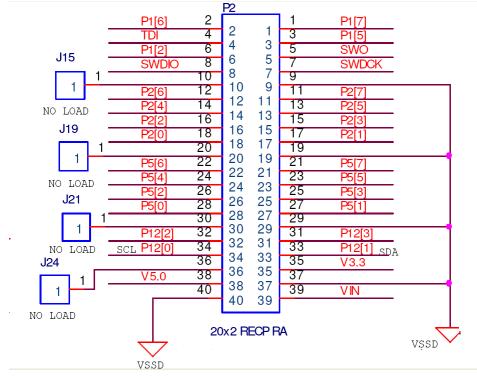

## 4.2.7.1 Port D

This is the miscellaneous port designed to handle CapSense-based application boards and digital application boards. The signal routing to this port adheres to the stringent requirements needed to provide good performance CapSense. This port can also be used for other functions and expansion board kits (EBKs).

This port is not designed for precision analog performance. The pins on the port are functionally compatible to port B of the PSoC Development Kit. Any project made to function on port B of the PSoC Development Kit can be easily ported over to port D on this board. A caveat to this is that there is no opamp available on this port; therefore, opamp-based designs are not recommended for use on this port.

The following figure shows the pin mapping for the port.

## Figure 4-10. Port D

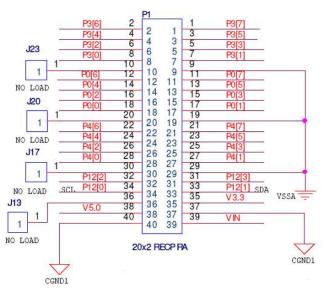

# 4.2.7.2 Port E

This is the analog port on the kit and has special layout considerations. It also brings out all analog resources such as dedicated opamps to a single connect. Therefore, this port is ideal for precision analog design development. This port is functionally compatible to port A of the PSoC Development Kit and it is easy to port an application developed on port A.

This port has two types of grounds, CGND1 and CGND2. The two grounds are connected to the GND on the board, but are provided for expansion boards designed for analog performance. The expansion boards have an analog and digital ground. The two grounds on this port help to keep it distinct even on this board until it reaches the GND plane.

Figure 4-11. Port E

CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. \*J

# 4.2.8 RS-232 Interface

The board has an RS-232 transceiver for designs using RS-232 (UART). The RS-232 section power can be disconnected through a single resistor R58. This is useful for low-power designs.

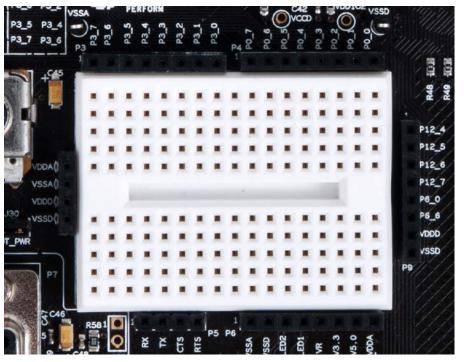

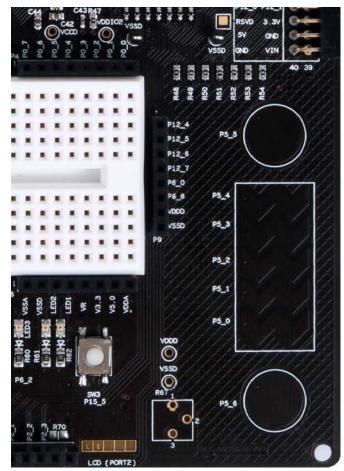

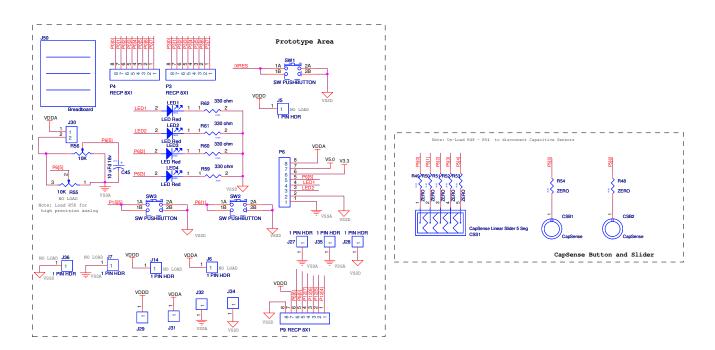

# 4.2.9 Prototyping Area

The prototyping area on the board has two complete ports of the device for simple custom circuit development. The ports in the area are port 0 and port 3, which bring out the four dedicated opamp pins on the device. Therefore, these ports can be used with the prototyping area to create simple yet elegant analog designs. It also brings SIOs such as port 12[4], port 12[5], port 12[6], and port 12[7] and GPIOs such as port P6[0] and port P6[6]. Power and ground connections are available close to the prototyping space for convenience.

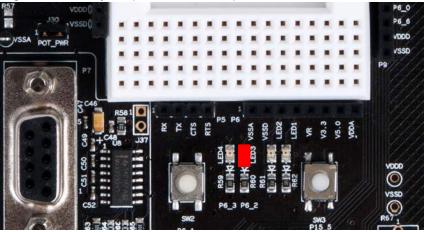

The area also has four LEDs and two switches for applications development. The two switches on the board are hard-wired to port 15[5] and port 6[1]. Two LEDs out of the four are hard-wired to port 6[2] and port 6[3] and the other two are brought out on pads closer to the prototyping area.

#### Figure 4-13. Prototyping Area

This area also comprises of a potentiometer to be used for analog system development work. The potentiometer connects from Vdda, which is a noise-free supply and is hence capable of being used for low-noise analog applications. The potentiometer output is available on P6[5] and VR on header P6 in the prototyping area.

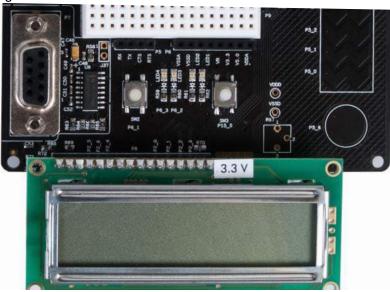

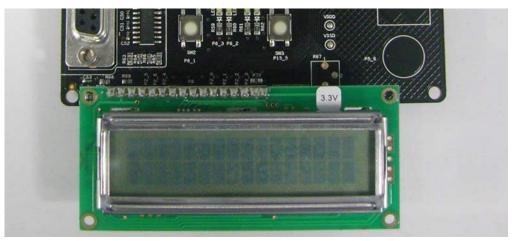

## 4.2.10 Character LCD

The kit has a character LCD module, which goes into the character LCD header, P8. The LCD runs on a 3.3-V supply and can function regardless of the voltage on which PSoC is powered. A  $0-\Omega$  resistor setting is available on the LCD section (R71/72), making it possible to convert it to a 3.3-V LCD.

**CAUTION** When the resistor is shifted to support a 5-V LCD module, plugging in a 3.3-V LCD module into the board can damage the LCD module.

Figure 4-15. LCD Connected on P8 Connector

# 4.2.11 CapSense Sensors

The board layout considers the special requirements for CapSense. It has two CapSense buttons and a five-element CapSense slider. The CapSense buttons are connected to pins P5[6] and P5[5]. The slider elements are connected to pins P5[0:4].

The Cmod (modulation capacitor) is connected to pin P6[4] and an optional Rb (bleeder resistor) is available on P15[4].

# Figure 4-16. CapSense Sensors

# 5.1 Introduction

5.

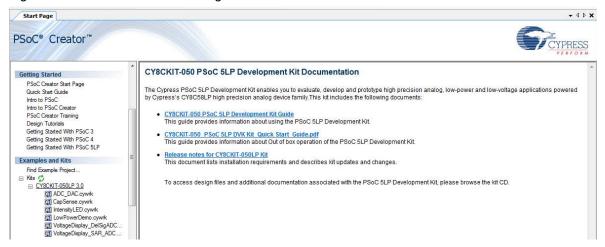

All the code examples of this kit are for CY8C5868AXI-LP035 device. To access code examples described in this section, open the PSoC Creator Start Page. For additional code examples, visit http://www.cypress.com.

Figure 5-1. PSoC Creator Start Page

Code Examples

## 5.1.1 Programming the Code Examples

Follow these steps to open and program code examples:

- 1. Click on a code example from **Kits** on the PSoC Creator Start Page.

- 2. Create a folder in the desired location and click OK.

- 3. The project opens in PSoC Creator and is saved to that folder.

- 4. Build the code example to generate the hex file.

- 5. To program, connect the board to a computer using the USB cable connected to port J1, as described in Onboard Programming Interface on page 20. The board is detected as DVKProg5

- 6. Click **Debug > Program**.

- 7. The programming window opens up. If the silicon is not yet acquired, select the DVKProg5 and click on the **Connect** button.

- 8. The silicon is acquired and is shown in a tree structure below the DVKProg5.

- 9. Click **OK** to exit the window and start programming.

# 5.2 Project: VoltageDisplay\_SAR\_ADC

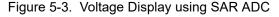

### 5.2.1 Project Description

This example code measures an analog voltage controlled by the potentiometer. The code uses the internal SAR ADC configured for a 12-bit operation; the ADC range is 0 to Vdda. The results are displayed on the character LCD module.

Note The PSoC 5LP Development Kit is factory-programmed with this example.

## 5.2.2 Hardware Connections

The example requires the character LCD on P8. Because it uses the potentiometer, the jumper POT\_PWR should be in place. This connects the potentiometer to the Vdda.

## 5.2.3 SAR ADC Configuration

To view or configure the SAR ADC component, double-click the component in the *TopDesign.cysch* file.

| Modes<br>Resolution (t<br>Conversion rate (S<br>Actual conv. rate (S<br>Clock frequency (k | PS): 100000 🔹                                          | Sample mode<br>Free running<br>Software trigger<br>Hardware trigger<br>Clock source<br>Internal<br>External |  |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| Input<br>Input range:                                                                      | Vssa to Vdda (Single Ended                             | ) 🔹                                                                                                         |  |

| Reference:                                                                                 | Internal Vref                                          | •                                                                                                           |  |

| Voltage reference:                                                                         | 1.6500 📩 Volts (Vd                                     | da/2)                                                                                                       |  |

| Enable EOS output                                                                          | La construction and and and and and and and and and an |                                                                                                             |  |

Figure 5-2. SAR ADC Configuration

The SAR ADC is configured as follows:

- Free-running mode of operation is selected because the ADC scans only one channel continuously.

- Conversion rate is set to 100 ksps. The code waits for each sample, processes it, and displays the result on the LCD.

- Range is set to Vssa to Vdda in single-ended mode because the potentiometer output is a singleended signal that can go from 0 to Vdda. Therefore, at 12-bit resolution, the ADC will resolve in steps of Vdda/2<sup>12</sup>.

Voltage reference should be set to Vdda/2 supply voltage when input range is set to 'Vssa to Vdda'. It is set to 1.65 V here, because by default, Vdda jumper setting on the board is set to 3.3 V. If J11 is changed to select 5 V, then this parameter should be changed to 2.5 V accordingly.

## 5.2.4 Verify Output

Build and program the code example, and reset the device. The LCD shows the voltage reading corresponding to the voltage on the potentiometer. Figure 5-3 demonstrates the functionality. When you turn the potentiometer, the voltage value changes. You can also verify the voltage on the potentiometer using a precision multimeter.

**Note** The potentiometer connects to a differential ADC, which works in single-ended mode. This means the ADC input is measured against internal Vssa. Any offset in the measurement can be positive or negative. This can result in a small offset voltage even when the potentiometer is zero.

# 5.3 Project: VoltageDisplay\_DelSigADC

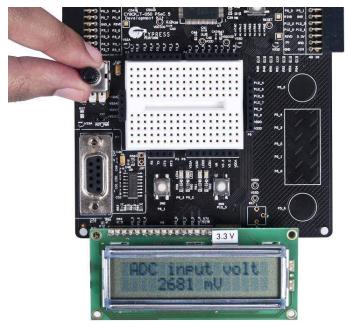

## 5.3.1 Project Description

This example code measures a simple analog voltage controlled by the potentiometer. The code uses the internal Del-Sig ADC configured for a 20-bit operation; the ADC range is 0 to Vdda. The voltage measurement resolution is in microvolts. The results are displayed on the character LCD module.

## 5.3.2 Hardware Connections

The example requires the character LCD on P8. Because it uses the potentiometer, the jumper POT\_PWR should be in place. This connects the potentiometer to the Vdda. Move jumper J10 and J11 to position 2-3, this will set Vdda to 5 V.

#### 5.3.3 **DelSig ADC Configuration**

To view or configure the Delsig ADC component, double-click the component in the TopDesign.cysch file.

> 2 38

| gure 'ADC_DelSi     | 9'             |                    |  |  |  |

|---------------------|----------------|--------------------|--|--|--|

| ame: ADC            |                |                    |  |  |  |

| Config1 Cor         | nmon Built-in  |                    |  |  |  |

| Comment:            | Default Config |                    |  |  |  |

| Configuration name: | CFG1           | ADC_CFG1           |  |  |  |

| Modes               |                |                    |  |  |  |

| Conversion mode:    | 2 - Continuous | •                  |  |  |  |

| Resolution (bits):  | 20 🔻           |                    |  |  |  |

| Conversion rate (SP | S): 187 🚔      | Range: 8 - 187 SPS |  |  |  |

| Autoritaria anto 10 | DC). 102       |                    |  |  |  |

Figure 5-4. Delta-Sigma ADC Configuration

4 0 conv. rate (SPS): 183 Clock frequency (kHz): 3063.808 Input options - Single ended mode Input range Input range: Vssa to Vdda • Vdda Buffer gain: -1 Rail to Rail Buffer mode: -ADC Range (Rail to Rail Mode) Reference Reference: Internal Vdda/4 Vref (V): 1.250 100 mV Vssa Alignmen Right Coherency = LOW C Left Bit-23 (OVF Protected) Datasheet OK Apply Cancel

To configure the Del-Sig ADC:

- Select the continuous mode of operation because the ADC scans only one channel.

- Set the conversion rate to 187 samples/sec, which is the maximum sample rate possible at 20-bit resolution.

- Set the range from Vssa to Vdda in single-ended mode because the potentiometer output is a single-ended signal that can go from 0 to Vdda. Therefore, at 20-bit resolution, the ADC will resolve in steps of Vdda/2<sup>20</sup>.

Note Internal Vdda/3 reference option is not available in the current PSoC 5LP silicon. In this project, Vdda = 5 V. The project will not work if Vdda = 3.3 V, because it needs Vdda/3 reference for Del-Sig ADC. To set Vdda to 5 V, in the VoltageDisplay DelSigADC.cydwr window of PSoC Creator, click on the System tab, go to the Operating Conditions option. Set Vdda to 5 V.

#### Figure 5-5. Operating Conditions Option

| Start Page TopDesign.cysch VoltageDispgADC.cydwr | - 4                     |

|--------------------------------------------------|-------------------------|

| D Reset   È⊞ Expand   È⊡ Collapse                |                         |

| Option                                           | Value                   |

| - Configuration                                  |                         |

| - Device Configuration Mode                      | DMA                     |

| - Enable Error Correcting Code (ECC)             |                         |

| - Store Configuration Data in ECC Memory         |                         |

| - Instruction Cache Enabled                      |                         |

| - Enable Fast IMO During Startup                 |                         |

| - Unused Bonded IO                               | Allow but warn          |

| - Heap Size (bytes)                              | 4096                    |

| - Stack Size (bytes)                             | 16384                   |

| - Include CMSIS Core Peripheral Library Files    | V.                      |

| - Programming\Debugging                          |                         |

| - Debug Select                                   | SWD (serial wire debug) |

| - Enable Device Protection                       |                         |

| - Embedded Trace (ETM)                           |                         |

| Use Optional XRES                                |                         |

| Operating Conditions                             |                         |

|                                                  | 5.0                     |

| - Vdda (V)                                       | 5.0                     |

| - Variable Vdda                                  | E                       |

| - Vddio0 (V)                                     | 5.0                     |

| - Vddio1 (V)                                     | 5.0                     |

## 5.3.4 Verify Output

Build and program the code example, and reset the device. The LCD shows the voltage reading corresponding to the voltage on the potentiometer. Figure 5-6 demonstrates the functionality. When you turn the potentiometer, the voltage value changes. You can also verify the voltage on the potentiometer using a precision multimeter.

#### Notes

- The potentiometer connects to a differential ADC, which works in single-ended mode. This means the ADC input is measured against internal Vssa. Any offset in the measurement can be positive or negative. This can result in a small offset voltage even when the potentiometer is zero. Move jumper J10 and J11 back to position 1-2 after verifying the output.

- The LCD displays negative voltages when the POT is at 0<sup>th</sup> position.

Figure 5-6. Voltage Display using Del-Sig ADC

# 5.4 Project: IntensityLED

### 5.4.1 Project Description

This example code uses a pulse-width modulator (PWM) to illuminate an LED. When the pulse width of the PWM varies, the LED brightness changes. By continuously varying the pulse width of the PWM, the example code makes an LED go from low brightness to a high brightness and back.

### 5.4.2 Hardware Connections

No hardware connections are required for this project, because all the connections are hard-wired to specific pins on the board.

### 5.4.3 Verify Output

When the example code is built and programmed into the device, reset the device by pressing the Reset button or power cycling the board.

The project output is LED3 glowing with a brightness control that changes with time (see Figure 5-7).

**Note** If the CY8CKIT-050 is programmed with any other code example involving LCD display prior to programming the *IntensityLED.hex* file, the LCD display continues to display the output of previous project as the LCD component is not handled in the **IntensityLED** project. The LCD display gets cleared by power cycling the board.

Figure 5-7. Verify Output - Code Example

## 5.5 Project: LowPowerDemo

### 5.5.1 Project Description

This code example demonstrates the low-power functionality of PSoC 5LP. The project implements an RTC based code, which goes to sleep and wakes up on the basis of switch inputs. The RTC uses an accurate 32-kHz clock generated using the external crystal provided on the board. When there is a key press, the device is put to sleep while the RTC is kept active.

### 5.5.2 Hardware Connections

The project requires a 3.3 V LCD to view the time display. No extra connections are required for project functionality. To make low-power measurements using this project, implement the changes proposed in Low-Power Functionality on page 18.

### 5.5.3 Verify Output

In normal operation, the project displays the time starting from 00:00:00 when SW2 is pressed. Normal mode is indicated by LED3 in ON state. When you press the SW2 button again, the device is put to sleep. Sleep mode is indicated by LED3 in OFF state. If an ammeter is connected to measure the system current (see Low-Power Functionality on page 18 for details), a system current of less than 2  $\mu$ A is displayed.

The device wakes up when SW2 is pressed again and displays the time on the LCD. The following figures show the output display.

Figure 5-8. PSoC 5LP in Active Mode

Figure 5-9. PSoC 5LP in Sleep Mode

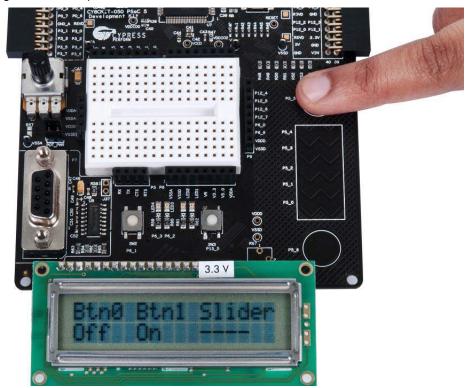

### 5.6 Project: CapSense

### 5.6.1 Project Description

This code example provides a platform to build CapSense-based projects using PSoC 5LP. The example uses two CapSense buttons and one five-element slider provided on the board. Each capacitive sensor on the board is scanned using the Cypress CSD algorithm. The buttons are pretuned in the example code to take care of factors such as board parasitic.

### 5.6.2 Hardware Connections

This project uses the LCD for display; therefore, ensure that it is plugged into the port. No specific hardware connections are required for this project because all connections are hard-wired on the board.

### 5.6.3 Verify Output

Build and program the code example, and reset the device. The LCD displays the status of the two buttons as On/Off. The LCD also shows the slider touch position as a percentage. When you touch a button, the LCD displays ON; when you remove the finger from the button, the LCD displays OFF. When the slider is touched, the corresponding finger position is displayed as a percentage on the LCD.

Figure 5-11. CapSense Button

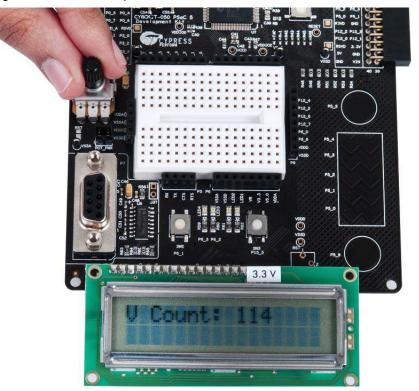

## 5.7 Project: ADC\_DAC

### 5.7.1 Project Description

This project demonstrates sine wave generation by using an 8-bit DAC and DMA. The sine wave period is based on the current value of the ADC value of the potentiometer.

The firmware reads the voltage output by the board potentiometer and displays the raw counts on the LCD. An 8-bit DAC outputs a table generated sine wave to an LED using DMA at a frequency proportional to the ADC count.

### 5.7.2 Hardware Connections

For this example, the character LCD must be installed on P8. The example uses the potentiometer; therefore, the jumper POT\_PWR should also be in place. This jumper connects the potentiometer to the Vdda.

### 5.7.3 Verify Output

Build and program the code example, and reset the device to view the ADC output displayed on the LCD. LED4 is an AC signal output whose period is based on the ADC. Turning the potentiometer results in LCD value change. This also results in change in the period of the sine wave fed into LED4. When the potentiometer changes, the blinking rate of LED4 changes.

### Figure 5-12. ADC Output

# A. Appendix

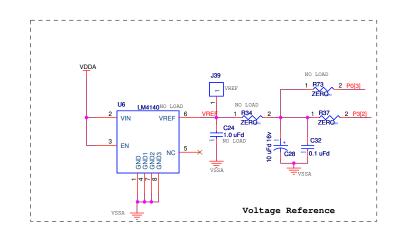

#### NO LOAD TP4 RED V5 Power Supply V5.0 5.0V/1A LDO +9V/+12V, 1A D3 SS12-E3/61T VIN U2 AP1117D50G R24 1 2 3 1 VIN VOUT ZERO J4 GND C14\*\*\* + $\wedge \Box$ 2 \*\*\*\* ر اؤر POWER JACK P-5 TP3 RED C4 10 uFd 16v 10 uFd 1 D4 V3.3 2 SS12-E3/61T GND CNI R26 ZERO 9V Battery V5.0 LM1117MPX-3.3 Terminals 3 VIN VOUT POS2 POS1 POS3 + C2 10 uFd 16v GND TAB 10 uFd 16v VDDA BH2 J33 U4 3.3V/0.8A LDO VDDA\_P RED N -BAT 9V FEMALE R23 ZERO GND VSSD VDDD VDDA J38 5V/3.3V/0.5A LDO NEG2 NEG1 NEG3 BH1 9v U1 LT1763CS8 1 2 3 10 uFd 16v 2 0.1 uFd IN OUT BAT 9V MALE C17 R12 3.16K 3.74K \*\*<u>+</u> C5 SENSE NO LOAD 10 uFd 16v 5 nSHDN 2 Вур →<sub>GND</sub> GND1 GND1 GND2 VSSA V5.0 VDDD VDDA VDDD R11 1K -V5.0 R30 R15 GND 1 2 N ZERO NO LOAD 330 ohm Note: Load R30 when either Analog and Digital regulator required VSSA 2 2 D5 000 J11 J10 R57 VSSB VSSA ZERO Note: For 5V: J11-3 to J11-2, J10-3 to J10-2 For 3.3V: J11-2 to J11-1, J10-2 to J10-1 For 5V Analog,3.3V Digital: J11-3 to J11-2, J10-2 to J10-1 NC VSSD VSSA VSSD Note: Load R25, R29 and R31 for operating the device on Boost Internal Boost Regulator VDDA VDDD g VBAT R29 VBAT R31 NO LOAD \* H29 R25 NO LOAD NO LOAD TP2 RED Q /boost D6 ZHCS L1 1 R27 ZERO 22 uH C23 C22 22 uFd 10V C6 22 u 10V C3 R28 NO LOAD R1 NO LOAD uFd TP1 BLACK 0.1 uFd 0.1 uFd GND VSSB GND GND GND Note: Load R1,R28 and Un-Load R27 for low power application

# A.1 Schematic

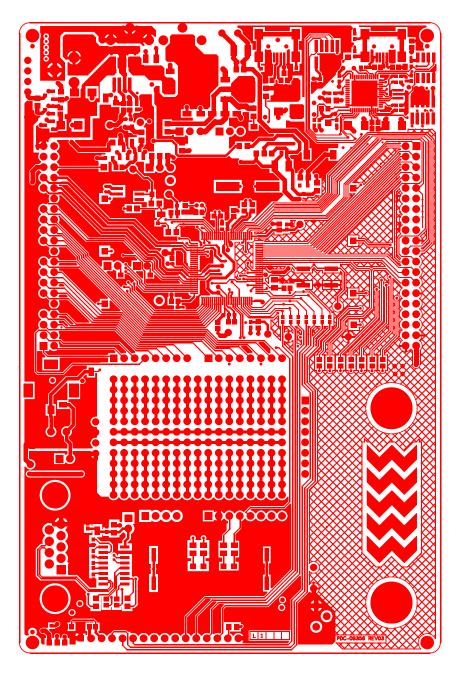

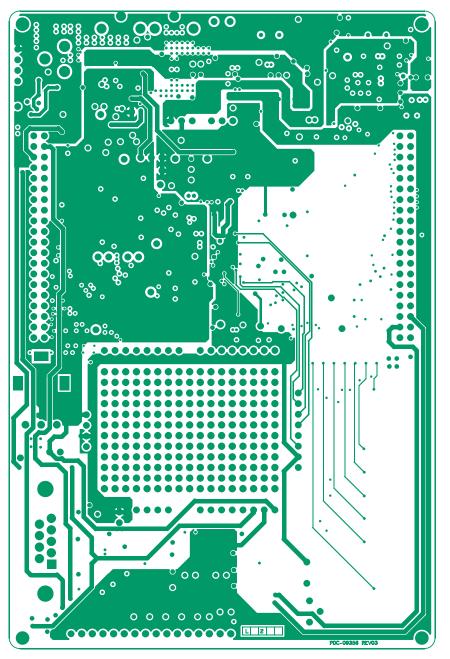

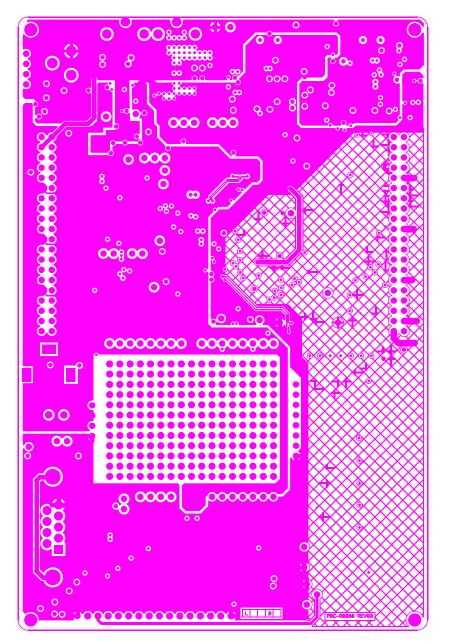

# A.2 Board Layout

# A.2.1 PDC-09356 Top

# A.2.2 PDC-09356 Power

## A.2.3 PDC-09356 Ground

## A.2.4 PDC-09356 Bottom

# A.3 Bill of Materials (BOM)

| Item | Qty Reference |                                                                                                                                                                         | Value              | Description                                 | Manufacturer                    | Manufacturer Part No.  |  |

|------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------|---------------------------------|------------------------|--|

|      |               |                                                                                                                                                                         |                    | РСВ                                         | Cypress                         | PDC-09356              |  |

| 1    | 1             | BH1 BAT 9V MALE                                                                                                                                                         |                    | BATTERY HOLDER 9V Male<br>PC MT             | Keystone Elec-<br>tronics       | 593                    |  |

| 2    | 1             | BH2                                                                                                                                                                     | BAT 9V FEMALE      | BATTERY HOLDER 9V<br>Female PC MT           | Keystone Elec-<br>tronics       | 594                    |  |

| 3    | 9             | C2, C4, C5, C13,<br>C14, C15, C28,<br>C45, C46                                                                                                                          | 10 uFd 16v         | CAP 10UF 16V TANTALUM<br>10% 3216           | AVX                             | TAJA106K016R           |  |

| 4    | 2             | C6, C22                                                                                                                                                                 | 22 uFd             | CAP CER 22UF 10V 10% X5R<br>1210            | Kemet                           | C1210C226K8PACTU       |  |

| 5    | 29            | C7, C10, C12,<br>C16, C17, C18,<br>C19, C20, C21,<br>C26, C32, C33,<br>C34, C35, C36,<br>C38, C40, C41,<br>C43, C47, C48,<br>C49, C50, C51,<br>C52, C53, C1,<br>C3, C23 | 0.1 uFd            | CAP .1UF 16V CERAMIC Y5V<br>0402            | Panasonic -<br>ECG              | ECJ-0EF1C104Z          |  |

| 6    | 2             | C8, C9                                                                                                                                                                  | 0.01 uFd           | CAP 10000PF 16V CERAMIC<br>0402 SMD         | Panasonic -<br>ECG              | ECJ-0EB1C103K          |  |

| 7    | 1             | C11                                                                                                                                                                     | 2.2 uFd            | CAP CER 2.2UF 6.3V 20%<br>X5R 0402          | Panasonic -<br>ECG              | ECJ-0EB0J225M          |  |

| 8    | 4             | C29, C37, C42,<br>C44                                                                                                                                                   | 1.0 uFd            | CAP CERAMIC 1.0UF 25V<br>X5R 0603 10%       | Taiyo Yuden                     | TMK107BJ105KA-T        |  |

| 9    | 2             | C25, C27                                                                                                                                                                | 22pF               | CAP, CER, 22 pF, 50V, 5%,<br>COG, 0603, SMD | Panasonic -<br>ECG              | ECJ-0EC1H220J          |  |

| 10   | 1             | C39                                                                                                                                                                     | 2200 pFd           | SMD/SMT 0805 2200pF<br>50volts C0G 5%       | Murata                          | GRM2165C1H222JA0<br>1D |  |

| 11   | 2             | C54, C55                                                                                                                                                                | 1.0 uFd            | CAP CERAMIC 1.0UF 25V<br>X5R 0603 10%       | Taiyo Yuden                     | TMK107BJ105KA-T        |  |

| 12   | 6             | D1, D2, D3, D4,<br>D7, D8                                                                                                                                               | SS12-E3/61T        | DIODE SCHOTTKY 20V 1A<br>SMA                | Vishay/General<br>Semiconductor | SS12-E3/61T            |  |

| 13   | 1             | D5                                                                                                                                                                      | LED Green          | LED GREEN CLEAR 0805<br>SMD                 | Chicago Minia-<br>ture          | CMD17-21VGC/TR8        |  |

| 14   | 1             | D6                                                                                                                                                                      | ZHCS               | DIODE SCHOTTKY 40V 1.0A<br>SOT23-3          | Zetex                           | ZHCS1000TA             |  |

| 15   | 6             | D9, D10, D11,<br>D12, D13, D14                                                                                                                                          | ESD diode          | SUPPRESSOR ESD 5VDC<br>0603 SMD             | Bourns Inc.                     | CG0603MLC-05LE         |  |

| 16   | 1             | D15                                                                                                                                                                     | 4.3V zener diode   | DIODE ZENER 4.3V 1W SOD-<br>106             | Rohm Semicon-<br>ductor         | PTZTE254.3B            |  |

| 17   | 1             | D16                                                                                                                                                                     | 2.0V Zener Diode   | DIODE ZENER 2V 500MW<br>SOD-123             | Diodes Inc                      | BZT52C2V0-7-F          |  |

| 18   | 2             | J1,J2                                                                                                                                                                   | USB MINI B         | CONN USB MINI B SMT<br>RIGHT ANGLE          | түсо                            | 1734035-2              |  |

| 19   | 2             | J3, J40                                                                                                                                                                 | 50MIL KEYED<br>SMD | CONN HEADER 10 PIN 50MIL<br>KEYED SMD       | Samtec                          | FTSH-105-01-L-DV-K     |  |

| Item | Qty | Reference                                                                        | Value                                               | Description                          | Manufacturer                   | Manufacturer Part No.     |

|------|-----|----------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------|--------------------------------|---------------------------|

| 20   | 1   | J4                                                                               | POWER JACK P-5                                      | CONN JACK POWER 2.1mm<br>PCB RA      | си                             | PJ-102A                   |

| 21   | 1   | J50                                                                              | Breadboard                                          | BREADBOARD 17x5x2                    | 3M                             | 923273-I                  |

| 22   | 5   | TP1, J26, J27,<br>J35, J28                                                       | BLACK TEST<br>POINT                                 | TEST POINT PC MINI .040"D<br>Black   | Keystone<br>Electronics        | 5001                      |

| 23   | 4   | LED1, LED2,<br>LED3, LED4                                                        | LED Red                                             | LED RED CLEAR 0805 SMD               | Rohm<br>Semiconductor          | SML-210LTT86              |

| 24   | 1   | L1                                                                               | 22 uH                                               | INDUCTOR SHIELD PWR<br>22UH 7032     | TDK Corporation                | SLF7032T-220MR96-<br>2-PF |

| 25   | 2   | P1,P2                                                                            | 20x2 RECP RA                                        | CONN FMALE 40POS DL .100<br>R/A GOLD | Sullins Electron-<br>ics Corp. | PPPC202LJBN-RC            |

| 26   | 1   | P7                                                                               | DB9 FEMALE                                          | CONN DB9 FMALE VERT<br>PRESSFIT SLD  | Norcomp Inc.                   | 191-009-223R001           |

| 27   | 1   | P8                                                                               | LCD HEADER W/<br>O BACKLIGHT                        | CONN RECEPT 16POS .100<br>VERT AU    | Tyco Electronics               | 1-534237-4                |

| 28   | 4   | P3, P4, P6, P9                                                                   | RECP 8X1                                            | CONN RECT 8POS .100 VERT             | ЗM                             | 929850-01-08-RA           |

| 29   | 6   | Q1, Q2, Q3, Q4,<br>Q5, Q6                                                        | P-MOS, 30V 3.8A<br>SOT23 in Protec-<br>tion circuit | MOSFET P-CH 30V 3.8A<br>SOT23-3      | Diodes Inc                     | DMP3098L-7                |

| 30   | 1   | R7                                                                               | RES 220 OHM 1/<br>10W 1% 0603<br>SMD                | Panasonic - ECG                      | ERJ-<br>3EKF2200V              | YES                       |

| 31   | 1   | R16                                                                              | RES 442 OHM 1/<br>10W 1% 0603<br>SMD                | Panasonic - ECG                      | ERJ-<br>3EKF4420V              | YES                       |

| 32   | 2   | R3, R4                                                                           | 100K                                                | RES 100K OHM 1/16W 5%<br>0402 SMD    | Panasonic -<br>ECG             | ERJ-2GEJ104X              |

| 33   | 6   | R9, R23, R24,<br>R26, R27, R71                                                   | ZERO                                                | RES 0.0 OHM 1/10W 5% 0805<br>SMD     | Panasonic-ECG                  | ERJ-6GEY0R00V             |

| 34   | 2   | R5, R6                                                                           | 2.2K                                                | RES 2.2K OHM 1/16W 5%<br>0402 SMD    | Panasonic -<br>ECG             | ERJ-2GEJ222X              |

| 35   | 3   | R11, R10, R18                                                                    | 1K                                                  | RES 1.0K OHM 1/8W 5% 0805<br>SMD     | Panasonic -<br>ECG             | ERJ-6GEYJ102V             |

| 36   | 1   | R12                                                                              | 3.16K                                               | RES 3.16K OHM 1/10W .5%<br>0603 SMD  | Yageo                          | RT0603DRD073K16L          |

| 37   | 1   | R13                                                                              | 3.74K                                               | RES 3.74K OHM 1/10W 1%<br>0603 SMD   | Panasonic -<br>ECG             | ERJ-3EKF3741V             |

| 38   | 1   | R14                                                                              | 100K                                                | RES 100K OHM 1/10W 1%<br>0603 SMD    | Yageo                          | RC0603FR-07100KL          |

| 39   | 5   | R15, R59, R60,<br>R61, R62                                                       | 330 ohm                                             | RES 330 OHM 1/10W 5% 0805<br>SMD     | Panasonic -<br>ECG             | ERJ-6GEYJ331V             |

| 40   | 8   | R17, R40, R41,<br>R42, R43, R44,<br>R45, R46                                     | 10K                                                 | RES 10K OHM 1/16W 5%<br>0402 SMD     | Stackpole Elec-<br>tronics Inc | RMCF 1/16S 10K 5%<br>R    |

| 41   | 13  | R35, R36, R39,<br>R47, R48, R49,<br>R50, R51, R52, ZERO<br>R53, R54, R64,<br>R66 |                                                     | RES ZERO OHM 1/16W 5%<br>0603 SMD    | Panasonic -<br>ECG             | ERJ-3GEY0R00V             |

| Item | Qty | Reference     | Value                                                 | Description                                              | Manufacturer                   | Manufacturer Part No.    |