# 110VPK-PK High-Efficiency Piezo Haptic Actuator Boost Driver

### **General Description**

The MAX77501 is a high-efficiency controller driver for piezo haptic actuators and is optimized for driving up to 2µF piezo elements. It can generate a single-ended haptic waveform of up to 110V<sub>PK-PK</sub> amplitude from a 2.8V to 5.5V input power supply or a single cell Li+ battery. Memory playback and haptic waveforms real-time streaming modes are supported.

A 25MHz SPI interface provides full system access and control, including fault reporting and monitoring. This allows for a rapid 600µs playback start-up time from shutdown. The on-board memory can be dynamically allocated as multiple waveforms storage or as a FIFO buffer. The IC also implements an ultra-low power boost architecture providing the lowest power consumption solution for a haptic actuator driver.

Built-in undervoltage lockout (UVLO), cycle-by-cycle overcurrent limit, overvoltage and thermal shutdown protections ensure safe operation under abnormal operating conditions.

The MAX77501 is available in a 30-bump, 0.4mm pitch, wafer-level package (WLP).

#### Benefits and Features

- 110V<sub>PK-PK</sub> Haptic Waveforms Generation

- Optimized for up to 2µF Haptic Piezo Actuator

- 2.8V to 5.5V Input Supply Range

- 600µs Start-Up Time to Haptic Playback

- High-Efficiency, Low In Extends Battery Life

- 75µA Standby Current/1µA Shutdown Current

- Maxim Patented Ultra-Low Power Boost Architecture

- 12-Bit Haptic Waveform Playback DAC

- Real-Time Streaming and RAM Playback Modes

- 9k FIFO Buffer with FIFO Ready Status Signal

- 8k RAM Buffer for Waveforms Storage

- 25MHz SPI Interface SPI Ready, Warning and Fault Conditions Interrupt

- Protection Features

- · Programmable Cycle-by-Cycle Overcurrent Limit, 130V Overvoltage, UVLO, and Thermal Protections

- Small Size and Low Profile

- 2.42mm x 2.02mm, 30 Bump WLP

Ordering Information appears at end of data sheet.

### **Applications**

- Smartphones, Tablets/E-readers, Game Consoles

- Keyboard, Mice, Remote Controls, and Peripherals

- Haptic/Tactile Feedback Enabled Equipment

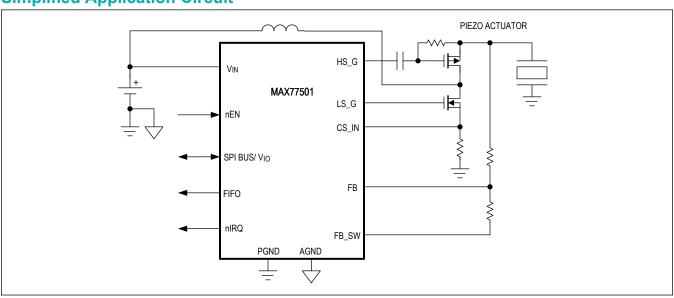

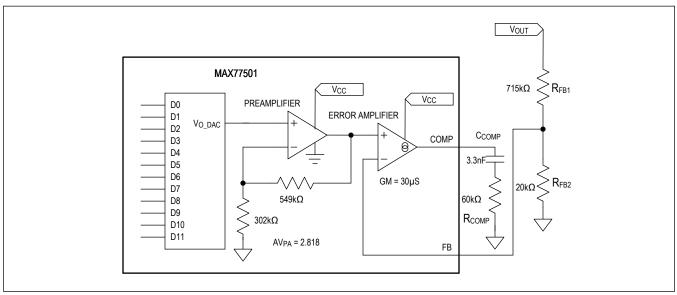

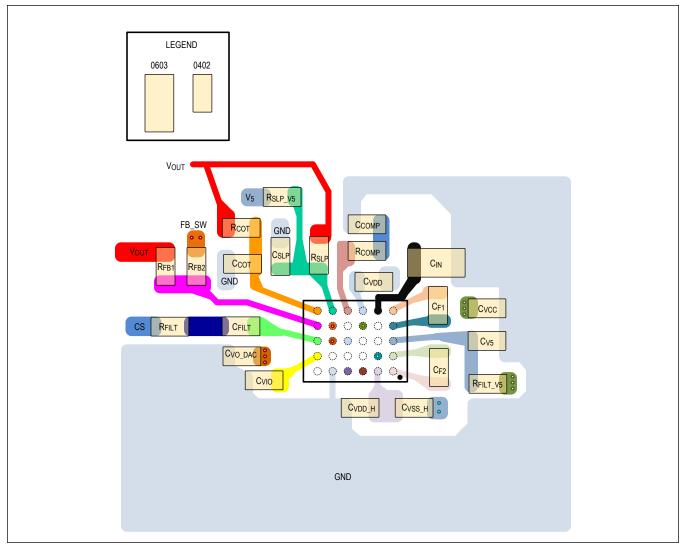

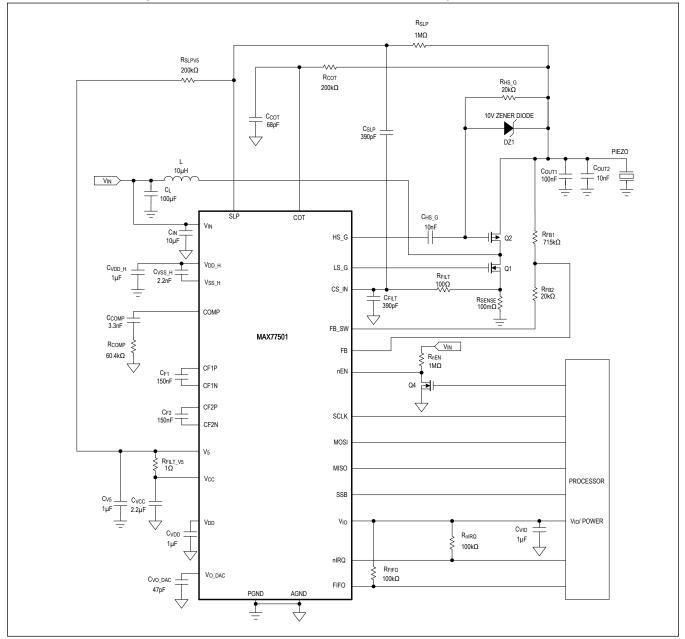

# Simplified Application Circuit

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

### TABLE OF CONTENTS

| General Description                                     | 1  |

|---------------------------------------------------------|----|

| Applications                                            | 1  |

| Benefits and Features                                   | 1  |

| Simplified Application Circuit                          | 1  |

| Absolute Maximum Ratings                                | 7  |

| Package Information                                     | 7  |

| WLP                                                     | 7  |

| Electrical Characteristics—Top Level                    | 7  |

| Electrical Characteristics—Boost Controller             | 10 |

| Electrical Characteristics—SPI Communication Controller | 12 |

| Typical Operating Characteristics                       | 14 |

| Bump Configurations                                     | 16 |

| 30 WLP                                                  | 16 |

| Bump Descriptions                                       | 16 |

| Functional Diagrams                                     | 19 |

| Simplified Block Diagram                                | 19 |

| Detailed Description—Top Level                          | 20 |

| State Diagram                                           | 20 |

| Turn-On Sequence                                        | 23 |

| Digital Configuration                                   | 23 |

| Digital Engine Overview                                 | 24 |

| Modes of Playback                                       | 24 |

| Waveform Input—FIFO                                     | 24 |

| FIFO Size                                               | 25 |

| FIFO Full, Empty, and Almost Empty                      | 26 |

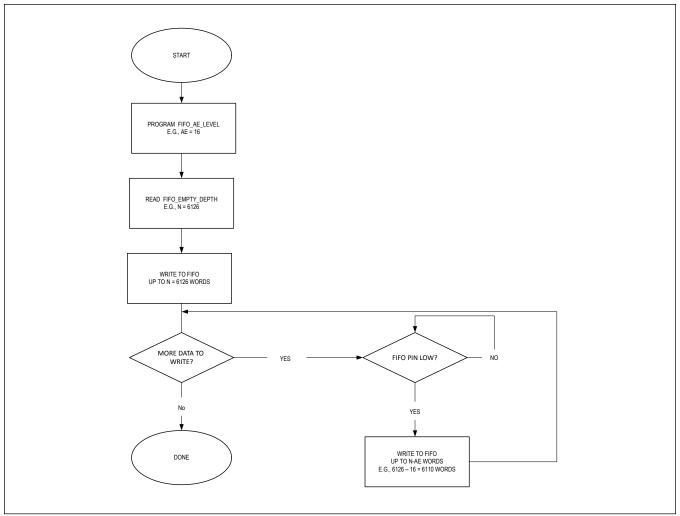

| Using the FIFO Mode                                     | 26 |

| Waveform Input—RAM                                      | 27 |

| Address Space for RAM and Registers                     | 28 |

| RAM Content Organization                                | 28 |

| Waveform Ending Address Registers                       | 29 |

| Number of Waveforms Stored in the RAM                   | 29 |

| Playlist Registers                                      | 29 |

| Repeat Count Register                                   | 29 |

| Example Configuration                                   | 30 |

| Using the RAM Playback Mode                             | 31 |

| Reading the RAM                                         | 31 |

| Overlapping Playback Requests                           | 31 |

| DAC Code to Output Voltage Conversion                   | 31 |

110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

# TABLE OF CONTENTS (CONTINUED)

| DAC Output Sampling Rate                           | 32 |

|----------------------------------------------------|----|

| Interrupts and Fault Protection                    | 32 |

| nEN Interrupt and Fault Condition                  | 32 |

| Undervoltage Lockout (UVLO) Fault Protection       | 33 |

| Charge Pump Time Out Fault Protection              | 33 |

| Charge Pump Not Okay Fault Protection              | 33 |

| ILIM Warning Interrupt and Fault Protection        | 33 |

| Invalid RAM Address Interrupt and Fault Protection | 33 |

| Empty RAM Interrupt and Fault Condition            | 33 |

| RAM Address Overflow Interrupt and Fault Condition | 34 |

| FIFO Overflow Interrupt and Fault Condition        | 34 |

| Thermal Interrupt and Fault Protection             | 34 |

| Bias NOT OK Fault Protection                       | 34 |

| SPI Ready Interrupt                                | 34 |

| Detailed Description—Boost Controller              | 34 |

| Description of Modulator Operation                 | 34 |

| Switching Frequency and COT Timer Operation        | 34 |

| Slope Compensation                                 | 35 |

| Small Signal Frequency Compensation                | 35 |

| Current Limit Protection                           | 35 |

| Overvoltage Protection                             | 35 |

| Detailed Description—SPI Communication Controller  | 35 |

| Features                                           | 36 |

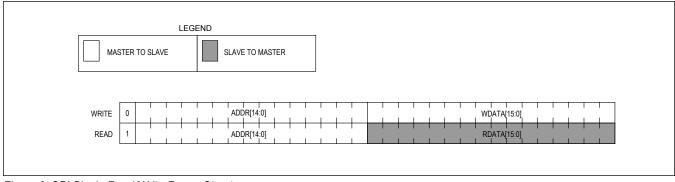

| Frame Structure                                    | 36 |

| Read/Write Bits                                    | 36 |

| Address Bits (ADDR[14:0])                          | 37 |

| Data Bits (RDATA[15:0]/WDATA[15:0])                | 37 |

| SPI Write Frame Diagram                            | 37 |

| SPI Read Frame Diagram                             | 37 |

| SPI Burst Write Diagram                            | 37 |

| SPI Burst Read Diagram                             | 38 |

| Register Map                                       | 39 |

| MAX77501                                           | 39 |

| Register Details                                   | 42 |

| Applications Information                           | 63 |

| nEN Enable Input                                   | 63 |

| Charge Pumps                                       | 63 |

| Piezo Suppliers                                    | 63 |

|                                                    |    |

110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

# TABLE OF CONTENTS (CONTINUED)

| Applications Information—Boost Controller                           | . 64 |

|---------------------------------------------------------------------|------|

| External Component Selection Guide                                  | . 64 |

| FET Selection Guide                                                 | . 65 |

| High-Side PFET Drive                                                | . 66 |

| Slew Rate Control                                                   | . 67 |

| Input Battery Voltage Blocking FET                                  | . 67 |

| Feedback Switch Functionality                                       |      |

| Full-Scale Settings                                                 | . 69 |

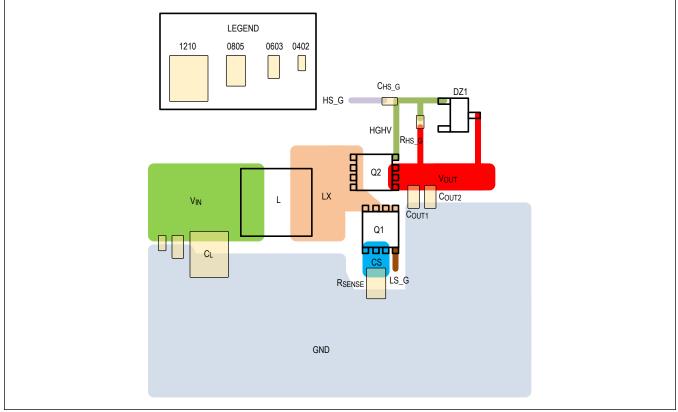

| PCB Layout Guidelines                                               | . 69 |

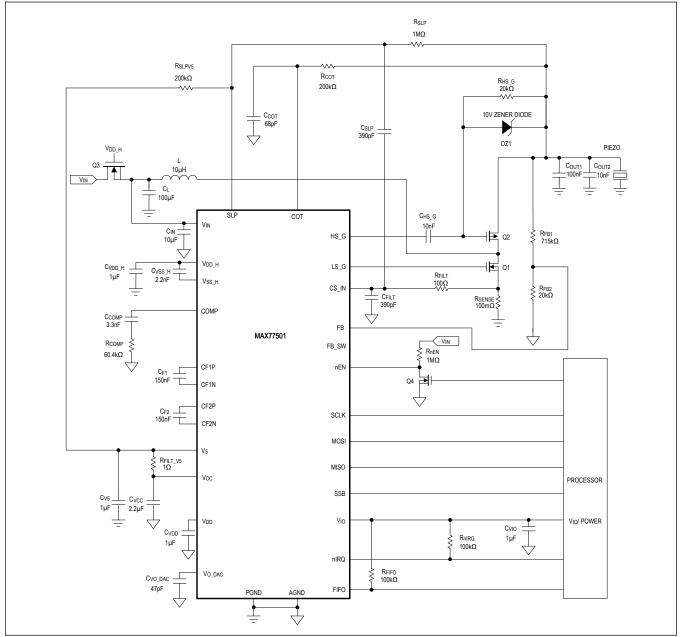

| Typical Application Circuits                                        | . 72 |

| Current Mode Configuration with Feedback Switch Functionality       | . 72 |

| Current Mode Configuration with Input Battery Voltage Blocking FET. | . 73 |

| Ordering Information                                                | . 74 |

| Revision History                                                    | . 75 |

|                                                                     |      |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

## LIST OF FIGURES

| Figure 1. State Diagram                                | 21 |

|--------------------------------------------------------|----|

| Figure 2. Digital Engine Block Diagram.                | 24 |

| Figure 3. FIFO Write Flow Chart                        | 27 |

| Figure 4. Error Amplifier Block Diagram                | 35 |

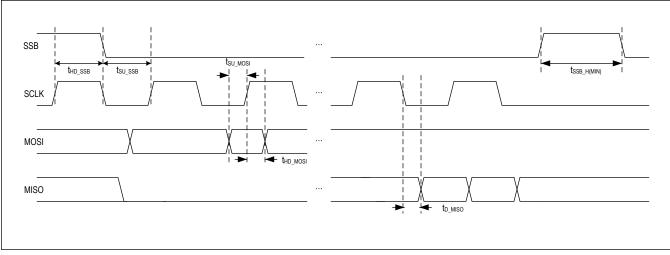

| Figure 5. SPI Interface Timing Diagram                 | 36 |

| Figure 6. SPI Single Read/Write Frame Structure        | 36 |

| Figure 7. SPI Write Frame                              | 37 |

| Figure 8. SPI Read Frame                               | 37 |

| Figure 9. SPI Burst Write Diagram                      | 38 |

| Figure 10. SPI Burst Read Diagram                      | 38 |

| Figure 11. High-Side PFET Gate Drive                   | 67 |

| Figure 12. Input Battery Voltage Blocking FET Diagram. | 68 |

| Figure 13. Feedback Switch Diagram                     | 69 |

| Figure 14. Inductor Power Path Layout Example          | 70 |

| Figure 15. IC Controller Layout                        | 71 |

|                                                        |    |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

### LIST OF TABLES

| Table 1. State Diagram Description                                             | 22 |

|--------------------------------------------------------------------------------|----|

| Table 2. Waveform Modes of Playback.                                           | 24 |

| Table 3. FIFO Total Size Example                                               | 25 |

| Table 4. Number of FIFO Samples Left for a Given FIFO_AE_LEVEL and Sample Rate | 26 |

| Table 5. RAM/Register Address Space.                                           | 28 |

| Table 6. RAM Content Organization Example                                      | 28 |

| Table 7. Example Playlist                                                      | 29 |

| Table 8. Repeat Count Example                                                  |    |

| Table 9. RAM Storage Example                                                   | 30 |

| Table 10. RAM Waveform Storage Example                                         | 30 |

| Table 11. RAM Playlist Example                                                 |    |

| Table 12. Piezo Suppliers                                                      | 63 |

| Table 13. Recommended Inductors and FETs                                       | 64 |

| Table 14. Recommended External Components                                      | 64 |

| Table 15. Recommended Active Components                                        | 65 |

| Table 16. Feedback Resistor Selection Table.                                   | 65 |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

## **Absolute Maximum Ratings**

| V <sub>IN</sub> to AGND0.3V to +6V                       | nEN  |

|----------------------------------------------------------|------|

| V <sub>5</sub> to PGND0.3V to +6V                        | FIF  |

| CF1P to PGND0.3V to +6V                                  | VSS  |

| CF1N to V <sub>IN</sub> 0.3V to +6V                      | HS_  |

| CF2P to PGND $V_5 - 0.1V$ to $V_{DD H} + 0.1V$           | SCL  |

| CF2N to PGND                                             | VSS  |

| V <sub>DD H</sub> to PGND0.3V to +16V                    | Con  |

| V <sub>IO</sub> to AGND0.3V to +2.2V                     | dera |

| V <sub>DD</sub> to AGND0.3V to +2.2V                     | Stor |

| V <sub>CC</sub> to AGND0.3V to +6V                       | Jun  |

| PGND to AGND0.3V to +0.3V                                | Solo |

| FB, COMP, COT, SLP to AGND0.3V to V <sub>CC</sub> + 0.3V | Оре  |

| CS_IN, $V_{O_DAC}$ to AGND0.3V to $V_{DD}$ + 0.3V        |      |

| nEN, FB_SW to AGND                     | 0.3V to V <sub>IN</sub> + 0.3V              |

|----------------------------------------|---------------------------------------------|

| FIFO, nIRQ to AGND                     | 0.3V to +6V                                 |

| V <sub>SS H</sub> to V <sub>DD H</sub> | 2.2V to +0.3V                               |

| HS_G, LS_G to PGND                     | 0.3V to V <sub>DD</sub> <sub>H</sub> + 0.3V |

| SCLK, SSB, MISO, MOSI to AGND          |                                             |

| V <sub>SS H</sub> to PGND              | 0.3V to V <sub>DD</sub> <sub>H</sub> + 0.3V |

| Continuous Power Dissipation (Multil   | ayer Board) (T <sub>A</sub> = +70°C,        |

| derate 40°C/W above +70°C)             |                                             |

| Storage Temperature Range              | 40°C to +150°C                              |

| Junction Temperature                   | +150°C                                      |

| Soldering Temperature (reflow)         | +260°C                                      |

| Operation Junction Temperature         | 40°C to +125°C                              |

|                                        |                                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### WLP

| Package Code                          | W302M2+1                       |

|---------------------------------------|--------------------------------|

| Outline Number                        | <u>21-100276</u>               |

| Land Pattern Number                   | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board: |                                |

| Junction to Ambient ( $\theta_{JA}$ ) | 49.38°C/W                      |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

## **Electrical Characteristics—Top Level**

$(V_{IN} = 3.6V, T_A = +25^{\circ}C)$ , limits are 100% tested at  $T_A = +25^{\circ}C$ , unless otherwise noted. Min and Max limits are guaranteed by design and characterization from  $T_A = T_J = -40^{\circ}C$  to +125°C.) (Note 1)

| PARAMETER                               | SYMBOL                        | COND                                             | ITIONS                  | MIN | TYP | MAX | UNITS |  |

|-----------------------------------------|-------------------------------|--------------------------------------------------|-------------------------|-----|-----|-----|-------|--|

| GENERAL OPERATING CONDITIONS            |                               |                                                  |                         |     |     |     |       |  |

| Input Supply Range                      | V <sub>IN</sub>               |                                                  |                         | 2.8 | 3.6 | 5.5 | V     |  |

|                                         |                               |                                                  | T <sub>A</sub> = +25°C  | -1  | 0.1 | +1  | μA    |  |

| Shutdown Supply<br>Current              | I <sub>SHDN</sub>             | V <sub>IN</sub> = 5.5V, nEN =<br>V <sub>IN</sub> | T <sub>A</sub> = +85°C  |     | 150 |     | - 1   |  |

| Guirent                                 |                               |                                                  | T <sub>A</sub> = +125°C |     | 750 |     | - nA  |  |

| Standby Current                         | lQ                            | nEN = 0V, STANDBY STATE                          |                         |     | 75  | 150 | μA    |  |

| Shutdown to Standby<br>State Time Delay | SHDN_STDB<br>Y <sub>DLY</sub> |                                                  |                         |     | 250 |     | μs    |  |

| Standby to Play Ready<br>Time Delay     | STDBY_PLAY<br>DLY             |                                                  |                         |     | 350 |     | μs    |  |

|                                         |                               | High Range: FULL_                                | SCALE = 1               |     | 120 |     | v     |  |

| Maximum V <sub>OUT</sub>                | V <sub>OUT_MAX</sub>          | Low Range: FULL_SCALE = 0 70                     |                         | 70  |     |     |       |  |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

## **Electrical Characteristics—Top Level (continued)**

$(V_{IN} = 3.6V, T_A = +25^{\circ}C)$ , limits are 100% tested at  $T_A = +25^{\circ}C$ , unless otherwise noted. Min and Max limits are guaranteed by design and characterization from  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ .) (Note 1)

| PARAMETER                                  | SYMBOL                | COND                                                                       | ITIONS                                                                  | MIN          | TYP | MAX   | UNITS    |  |

|--------------------------------------------|-----------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------|-----|-------|----------|--|

| Minimum V <sub>OUT</sub>                   | V <sub>OUT_MIN</sub>  |                                                                            |                                                                         |              | 10  |       | V        |  |

|                                            |                       | C <sub>PIEZO</sub> = 330nF, fre<br>V <sub>OUT</sub> = 60Vpp                | equency = 130Hz,                                                        |              | 60  |       |          |  |

| Operating Current                          | I <sub>IN</sub>       | $C_{PIEZO}$ = 680nF, frequency = 130Hz,<br>V <sub>OUT</sub> = 60Vpp        |                                                                         |              | 80  |       | mA       |  |

|                                            |                       | C <sub>PIEZO</sub> =1µF, freque<br>= 60Vpp                                 | C <sub>PIEZO</sub> =1µF, frequency = 130Hz, V <sub>OUT</sub><br>= 60Vpp |              | 90  |       |          |  |

|                                            |                       |                                                                            | I <sub>LIM_SEL</sub> <1:0> =<br>(0, 0)                                  |              | 1   |       |          |  |

| Inductor Peak Current                      | hur                   | nEN = 0V                                                                   | I <sub>LIM_SEL</sub> <1:0> =<br>(0, 1)                                  |              | 2   |       | -<br>- A |  |

| Limit                                      | ILIM                  | R <sub>SENSE</sub> = 100mΩ                                                 | I <sub>LIM_SEL</sub> <1:0> =<br>(1, 0)                                  |              | 3   |       |          |  |

|                                            |                       |                                                                            | I <sub>LIM_SEL</sub> <1:0> =<br>(1, 1)                                  |              | 4   |       |          |  |

|                                            |                       | SMP_RATE <1:0> =                                                           | : (0,0)                                                                 | 7.6          | 8   | 8.4   |          |  |

| Haptic Sample Rate                         | FSR <sub>SEL</sub>    | SMP_RATE <1:0> =                                                           | SMP_RATE <1:0> = (0,1)                                                  |              | 32  | 33.6  | kHz      |  |

|                                            |                       | SMP_RATE <1:0> =                                                           | : (1,0)                                                                 | 45.6         | 48  | 50.4  | ]        |  |

| Undervoltage Lockout                       | 10/10                 | Rising V <sub>IN</sub> 2.646 2.7 2                                         |                                                                         | 2.754        | - v |       |          |  |

| Undervoltage Lockout                       | UVLO                  | Falling V <sub>IN</sub>                                                    |                                                                         | 2.548 2.6 2. |     | 2.652 | v        |  |

| Undervoltage-Lockout<br>Hysteresis         | UVLO <sub>HYST</sub>  | UVLO hysteresis                                                            |                                                                         |              | 100 |       | mV       |  |

| Thermal Shutdown                           | THERMSHDN             | nEN = 0V                                                                   |                                                                         |              | 165 |       | °C       |  |

| Thermal-Shutdown<br>Hysteresis             | THERM <sub>HYST</sub> | nEN = 0V                                                                   |                                                                         |              | 21  |       | °C       |  |

| Total Harmonic<br>Distortion + Noise       | THD+N                 | C <sub>PIEZO</sub> = 680nF, frequency = 130Hz,<br>V <sub>OUT</sub> = 80Vpp |                                                                         |              | 1   |       | %        |  |

| V <sub>DD</sub> Output Voltage             | V <sub>DD</sub>       | V <sub>IN</sub> = 3.8V, nEN = 0V, no load                                  |                                                                         |              | 1.8 |       | V        |  |

| V <sub>DD</sub> Output Voltage<br>Accuracy | V <sub>DDACC</sub>    |                                                                            |                                                                         | -5           |     | +5    | %        |  |

| V <sub>CC</sub> Supply Range               | V <sub>CC</sub>       | Haptic playback mod                                                        | de                                                                      | 4.75         | 5   | 5.25  | V        |  |

| V <sub>CC</sub> Load Current<br>(Internal) | ILDVCC                | V <sub>CC</sub> = 5V, haptic pla                                           | yback mode                                                              |              | 105 |       | μA       |  |

| / <sub>OUT</sub> Overvoltage               |                       | FULL_SCALE = 1                                                             |                                                                         |              | 130 |       | .,       |  |

| Regulation                                 | VOUTOVP               | FULL_SCALE = 0                                                             |                                                                         |              | 80  |       | - V      |  |

| DAC                                        |                       |                                                                            |                                                                         |              |     |       |          |  |

| DAC Resolution                             | DAC <sub>RES</sub>    |                                                                            |                                                                         |              | 12  |       | bit      |  |

| DAC Linearity                              | DAC <sub>DNL</sub>    | No compression                                                             |                                                                         | -2           |     | +2    | LSB      |  |

| DAC FS Gain Accuracy                       | DAC <sub>FS_ACC</sub> | No compression                                                             |                                                                         | -2           |     | +2    | %        |  |

| DAC Output Resistance                      | DAC <sub>RO</sub>     |                                                                            |                                                                         |              | 1.2 |       | MΩ       |  |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

## **Electrical Characteristics—Top Level (continued)**

$(V_{IN} = 3.6V, T_A = +25^{\circ}C)$ , limits are 100% tested at  $T_A = +25^{\circ}C$ , unless otherwise noted. Min and Max limits are guaranteed by design and characterization from  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ .) (Note 1)

| PARAMETER                                                       | SYMBOL                           | COND                                                 | ITIONS                                        | MIN                         | TYP                         | MAX                         | UNITS |

|-----------------------------------------------------------------|----------------------------------|------------------------------------------------------|-----------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-------|

| Full-Scale DAC Output<br>Voltage                                | DAC <sub>FS</sub>                |                                                      |                                               | 1.2275                      | 1.25                        | 1.2725                      | V     |

| CHARGE-PUMPS                                                    |                                  |                                                      |                                               |                             |                             |                             |       |

| 5V Charge-Pump<br>Overall Accuracy                              | CP <sub>V5_ACC</sub>             | 2.8V < V <sub>IN</sub> < 5.5V ar                     | nd I <sub>LOAD</sub> < 7mA                    |                             | ±10                         |                             | %     |

| 9V Charge-Pump<br>Overall Accuracy                              | CP1 <sub>VDDH_AC</sub><br>C      | 2.8V < V <sub>IN</sub> < 5.5V ar                     | nd I <sub>LOAD</sub> < 7mA                    |                             | ±10                         |                             | %     |

| V <sub>DD_H</sub> Charge-Pump<br>Switching Frequency            | CP <sub>VDDH_FSW</sub>           |                                                      |                                               | 0.95                        | 1                           | 1.05                        | MHz   |

| 5V Charge-Pump Start-<br>Up Time                                | CP <sub>V5_TSU</sub>             | C <sub>F1</sub> = 150nF, C <sub>V5</sub><br>= 1µF    | 0 to 95% of final V <sub>5</sub> output       |                             | 200                         |                             | μs    |

| V <sub>DD_H</sub> Charge-Pump<br>Start-Up Time                  | CP <sub>VDDH_</sub> TSU          | C <sub>F2</sub> = 150nF,<br>C <sub>VDD_H</sub> = 1µF | 0 to 95% of final<br>V <sub>DD_H</sub> output |                             | 300                         |                             | μs    |

| V <sub>SS_H</sub> Accuracy                                      | V <sub>SSHACC</sub>              | V <sub>IN</sub> = 3.6V, C <sub>VSS_</sub> H          | l = 2.2nF                                     | V <sub>DD_H</sub> -<br>1.9V | V <sub>DD_H</sub> -<br>1.8V | V <sub>DD_H</sub> -<br>1.7V | V     |

| 5V Charge-Pump Active<br>Discharge Resistance                   | CP <sub>V5_RPD</sub>             | STANDBY state                                        |                                               |                             | 200                         |                             | Ω     |

| V <sub>DD_H</sub> Charge-Pump<br>Active Discharge<br>Resistance | CP <sub>VDDH_RPD</sub>           |                                                      |                                               | 200                         |                             | Ω                           |       |

| 5V Charge-Pump VOK                                              | CP <sub>V5_VOK_TH</sub>          | 5V VOK comparator                                    | 5V VOK comparator rising threshold            |                             | 4.5                         | 4.65                        | V     |

| Threshold                                                       | CP <sub>V5_VOK_TH</sub> _F       | 5V VOK comparator                                    | falling threshold                             | 3.85                        | 4                           | 4.17                        | V     |

| V <sub>DD H</sub> Charge-Pump                                   | CP <sub>VDDH_</sub> VOK<br>_TH_R | 10V VOK comparate                                    | r rising threshold                            | 6.7                         | 7                           | 7.2                         | V     |

| VOKThreshold                                                    | CP <sub>VDDH_VOK</sub>           | 10V VOK comparato                                    | r falling threshold                           | 5.63                        | 5.9                         | 6.09                        | V     |

| V <sub>DD H</sub> Charge-Pump                                   | CP <sub>VDDH_EN_</sub>           | 10V Enable compara                                   | ator rising threshold                         | 3.35                        | 3.5                         | 3.65                        | V     |

| Enable Threshold                                                | тн –                             | 10V Enable compara                                   | ator falling threshold                        | 2.95                        | 3.1                         | 3.25                        | v     |

| V <sub>DD_H</sub> Charge-Pump<br>Enable Hysteresis              | CP <sub>VDDH_EN_</sub><br>HYS    | 10V Enable compara                                   | 10V Enable comparator hysteresis              |                             | 0.4                         |                             | V     |

| FIFO STATUS PIN                                                 |                                  |                                                      |                                               |                             |                             |                             |       |

| FIFO Status VOL                                                 | VOL <sub>FIFO</sub>              | I <sub>SINK</sub> = 2mA                              |                                               |                             |                             | 0.4                         | V     |

| FIFO Status Falling<br>Edge Time                                | tFALL_FIFO                       | C <sub>LOAD</sub> = 25pF                             |                                               |                             | 2                           |                             | ns    |

|                                                                 |                                  |                                                      | T <sub>A</sub> = +25°C                        | -1                          |                             | +1                          |       |

| FIFO Leakage Current                                            | FIFO <sub>LKG</sub>              | V <sub>IN</sub> = V <sub>FIFO</sub> = 5.5V           | T <sub>A</sub> = +85°C                        |                             | ±0.01                       |                             | μA    |

|                                                                 |                                  |                                                      | T <sub>A</sub> = +125°C                       |                             | ±0.01                       |                             |       |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

## **Electrical Characteristics—Top Level (continued)**

$(V_{IN} = 3.6V, T_A = +25^{\circ}C)$ , limits are 100% tested at  $T_A = +25^{\circ}C$ , unless otherwise noted. Min and Max limits are guaranteed by design and characterization from  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ .) (Note 1)

| PARAMETER                      | SYMBOL                  | COND                                      | ITIONS                    | MIN                 | TYP   | MAX | UNITS |

|--------------------------------|-------------------------|-------------------------------------------|---------------------------|---------------------|-------|-----|-------|

| ENABLE INPUT (nEN)             |                         |                                           |                           |                     |       |     |       |

|                                |                         |                                           | T <sub>A</sub> = +25°C    | -1                  |       | +1  |       |

| nEN Input Leakage<br>Current   | I <sub>nEN_LKG</sub>    | V <sub>IN</sub> = V <sub>nEN</sub> = 5.5V | T <sub>A</sub> = +85°C    |                     | ±0.01 |     | μΑ    |

| Guirent                        | _                       |                                           | T <sub>A</sub> = +125°C   |                     | ±0.01 |     | 1     |

| nEN Input Falling<br>Threshold | V <sub>TH_nEN_F</sub>   | nEN falling                               |                           |                     |       | 1   | V     |

| nEN Input Rising<br>Threshold  | V <sub>TH_nEN_R</sub>   | nEN rising                                |                           | V <sub>IN</sub> - 1 |       |     | V     |

| OPEN-DRAIN INTERRUP            | PT OUTPUT (nIR          | Q)                                        |                           |                     |       |     |       |

| nIRQ VOL                       | VOL <sub>nIRQ</sub>     | I <sub>SINK</sub> = 2mA                   |                           |                     |       | 0.4 | V     |

| nIRQ Falling Edge Time         | t <sub>FALL_nIRQ</sub>  | C <sub>nIRQ</sub> = 25pF                  |                           |                     | 2     |     | ns    |

|                                |                         |                                           | T <sub>A</sub> = +25°C    | -1                  |       | +1  |       |

| nIRQ Leakage Current           | l <sub>nlRQ_LKG</sub>   | $V_{IN} = V_{nIRQ} = 5.5V$                | T <sub>A</sub> = +85°C    |                     | ±0.01 |     | μA    |

|                                |                         |                                           | T <sub>A</sub> = +125°C   |                     | ±0.01 |     | ]     |

|                                |                         |                                           | ILIM_FLAG<1,0> =<br>(0,0) |                     | 128   |     |       |

|                                |                         |                                           | ILIM_FLAG<1,0> =<br>(0,1) |                     | 256   |     |       |

| ILIM Flag Count                | ILIM <sub>FLG_CNT</sub> | (*<br>                                    | ILIM_FLAG<1,0> =<br>(1,0) |                     | 1024  |     | ]     |

|                                |                         |                                           | ILIM_FLAG<1,0><br>= (1,1) |                     | 2048  |     | ]     |

### **Electrical Characteristics—Boost Controller**

$(V_{IN} = 3.6V, T_A = +25^{\circ}C)$ , limits are 100% tested at  $T_A = +25^{\circ}C$ , unless otherwise noted. Min and Max limits are guaranteed by design and characterization from  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ .) (Note 1)

| PARAMETER                       | SYMBOL               | CONDITIONS | MIN  | ТҮР   | MAX                      | UNITS |

|---------------------------------|----------------------|------------|------|-------|--------------------------|-------|

| GMAMP                           |                      |            |      |       |                          |       |

| GMAMP<br>Transconductance       | GMAMP <sub>GM</sub>  |            | 25   | 30    | 33                       | μS    |

| Input Common Mode<br>Range      | GMAMP <sub>CMR</sub> |            | 0.23 |       | 3.4                      | V     |

| GMAMP Output Swing              | GM <sub>VO</sub>     | No load    | 0.1  |       | V <sub>CC</sub> -<br>0.1 | V     |

| GMAMP Maximum<br>Output Current | GMAMP <sub>IO</sub>  |            | 7    |       |                          | μA    |

| PREAMPLIFIER                    |                      |            |      |       |                          |       |

| Preamplifier Gain               | AV <sub>PA</sub>     |            |      | 2.818 |                          | V/V   |

| Preamplifier Gain<br>Accuracy   | AV <sub>PA_ACC</sub> |            | -2   |       | +2                       | %     |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

## **Electrical Characteristics—Boost Controller (continued)**

$(V_{IN} = 3.6V, T_A = +25^{\circ}C)$ , limits are 100% tested at  $T_A = +25^{\circ}C$ , unless otherwise noted. Min and Max limits are guaranteed by design and characterization from  $T_A = T_J = -40^{\circ}C$  to +125°C.) (Note 1)

| PARAMETER                                 | SYMBOL                 | CO                               | NDITIONS                | MIN   | TYP                        | MAX   | UNITS      |

|-------------------------------------------|------------------------|----------------------------------|-------------------------|-------|----------------------------|-------|------------|

| SLP COMPARATOR                            | •                      | l                                |                         | 1     |                            |       |            |

| SLP Comparator Level<br>Shift             | SLP <sub>CMP_LS</sub>  | SLP rising thresholow to high    | old when LX switches    |       | V <sub>COMP</sub> -<br>0.4 |       | V          |

| SLP Rising Threshold<br>Propagation Delay | CMP <sub>TPD</sub>     | Rising input slew                | rate = 1V/µs            |       | 10                         |       | ns         |

| SLP Discharge<br>Resistance               | SLP <sub>DSCHG</sub>   |                                  |                         |       | 8                          |       | Ω          |

|                                           |                        |                                  | T <sub>A</sub> = +25°C  | -1    |                            | +1    | μA         |

| SLP Leakage                               | SLP <sub>LKG</sub>     | V <sub>SLP</sub> = 5V            | T <sub>A</sub> = +85°C  |       | ±50                        |       | nA         |

|                                           |                        |                                  | T <sub>A</sub> = +125°C |       | ±250                       |       |            |

| COT COMPARATOR                            |                        | -                                |                         |       |                            |       |            |

| COT Comparator<br>Threshold               | COT <sub>CMP_TH</sub>  | COT rising thresh<br>high to low | old when LX switches    |       | V <sub>IN</sub> /10        |       | V          |

| COT Rising Threshold<br>Propagation Delay | COT <sub>TPD_R</sub>   | Rising input slew                | rate = 1V/µs            |       | 10                         |       | ns         |

| COT Discharge<br>Resistance               | COT <sub>DSCHG</sub>   |                                  |                         |       | 8                          |       | Ω          |

| COT Leakage                               | COT <sub>LKG</sub>     | s V <sub>COT</sub> = 5V          | T <sub>A</sub> = +25°C  | -1    |                            | +1    | µA<br>- nA |

|                                           |                        |                                  | T <sub>A</sub> = +85°C  |       | ±50                        |       |            |

|                                           |                        |                                  | T <sub>A</sub> = +125°C |       | ±250                       |       |            |

| ILIM COMPARATOR                           |                        |                                  |                         |       |                            |       |            |

|                                           |                        | ILIM_SEL<1,0> =                  | • (0,0)                 | 90    | 100                        | 110   |            |

| ILIM Comparator                           | ILIM <sub>CMP_TH</sub> | ILIM_SEL <1:0> =                 | = (0,1)                 | 190   | 200                        | 210   |            |

| Threshold                                 |                        | ILIM_SEL<1,0> = (1,0)            |                         | 285   | 300                        | 315   | – mV       |

|                                           |                        | ILIM_SEL<1,0> =                  | : (1,1)                 | 380   | 400                        | 420   |            |

| ILIM Rising Theshold<br>Propagation Delay | tPD_ILIM_CMP           | Rising input slew                | rate = 1V/µs            |       | 10                         |       | ns         |

| OVP COMPARATOR                            |                        |                                  |                         |       |                            |       |            |

| OVP Comparator<br>Threshold               | OVP <sub>CMP_TH</sub>  | OVP rising thresh low to high    | old when LX switches    | 3.336 | 3.512                      | 3.688 | V          |

| OVP Rising Threshold<br>Propagation Delay | OVP <sub>CMP_TPD</sub> | Rising input slew                | rate = 1V/µs            |       | 10                         |       | ns         |

| GATE DRIVER                               |                        |                                  |                         | •     |                            |       |            |

| HS_G Gate Driver<br>Pullup Strength       | HSG <sub>P_RON</sub>   |                                  |                         | 0.5   | 1                          | 2     | Ω          |

| HS_G Gate Driver<br>Pulldown Strength     | HSG <sub>N_RON</sub>   |                                  |                         | 21    | 33                         | 52    | Ω          |

| LS_G Gate Driver<br>Pulldown Strength     | LSG <sub>N_RON</sub>   |                                  |                         | 0.25  | 0.5                        | 1     | Ω          |

| LS_G Gate Driver<br>Pullup Strength       | LSG <sub>P_RON</sub>   |                                  |                         | 21    | 30                         | 49    | Ω          |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

### **Electrical Characteristics—Boost Controller (continued)**

(V<sub>IN</sub> = 3.6V, T<sub>A</sub> = +25°C, limits are 100% tested at T<sub>A</sub> = +25°C, unless otherwise noted. Min and Max limits are guaranteed by design and characterization from T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C.) (Note 1)

| PARAMETER                                   | SYMBOL               | CON                | CONDITIONS                    |    | TYP   | MAX | UNITS |

|---------------------------------------------|----------------------|--------------------|-------------------------------|----|-------|-----|-------|

| T <sub>ON</sub> AND T <sub>OFF</sub> CONTRO | LLER                 | •                  |                               |    |       |     |       |

| Maximum T <sub>ON</sub>                     | TON <sub>MAX</sub>   | Maximum on time le | Maximum on time low-side NFET |    | 3.6   | 7   | μs    |

| Maximum T <sub>OFF</sub>                    | TOFF <sub>MAX</sub>  | Maximum on time h  | nigh-side PFET                | 1  | 2     | 4   | μs    |

| Minimum T <sub>ON</sub>                     | TON <sub>MIN</sub>   | Minimum on time Ic | w-side NFET                   |    | 50    |     | ns    |

| Minimum T <sub>OFF</sub>                    | TOFF <sub>MIN</sub>  | Minimum on time h  | igh-side PFET                 |    | 10    |     | ns    |

| FB_SW PIN                                   |                      |                    |                               | ·  |       |     |       |

| FB_SW Input<br>Resistance                   | FB_SW <sub>IR</sub>  |                    |                               |    | 54    |     | Ω     |

|                                             |                      |                    | T <sub>A</sub> = +25°C        | -1 |       | +1  | μA    |

| FB_SW Leakage                               | FB_SW <sub>LKG</sub> | $V_{FB_SW} = 5V$   | T <sub>A</sub> = +85°C        |    | ±50   |     | - 0   |

|                                             |                      |                    | T <sub>A</sub> = +125°C       |    | ±250  |     | nA    |

| CS_IN LEAKAGE                               |                      | ·                  | ·                             | ·  |       |     |       |

|                                             |                      | nEN = 0V, SSB =    | T <sub>A</sub> = +25°C        | -1 |       | +1  |       |

| CS_IN Leakage Current                       |                      |                    | T <sub>A</sub> = +85°C        |    | ±0.01 |     | μΑ    |

|                                             |                      | V <sub>IO</sub>    | T <sub>A</sub> = +125°C       |    | ±0.01 |     | ]     |

### **Electrical Characteristics—SPI Communication Controller**

$(V_{IN} = 3.6V, T_A = +25^{\circ}C)$ , limits are 100% tested at  $T_A = +25^{\circ}C$ , unless otherwise noted. Min and Max limits are guaranteed by design and characterization from  $T_A = T_J = -40^{\circ}C$  to +125°C.) (Note 1)

| PARAMETER SYMBOL                                                        |                     | CONDITIONS                                      | MIN                  | ТҮР          | MAX  | UNITS |

|-------------------------------------------------------------------------|---------------------|-------------------------------------------------|----------------------|--------------|------|-------|

| SPI                                                                     |                     | -                                               |                      |              |      | 1     |

| V <sub>IO</sub> Supply Voltage                                          | V <sub>IO</sub>     |                                                 | 1.62                 | 1.8          | 1.98 | V     |

|                                                                         |                     | T <sub>A</sub> = +25°C                          | -1                   | 0.1          | +1   | μA    |

| Input Leakage Current<br>(SSB, SCLK, MOSI)                              | LEAK <sub>SPI</sub> | T <sub>A</sub> = +85°C                          |                      | ±10          |      | 20    |

|                                                                         |                     | T <sub>A</sub> = +125°C                         |                      | ±250         |      | - nA  |

| Input Capacitance (SSB, SCLK, MOSI)                                     | C_IN <sub>SPI</sub> |                                                 |                      | 10           |      | pF    |

| SPI Input Logic Low<br>Voltage (SSB, SCLK,<br>MOSI)                     | VIL <sub>SPI</sub>  |                                                 |                      |              | 0.4  | v     |

| SPI Input Logic High<br>Voltage (SSB, SCLK, VIH <sub>SPI</sub><br>MOSI) |                     |                                                 | 1.4                  |              |      | v     |

| SPI Input Logic<br>Hysteresis                                           | VI <sub>HYST</sub>  |                                                 |                      | 275          |      | mV    |

| SPI Logic VOH VOH <sub>MISO</sub>                                       |                     | IOH <sub>MISO</sub> = 2mA                       | V <sub>IO</sub> -0.4 |              |      | V     |

| SPI Logic VOL                                                           | VOL <sub>MISO</sub> | IOL <sub>MISO</sub> = 2mA                       |                      |              | 0.4  | V     |

| MISO Lookago Current                                                    | MISO                | SSB = $V_{IO}$ , $T_A$ = +25°C                  | -1                   | -1 +1<br>0.1 |      |       |

| MISO Leakage Current                                                    | MISO <sub>LKG</sub> | SSB = V <sub>IO</sub> , T <sub>A</sub> = +125°C |                      |              |      | - μΑ  |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

## **Electrical Characteristics—SPI Communication Controller (continued)**

$(V_{IN} = 3.6V, T_A = +25^{\circ}C)$ , limits are 100% tested at  $T_A = +25^{\circ}C$ , unless otherwise noted. Min and Max limits are guaranteed by design and characterization from  $T_A = T_J = -40^{\circ}C$  to +125°C.) (Note 1)

| PARAMETER                                   | SYMBOL                          | CONDITIONS                                    | MIN | TYP | MAX | UNITS |  |  |

|---------------------------------------------|---------------------------------|-----------------------------------------------|-----|-----|-----|-------|--|--|

| SPI INTERFACE TIMING                        |                                 |                                               |     |     |     |       |  |  |

| SPI Operating<br>Frequency                  | f <sub>SPI</sub>                | V <sub>IO</sub> = 1.8V                        |     | 25  |     | MHz   |  |  |

| MOSI Input Valid to<br>SCLK Rising Edge     | <sup>t</sup> su_mosi            | V <sub>IO</sub> = 1.8V                        | 10  |     |     | ns    |  |  |

| MOSI Input Valid from<br>SCLK Rising Edge   | <sup>t</sup> HD_MOSI            | V <sub>IO</sub> = 1.8V                        | 10  |     |     | ns    |  |  |

| MISO Output Valid from<br>SCLK Falling Edge | <sup>t</sup> D_MISO             | V <sub>IO</sub> = 1.8V, C <sub>L</sub> = 50pF |     |     | 19  | ns    |  |  |

| MISO Rising/Falling<br>Time                 | t <sub>R</sub> , t <sub>F</sub> | V <sub>IO</sub> = 1.8V, C <sub>L</sub> = 20pF |     |     | 10  | ns    |  |  |

| SSB Setup Time Before<br>SCLK               | t <sub>SU_SSB</sub>             | V <sub>IO</sub> = 1.8V                        | 20  |     |     | ns    |  |  |

| SSB Hold Time After<br>SCLK                 | t <sub>HD_SSB</sub>             | V <sub>IO</sub> = 1.8V                        | 20  |     |     | ns    |  |  |

| Minimum SSB HIGH<br>Pulse Width             | t <sub>SSB_</sub> H(MIN)        | V <sub>IO</sub> = 1.8V                        | 50  |     |     | ns    |  |  |

Note 1: See the Typical Applications Circuit.

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

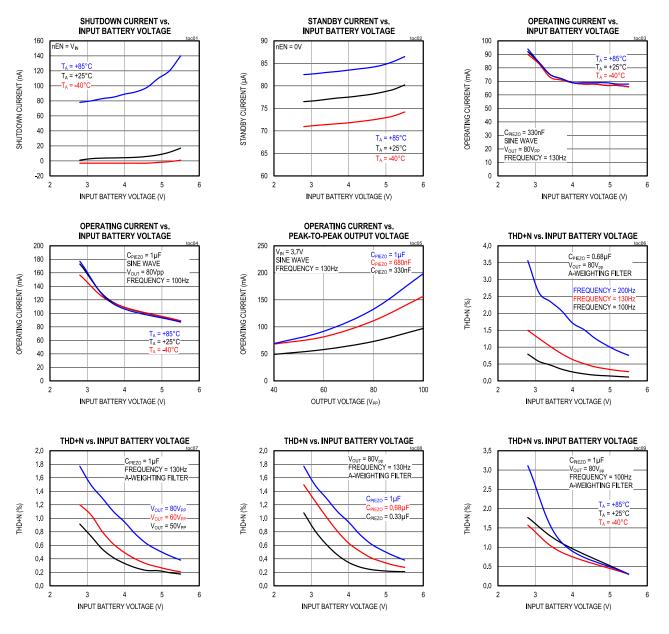

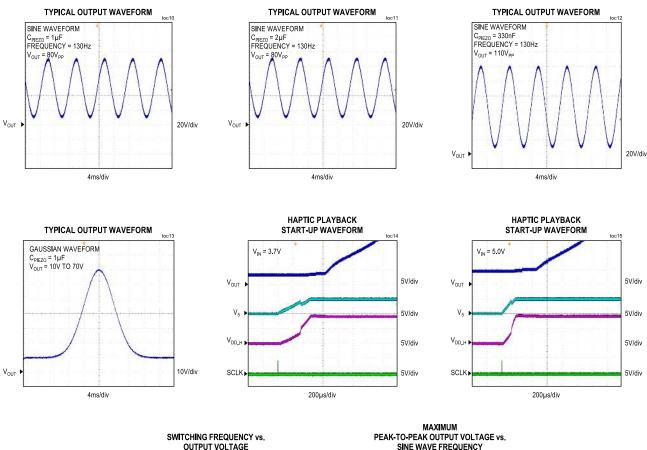

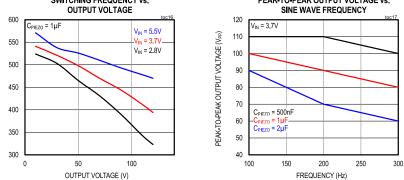

## **Typical Operating Characteristics**

(Typical Applications Circuit,  $V_{IN}$  = 3.7V,  $V_{IO}$  = 1.8V, L = 10µH, T<sub>A</sub> = +25°C, unless otherwise noted. See <u>Table 13</u> for the components chosen for specific piezo capacitance values (C<sub>PIEZO</sub>) listed.)

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

## **Typical Operating Characteristics (continued)**

(Typical Applications Circuit,  $V_{IN}$  = 3.7V,  $V_{IO}$  = 1.8V, L = 10µH, T<sub>A</sub> = +25°C, unless otherwise noted. See <u>Table 13</u> for the components chosen for specific piezo capacitance values (C<sub>PIEZO</sub>) listed.)

SWITCHING FREQUENCY (kHz)

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

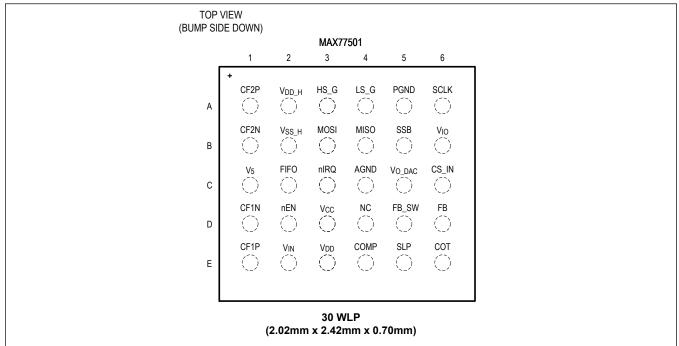

## **Bump Configurations**

#### **30 WLP**

### **Bump Descriptions**

| PIN | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                      |

|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A5  | PGND              | Power Ground. Connect the PGND pin to the PCB ground plane. Refer to the <u>PCB Layout</u><br><u>Guidelines</u> section for more information.                                                                                                                                                                                 |

| C4  | AGND              | Analog Ground. The AGND pin must be connected to PGND, preferably close to the PGND pin. See the <u>PCB Layout Guidelines</u> section for more information.                                                                                                                                                                   |

| E2  | V <sub>IN</sub>   | Voltage Input Supply Pin. Bypass to AGND with a 1 $\mu$ F ceramic capacitor close to the IC. There should be two separate supply paths from the input power supply, a high-current path to the inductor and a separate, low-current path to V <sub>IN.</sub> See the <u>Typical Application Circuit</u> for more information. |

| B2  | V <sub>SS_H</sub> | High-Side Voltage Reference. Connect a 2.2nF decoupling capacitor for the high-side gate driver from $V_{SS_H}$ to the $V_{DD_H}$ pin.                                                                                                                                                                                        |

| A2  | V <sub>DD_H</sub> | Gate Driver Supply Voltage Output. Bypass this pin with a 1µF capacitor to PGND. This pin is the output of the second charge pump and is approximately 9V.                                                                                                                                                                    |

| E3  | V <sub>DD</sub>   | Internal Logic Supply Voltage Output. 1.8V output from internal bias block, powered from $V_{IN}$ .<br>Bypass with 1µF to AGND. Do not use for external loads.                                                                                                                                                                |

| C1  | V <sub>5</sub>    | 5 Volt Internal Charge Pump Output. V <sub>5</sub> is a regulated charge pump output voltage powered by $V_{IN}$ . Bypass with 1µF to PGND. Do not use for external loads.                                                                                                                                                    |

| D3  | V <sub>CC</sub>   | Low Noise Analog Supply Input. Connect a 2.2 $\mu$ F capacitor from this pin to AGND close to the IC. Connect a low value resistor (typically 1 $\Omega$ ) from V <sub>5</sub> to this pin.                                                                                                                                   |

| B6  | V <sub>IO</sub>   | SPI Logic I/O Supply Input. Bypass with a 1µF capacitor to AGND.                                                                                                                                                                                                                                                              |

| B5  | SSB               | SPI Chip Select Logic Input. Active-low.                                                                                                                                                                                                                                                                                      |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

## **Bump Descriptions (continued)**

| PIN | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B3  | MOSI               | SPI Serial Data Input (Master Output Slave Input).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B4  | MISO               | SPI Serial Data Output (Master Input Slave Output). MISO is high-Z with SSB = V <sub>IO</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A6  | SCLK               | SPI Serial Clock Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| E1  | CF1P               | 5V Charge Pump Fly Cap, Positive Pin. Connect a 150nF capacitor from this pin to CF1N.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D1  | CF1N               | 5V Charge Pump Fly Cap, Negative Pin. Connect a 150nF capacitor from this pin to CF1P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A1  | CF2P               | 9V Charge Pump Fly Cap, Positive Pin. Connect a 150nF capacitor from this pin to CF2N.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| B1  | CF2N               | 9V Charge Pump Fly Cap, Negative Pin. Connect a 150nF capacitor from this pin to CF2P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A3  | HS_G               | High-Side Gate Driver Output. Connect a 10nF capacitor (150V minimum rating) from this pin to the gate of the external P-Channel power FET (see the <u>High Side PFET Drive applications</u> information section).                                                                                                                                                                                                                                                                                                                                                           |

| A4  | LS_G               | Low-Side Gate Driver Output. Connect this pin to the gate of the external power NFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D6  | FB                 | Voltage Feedback Input. Connect a resistor from V <sub>OUT</sub> to this pin and another resistor from this pin to either AGND or to the FB_SW pin. The two resistors form a resistor divider to set the closed-loop gain of the system. Route the resistor divider close to the IC and away from clock, logic or other digital signals. The FB_SW pin is off (high-Z) when the part is in shutdown or standby modes reducing leakage current from V <sub>OUT</sub> if desired. See the <i>Full-Scale Options</i> section for more information on selecting resistor values. |

| C5  | V <sub>O_DAC</sub> | DAC Output. Connect a 39pF filter capacitor from this pin to AGND to provide a LPF function to the DAC output signal. The LPF reduces clock and sampling frequency energy at the DAC output (i.e., anti-aliasing) before driving the boost converter.                                                                                                                                                                                                                                                                                                                        |

| E4  | COMP               | Compensation Network Input. Connect the external compensation components from this pin to AGND as shown in the <i>External Component Selection Guide</i> section. Place these components as close to the COMP pin as possible.                                                                                                                                                                                                                                                                                                                                               |

| C6  | CS_IN              | Current Sense Input. Connect this pin to a 390pF capacitor to AGND and to the slope-<br>compensation capacitor (see the Slope Compensation section). Additionally, connect a $100\Omega$ from<br>this pin to the current sense resistor thereby forming a low-pass filter between the current sense<br>resistor and the CS_IN pin.                                                                                                                                                                                                                                           |

| D2  | nEN                | Active-Low Enable Input. Driving nEN low causes the IC to enter STANDBY mode. Connect a pullup resistor from this pin to $V_{IN}$ for shutdown. If nEN is driven from a source (e.g., a $\mu$ P) that is not 6V tolerant, then an external FET can be used as a level shift. See the <u>Turn-On Sequence</u> section for details on the nEN functionality.                                                                                                                                                                                                                   |

| C2  | FIFO               | Open-Drain FIFO Status Flag Output. The FIFO pin is active-low and indicates the fill status (see the <u>FIFO Full, Empty</u> , and <u>Almost Empty</u> section for more information). An external pullup resistor to $V_{IO}$ is required to use this pin function. Leave this pin unconnected if not used.                                                                                                                                                                                                                                                                 |

| D4  | NC                 | Leave this pin unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| E6  | СОТ                | Computed Off-Time Input. Connect a resistor from $V_{OUT}$ to this pin and a capacitor from this pin to AGND to form a Low-Pass Filter from $V_{OUT}$ . The time constant of this filter partly determines the switching frequency of the boost converter (typically ~ 20µs for 500kHz switching frequency). See the <u>Switching Frequency and COT Timer Operation</u> section for more information.                                                                                                                                                                        |

| E5  | SLP                | Slope-Compensation Input Pin. Connect a resistor from $V_{OUT}$ to this pin, a resistor from $V_5$ to this pin, and a capacitor from this pin to the CS_IN pin. See the <u>Slope Compensation</u> section for more details.                                                                                                                                                                                                                                                                                                                                                  |

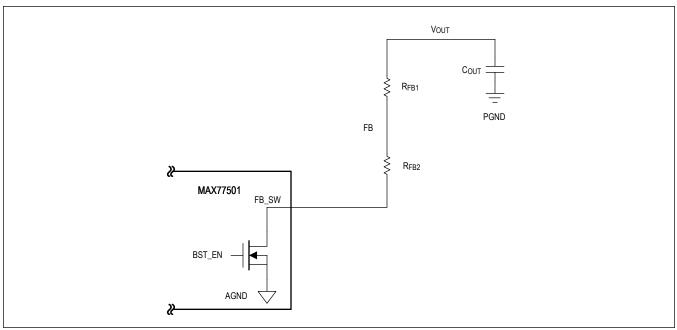

| D5  | FB_SW              | Feedback Resistor Termination Input. Connect the low-side feedback resistor (from FB) to this pin to reduce resistive load on V <sub>OUT</sub> during SHUTDOWN. Leave this pin unconnected if not used. See the <i>Feedback Switch Functionality</i> section for more details.                                                                                                                                                                                                                                                                                               |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

## **Bump Descriptions (continued)**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                       |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C3  | nIRQ | Active-Low Interrupt Request Output. An external pullup resistor to $V_{IO}$ (e.g., 100k $\Omega$ ) is required to use this pin function. The nIRQ is an active-LOW signal and is used to indicate a number of internal interrupt and fault conditions. See the nIRQ description in the <u>Interrupts and Fault</u> <u>Conditions</u> section. |

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

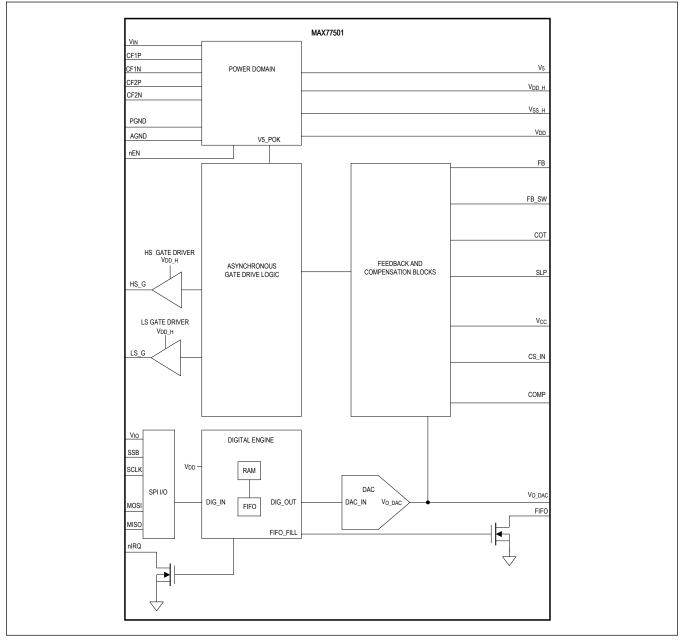

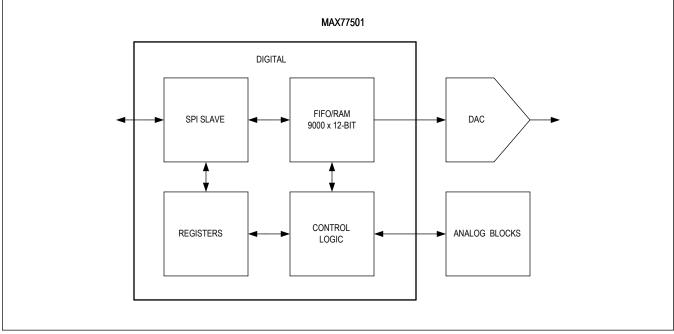

## **Functional Diagrams**

### Simplified Block Diagram

### **Detailed Description—Top Level**

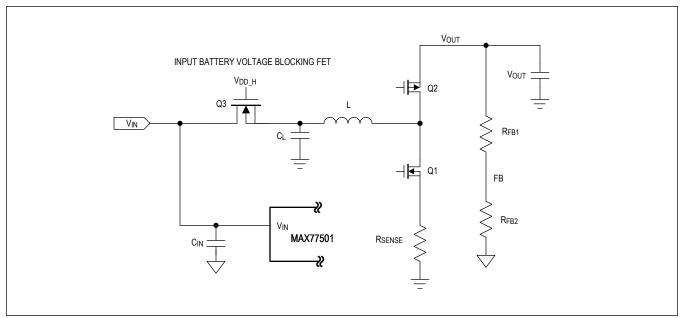

The MAX77501 is a highly-efficient piezo driver specifically developed for haptic, audio, or other transducer applications. The IC converts a stored or streamed digital input signal into a high voltage drive waveform up to 110Vpp (i.e., 10V minimum to 120V maximum  $V_{OUT}$ ). A proprietary, highly-efficient DC-to-AC, single-ended wave-shaping conversion process drives a piezo element, while consuming minimum input power.

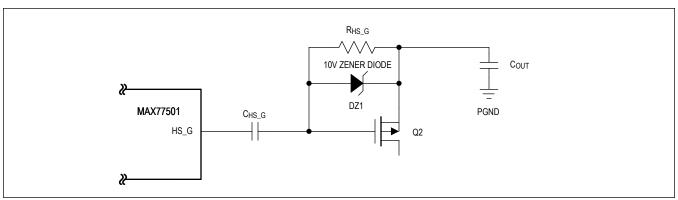

An internal charge pump generates a regulated 5V (V<sub>5</sub>), which then drives a second, voltage-doubling charge pump to generate a 9V ( $V_{DD\_H}$ ) voltage rail used by the gate drivers to drive the external power FETs. The high-side gate drive (HS\_G) is AC coupled to level-shift the gate drive to  $V_{OUT}$  and drives the high-side PFET. An external, 10V Zener diode and a parallel 20k $\Omega$  resistor resets the PFET gate charge to turn it off when HS\_G goes high. In this way, the PFET gate logic signal follows  $V_{OUT}$  at about one diode voltage above  $V_{OUT}$  to about 9V below  $V_{OUT}$  during each off time.

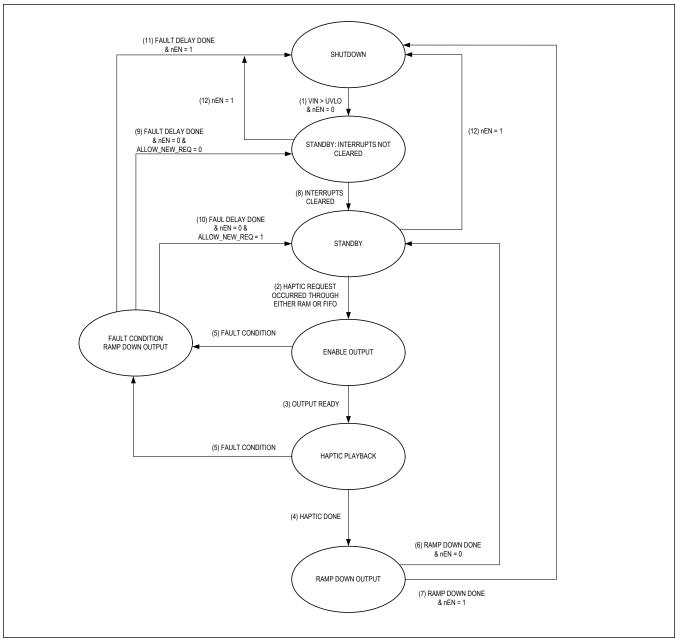

### State Diagram

The MAX77501 has three primary modes of operation:

- A low current SHUTDOWN mode where all of the internal blocks are off.

- A STANDBY mode where a minimal set of circuits are active to receive SPI commands.

- A fully enabled HAPTIC PLAYBACK mode.

Figure 1 describes this state diagram and how to move between each of the three states as well as other, intermediary states.

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

Figure 1. State Diagram

# 110V<sub>PK-PK</sub> High-Efficiency Piezo Haptic Actuator Boost Driver

# Table 1. State Diagram Description

| STATE/<br>TRANSITION                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SHUTDOWN                                                    | The IC is in SHUTDOWN mode with low shutdown current. All functionality is off and the SPI communication bus does not function.                                                                                                                                                                                                                                                                                                                                                                    |

| (1) V <sub>IN</sub> > UVLO and<br>nEN = 0                   | When the power supply is present and nEN is pulled low, the part enables the internal oscillator and bias circuitry. Once this is complete, the part transitions into the STANDBY: INTERRUPTS NOT CLEARED state. The SPI Ready interrupt occurs and the ISR_SPI_RDY register needs to be read and cleared before moving to the STANDBY state.                                                                                                                                                      |

| STANDBY:<br>INTERRUPTS NOT<br>CLEARED                       | After the output is disabled due to a fault condition, the IC transitions back into the STANDBY:<br>INTERRUPTS NOT CLEARED state. HAPTIC PLAYBACK mode cannot occur until the interrupts are<br>cleared. Read the ISR register in order to clear the interrupts and transition into the STANDBY state. The IC<br>also transitions into this state when nEN is pulled low due to the SPI Ready Interrupt. This state is the same<br>as the STANDBY state, except haptic playback cannot be enabled. |

| STANDBY                                                     | STANDBY mode is a low-power state where the output is disabled and the system awaits a haptic playback request from the user. The SPI bus is working and the registers and RAM can be written to and read from in order to prepare for a haptic request.                                                                                                                                                                                                                                           |