# **TMC4361A DATASHEET**

TMC4361A Document Revision 1.24 • 2018-Sep-20

The S-ramp and sixPoint<sup>™</sup> ramp motion controller for stepper motors is optimized for high velocities, allowing on-the-fly changes. TMC4361A offers SPI and Step/Dir interfaces, as well as an encoder interface for closed-loop operation.

# <u>NOTE:</u>

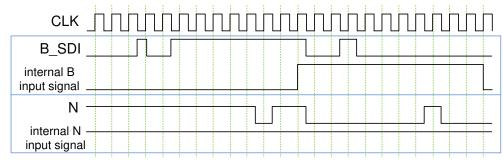

$\rightarrow$  TMC4361A is a product upgrade of TMC4361.

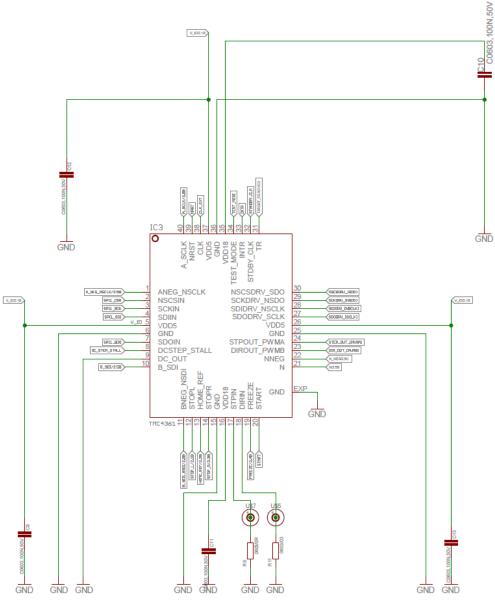

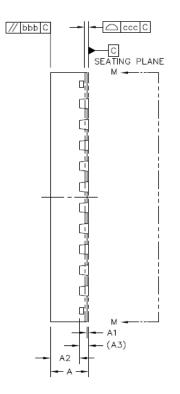

Figure 1: Sample Image TMC4361A Closed-Loop Drive \*Marking details are explained on page 224.

- Textile, sewing machines

- CCTV, security

- Printers, scanners

- ATM, cash recycler

- Features

- SPI Interfaces for µC with easy-to-use protocol.

- SPI Interfaces for SPI motor stepper drivers.

- Encoder interface for incremental or serial encoders.

- Closed-loop operation for Step and SPI drivers.

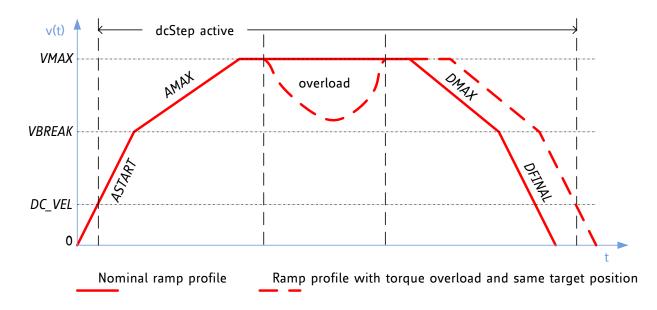

- Integrated ChopSync<sup>™</sup> and dcStep<sup>™</sup> support.

- Internal ramp generator generating S-shaped ramps or sixPoint<sup>™</sup> ramps supporting on-the-fly changes.

- Controlled PWM output.

- Reference switch handling.

- Hardware and virtual stop switches.

- Extensive Support of TMC stepper motor drivers.

# **Applications**

- Office automation

- POS

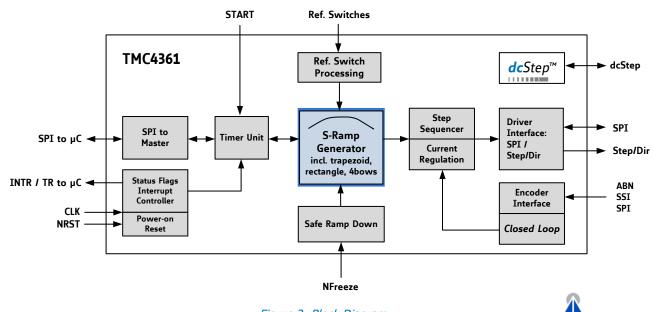

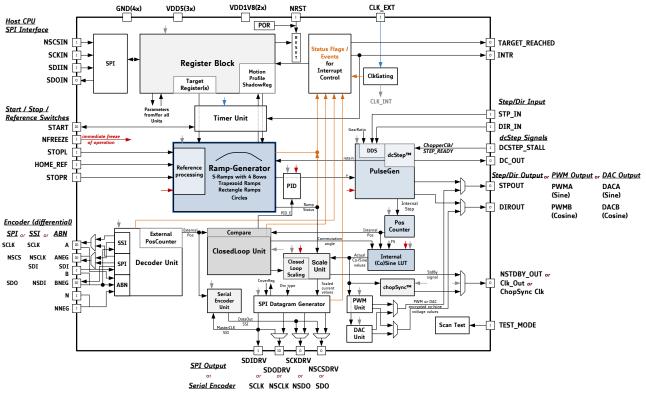

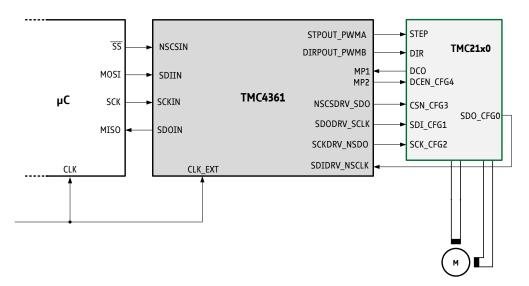

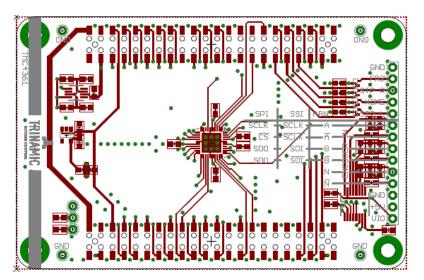

**Block Diagram: TMC4361A Interfaces & Features**

- Factory automation

- Lab automation

- Pumps and valves

- Heliostat controllers

- CNC machines

- Robotics

Figure 2: Block Diagram

© 2018 TRINAMIC Motion Control GmbH & Co. KG, Hamburg, Germany — Terms of delivery and rights to technical change reserved. Download newest version at: <u>www.trinamic.com</u>.

Read entire documentation; especially the Supplemental Directives in chapter 22 (page 225).

# **Functional Scope of TMC4361A**

TMC4361A is a miniaturized high-performance motion controller for stepper motor drivers, particularly designed for fast and jerk-limited motion profile applications with a wide range of ramp profiles. The S-shaped or sixPoint<sup>™</sup> velocity profile, closed-loop and open-loop features offer many configuration options to suit the user's specifications, as presented below:

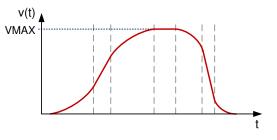

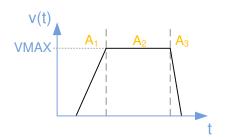

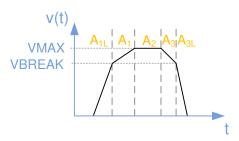

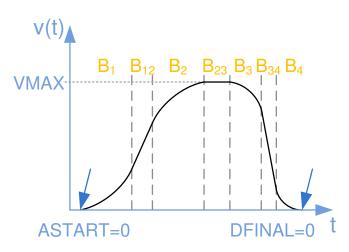

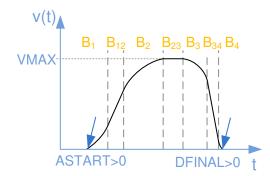

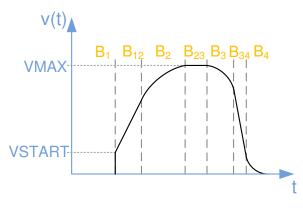

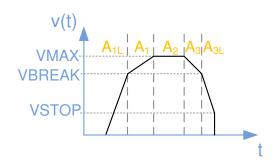

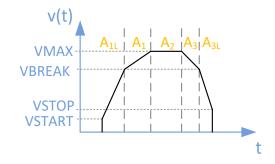

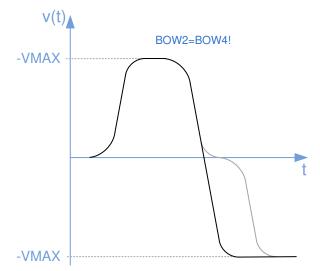

S-Shaped Velocity Profile S-shaped ramp profiles are jerk-free. Seven ramp segments form the S-shaped ramp that can be optimally adapted to suit the user's requirements. High torque with high velocities can be reached by calibrating the bows of the ramp, as explained in this user manual.

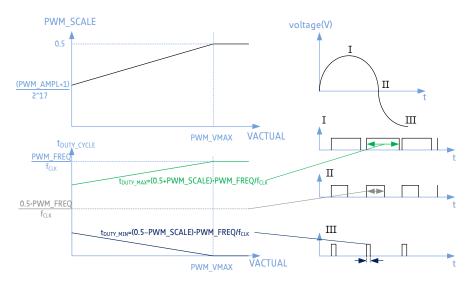

Figure 3: S-shaped Velocity Profile

More information on ramp configurations and other velocity profiles, e.g. sixPoint<sup>™</sup> ramps, are provided in chapter <u>6</u> (Page <u>28</u>).

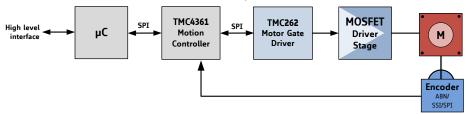

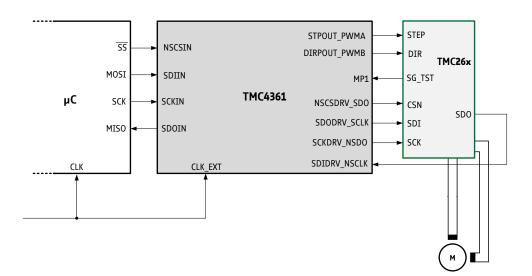

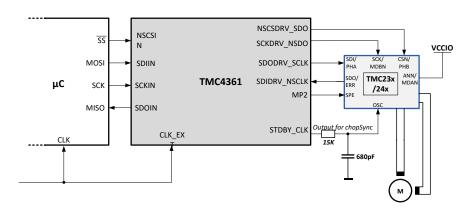

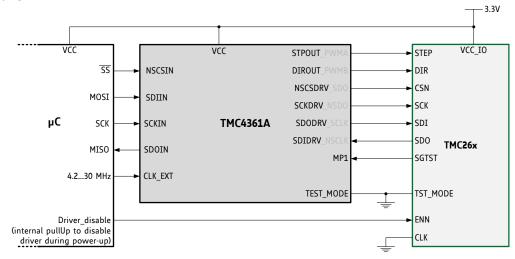

Closed-loop Operation Feature A typical hardware setup for closed-loop operation with a TMC262 stepper motor gate driver is shown in the diagram below. In case internal MOSFETs are desired, combine the TMC4361A with the TMC2620, the TMC261 or the TMC2660.

Figure 4: Hardware Set-up for Closed-loop Operation with TMC262

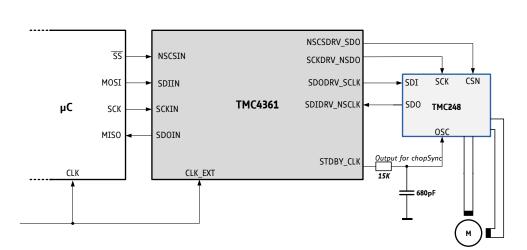

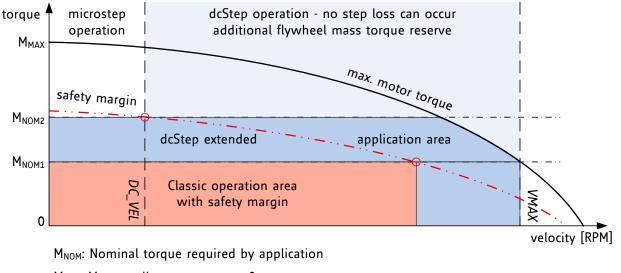

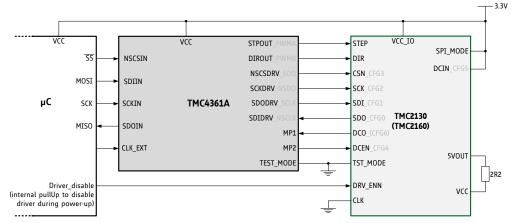

Open-loop Operation with dcStep™ Feature A typical hardware setup for dcStep operation with a TMC2130 stepper motor driver is shown in the diagram below. This feature is also available for TMC2160 and TMC26x stepper motor drivers.

Figure 5: Hardware Set-up for Open-loop Operation with TMC2130 resp. TMC2160

# **Order Codes**

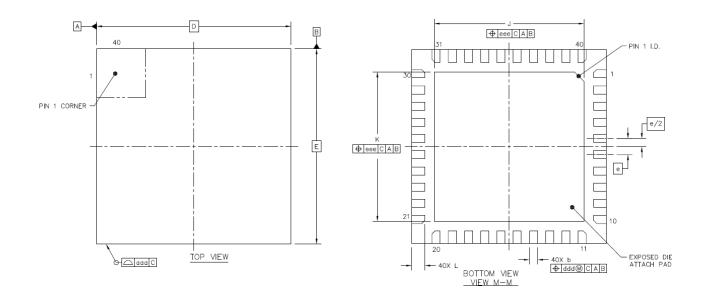

| Order code    | Description                                                         | Size      |

|---------------|---------------------------------------------------------------------|-----------|

| TMC4361A-LA   | Motion controller with closed-loop and dcStep features, QFN40, Tray | 6 x 6 mm² |

| TMC4361A-LA-T | Motion controller with closed-loop and dcStep features, QFN40, Tape | 6 x 6 mm² |

Table 1: TMC4361A Order Codes

© 2018 TRINAMIC Motion Control GmbH & Co. KG, Hamburg, Germany — Terms of delivery and rights to technical change reserved. Download newest version at: <a href="http://www.trinamic.com">www.trinamic.com</a> .

Read entire documentation; especially the Supplemental Directives in chapter 22 (page 225)

# TABLE OF CONTENTS

| ТМ  | C4361A           | DATASHEET                                                                                                               | 1  |

|-----|------------------|-------------------------------------------------------------------------------------------------------------------------|----|

| SH  | ORT SPE          | EC                                                                                                                      | 1  |

| Fea | atures           |                                                                                                                         | 1  |

| Ap  | plication        | IS                                                                                                                      | 1  |

| Blo | ck Diag          | ram: TMC4361A Interfaces & Features                                                                                     | 1  |

|     | _                | Scope of TMC4361A                                                                                                       |    |

|     |                  | 25                                                                                                                      |    |

|     |                  | CONTENTS                                                                                                                |    |

|     |                  |                                                                                                                         | _  |

|     |                  |                                                                                                                         |    |

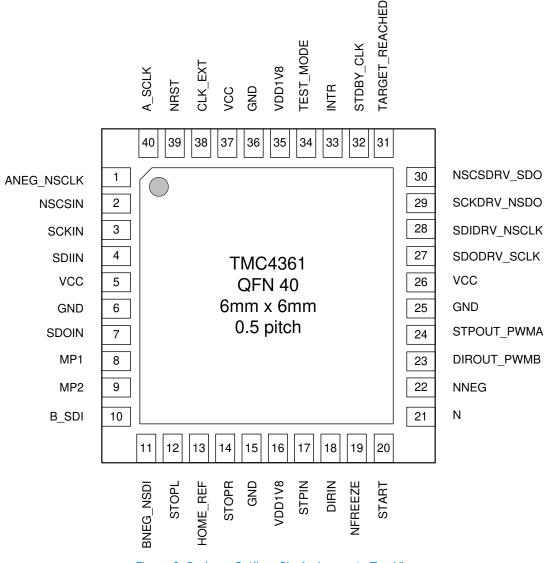

| 1.  |                  | g and Design-In Process Information                                                                                     |    |

|     | 1.1.<br>1.2.     | Pin Assignment: Top View<br>Pin Description                                                                             |    |

|     | 1.2.             | System Overview                                                                                                         |    |

| 2.  | -                | tion Circuits                                                                                                           |    |

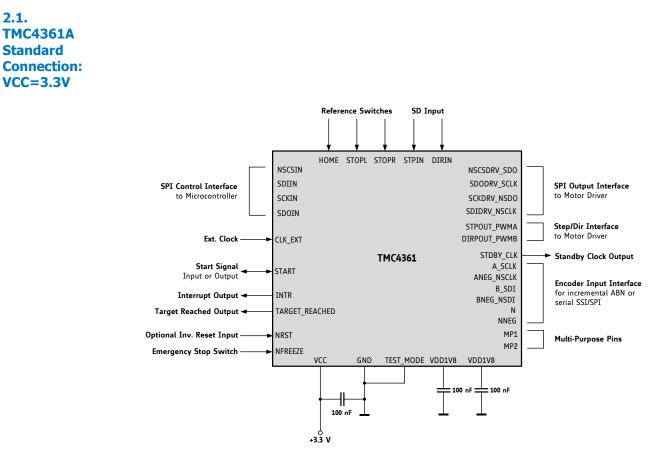

|     | 2.1.             | TMC4361A Standard Connection: VCC=3.3V                                                                                  |    |

|     | 2.2.             | TMC4361A with TMC26x Stepper Connection                                                                                 |    |

|     | 2.3.             | TMC4361A with TMC248 Stepper Driver                                                                                     |    |

|     | 2.4.             | TMC4361A with TMC2130 resp. TMC2160 Stepper Driver                                                                      |    |

|     | 2.5.             | TMC4361A with TMC5130A, or TMC5160                                                                                      | 15 |

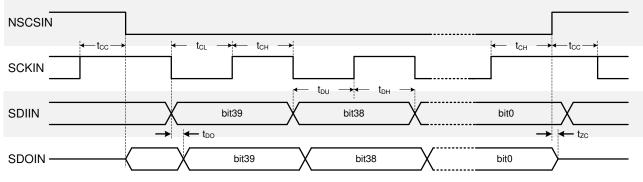

| 3.  | SPI Int          | erfacing                                                                                                                | 16 |

|     | 3.1.             | SPI Datagram Structure                                                                                                  | 16 |

|     | 3.1.1.           | SPI Timing Description                                                                                                  | 19 |

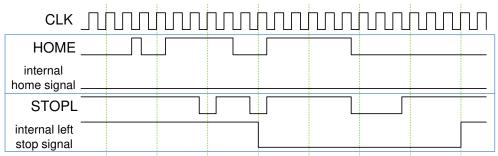

| 4.  | Input F          | Filtering                                                                                                               | 20 |

|     | 4.1.             | Input Filtering Examples                                                                                                | 22 |

|     | 4.2.             | Configuration of Step/Dir Input Filter                                                                                  | 23 |

| 5.  | Status           | Flags and Events                                                                                                        | 24 |

|     | 5.1.             | Status Event Description                                                                                                | 25 |

|     | 5.2.             | SPI Status Bit Transfer                                                                                                 | -  |

|     | 5.3.             | Generation of Interrupts                                                                                                |    |

|     | 5.4.             | Connection of Multiple INTR Pins                                                                                        |    |

| 6.  | Ramp (           | Configurations for different Motion Profiles                                                                            |    |

|     | 6.1.             | Step/Dir Output Configuration                                                                                           |    |

|     | 6.1.1.           | Step/Dir Output Configuration Steps                                                                                     |    |

|     | 6.1.2.           | STPOUT: Changing Polarity                                                                                               |    |

|     | 6.2.             | Altering the Internal Motion Direction                                                                                  |    |

|     | 6.3.<br>6.3.1.   | Configuration Details for Operation Modes and Motion Profiles<br>Starting Point: Choose Operation Mode                  |    |

|     | 6.3.1.<br>6.3.2. | Stop during Motion                                                                                                      |    |

|     | 6.3.3.           | Motion Profile Configuration                                                                                            |    |

|     | 6.3.4.           | No Ramp Motion Profile                                                                                                  |    |

|     | 6.3.5.           | Trapezoidal 4-Point Ramp without Break Point                                                                            |    |

|     | 6.3.6.           | Trapezoidal Ramp with Break Point                                                                                       |    |

|     | 6.3.7.           | Position Mode combined with Trapezoidal Ramps                                                                           |    |

|     |                  | Motion Control GmbH & Co. KG, Hamburg, Germany — Terms of delivery and rights to technical change reserved.             |    |

| Do  | wnload newest v  | version at: www.trinamic.com 🚱 Read entire documentation; especially the Supplemental Directives in chapter 22, p. 225. |    |

|    | 6.3.8.                                                                                                                                                                                               | Configuration of S-Shaped Ramps                                                                                                                                                                                                                                                                                                                             | 37                                                                                                                                                |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 6.3.9.                                                                                                                                                                                               | S-Ramps: Changing Ramp Parameters during Motion or Switching to Positiong Mode                                                                                                                                                                                                                                                                              | 38                                                                                                                                                |

|    | 6.3.10.                                                                                                                                                                                              | Configuration of S-shaped Ramp with ASTART and DFINAL                                                                                                                                                                                                                                                                                                       | 38                                                                                                                                                |

|    | 6.3.11.                                                                                                                                                                                              | S-shaped Mode and Positioning: Fast Motion                                                                                                                                                                                                                                                                                                                  | 39                                                                                                                                                |

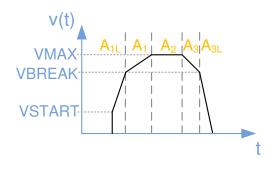

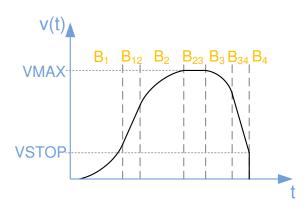

|    | 6.4.                                                                                                                                                                                                 | Start Velocity VSTART and Stop Velocity VSTOP                                                                                                                                                                                                                                                                                                               | 40                                                                                                                                                |

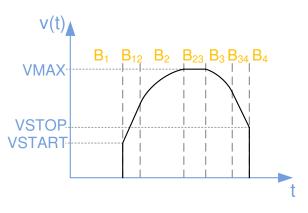

|    | 6.4.1.                                                                                                                                                                                               | S-shaped Ramps with Start and Stop Velocity                                                                                                                                                                                                                                                                                                                 | 44                                                                                                                                                |

|    | 6.4.2.                                                                                                                                                                                               | Combined Use of VSTART and ASTART for S-shaped Ramps                                                                                                                                                                                                                                                                                                        | 45                                                                                                                                                |

|    | 6.5.                                                                                                                                                                                                 | sixPoint Ramps                                                                                                                                                                                                                                                                                                                                              | 46                                                                                                                                                |

|    | 6.6.                                                                                                                                                                                                 | U-Turn Behavior                                                                                                                                                                                                                                                                                                                                             | 47                                                                                                                                                |

|    | 6.6.1.                                                                                                                                                                                               | Continuous Velocity Motion Profile for S-shaped Ramps                                                                                                                                                                                                                                                                                                       | 48                                                                                                                                                |

|    | 6.7.                                                                                                                                                                                                 | Internal Ramp Generator Units                                                                                                                                                                                                                                                                                                                               | 49                                                                                                                                                |

|    | 6.7.1.                                                                                                                                                                                               | Clock Frequency                                                                                                                                                                                                                                                                                                                                             | 49                                                                                                                                                |

|    | 6.7.2.                                                                                                                                                                                               | Velocity Value Units                                                                                                                                                                                                                                                                                                                                        | 49                                                                                                                                                |

|    | 6.7.3.                                                                                                                                                                                               | Acceleration Value Units                                                                                                                                                                                                                                                                                                                                    | 49                                                                                                                                                |

|    | 6.7.4.                                                                                                                                                                                               | Bow Value Units                                                                                                                                                                                                                                                                                                                                             | 50                                                                                                                                                |

|    | 6.7.5.                                                                                                                                                                                               | Overview of Minimum and Maximum Values:                                                                                                                                                                                                                                                                                                                     | 50                                                                                                                                                |

| 7. | Extern                                                                                                                                                                                               | al Step Control and Electronic Gearing                                                                                                                                                                                                                                                                                                                      | 51                                                                                                                                                |

|    | 7.1.                                                                                                                                                                                                 | Description of Electronic Gearing                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                   |

|    | 7.2.                                                                                                                                                                                                 | Adapting VACTUAL during direct external step control                                                                                                                                                                                                                                                                                                        |                                                                                                                                                   |

|    | 7.3.                                                                                                                                                                                                 | Indirect External Control                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                   |

|    | 7.4.                                                                                                                                                                                                 | Switching from External to Internal Control                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                   |

| 8. |                                                                                                                                                                                                      | nce Switches                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                   |

| 0. | 8.1.                                                                                                                                                                                                 | Hardware Switch Support                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                 |

|    | 0.1.                                                                                                                                                                                                 | Haruware Switch Support                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                   |

|    | 011                                                                                                                                                                                                  | Ston Slong Configuration for Hard or Lingar Ston Slongs                                                                                                                                                                                                                                                                                                     | <b>CC</b>                                                                                                                                         |

|    | 8.1.1.                                                                                                                                                                                               | Stop Slope Configuration for Hard or Linear Stop Slopes                                                                                                                                                                                                                                                                                                     |                                                                                                                                                   |

|    | 8.1.2.                                                                                                                                                                                               | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56                                                                                                                                                |

|    | 8.1.2.<br>8.1.3.                                                                                                                                                                                     | How Active Stops are indicated and reset to Free Motion<br>How to latch Internal Position on Switch Events                                                                                                                                                                                                                                                  | 56<br>56                                                                                                                                          |

|    | 8.1.2.<br>8.1.3.<br>8.2.                                                                                                                                                                             | How Active Stops are indicated and reset to Free Motion<br>How to latch Internal Position on Switch Events<br>Virtual Stop Switches                                                                                                                                                                                                                         | 56<br>56<br>57                                                                                                                                    |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.                                                                                                                                                                   | How Active Stops are indicated and reset to Free Motion<br>How to latch Internal Position on Switch Events<br>Virtual Stop Switches<br>Enabling Virtual Stop Switches                                                                                                                                                                                       | 56<br>56<br>57<br>57                                                                                                                              |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.                                                                                                                                                         | How Active Stops are indicated and reset to Free Motion<br>How to latch Internal Position on Switch Events<br>Virtual Stop Switches<br>Enabling Virtual Stop Switches<br>Virtual Stop Slope Configuration                                                                                                                                                   | 56<br>56<br>57<br>57<br>57                                                                                                                        |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.2.<br>8.2.3.                                                                                                                                     | How Active Stops are indicated and reset to Free Motion<br>How to latch Internal Position on Switch Events<br>Virtual Stop Switches<br>Enabling Virtual Stop Switches<br>Virtual Stop Slope Configuration<br>How Active Virtual Stops are indicated and reset to Free Motion                                                                                | 56<br>57<br>57<br>57<br>57                                                                                                                        |

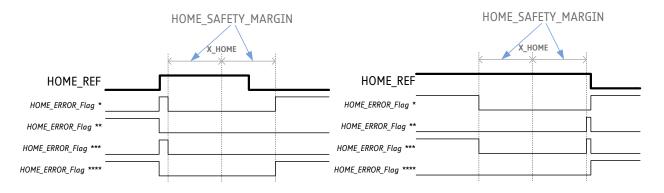

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.                                                                                                                                       | How Active Stops are indicated and reset to Free Motion<br>How to latch Internal Position on Switch Events<br>Virtual Stop Switches<br>Enabling Virtual Stop Switches<br>Virtual Stop Slope Configuration<br>How Active Virtual Stops are indicated and reset to Free Motion<br>Home Reference Configuration                                                | 56<br>57<br>57<br>57<br>57<br>58<br>59                                                                                                            |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.<br>8.3.1.                                                                                                                             | How Active Stops are indicated and reset to Free Motion<br>How to latch Internal Position on Switch Events<br>Virtual Stop Switches<br>Enabling Virtual Stop Switches<br>Virtual Stop Slope Configuration<br>How Active Virtual Stops are indicated and reset to Free Motion<br>Home Reference Configuration<br>Home Event Selection                        | 56<br>57<br>57<br>57<br>57<br>58<br>59<br>59                                                                                                      |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.<br>8.3.1.<br>8.3.2.                                                                                                                   | How Active Stops are indicated and reset to Free Motion<br>How to latch Internal Position on Switch Events<br>Virtual Stop Switches<br>Enabling Virtual Stop Switches<br>Virtual Stop Slope Configuration<br>How Active Virtual Stops are indicated and reset to Free Motion<br>Home Reference Configuration<br>Home Event Selection<br>HOME_REF Monitoring | 56<br>57<br>57<br>57<br>58<br>59<br>59<br>60                                                                                                      |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.<br>8.3.1.<br>8.3.2.<br>8.3.3.                                                                                                         | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>58<br>59<br>60<br>61                                                                                                      |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.<br>8.3.1.<br>8.3.2.<br>8.3.3.<br>8.3.3.<br>8.4.                                                                                       | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>58<br>59<br>60<br>61<br>62                                                                                                |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.<br>8.3.1.<br>8.3.2.<br>8.3.3.<br>8.4.<br>8.4.1.                                                                                       | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>58<br>59<br>60<br>61<br>62<br>62                                                                                          |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.<br>8.3.1.<br>8.3.2.<br>8.3.3.<br>8.4.<br>8.4.1.<br>8.4.2.                                                                             | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>58<br>59<br>60<br>61<br>62<br>62<br>63                                                                                    |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.<br>8.3.1.<br>8.3.2.<br>8.3.3.<br>8.4.<br>8.4.1.<br>8.4.1.<br>8.4.2.<br>8.4.3.                                                         | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>58<br>59<br>60<br>61<br>62<br>62<br>63<br>64                                                                              |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.<br>8.3.1.<br>8.3.2.<br>8.3.3.<br>8.4.<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.5.                                                           | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>58<br>59<br>59<br>60<br>60<br>61<br>62<br>62<br>63<br>64<br>55                                                            |

|    | $\begin{array}{c} 8.1.2.\\ 8.1.3.\\ 8.2.\\ 8.2.1.\\ 8.2.2.\\ 8.2.3.\\ 8.3.\\ 8.3.1.\\ 8.3.2.\\ 8.3.3.\\ 8.4.\\ 8.4.1.\\ 8.4.2.\\ 8.4.3.\\ 8.5.\\ 8.5.1.\\ \end{array}$                               | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>58<br>59<br>60<br>61<br>62<br>62<br>63<br>65                                                                              |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.1.<br>8.3.2.<br>8.3.3.<br>8.4.<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.5.<br>8.5.1.<br>8.5.2.                                               | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>58<br>59<br>59<br>59<br>59<br>60<br>61<br>62<br>62<br>62<br>63<br>64<br>55<br>65<br>55                                    |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.1.<br>8.3.2.<br>8.3.3.<br>8.4.<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.5.<br>8.5.1.<br>8.5.2.<br>8.5.3.                                     | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>58<br>59<br>60<br>61<br>62<br>62<br>63<br>64<br>65<br>65<br>65                                                            |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.<br>8.3.1.<br>8.3.2.<br>8.3.3.<br>8.4.<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.5.<br>8.5.1.<br>8.5.2.<br>8.5.3.<br>8.5.4.                   | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>57<br>59<br>59<br>59<br>59<br>60<br>61<br>61<br>62<br>62<br>62<br>63<br>63<br>64<br>65<br>65<br>65<br>65<br>65<br>66<br>7 |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.<br>8.3.1.<br>8.3.2.<br>8.3.2.<br>8.3.3.<br>8.4.<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.5.<br>8.5.1.<br>8.5.2.<br>8.5.3.<br>8.5.4.<br>8.6. | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>58<br>59<br>60<br>61<br>62<br>62<br>62<br>63<br>65<br>65<br>65<br>65<br>67<br>67                                          |

|    | 8.1.2.<br>8.1.3.<br>8.2.<br>8.2.1.<br>8.2.2.<br>8.2.3.<br>8.3.<br>8.3.1.<br>8.3.2.<br>8.3.3.<br>8.4.<br>8.4.1.<br>8.4.2.<br>8.4.3.<br>8.5.<br>8.5.1.<br>8.5.2.<br>8.5.3.<br>8.5.4.                   | How Active Stops are indicated and reset to Free Motion                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>57<br>58<br>59<br>60<br>61<br>61<br>62<br>63<br>63<br>65<br>65<br>65<br>65<br>67<br>67                                          |

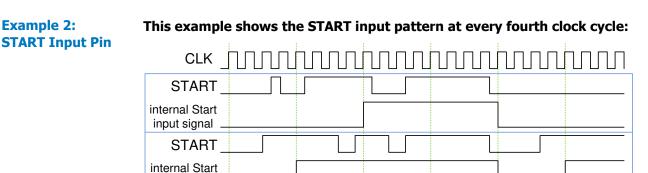

| 9.  | Ramp    | Timing and Synchronization                                             | 69  |

|-----|---------|------------------------------------------------------------------------|-----|

|     | 9.1.    | Basic Synchronization Settings                                         | 70  |

|     | 9.1.1.  | Start Signal Trigger Selection                                         | 70  |

|     | 9.1.2.  | User-specified Impact Configuration of Timing Procedure                | 70  |

|     | 9.1.3.  | Delay Definition between Trigger and internally generated Start Signal | 71  |

|     | 9.1.4.  | Active START Pin Output Configuration                                  | 71  |

|     | 9.1.5.  | Ramp Timing Examples                                                   | 72  |

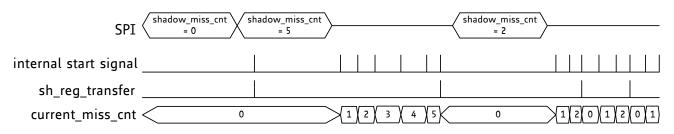

|     | 9.2.    | Shadow Register Settings                                               | 75  |

|     | 9.2.1.  | Shadow Register Configuration Options                                  | 76  |

|     | 9.2.2.  | Delayed Shadow Transfer                                                | 80  |

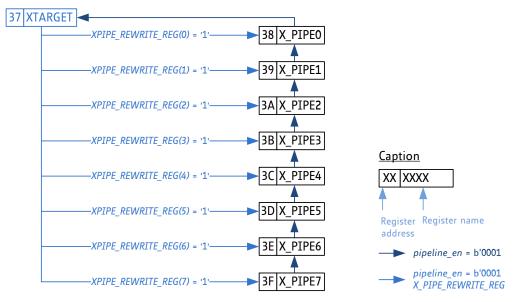

|     | 9.3.    | Pipelining Internal Parameters                                         | 81  |

|     | 9.3.1.  | Configuration and Activation of Target Pipeline                        | 81  |

|     | 9.3.2.  | Using the Pipeline for different internal Registers                    | 82  |

|     | 9.3.3.  | Pipeline Mapping Overview                                              | 83  |

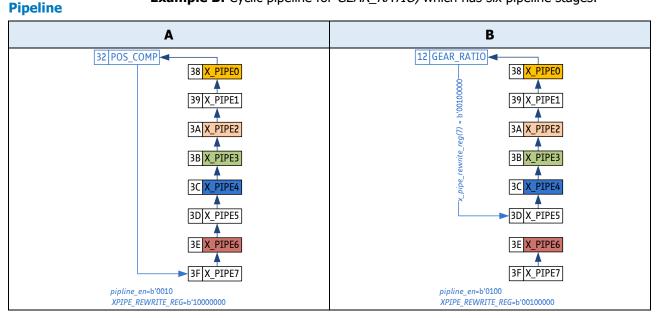

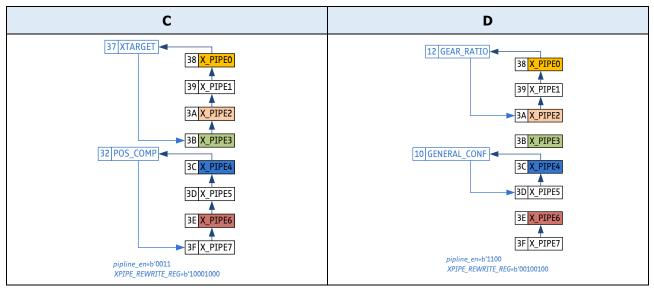

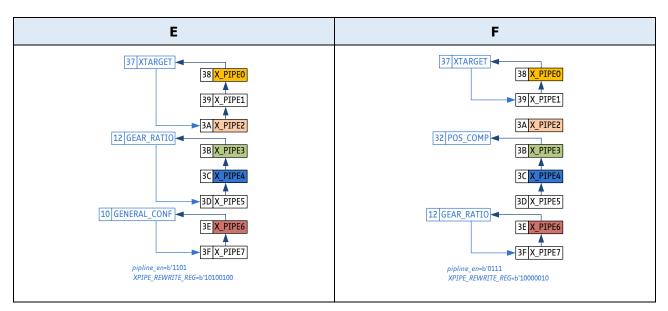

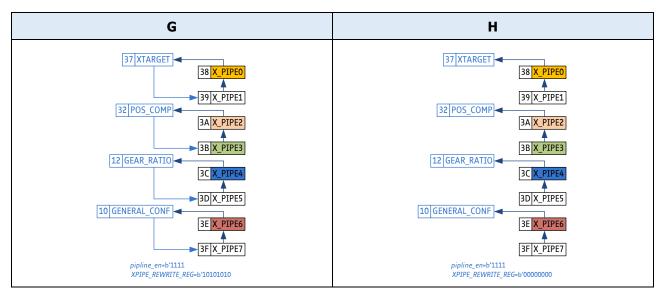

|     | 9.3.4.  | Cyclic Pipelining                                                      | 84  |

|     | 9.3.5.  | Pipeline Examples                                                      | 84  |

|     | 9.4.    | Masterless Synchronization of Several Motion Controllers via START Pin | 86  |

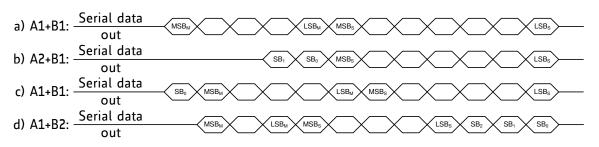

| 10. | Serial  | Data Output                                                            | 87  |

|     | 10.1.   | Getting Started with TMC Motor Drivers                                 |     |

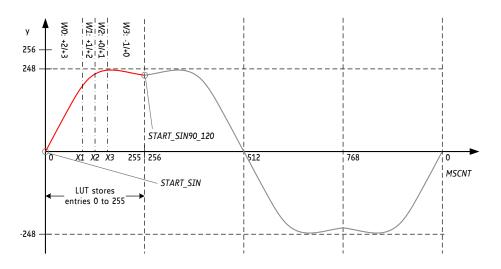

|     | 10.2.   | Sine Wave Lookup Tables                                                |     |

|     | 10.2.1. | Actual Current Values Output                                           |     |

|     | 10.2.2. | How to Program the Internal MSLUT                                      |     |

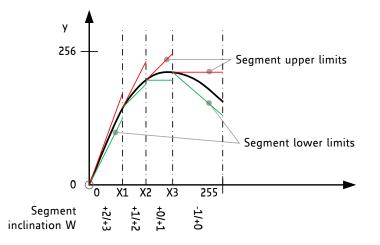

|     | 10.2.3. | Setup of MSLUT Segments                                                |     |

|     | 10.2.4. | Current Waves Start Values                                             |     |

|     | 10.2.5. | Default MSLUT                                                          |     |

|     | 10.2.6. | Explanatory Notes for Base Wave Inclinations                           |     |

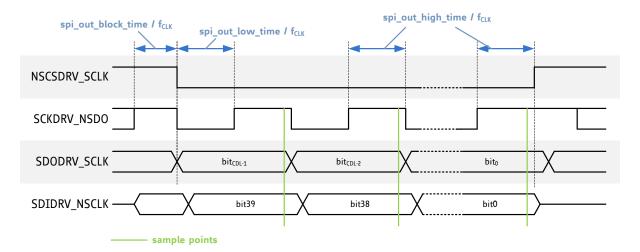

|     | 10.3.   | SPI Output Interface Configuration Parameters                          |     |

|     | 10.3.1. | How to enable SPI Output Communication                                 |     |

|     | 10.3.2. | Setup of SPI Output Timing Configuration                               |     |

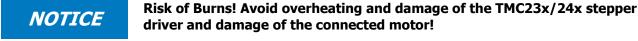

|     | 10.3.3. | Current Diagrams                                                       |     |

|     | 10.3.4. | Change of Microstep Resolution                                         |     |

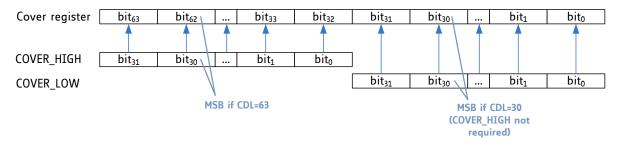

|     | 10.3.5. | Cover Datagrams Communication between µC and Driver                    |     |

|     | 10.3.6. | Sending Cover Datagrams                                                |     |

|     | 10.3.7. | Configuring Automatic Generation of Cover Datagrams                    |     |

|     | 10.4.   | Overview: TMC Motor Driver Connections                                 |     |

|     | 10.4.1. | TMC Stepper Motor Driver Settings                                      |     |

|     | 10.4.2. | TMC Motor Driver Response Datagram and Status Bits                     |     |

|     | 10.4.3. | Events and Interrupts based on Motor Driver Status Bits                |     |

|     | 10.4.4. | Stall Detection and Stop-on-Stall                                      |     |

|     | 10.5.   | TMC23x, TMC24x Stepper Motor Driver                                    |     |

|     | 10.5.1. | TMC23x Setup                                                           |     |

|     | 10.5.2. | TMC24x Setup                                                           |     |

|     | 10.5.3. | TMC23x/24x Status Bits                                                 |     |

|     | 10.5.4. | Automatic Fullstep Switchover for TMC23x/24x                           | 104 |

|     | 10.5.5. | Mixed Decay Configuration for TMC23x/24x                               |     |

|     | 10.5.6. | ChopSync Configuration for TMC23x/24x Stepper Drivers                  | 105 |

|     | 10.5.7. | Doubling ChopSync Frequency during Standstill                          | 105 |

|     | 10.5.8. | Using TMC24x stallGuard Characteristics                                | 106 |

|     | 10.6.   | TMC26x Stepper Motor Driver                                            | 107 |

|     | 10.6.1. | TMC26x Setup (SPI mode)                                                |     |

|     |         |                                                                        |     |

| 6        | /234 |

|----------|------|

| <b>U</b> | 231  |

|            | 10.6.2.                                                                                                                                                                                           | TMC26x Setup (S/D mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 107                                                                                                                                                                  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 10.6.3.                                                                                                                                                                                           | Sending Cover Datagrams to TMC26x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 108                                                                                                                                                                  |

|            | 10.6.4.                                                                                                                                                                                           | Automatic Continuous Streaming of Cover Datagrams for TMC26x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 108                                                                                                                                                                  |

|            | 10.6.5.                                                                                                                                                                                           | TMC26x SPI Mode: Automatic Fullstep Switchover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 109                                                                                                                                                                  |

|            | 10.6.6.                                                                                                                                                                                           | TMC26x S/D Mode: Automatic Fullstep Switchover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 109                                                                                                                                                                  |

|            | 10.6.7.                                                                                                                                                                                           | TMC 26x S/D Mode: Change of Current Scaling Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 110                                                                                                                                                                  |

|            | 10.6.8.                                                                                                                                                                                           | TMC26x Status Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 110                                                                                                                                                                  |

|            | 10.6.9.                                                                                                                                                                                           | TMC26x Status Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

|            | 10.7.                                                                                                                                                                                             | TMC389 Stepper Motor Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

|            | 10.8.                                                                                                                                                                                             | TMC2130 / TMC2160 Stepper Motor Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

|            | 10.8.1.                                                                                                                                                                                           | Set-up TMC21x0 Support (SPI Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

|            | 10.8.2.                                                                                                                                                                                           | Set-up TMC21x0 Support (S/D Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

|            | 10.8.3.                                                                                                                                                                                           | Sending Cover Datagrams to TMC21x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

|            | 10.8.4.                                                                                                                                                                                           | Automatic Continuous Streaming of Cover Datagrams for TMC21x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

|            | 10.8.5.                                                                                                                                                                                           | TMC21x0 SPI Mode: Automatic Fullstep Switchover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                      |

|            | 10.8.6.                                                                                                                                                                                           | TMC21x0 S/D Mode: Automatic Fullstep Switchover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                      |

|            | 10.8.7.                                                                                                                                                                                           | TMC 21x0 S/D Mode: Changing current Scaling Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

|            | 10.8.8.                                                                                                                                                                                           | TMC21x0 Status Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                      |

|            | 10.9.                                                                                                                                                                                             | Connecting Non-TMC Stepper Motor Driver or SPI-DAC at SPI output interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                      |

|            | 10.9.1.                                                                                                                                                                                           | Connecting a SPI-DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                      |

|            | 10.9.2.                                                                                                                                                                                           | DAC Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

|            | 10.9.3.                                                                                                                                                                                           | Changing SPI Output Protocol for SPI-DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

|            | 10.9.4.                                                                                                                                                                                           | DAC Address Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

|            |                                                                                                                                                                                                   | DAC Data Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                      |

|            | 10.9.5.                                                                                                                                                                                           | DAC Data Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                      |

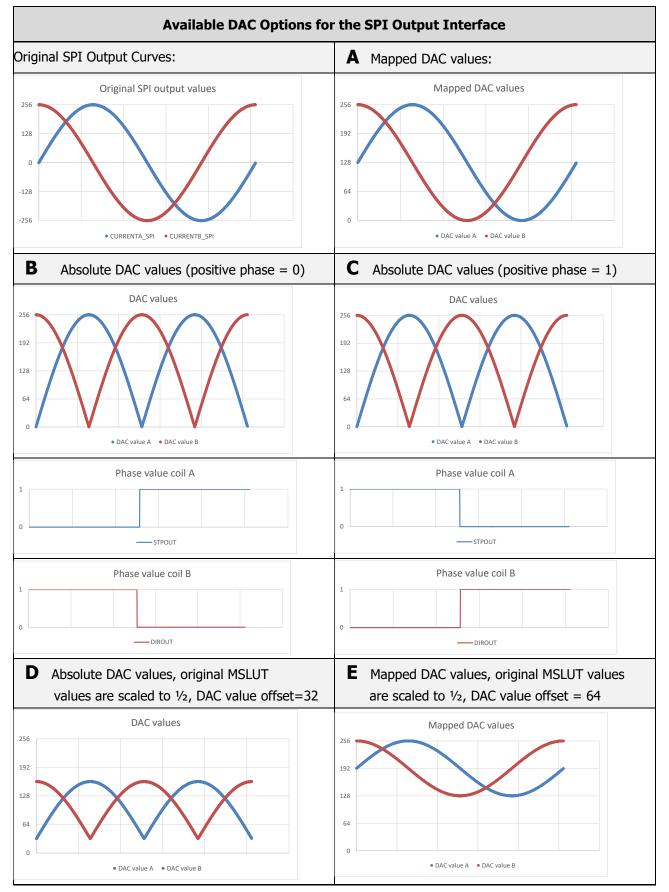

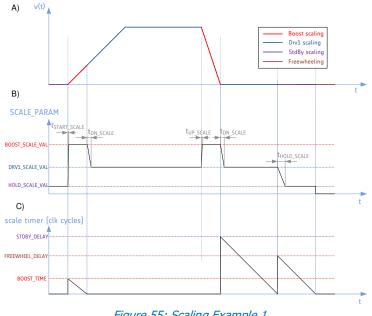

| 11.        |                                                                                                                                                                                                   | DAC Data Values<br>t Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

| 11.        |                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 120                                                                                                                                                                  |

| 11.        | <b>Curren</b><br>11.1.<br>11.2.                                                                                                                                                                   | <b>t Scaling</b><br>Hold Current Scaling<br>Freewheeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>120</b><br>121<br>121                                                                                                                                             |

| 11.        | <b>Curren</b><br>11.1.                                                                                                                                                                            | <b>t Scaling</b><br>Hold Current Scaling<br>Freewheeling<br>Current Scaling during Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>120</b><br>121<br>121<br>122                                                                                                                                      |

| 11.        | Curren<br>11.1.<br>11.2.<br>11.3.<br>11.3.1.                                                                                                                                                      | t Scaling<br>Hold Current Scaling<br>Freewheeling<br>Current Scaling during Motion<br>Drive Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>120</b><br>121<br>121<br>122<br>122                                                                                                                               |

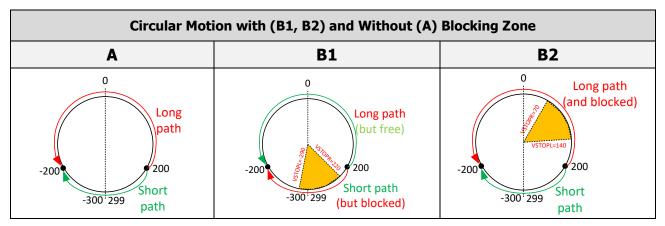

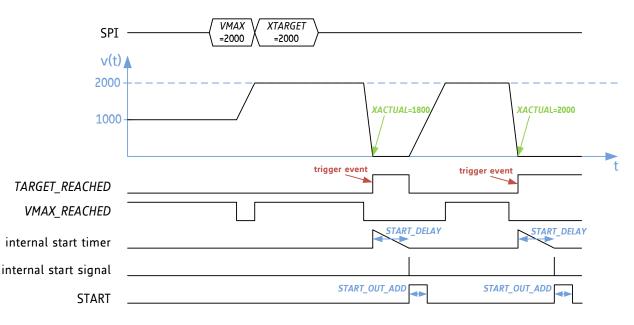

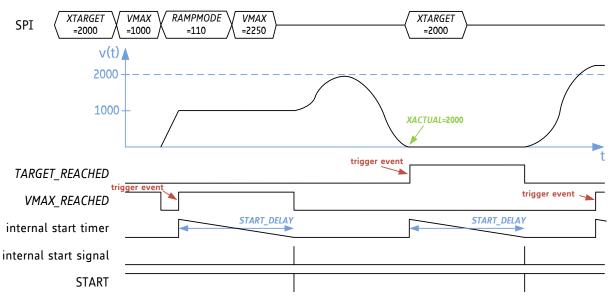

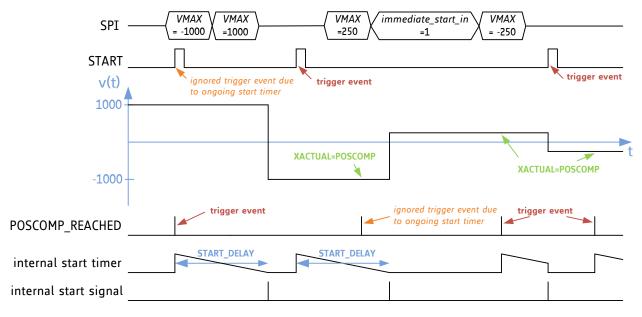

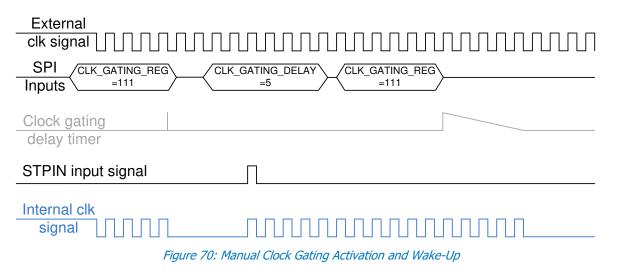

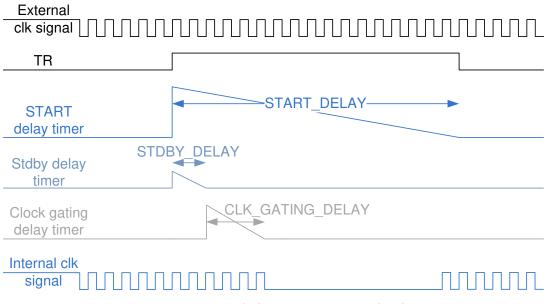

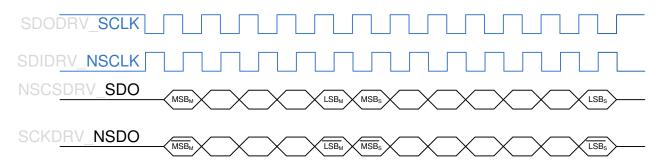

| 11.        | Curren<br>11.1.<br>11.2.<br>11.3.<br>11.3.1.<br>11.3.2.                                                                                                                                           | t Scaling<br>Hold Current Scaling<br>Freewheeling<br>Current Scaling during Motion<br>Drive Scaling<br>Alternative Drive Scaling                                                                                                                                                                                                                                                                                                                                                                                                             | 120<br>121<br>121<br>121<br>122<br>122<br>122                                                                                                                        |