# ISD61S00 ChipCorder Telephony Feature Chip Design Guide

©2008 Nuvoton Technology Corporation America all rights reserved.

#### **Important Notice**

Nuvoton products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Further more, Nuvoton products are not intended for applications wherein failure of Nuvoton products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.

Nuvoton customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nuvoton for any damages resulting from such improper use or sales.

### nuvoTon

### **Table of Contents**

| 1.  | GENERA            | AL DESCRIPTION                         | 10 |  |  |  |

|-----|-------------------|----------------------------------------|----|--|--|--|

| 2.  | FEATURES          |                                        |    |  |  |  |

| 3.  | PIN CONFIGURATION |                                        |    |  |  |  |

| 4.  | PIN DES           | CRIPTION                               | 13 |  |  |  |

| 5.  | BLOCK [           | DIAGRAM                                | 16 |  |  |  |

| 6.  | CONFIG            | URATION REGISTER MAP                   | 17 |  |  |  |

| 6.1 |                   | onfiguration Register Groups           |    |  |  |  |

| 6.2 |                   | egister Map                            |    |  |  |  |

| 7.  |                   | STATUS                                 |    |  |  |  |

| 7.1 |                   | evice Status Register                  |    |  |  |  |

| 8.  |                   | ONAL DESCRIPTION                       |    |  |  |  |

| 8.1 |                   | PI Interface                           |    |  |  |  |

| 8.2 |                   | ecord and Playback Control             |    |  |  |  |

| 0.2 | 8.2.1             | COMP_CFG – Compression Configuration   |    |  |  |  |

|     | 8.2.2             | COMP_CTRL - Compression Control        |    |  |  |  |

|     | 8.2.3             | COMP_SRC – Compression Source          |    |  |  |  |

|     | 8.2.4             | CLK CTRL – Clock Control               |    |  |  |  |

|     | 8.2.5             | CFG17 – Update Mode                    |    |  |  |  |

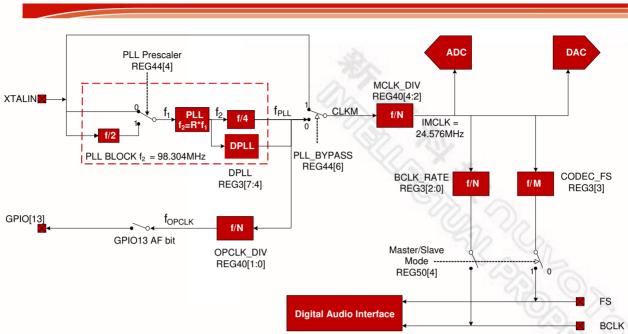

| 8.3 | С                 | lock Generation and PLL                | 40 |  |  |  |

|     | 8.3.1             | Phase Locked Loop (PLL) Design Example | 41 |  |  |  |

|     | 8.3.2             | PLL_CLK                                | 42 |  |  |  |

|     | 8.3.3             | PLL_FRAC                               | 43 |  |  |  |

|     | 8.3.4             | PLL_CTRL                               | 43 |  |  |  |

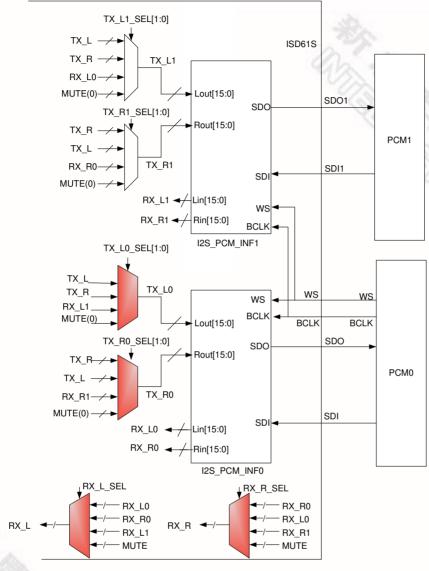

| 8.4 | D                 | igital Audio Interface Control         | 43 |  |  |  |

|     | 8.4.1             | PCM_CFG                                | 44 |  |  |  |

|     | 8.4.2             | PCM_TSLOTL                             | 45 |  |  |  |

|     | 8.4.3             | PCM_TSLOTR                             |    |  |  |  |

|     | 8.4.4             | PCM_COMP0                              |    |  |  |  |

|     | 8.4.5             | PCM_TSLOTL1                            |    |  |  |  |

|     | 8.4.6             | PCM_TSLOTR1                            |    |  |  |  |

|     | 8.4.7             | PCM_COMP1                              |    |  |  |  |

|     | 8.4.8             | PCM_TX_SEL                             |    |  |  |  |

| ٥.  | 8.4.9             | PCM_RX_SEL                             |    |  |  |  |

| 8.5 |                   | PIO and Interrupt Configuration        |    |  |  |  |

|     | 8.5.1             | PORT_UF                                |    |  |  |  |

|     | 8.5.2<br>8.5.3    | PORTx_IE                               |    |  |  |  |

|     | 8.5.3<br>8.5.4    | IE1                                    |    |  |  |  |

|     | 0.3.4             | IET                                    | 50 |  |  |  |

# nuvoTon

|      | 8.5.5   | PORTA DO                                     | 50 |

|------|---------|----------------------------------------------|----|

|      | 8.5.6   | PORTA OE                                     |    |

|      | 8.5.7   | PORTA_PE                                     |    |

|      | 8.5.8   | PORTA DI                                     |    |

|      | 8.5.9   | PORTA PS                                     |    |

|      | 8.5.10  | PORTA DS                                     |    |

|      | 8.5.11  | PORTA_AF                                     | 51 |

| 8.6  |         | 16 bit Indirect Index register R0-R7         |    |

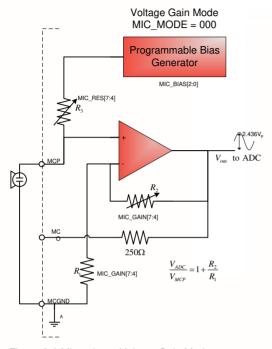

| 8.7  |         | Microphone interface and Auxiliary Interface |    |

|      | 8.7.1   | MIC_CTRL                                     |    |

|      | 8.7.2   | MIC BIAS                                     |    |

| 8.8  |         | PSTN Analog Input                            | 60 |

|      | 8.8.1   | TI GAIN                                      |    |

|      | 8.8.2   | TI_CTRL                                      | 61 |

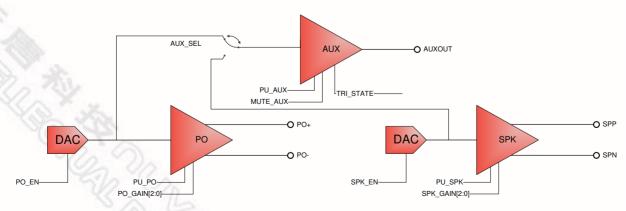

| 8.9  |         | Analog Outputs                               |    |

|      | 8.9.1   | ANA OUT                                      |    |

|      | 8.9.2   | ANA CTRL                                     |    |

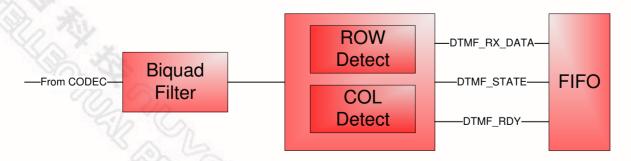

| 8.10 |         | DTMF Detection                               | 65 |

|      | 8.10.1  | DTMF CTRL                                    |    |

|      | 8.10.2  | DTMF FIFO CTRL                               |    |

|      | 8.10.3  | DTMF FIFO                                    |    |

|      | 8.10.4  | DTMF FIFO STATUS                             | 68 |

|      | 8.10.5  | DTMF THRES                                   |    |

|      | 8.10.6  | DTMF PDT                                     |    |

|      | 8.10.7  | DTMF ADT                                     | 70 |

|      | 8.10.8  | DTMF_ACCT                                    | 70 |

|      | 8.10.9  | 70                                           |    |

|      | 8.10.10 | DTMF_RX_DATA                                 | 70 |

|      | 8.10.11 | DTMF_ROW_FREQ                                | 71 |

|      | 8.10.12 | DTMF_COL_FREQ                                | 71 |

|      | 8.10.13 | Tip & Tricks                                 | 71 |

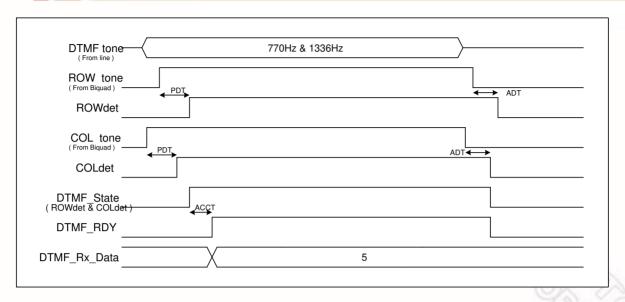

| 8.11 |         | DTMF and Arbitrary Tone Generation           | 72 |

|      | 8.11.1  | TONE_CTRL                                    | 73 |

|      | 8.11.2  | TONE_FREQ_A                                  | 73 |

|      | 8.11.3  | TONE_FREQ_B                                  | 74 |

|      | 8.11.4  | TONE_LEVEL_A                                 | 74 |

|      | 8.11.5  | TONE_LEVEL_B                                 | 74 |

|      | 8.11.6  | TONE_ON_TIME                                 | 74 |

|      | 8.11.7  | TONE_OFF_TIME                                | 75 |

|      | 8.11.8  | TONE_LENGTH                                  | 75 |

|      | 8.11.9  | 75                                           |    |

|      | 8.11.10 | TONE_INDEX_0 ~ TONE_INDEX_A                  | 76 |

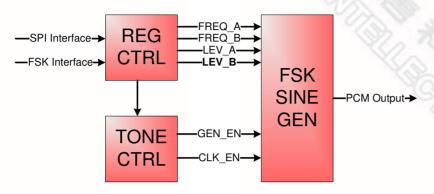

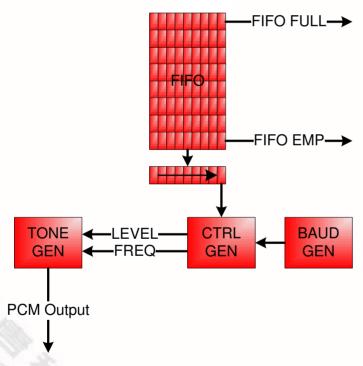

| 8.12 |         | FSK Generation                               | 76 |

|      | Q 12 1  | ESKE CTRL1                                   | 78 |

|      | 8.12.2  | FSKE CTRL2                                  | 78  |

|------|---------|---------------------------------------------|-----|

|      | 8.12.3  | FSKE TX DATA                                |     |

|      | 8.12.4  | FSKE STATUS                                 |     |

|      | 8.12.5  | FSKE_GAIN                                   |     |

|      | 8.12.6  | FSKE PROG                                   |     |

|      | 8.12.7  | FSKE BAUD (SW MODE = 1)                     | 80  |

|      | 8.12.8  | FSKE_MARK_FREQ (SW_MODE = 1)                |     |

|      | 8.12.9  | FSKE_SPACE_FREQ (SW_MODE = 1)               |     |

|      | 8.12.10 | FSKE_TEST                                   |     |

|      | 8.12.11 | 81                                          |     |

|      | 8.12.12 | Example FSK Generator Usage                 | 81  |

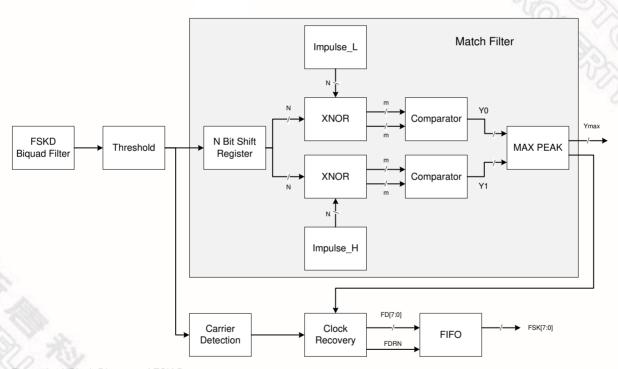

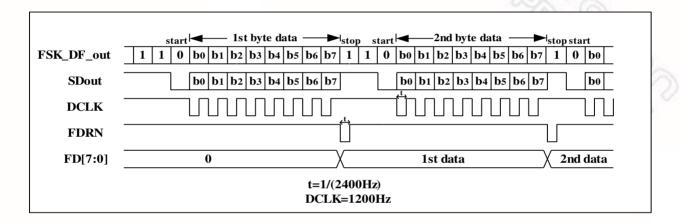

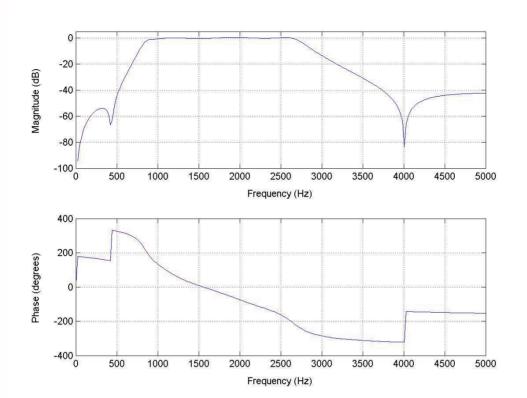

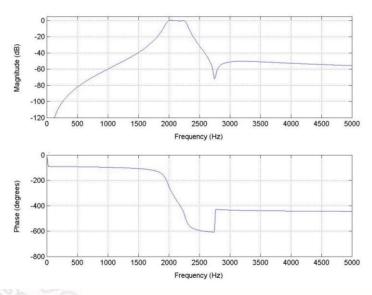

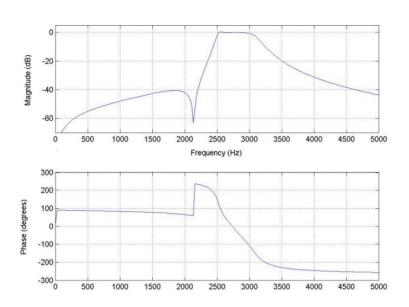

| 8.13 | FSK     | Detection                                   | 85  |

|      | 8.13.1  | FSKD CTRL                                   |     |

|      | 8.13.2  | FSKD_MODE                                   |     |

|      | 8.13.3  | FSKD ADJUST                                 |     |

|      | 8.13.4  | FSKD_STATUS                                 | 89  |

|      | 8.13.5  | FSKD THRES                                  | 89  |

|      | 8.13.6  | FSKD JUDGE                                  | 90  |

|      | 8.13.7  | FSKD_SYNC                                   | 90  |

|      | 8.13.8  | FSKD_CDET                                   | 90  |

|      | 8.13.9  | FSKD_FIFO_CTRL                              | 91  |

|      | 8.13.10 | FSKD_FIFO_DOUT                              | 92  |

|      | 8.13.11 | FSKD_FIFO_STATUS                            | 92  |

|      | 8.13.12 | FSKD_ENERGY_HIGH_TH                         | 92  |

|      | 8.13.13 | FSKD_ENERGY_LOW_TH                          | 93  |

|      | 8.13.14 | FSKD_ENERGY_TC                              | 93  |

|      | 8.13.15 | 93                                          |     |

|      | 8.13.16 | FSKD_CDB_FREQ_LOW_CNT                       | 93  |

|      | 8.13.17 | FSKD_CDB_FREQ_HIGH_CNT                      | 94  |

|      | 8.13.18 | FSKD_LIMIT_TH                               | 94  |

|      | 8.13.19 | Example FSK Detector Usage                  | 95  |

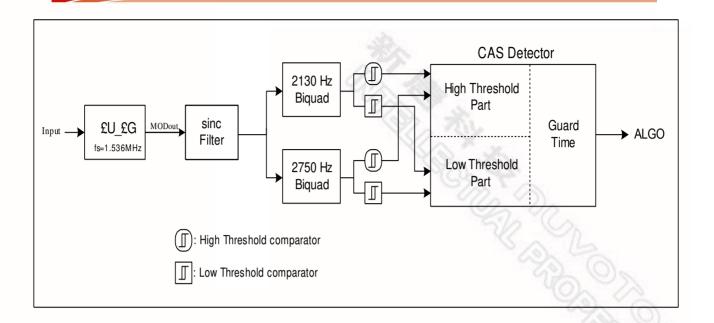

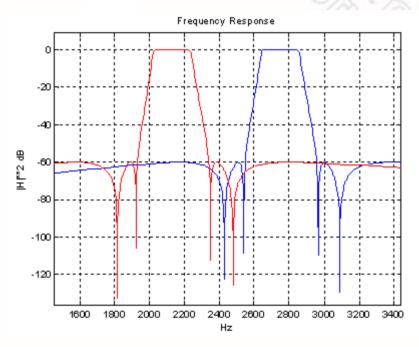

| 8.14 | CAS     | and Arbitrary Tone (ATD) Detector           | 99  |

|      | 8.14.1  | CAS_CTRL                                    | 101 |

|      | 8.14.2  | CAS_THRES_LOW - CAS detector low threshold  |     |

|      | 8.14.3  | CAS_MULT                                    | 102 |

|      | 8.14.4  | CAS_PRESENT                                 | 103 |

|      | 8.14.5  | CAS_ABSENT                                  | 104 |

|      | 8.14.6  | CAS_STATUS                                  | 104 |

|      | 8.14.7  | CAS_MODE - Arbitrary Tone Detection Mode    | 104 |

|      | 8.14.8  | ATD_MAX_HFC (ATD_MODE = 1)                  | 105 |

|      | 8.14.9  | ATD_MIN_HFC (ATD_MODE = 1)                  | 105 |

|      | 8.14.10 | ATD_MAX_LFC (ATD_MODE = 1)                  | 106 |

|      | 8.14.11 | ATD_MIN_LFC (ATD_MODE = 1)                  | 106 |

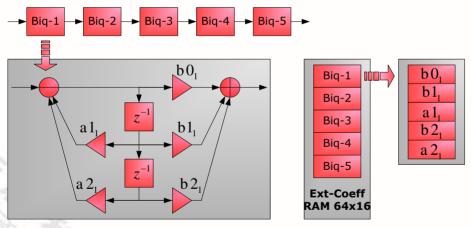

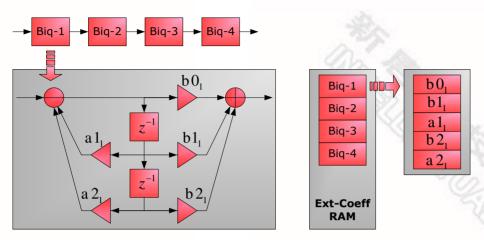

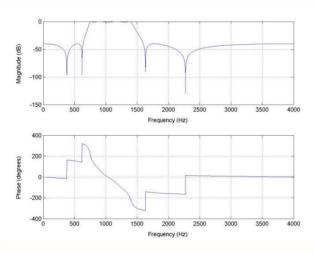

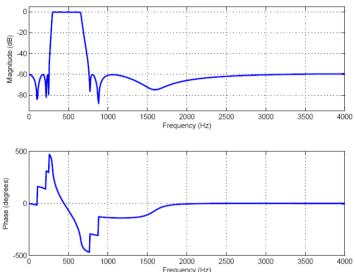

|      | 8 14 12 | External Dual-IIR Coefficient (ATD_MODE= 1) | 106 |

|      | 8.14.13 | FSK_COEFF - FSK Encoder Coefficient RAM Data         | 107 |

|------|---------|------------------------------------------------------|-----|

|      | 8.14.14 | FSK_COEFF_ADDR - FSK Encoder Coefficient RAM Address |     |

|      | 8.14.15 | CAS_MAX_HFC (FINE_TUNE = 1)                          |     |

|      | 8.14.16 | CAS_MIN_HFC (FINE_TUNE = 1)                          |     |

|      | 8.14.17 | CAS_MAX_LFC (FINE_TUNE = 1)                          |     |

|      | 8.14.18 | CAS_MIN_LFC (FINE_TUNE = 1)                          |     |

|      | 8.14.19 | 110                                                  |     |

|      | 8.14.20 | 110                                                  |     |

|      | 8.14.21 | Arbitrary Tone Detector Example                      | 110 |

| 8.15 |         | ice Energy Detection (Speech Energy Detection)       |     |

|      | 8.15.1  | VD_CTRL                                              |     |

|      | 8.15.2  | VD STATUS                                            |     |

|      | 8.15.3  | VD_THRES                                             |     |

|      | 8.15.4  | VD ENERGY                                            |     |

| 8.16 | Cal     | Il Progress Tone Detector                            |     |

|      | 8.16.1  | CPT CTRL                                             |     |

|      | 8.16.2  | CPT STATUS                                           |     |

|      | 8.16.3  | CPT THRES H                                          |     |

|      | 8.16.4  | CPT THRES L                                          |     |

|      | 8.16.5  | CPT ENERGY                                           |     |

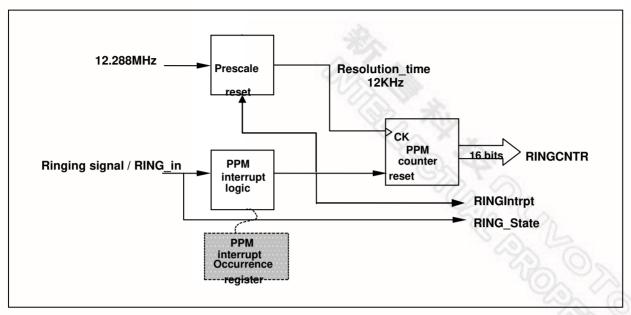

| 8.17 | Rin     | g Detection and Pulse / Period Width Measurement     |     |

|      | 8.17.1  | RNG CTRL                                             |     |

|      | 8.17.2  | RNG STATE                                            |     |

|      | 8.17.3  | RNG CNTR                                             |     |

|      | 8.17.4  | RNG LATCH                                            | 123 |

|      | 8.17.5  | 123                                                  |     |

| 8.18 | Tim     | ner                                                  | 123 |

|      | 8.18.1  | 123                                                  |     |

|      | 8.18.2  | TIME_TARG                                            | 124 |

|      | 8.18.3  | TIME_CNT                                             | 124 |

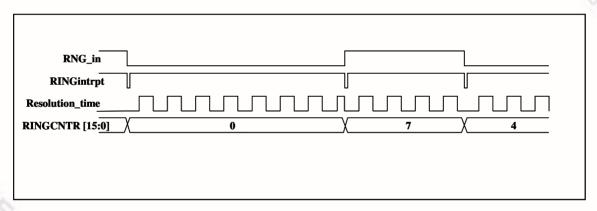

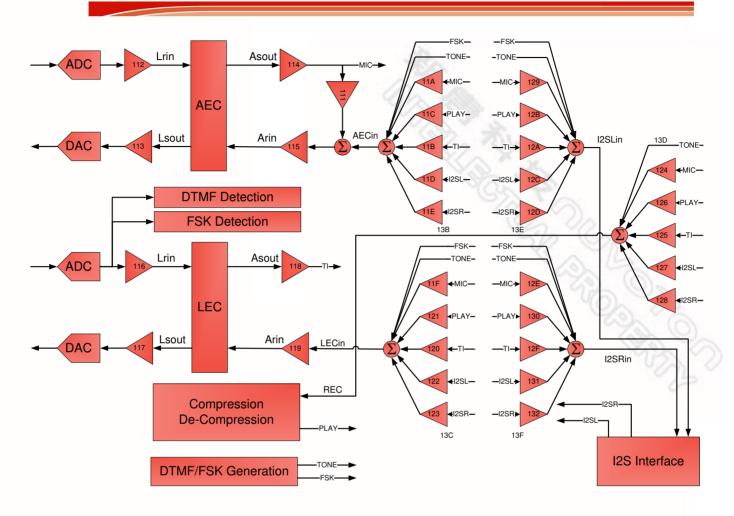

| 8.19 | Ga      | in Stage and Mixer                                   | 124 |

|      | 8.19.1  | GS_CTRL                                              | 128 |

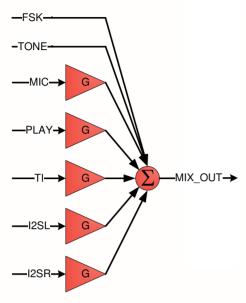

|      | 8.19.2  | CODEC EC Gain Stages                                 | 129 |

|      | 8.19.3  | AECin Path Mixing Gain Control                       |     |

|      | 8.19.4  | LECin Path Mixing Gain Control                       | 130 |

|      | 8.19.5  | REC Path Mixing Gain Control Registers               | 131 |

|      | 8.19.6  | I2SLin Path Mixing Gain Control Registers            | 132 |

|      | 8.19.7  | I2SRin Path Mixing Gain Control Registers            | 132 |

|      | 8.19.8  | Mixer Source Enable Registers                        | 133 |

| 8.20 | Air     | and Line CODEC                                       | 133 |

|      | 8.20.1  | AC_EN, LC_EN – Air /Line CODEC Enable Register       | 134 |

|      | 8.20.2  | AC_CTRL, LC_CTRL - Air /Line CODEC Dither Control    | 135 |

|      | 8.20.3  | AC_ADCG, LC_ADCG - Air/Line CODEC ADC Gain           | 135 |

|      | 8.20.4  | AC_DACG, LC_DACG - Air/Line CODEC DAC Gain           | 135 |

|      | 8.20.5 | 136                                    |     |

|------|--------|----------------------------------------|-----|

|      | 8.20.6 | 136                                    |     |

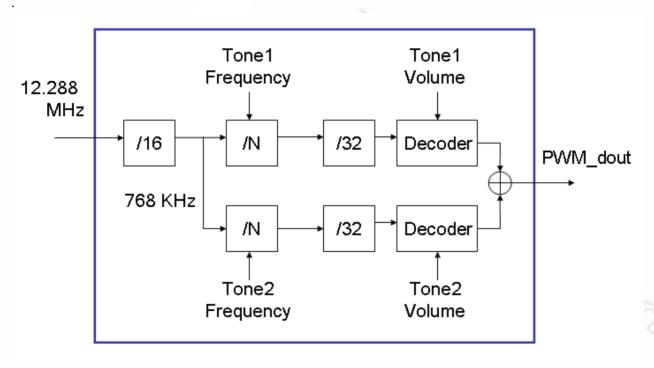

| 8.21 |        | RINGER TONE GENERATOR                  |     |

|      | 8.21.1 | PWM Clock                              | 137 |

|      | 8.21.2 |                                        |     |

|      | 8.21.3 | (102)                                  |     |

|      | 8.21.4 |                                        |     |

|      | 8.21.5 | PWM Tone2 Frequency                    | 139 |

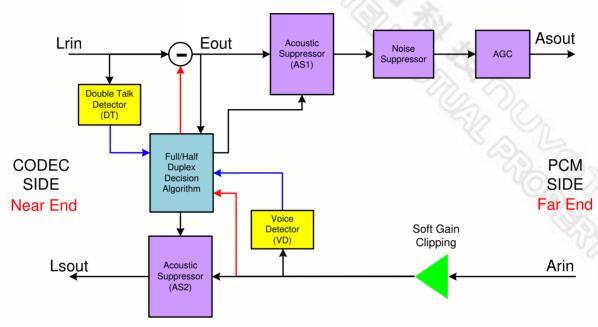

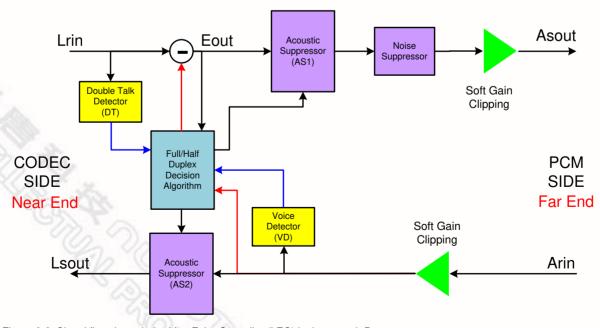

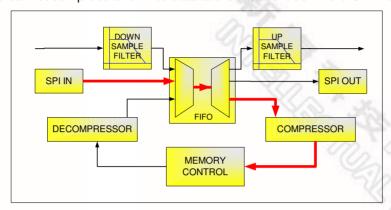

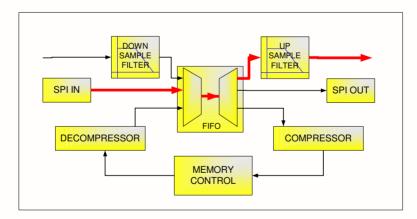

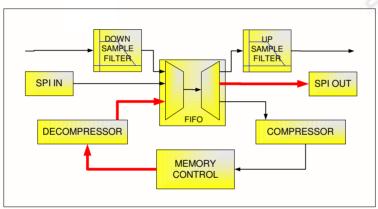

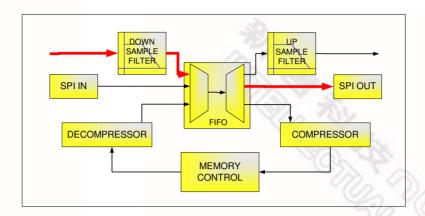

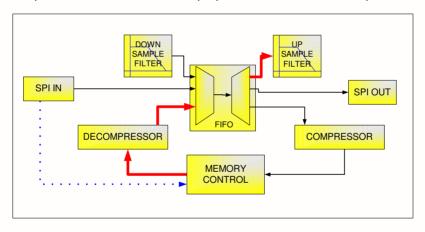

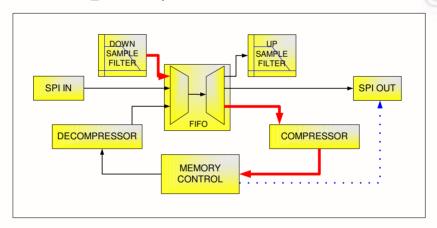

| 9.   | ACOL   | JSTIC PROCESSING BLOCK                 | 139 |

| 9.1  |        | Full/Half AEC Block Diagram            | 139 |

| 9.2  |        | Control Register Memory Map            | 141 |

|      | 9.2.1  | Threshold and Power Calculation        | 145 |

| 9.3  |        | Control Registers                      | 145 |

|      | 9.3.1  | CONFIG                                 |     |

|      | 9.3.2  | RESET                                  | 146 |

|      | 9.3.3  | EC_BELTA                               | 147 |

|      | 9.3.4  | AS_COEFF                               | 148 |

| 9.4  |        | Double Talk Detector Control Registers | 148 |

|      | 9.4.1  | Function                               | 149 |

|      | 9.4.2  | DT_LONG_TC                             | 149 |

|      | 9.4.3  | DT_SHORT_TC                            | 149 |

|      | 9.4.4  | Double Talk Detector Parameters        | 150 |

|      | 9.4.5  | DIVERGENCE                             | 150 |

| 9.5  |        | Voice Detector Control Registers       | 151 |

|      | 9.5.1  | Function                               | 151 |

|      | 9.5.2  | VD_LONG_TC                             | 151 |

|      | 9.5.3  | VD_SHORT_TC                            | 151 |

|      | 9.5.4  | Voice Detector Parameters              | 151 |

|      | VD_A\  | /E_TC 152                              |     |

|      | 9.5.5  | VD_AVE_THRESH                          | 153 |

| 9.6  |        | AS1 & AS2 Control Registers            | 153 |

|      | 9.6.1  | Function                               | 153 |

|      | 9.6.2  | AS1_BUILD_UP_TIME                      | 153 |

|      | 9.6.3  | AS1_MAX_ATTEN                          | 153 |

|      | 9.6.4  | AS2_BUILD_UP_TIME                      | 154 |

|      | 9.6.5  | AS2_MAX_ATTEN                          | 154 |

| 9.7  |        | Noise Suppressor Registers             | 154 |

|      | 9.7.1  | Function                               | 154 |

|      | 9.7.2  | NS_POWER_ATTACK_TC                     | 155 |

|      | 9.7.3  | NS_ATTEN _TC                           | 155 |

|      | 9.7.4  | NS_ACTIVE_THRESHOLD                    | 155 |

| 9.8  |        | 155                                    |     |

| 99   |        | Soft Clin (SC) Control Registers       | 156 |

# nuvoTon

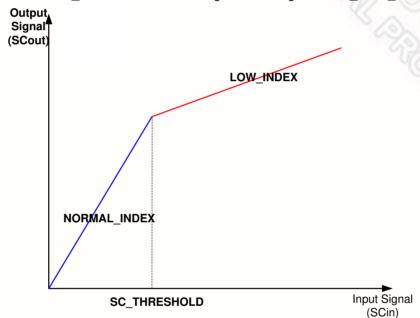

|      | 9.9.1   | Functional Description                                         | 156 |

|------|---------|----------------------------------------------------------------|-----|

|      | 9.9.2   | SC_CTRL                                                        | 156 |

|      | 9.9.3   | SC_NORMAL_INDEX                                                | 157 |

|      | 9.9.4   | SC_LOW_INDEX                                                   |     |

|      | 9.9.5   | SC_THRESH                                                      | 158 |

|      | 9.9.6   | SC_POWER_ATTACK_TC                                             | 158 |

|      | 9.9.7   | SC_GAIN_TC                                                     | 159 |

| 9.10 | Sta     | ate Read back Registers                                        |     |

|      | 9.10.1  | Functional Description                                         |     |

|      | 9.10.2  | Power Monitor                                                  | 159 |

|      | 9.10.3  | Signal Monitor                                                 | 160 |

| 9.11 | 160     |                                                                |     |

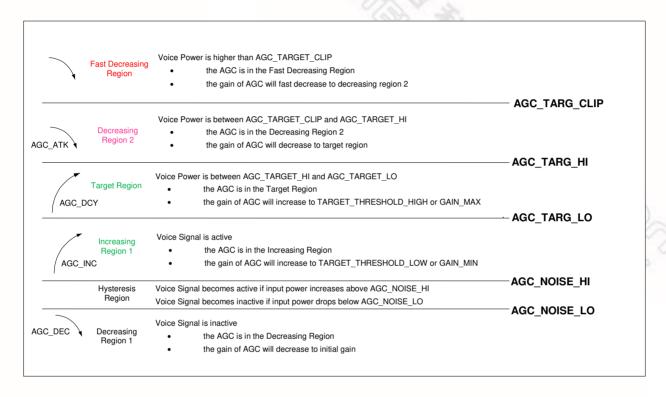

| 9.12 | Au      | tomatic Gain Control                                           | 161 |

|      | 9.12.1  | AGC_CTRL                                                       |     |

|      | 9.12.2  | AGC INIT GAIN                                                  |     |

|      | 9.12.3  | AGC GAIN HOLD                                                  |     |

|      | 9.12.4  | AGC INC DEC                                                    |     |

|      | 9.12.5  | AGC ATK DCY                                                    |     |

|      | 9.12.6  | AGC_GAIN_READ                                                  |     |

|      | 9.12.7  | AGC STATE                                                      |     |

|      | 9.12.8  | AGC PWR TC                                                     |     |

|      | 9.12.9  | AGC PK TC                                                      |     |

|      | 9.12.10 | AGC PK                                                         |     |

|      | 9.12.11 | AGC TARGETS                                                    |     |

|      | 9.12.12 | AGC NOISE PARAMETERS                                           |     |

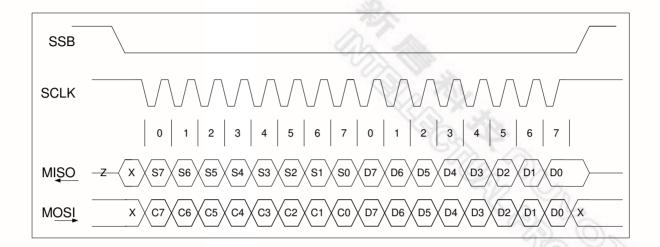

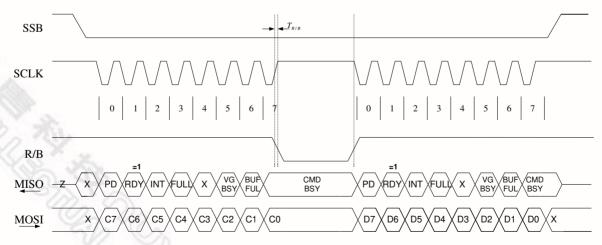

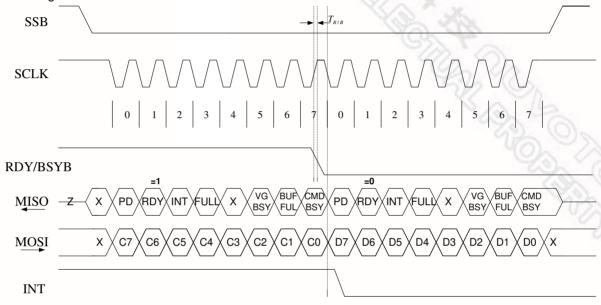

| 10.  | SPI COM | MANDS                                                          |     |

| 10.1 |         | dio Play and Record Commands                                   |     |

|      | 10.1.1  | Play Voice Prompt                                              |     |

|      | 10.1.2  | Play Voice Prompt @Rn, n = 0 ~ 7                               |     |

|      | 10.1.3  | Play Voice Prompt, Loop                                        |     |

|      | 10.1.4  | Play Voice Prompt, Loop, @Rn, n = 0 ~ 7                        |     |

|      | 10.1.5  | Stop Loop-Play Command                                         |     |

|      | 10.1.6  | Execute Voice Macro                                            |     |

|      | 10.1.7  | Execute Voice Macro @Rn, n = 0 ~ 7                             |     |

|      | 10.1.8  | Record Message                                                 |     |

|      | 10.1.9  | Record Message at Address                                      |     |

|      | 10.1.10 | Play Message at Address                                        |     |

|      | 10.1.11 | Play Silence                                                   |     |

|      | 10.1.12 | Stop Command                                                   |     |

|      | 10.1.12 | Erase Message at Address                                       |     |

|      | 10.1.14 | SPI Send Audio Data                                            |     |

|      | 10.1.15 | SPI Receive Audio Data                                         |     |

|      | 10 1 16 | SPI Send Compressed Audio Data for direct programming to flash | 179 |

|      | 10.1.17              | SPI Receive previous REC_MSG or REC_MSG@ compress | ed Audio Data stored in flash |

|------|----------------------|---------------------------------------------------|-------------------------------|

|      | 10.1.18              | SPI Send Compressed Data to Decode                | 181                           |

|      | 10.1.19              | SPI Receive Encoded Data                          |                               |

| 10.2 | De                   | evice Status Commands                             |                               |

|      | 10.2.1               | Read Status                                       |                               |

|      | 10.2.2               | Read Interrupt                                    | 183                           |

|      | 10.2.3               | Read Recorded Message Address Details             | 183                           |

|      | 10.2.4               | Read Message Length                               | 184                           |

|      | 10.2.5               | Read ISD61S00 ID                                  |                               |

| 10.3 | Dig                  | gital Memory Commands                             | 185                           |

|      | 10.3.1               | Digital Read                                      | 185                           |

|      | 10.3.2               | Digital Write                                     | 185                           |

|      | 10.3.3               | Erase Memory                                      | 186                           |

|      | 10.3.4               | Chip Erase                                        | 186                           |

|      | 10.3.5               | CHECKSUM                                          | 187                           |

| 10.4 | De                   | evice Configuration Commands                      | 187                           |

|      | 10.4.1               | PWR_UP – Power up                                 | 188                           |

|      | 10.4.2               | PWR_DN – Power Down                               | 188                           |

|      | 10.4.3               | WR_CFG_REG – Write Configuration Register         |                               |

|      | 10.4.4               | RD_CFG_REG - Read Configuration Register          |                               |

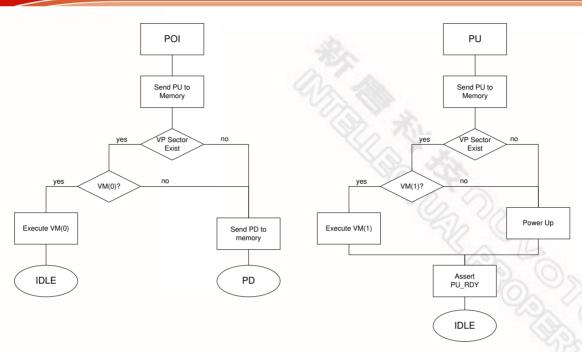

| 10.5 | De                   | evice Power Up Sequence                           | 189                           |

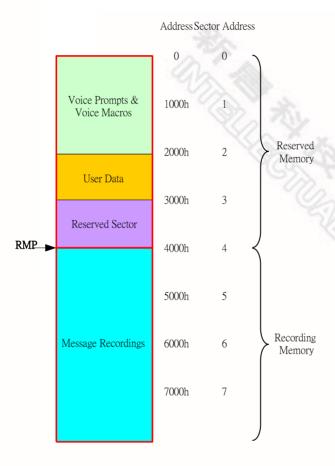

| 11.  | ISD61S00             | ) MEMORY MANAGEMENT                               | 189                           |

| 11.1 | ISI                  | D61S00 Memory Format                              | 189                           |

| 11.2 | Me                   | essage Management                                 | 190                           |

|      | 11.2.1               | Voice Prompts                                     | 191                           |

|      | 11.2.2               | Voice Macros                                      | 191                           |

|      | 11.2.3               | User Data                                         | 192                           |

|      | 11.2.4               | Reserved Sectors                                  | 192                           |

|      | 11.2.5               | Message Recordings                                | 192                           |

| 11.3 | Me                   | emory and Message Headers                         | 193                           |

|      | 11.3.1               | Memory Header                                     | 193                           |

|      | 11.3.2               | Message Header                                    |                               |

| 11.4 | 271.1.1              | gital Access of Memory                            |                               |

| 11.5 | De                   | evice Erase Commands                              | 195                           |

| 11.6 | Me                   | emory Contents Protection                         | 195                           |

| 12.  | DEVICE I             | NITIALIZATION                                     | 195                           |

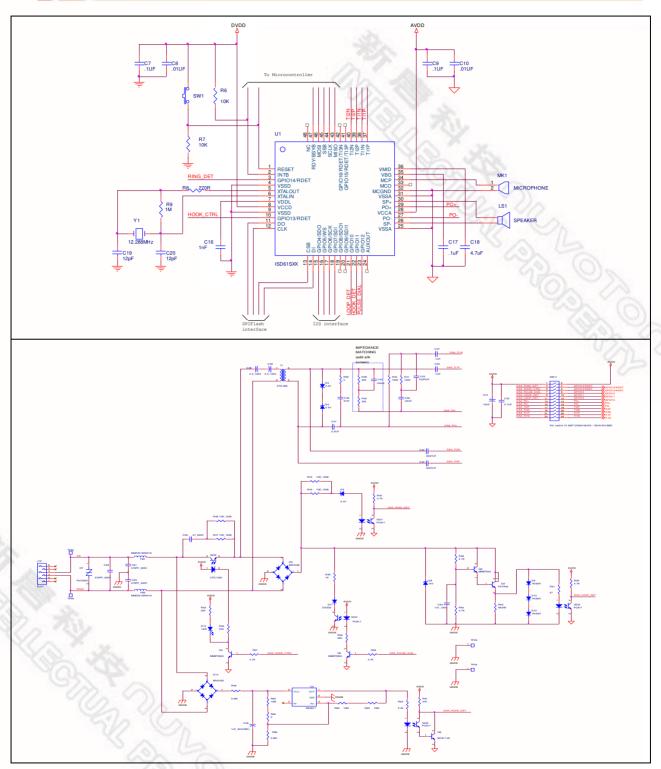

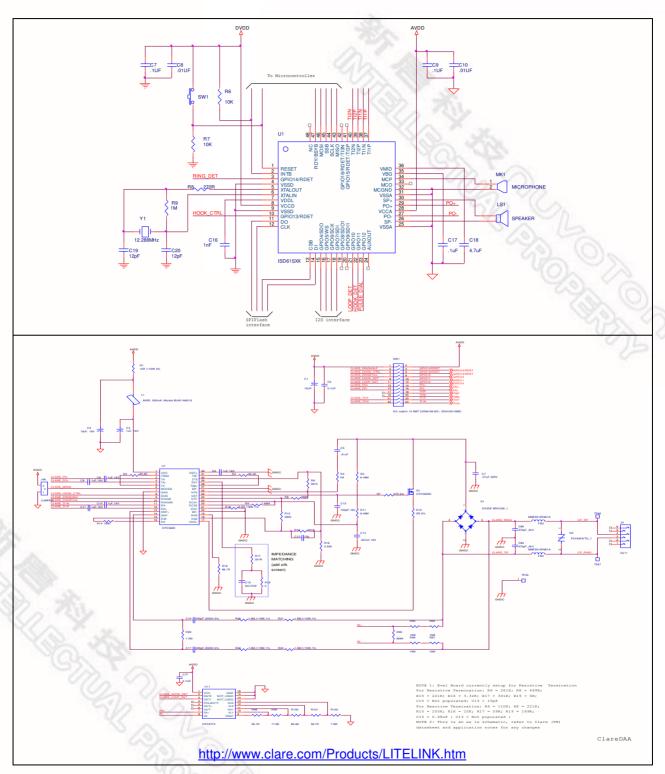

| 13.  | APPLICA <sup>*</sup> | TION REFERENCE SCHEMATICS                         | 196                           |

| 13.1 | PC                   | CB Layout Guidelines                              | 196                           |

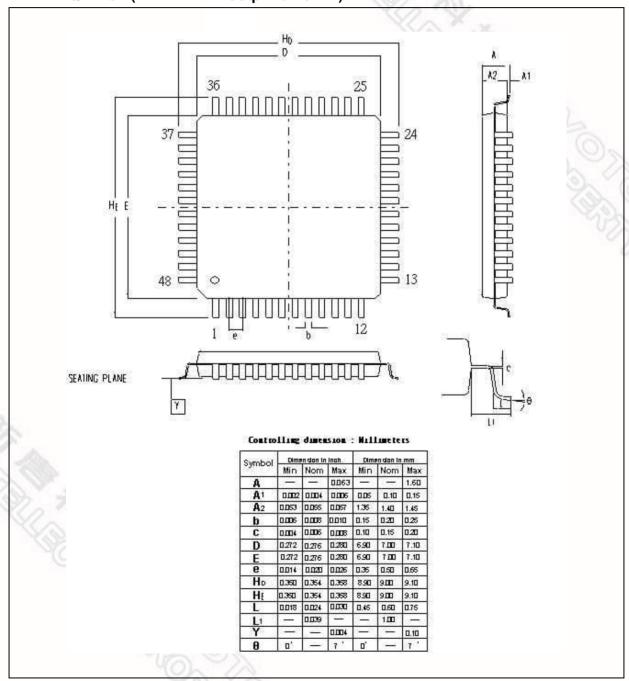

| 14.  | PACKAGI              | E SPECIFICATION                                   | 199                           |

| 14.1 | LC                   | QFP48L (7x7x1.4mm footprint 2.0mm)                | 199                           |

| 15.  |                      | CAL CHARACTERISTICS                               |                               |

| 15 1 |                      | scalute Maximum Detings                           | 200                           |

| 15.2  |        | Operating Conditions                                                     | 200 |

|-------|--------|--------------------------------------------------------------------------|-----|

| 15.3  |        | DC Parameters                                                            | 201 |

| 15.4  |        | Analog Transmission Characteristics                                      | 202 |

| 15.5  |        | Analog Distortion and Noise Parameters                                   | 202 |

|       | 15.5.1 | 8kHz sampling                                                            |     |

|       | 15.5.2 | 16kHz sampling                                                           | 203 |

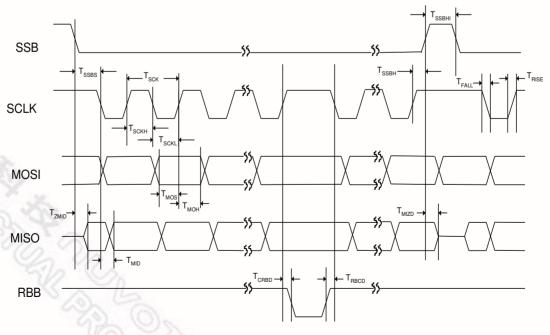

| 15.6  |        | SPI Timing                                                               | 203 |

| 15.7  |        | Recommended Clock/Crystal Specification                                  | 204 |

| 15.8  |        | Dual Tone Alert Signal (CAS)                                             | 205 |

| 15.9  |        | FSK Detection – 1200baud Bell 202, ITU V.23, 300 baud Bell 103, ITU V.21 | 206 |

| 15.10 |        | FSK Transmitter – Bell 202, ITU-V.23, Bell 103, ITU-V.21                 | 208 |

| 15.11 |        | DTMF Detection                                                           | 209 |

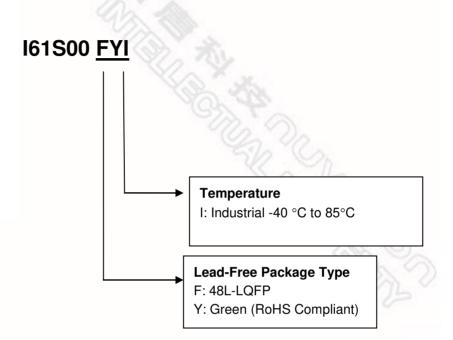

| 16.   | ORDE   | RING INFORMATION                                                         | 210 |

| 17.   | REVIS  | SION HISTORY                                                             | 211 |

#### 1. GENERAL DESCRIPTION

The ISD61S00 is a feature chip for the security and telephony industry. The device incorporates audio storage with a powerful macro scripting ability to facilitate audio prompting in a multi-language environment and simple address-free recording and playback. It utilizes external serial flash memory for audio data storage. In addition, the device includes circuitry to perform telephony based data communications including DTMF detection and generation, FSK modem functions from 75-1200 baud, CAS and CPT (Call Progress Tone) detection and ring detection. The audio path of the device is designed to interface to both the air side and line side of a PSTN system. The air side includes a flexible microphone interface incorporating a bias generator and gain control and a differential analog output for driving a speaker or power amplifier. The line side incorporates a line driver to drive PSTN loads and two variable gain differential inputs. The audio path includes full and half-duplex acoustic and line echo cancellation to implement full and half-duplex speakerphone functions. The digital audio interface can be configured to I<sup>2</sup>S or PCM mode for digital serial audio communication. Control, monitoring and device programming is performed via a SPI interface. The device package is LQFP-48L.

#### 2. FEATURES

- External Memory:

- o The ISD61S00 supports the following flash:

| Manufacturer | Winbond  |          | Numonyx  |          |          | MXIC      |

|--------------|----------|----------|----------|----------|----------|-----------|

| Family       | 25X      | 25Q      | 25P      | 25PX     | 25PE     | 25L / 25V |

| JEDEC ID     | EF 30 1X | EF 40 1X | 20 20 1X | 20 71 1X | 20 80 1X | C2 20 1X  |

- The addressing ability of ISD61S00 is up to 128Mbit, which is 64-minute record/playback time based on 8kHz/4bit ADPCM.

- Fast pre-recording: Recording is limited by the write rate of the attached external flash.

- Operating voltage: 2.7-3.6V.

- Sampling frequency: Recording and playback sampling frequencies of 4, 5.3, 6.4, 8, 10.6, 12.8 and 16 kHz.

- Compression algorithm:

- For record and playback:

- o ADPCM compression at 2, 3, 4 or 5 bits per sample.

- μ-Law companding at 6, 7 or 8 bits per sample.

- O Differential μ-Law encoding at 6, 7 or 8 bits per sample.

- o PCM encoding at 8, 10 or 12 bits per sample.

- For pre-recorded audio playback (Voice prompts) additionally:

- Enhanced ADPCM compression at 2, 3, 4 or 5 bits per sample.

- Multi-Bit rate optimized compression. This allows best possible compression given a metric of SNR and background noise levels.

- Message Management:

- Simple address free real-time recording.

- Flexible Voice Prompt message management and Voice Macro scripting for pre-recorded messages.

- External serial flash memory interface: Support up to 128Mbit for audio and digital data storage, equivalent to 64 minutes based on 8khz 4bit ADPCM.

- Digital access to flash memory: Memory can be reserved on a 4Kbyte sector basis for use as

#### nuvoton

conventional digital memory by host.

- Telephony/Modem/Data Features at 8KHz CODEC sampling rate:

- o DTMF encoder with 20 digit dial string buffer.

- o DTMF detector.

- FSK generation at 75/110/150/300/1200 baud for Bell 103, Bell 202, V.21 or V.23 modem standards. Transmit FIFO to reduce host interaction.

- FSK detector at 75/110/150/300/1200 baud for Bell 103, Bell 202, V.21 or V.23 modem standards with receive FIFO.

- o Ring Detector.

- o Call Progress Tone (CPT) detector for detecting dial tones, busy tones etc.

- CAS detector for caller ID type I, type II implementation.

- Arbitrary dual tone generator.

- Arbitrary tone detector.

- Acoustic Echo Cancellation (AEC), Line Echo Cancellation (LEC) and Automatic Gain Control (AGC) for on-chip speakerphone support.

- Up to 17 GPIO pins accessible through the SPI interface.

- Audio Input:

- o TI1 and TI2: Differential Analog inputs for PSTN interface (on-hook and off-hook).

- o MIC+/-: Analog interface to microphone.

- Audio Output:

- PO: Differential Analog output for PSTN interface.

- SPK: Differential output buffer for speaker driver.

- I/O:

- SPI interface: MISO, MOSI, SCLK, SS for commands and digital audio data.

- 11 -

- o INT and R/B signal for signaling and flow control.

- Package: Green LQFP-48L

- Temperature: -40°C to 85°C

Publication Release Date: March 10, 2011

Revision 2.7

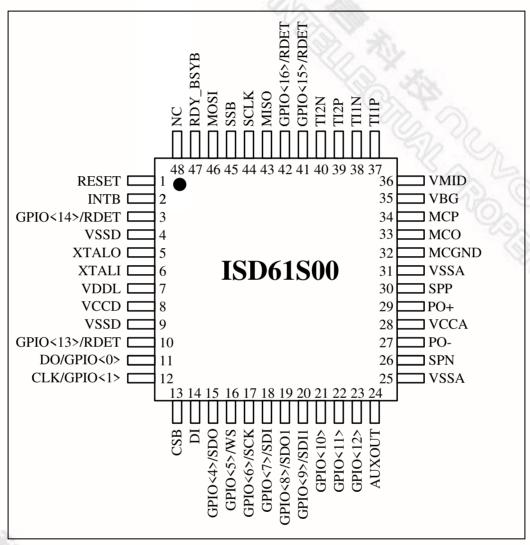

#### 3. PIN CONFIGURATION

Figure 3-1 ISD61S00 48-Lead LQFP Pin Configuration.

#### 4. PIN DESCRIPTION

| T. 1 111      | DESCRIPTION   |      |                                                                                                                     |        |

|---------------|---------------|------|---------------------------------------------------------------------------------------------------------------------|--------|

| Pin<br>Number | Pin Name      | I/O  | Function                                                                                                            | Drive  |

| 1             | RESET         | I    | Raising this pin to VCC will reset the chip.                                                                        | N/A    |

| 2             | INTB          | 0    | Active low interrupt request pin. This pin has an open drain output.                                                | 4/8mA  |

| 3             | GPIO<14>/RDET | I/O* | General Purpose IO Pin or the Ring Detect input (RDET).                                                             | 4/8mA  |

| 4             | VSSD          | G    | Digital Ground.                                                                                                     | N/A    |

| 5             | XTALOUT       | 0    | Crystal Interface output pin.                                                                                       | N/A    |

| 6             | XTALIN        | ı    | Crystal interface input pin. It can also be used to provide an external clock to the device.                        | N/A    |

| 7             | VDDL          | 0    | This pin has a nominal 1.8V output to supply the internal logic. A 2.2nF capacitor should be connected to this pin. | N/A    |

| 8             | VCCD          | Р    | Digital power supply pin                                                                                            | N/A    |

| 9             | VSSD          | G    | Digital Ground.                                                                                                     | N/A    |

| 10            | GPIO<13>/RDET | I/O* | General Purpose IO Pin.                                                                                             | 4/8mA  |

| 11            | DO/GPIO<0>    | I/O  | Flash interface data out. Alternatively General Purpose IO Pin.                                                     | 4/8mA  |

| 12            | CLK/GPIO<1>   | I/O  | Flash interface clock. Alternatively General Purpose IO Pin.                                                        | 4/8mA  |

| 13            | CSB           | 0    | Flash interface chip select bar.                                                                                    | 4/8mA  |

| 14            | DI            | I    | Flash interface data in.                                                                                            | 4/8mA  |

| 15            | GPIO<4>/SDO   | I/O* | General Purpose IO Pin. Serial Data Out for the I2S interface.                                                      | 8/16mA |

| 16            | GPIO<5>/WS    | I/O* | General Purpose IO Pin. Word Select (WS) output for the I2S Interface                                               | 8/16mA |

| 17            | GPIO<6>/SCK   | I/O* | General Purpose IO Pin. Serial Clock output for the I2S Interface                                                   | 8/16mA |

| 18            | GPIO<7>/SDI   | I/O* | General Purpose IO Pin. Serial Data Input (SDI) input pin for the I2S Interface.                                    | 8/16mA |

| 19            | GPIO<8>/SDO1  | I/O* | General Purpose IO Pin. Secondary Serial Data Out for the I2S interface.                                            | 4/8mA  |

| 20            | GPIO<9>SDI1   | I/O* | General Purpose IO Pin. Secondary Serial Data Input (SDI) input pin for the I2S Interface.                          | 4/8mA  |

# nuvoTon

| 21 | GPIO<10>      | I/O* | General Purpose IO Pin.                                                                                                          | 4/8mA |

|----|---------------|------|----------------------------------------------------------------------------------------------------------------------------------|-------|

| 22 | GPIO<11>      | I/O* | General Purpose IO Pin or the Ring Detect input (RDET).                                                                          | 4/8mA |

| 23 | GPIO<12>      | I/O* | General Purpose IO Pin.                                                                                                          | 4/8mA |

| 24 | AUXOUT        | 0    | Auxiliary output from PSTN or SPEAKER DAC.                                                                                       | N/A   |

| 25 | VSSA          | G    | Analog Ground Pin                                                                                                                | N/A   |

| 26 | SPKN          | 0    | Negative speaker driver output                                                                                                   | N/A   |

| 27 | PO-           | 0    | Negative line driver output                                                                                                      | N/A   |

| 28 | VCCA          | Р    | Analog Power Pin                                                                                                                 | N/A   |

| 29 | PO+           | 0    | Positive line driver output                                                                                                      | N/A   |

| 30 | SPKP          | 0    | Positive speaker driver output                                                                                                   | N/A   |

| 31 | VSSA          | G    | Analog Ground Pin                                                                                                                | N/A   |

| 32 | MCGND         | I    | Analog ground pin for MIC. This pin should be connected to a quiet VSSA and used as the return for microphones connected to MCP. | N/A   |

| 33 | MCO           | I/O  | MIC feedback signal                                                                                                              | N/A   |

| 34 | MCP           | I    | Positive MIC signal input.                                                                                                       | N/A   |

| 35 | VBG           | I/O  | Voltage reference, a 100nF capacitor should be connected to this pin.                                                            | N/A   |

| 36 | VMID          | I/O  | Voltage reference, a 4.7uF capacitor should be connected to this pin.                                                            | N/A   |

| 37 | TI1P          | I    | PSTN Line #1 positive input                                                                                                      | N/A   |

| 38 | TI1N          | I    | PSTN Line #1 negative input                                                                                                      | N/A   |

| 39 | TI2P          | I    | PSTN Line #2 positive input                                                                                                      | N/A   |

| 40 | TI2N          | I    | PSTN Line #2 negative input                                                                                                      | N/A   |

| 41 | GPIO<15>/RDET | I/O* | General Purpose IO Pin. Can be configured as Ring Detect (RDET) input.                                                           | 4/8mA |

| 42 | GPIO<16>/RDET | I/O* | General Purpose IO Pin. Can be configured as Ring Detect (RDET) input.                                                           | 4/8mA |

| 43 | MISO          | 0    | SPI slave serial data output from the ISD61S00 to the host. This pin is tri-stated when SSB=1.                                   | 4/8mA |

| 44 | SCLK          | I    | SPI serial Clock input to the ISD61S00 from the host.                                                                            | N/A   |

| 45 | SSB           | I    | Slave select input to the ISD61S00 from the host                                                                                 | N/A   |

| 46 | MOSI          | I    | SPI slave serial data input to the ISD61S00 from the host.                                                                       | 4/8mA |

|    |               | P    | 1                                                                                                                                |       |

| 47 | RDY/BSYB | 0 | This pin is at VCCD when the chip is ready to accept a new command/data and is at VSSD when device is busy. |  |

|----|----------|---|-------------------------------------------------------------------------------------------------------------|--|

| 48 | NC       |   | Gh -                                                                                                        |  |

<sup>\*</sup> Default state for digital I/O pins is input with internal pull-up [38Kohms to 83Kohms] to VCCD supply

Publication Release Date: March 10, 2011 Revision 2.7

- 15 -

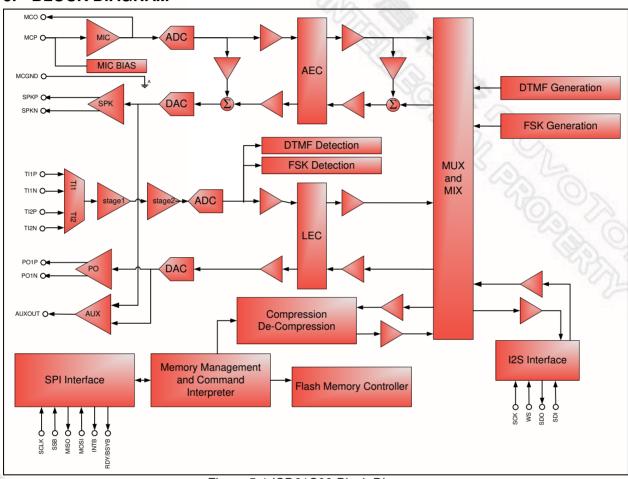

#### 5. BLOCK DIAGRAM

Figure 5-1 ISD61S00 Block Diagram

#### 6. CONFIGURATION REGISTER MAP

# 6.1 Configuration Register Groups

|                                          |  | •      |                                        |

|------------------------------------------|--|--------|----------------------------------------|

| Data memory address Size (Byte) Usage AL |  | (Byte) | Function                               |

|                                          |  | ALL    | T diletion                             |

| 0x000 ~ 0x0FF                            |  | 256    | Device Control Registers               |

| 0x110 ~ 0x13F                            |  | 32     | Gain stage and Mixer Control Registers |

| 0x140 ~ 0x14F                            |  | 16     | Air CODEC Control                      |

| 0x150 ~ 0x15F                            |  | 16     | Line CODEC Control                     |

| 0x160 ~ 0x17F                            |  | 32     | FSK Encoder Control                    |

| 0x180 ~ 0x19F                            |  | 32     | FSK Decoder Control                    |

| 0x1A0 ~ 0x1AF                            |  | 16     | Ringer Tone(PWM) Control Registers     |

| 0x1B0 ~ 0x1BF                            |  | 16     | Ring Detection PPM Control             |

| 0x1CO ~ 0x1DF                            |  | 32     | DTMF and Tone Generation               |

| 0x1E0 ~ 0x1EF                            |  | 16     | DTMF Detection Control                 |

| 0x1F0 ~ 0x1FF                            |  | 16     | Voice Energy Detection Control         |

| 0x200 ~ 0x27F                            |  | 128    | CAS Detection Control                  |

| 0x280 ~ 0x28F                            |  | 16     | CPT Detector Control                   |

| 0x290 ~ 0x29F                            |  | 16     | Timer Control                          |

| 0x300 ~ 0x3FF                            |  | 256    | AEC/LEC Control                        |

### 6.2 Register Map

| Addr. | Name     | Mode | Value<br>At<br>Reset | Function                |              |

|-------|----------|------|----------------------|-------------------------|--------------|

| 0x000 | AUD      | R/W  | 0x64                 | Compression & SR ctrl   | <u>8.2.1</u> |

| 0x001 | REG1     | R/W  | 0x00                 | Compression Control     | 8.2.2        |

| 0x002 | REG2     | R/W  | 0x00                 | Compression Source      | 8.2.3        |

| 0x003 | REG3     | R/W  | 0x03                 | Clock Control           | <u>8.2.4</u> |

| 0x004 | TI_GAIN  | R/W  | 0x00                 | Input Amplifier Gain    | <u>8.8.1</u> |

| 0x005 | TI_CTRL  | R/W  | 0x00                 | Input Amplifier Control | 8.8.2        |

| 0x006 | MIC_CTRL | R/W  | 0x00                 | MIC Interface Control   | <u>8.7.1</u> |

# nuvoTon

| Addr. | Name         | Mode | Value<br>At<br>Reset | Function                  |               |

|-------|--------------|------|----------------------|---------------------------|---------------|

| 0x007 | MIC_BIAS     | R/W  | 0x00                 | MIC Interface Bias        | 8.7.2         |

| 0x008 | ANA_OUT      | R/W  | 0x00                 | Analog Output Control     | <u>8.9.1</u>  |

| 0x009 | ANA_CTRL     | R/W  | 0x10                 | Analog Control            | 8.8.2         |

| 0x00A | ID_OVR       | R/W  | 0x00                 | Memory Control            |               |

| 0x00B | PORT_CFG     | R/W  | 0x00                 | GPIO INT Ctrl             | 8.5.1         |

| 0x00C | PORTA_IE     | R/W  | 0x00                 | Port A INT Enable         | 8.5.2         |

| 0x00D | PORTB_IE     | R/W  | 0x00                 | Port B INT Enable         | 8.5.2         |

| 0x00E | PORTC_IE     | R/W  | 0x00                 | Port C INT Enable         | 8.5.2         |

| 0x00F | DPLL Control | R/W  | 0x00                 | Digital PLL Control       | 8.5.2         |

| 0x014 | IE0          | R/W  | 0xFF                 | INT Enable 0              | 8.5.3         |

| 0x015 | IE1          | R/W  | 0xFF                 | INT Enable 1              | 8.5.4         |

| 0x017 | UPDATE_MD    | R/W  | 0x01                 | Update Ctrl               | 8.2.5         |

| 0x018 | CHK_SUM_CTRL | R/W  | 0x01                 | Check sum control         | (((           |

| 0x019 | PORTA_DO     | R/W  | 0x00                 | Port A Dout               | <u>8.5.5</u>  |

| 0x01A | PORTA_OE     | R/W  | 0x00                 | Port A Output Enable      | <u>8.5.6</u>  |

| 0x01B | PORTA_PE     | R/W  | 0xFF                 | Port A Pull Enable        | 8.5.7         |

| 0x01C | PORTA_DI     | R    | NA                   | Port A Din                | <u>8.5.8</u>  |

| 0x01D | PORTA_PS     | R/W  | 0xFF                 | Port A pull Select        | <u>8.5.9</u>  |

| 0x01E | PORTA_DS     | R/W  | 0x00                 | Port A Drive Strength     | <u>8.5.10</u> |

| 0x01F | PORTA_AF     | R/W  | 0x03                 | Port A Alternate Function | <u>8.5.11</u> |

| 0x020 | R0_LSB       | R/W  | 0x00                 | Indirect reg R0 LSB       | <u>8.6</u>    |

| 0x021 | R0           | R/W  | 0x00                 | Indirect reg R0           | 8.6           |

| 0x022 | R1_LSB       | R/W  | 0x00                 | Indirect reg R1 LSB       | <u>8.6</u>    |

| 0x023 | R1           | R/W  | 0x00                 | Indirect reg R1           | 8.6           |

| 0x024 | R2_LSB       | R/W  | 0x00                 | Indirect reg R2 LSB       | <u>8.6</u>    |

| 0x025 | R2           | R/W  | 0x00                 | Indirect reg R2           | 8.6           |

| 0x026 | R3_LSB       | R/W  | 0x00                 | Indirect reg R3 LSB       | <u>8.6</u>    |

| 0x027 | R3           | R/W  | 0x00                 | Indirect reg R3           | <u>8.6</u>    |

| 0x028 | R4_LSB       | R/W  | 0x00                 | Indirect reg R4 LSB       | 8.6           |

| 0x029 | R4           | R/W  | 0x00                 | Indirect reg R4           | 8.6           |

| 0x02A | R5_LSB       | R/W  | 0x00                 | Indirect reg R5 LSB       | <u>8.6</u>    |

| 0x02B | R5           | R/W  | 0x00                 | Indirect reg R5           | 8.6           |

| 0x02C | R6_LSB       | R/W  | 0x00                 | Indirect reg R6 LSB       | 8.6           |

| 0x02D | R6           | R/W  | 0x00                 | Indirect reg R6           | 8.6           |

# nuvoTon

| Addr. | Name            | Mode | Value<br>At<br>Reset | Function                     |               |

|-------|-----------------|------|----------------------|------------------------------|---------------|

| 0x02E | R7_LSB          | R/W  | 0x00                 | Indirect reg R7 LSB          | <u>8.6</u>    |

| 0x02F | R7              | R/W  | 0x00                 | Indirect reg R7              | <u>8.6</u>    |

| 0x030 | PORTB_DO        | R/W  | 0x00                 | Port B Dout                  | <u>8.5</u>    |

| 0x031 | PORTB_OE        | R/W  | 0x00                 | Port B Output Enable         | <u>8.5</u>    |

| 0x032 | PORTB_PE        | R/W  | 0xFF                 | Port B Pull Enable           | <u>8.5</u>    |

| 0x033 | PORTB_DI        | R    | NA                   | Port B Din                   | <u>8.5</u>    |

| 0x034 | PORTB_PS        | R/W  | 0xFF                 | Port B pull Select           | <u>8.5</u>    |

| 0x035 | PORTB_DS        | R/W  | 0x00                 | Port B Drive Strength        | <u>8.5</u>    |

| 0x036 | PORTB_AF        | R/W  | 0x00                 | Port B Alternate Function    | <u>8.5.11</u> |

| 0x037 | PORTC_DO        | R/W  | 0x00                 | Port C Dout                  | 8.5           |

| 0x038 | PORTC_OE        | R/W  | 0x00                 | Port C Output Enable         | <u>8.5</u>    |

| 0x039 | PORTC_PE        | R/W  | 0xFF                 | Port C Pull Enable           | <u>8.5</u>    |

| 0x03A | PORTC_DI        | R    | NA                   | Port C Din                   | 8.5           |

| 0x03B | PORTC_PS        | R/W  | 0xFF                 | Port C pull Select           | 8.5           |

| 0x03C | PORTC_DS        | R/W  | 0x00                 | Port C Drive Strength        | 8.5           |

| 0x03D | PORTC_AF        | R/W  | 0xFC                 | Port C Alternate Function    | 8.5           |

| 0x040 | PLL_CLK         | R/W  | 0x20                 | PLL Clock Control            | 8.3.2         |

| 0x041 | PLL_K2          | R/W  | 0x00                 | PLL Fraction MSB             | 8.3.3         |

| 0x042 | PLL_K1          | R/W  | 0x00                 | PLL Fraction byte 1          | 8.3.3         |

| 0x043 | PLL_K0          | R/W  | 0x00                 | PLL Fraction LSB             | 8.3.3         |

| 0x044 | PLL_CTRL        | R/W  | 0x88                 | PLL Control Register         | 8.3.4         |

| 0x050 | PCM_CFG         | R/W  | 0x00                 | PCM Configuration            | 8.4.1         |

| 0x051 | PCM_TSLOTL      | R/W  | 0x01                 | Left Channel PCM MSB start   | 8.4.2         |

| 0x052 | PCM_TSLOTR      | R/W  | 0x11                 | Right Channel PCM MSB start  | 8.4.3         |

| 0x053 | PCM_COMP0       | R/W  | 0x00                 | PCM0 Compression             | 8.4.4         |

| 0x054 | PCM_TSLOTL1     | R/W  | 0x01                 | Left Channel PCM1 MSB start  | 8.4.5         |

| 0x055 | PCM_TSLOTR1     | R/W  | 0x11                 | Right Channel PCM1 MSB start | 8.4.6         |

| 0x056 | PCM_COMP1       | R/W  | 0x00                 | PCM1 Compression             | 8.4.7         |

| 0x057 | PCM_TX_SEL      | R/W  | 0x00                 | PCM Transmission Select      | 8.4.8         |

| 0x058 | PCM_RX_SEL      | R/W  | 0x00                 | PCM Receive Select           | 8.4.9         |

| 0x059 | CHKSUM SUM1 LSB | R    | 0x00                 | Chksum1[7:0]                 |               |

| 0x05A | CHKSUM SUM1     | R    | 0x00                 | Chksum1[15:8]                |               |

| 0x05B | CHKSUM SUM2 LSB | R    | 0x00                 | Chksum2[7:0]                 |               |

| 0x05C | CHKSUM SUM2     | R    | 0x00                 | Chksum2[15:8]                |               |

# nuvoTon

| Addr. | Name            | Mode | Value<br>At<br>Reset | Function                         |   |

|-------|-----------------|------|----------------------|----------------------------------|---|

| 0x05D | REC_MSG_LEN LSB | R/W  | 0x00                 | REC Message Sector Length [7:0]  |   |

| 0x05E | REC_MSG_LEN     | R/W  | 0x00                 | REC Message Sector Length [15:8] |   |

| 0x110 | GS_CTRL         | R/W  | 0x00                 | GS Control                       |   |

| 0x111 | GS_ACST         | R/W  | 0x40                 | Air CODEC Side tone              |   |

| 0x112 | GS_ACIG         | R/W  | 0x00                 | Air CODEC input Gain             |   |

| 0x113 | GS_ACOG         | R/W  | 0x00                 | Air CODEC output Gain            |   |

| 0x114 | GS_AEOG         | R/W  | 0x00                 | AEC Output Gain                  |   |

| 0x115 | GS_AEIG         | R/W  | 0x00                 | AEC Input Gain                   |   |

| 0x116 | GS_LCIG         | R/W  | 0x00                 | Line CODEC input Gain            |   |

| 0x117 | GS_LCOG         | R/W  | 0x00                 | Line CODEC output Gain           |   |

| 0x118 | GS_LEOG         | R/W  | 0x00                 | LEC Output Gain                  |   |

| 0x119 | GS_LEIG         | R/W  | 0x00                 | LEC Input Gain                   |   |

| 0x11A | GS_AOAI         | R/W  | 0x00                 | AEC out - AEC in Gain            | ) |

| 0x11B | GS_LOAI         | R/W  | 0x00                 | LEC out - AEC in Gain            |   |

| 0x11C | GS_PLAI         | R/W  | 0x00                 | PLAY - AEC in Gain               |   |

| 0x11D | GS_ILAI         | R/W  | 0x00                 | I2SL - AEC in                    |   |

| 0x11E | GS_IRAI         | R/W  | 0x00                 | I2SR - AEC in                    |   |

| 0x11F | GS_AOLI         | R/W  | 0x00                 | AEC out - LEC in Gain            |   |

| 0x120 | GS_LOLI         | R/W  | 0x00                 | LEC out - LEC in Gain            |   |

| 0x121 | GS_PLLI         | R/W  | 0x00                 | PLAY - LEC in Gain               |   |

| 0x122 | GS_ILLI         | R/W  | 0x00                 | I2SL - LEC in                    |   |

| 0x123 | GS_IRLI         | R/W  | 0x00                 | I2SR - LEC in                    |   |

| 0x124 | GS_AORI         | R/W  | 0x00                 | AEC out - REC in Gain            |   |

| 0x125 | GS_LORI         | R/W  | 0x00                 | LEC out - REC in Gain            |   |

| 0x126 | GS_PLRI         | R/W  | 0x00                 | PLAY - REC in Gain               |   |

| 0x127 | GS_ILRI         | R/W  | 0x00                 | I2SL - REC in                    |   |

| 0x128 | GS_IRRI         | R/W  | 0x00                 | I2SR - REC in                    |   |

| 0x129 | GS_AOIL         | R/W  | 0x00                 | AEC out - I2SL in Gain           |   |

| 0x12A | GS_LOIL         | R/W  | 0x00                 | LEC out - I2SL in Gain           |   |

| 0x12B | GS_PLIL         | R/W  | 0x00                 | PLAY - I2SL in Gain              |   |

| 0x12C | GS_ILIL         | R/W  | 0x00                 | 12SL - 12SL in                   |   |

| 0x12D | GS_IRIL         | R/W  | 0x00                 | I2SR - I2SL in                   |   |

| 0x12E | GS_AOIR         | R/W  | 0x00                 | AEC out - I2SR in Gain           |   |

| 0x12F | GS_LOIR         | R/W  | 0x00                 | LEC out - I2SR in Gain           | - |

# nuvoTon

| Addr. | Name         | Mode | Value<br>At<br>Reset | Function            |        |

|-------|--------------|------|----------------------|---------------------|--------|

| 0x130 | GS_PLIR      | R/W  | 0x00                 | PLAY - I2SR in Gain |        |

| 0x131 | GS_ILIR      | R/W  | 0x00                 | I2SL - I2SR in      |        |

| 0x132 | GS_IRIR      | R/W  | 0x00                 | I2SR - I2SR in      |        |

| 0x13B | MX_AEC       | R/W  | 0x00                 | AEC Mix Ctrl        |        |

| 0x13C | MX_LEC       | R/W  | 0x00                 | LEC Mix Ctrl        |        |

| 0x13D | MX_REC       | R/W  | 0x00                 | REC Mix Ctrl        |        |

| 0x13E | MX_ISL       | R/W  | 0x00                 | I2S_L Mix Ctrl      |        |

| 0x13F | MX_ISR       | R/W  | 0x00                 | I2S_R Mix Ctrl      |        |

| 0x140 | AC_EN        | R/W  | 0x20                 | Air CODEC Enable    |        |

| 0x141 | AC_CTRL      | R/W  | 0x07                 | Air CODEC Control   |        |

| 0x142 | AC_ADCG_MSB  | R/W  | 0x04                 | Air ADC Gain MSB    |        |

| 0x143 | AC_ADCG_LSB  | R/W  | 0x00                 | Air ADC Gain LSB    | )      |

| 0x144 | AC_DACG_MSB  | R/W  | 0x04                 | Air DAC Gain MSB    | (0)    |

| 0x145 | AC_DACG_LSB  | R/W  | 0x00                 | Air DAC Gain LSB    |        |

| 0x146 | AC_ADOUT_MSB | R    | NA                   | Air ADC Output MSB  |        |

| 0x147 | AC_ADOUT_LSB | R    | NA                   | Air ADC Output LSB  |        |

| 0x148 | AC_DAOUT_MSB | R    | NA                   | Air DAC Output MSB  |        |

| 0x149 | AC_DAOUT_LSB | R    | NA                   | Air DAC Output MSB  |        |

|       |              |      |                      |                     |        |

| 0x150 | LC_EN        | R/W  | 0x20                 | Line CODEC Enable   |        |

| 0x151 | LC_CTRL      | R/W  | 0x07                 | Line CODEC Control  |        |

| 0x152 | LC_ADCG_MSB  | R/W  | 0x04                 | Line ADC Gain MSB   |        |

| 0x153 | LC_ADCG_LSB  | R/W  | 0x00                 | Line ADC Gain LSB   |        |

| 0x154 | LC_DACG_MSB  | R/W  | 0x04                 | Line DAC Gain MSB   |        |

| 0x155 | LC_DACG_LSB  | R/W  | 0x00                 | Line DAC Gain LSB   |        |

| 0x156 | LC_ADOUT_MSB | R    | 0x00                 | Line ADC Dout       |        |

| 0x157 | LC_ADOUT_LSB | R    | 0x00                 | Line ADC Dout LSB   |        |

| 0x158 | LC_DAOUT_MSB | R    | 0x00                 | Line DAC Dout MSB   |        |

| 0x159 | LC_DAOUT_LSB | R    | 0x00                 | Line DAC Dout LSB   |        |

|       | SK C         |      |                      |                     |        |

| 0x160 | FSKE_CTRL1   | R/W  | 0x00                 | FSK Encoder Control | 8.12.1 |

| 0x161 | FSKE_CTRL2   | R/W  | 0x23                 | FSK Encoder Control | 8.12.2 |

# nuvoTon

| Addr. | Name                       | Mode | Value<br>At<br>Reset | Function                             |         |

|-------|----------------------------|------|----------------------|--------------------------------------|---------|

| 0x162 | FSKE_FIFO_W                | V    | NA                   | FSK Encoder FIFO input               | 8.12.3  |

| 0x163 | FSKE_STATUS                | R    | 0x20                 | FSK Encoder Status                   | 8.12.4  |

| 0x164 | FSKE_GAIN                  | R/W  | 0x39                 | FSK Encoder Signal Gain              | 8.12.5  |

| 0x165 | FSKE_PROG                  | R/W  | 0x00                 | FSK Encoder Programmable mode        | 8.12.6  |

| 0x166 | FSKE_BAUD_2                | R/W  | 0x00                 | FSK Encoder Baud Rate                | 8.12.7  |

| 0x167 | FSKE_BAUD_1                | R/W  | 0x00                 | FSK Encoder Baud Rate                | 8.12.7  |

| 0x168 | FSKE_BAUD_0                | R/W  | 0x00                 | FSK Encoder Baud Rate                | 8.12.7  |

| 0x169 | FSKE_MARK_1                | R/W  | 0x00                 | FSK Encoder Mark Freq                | 8.12.8  |

| 0x16A | FSKE_MARK_0                | R/W  | 0x00                 | FSK Encoder Mark Freq                | 8.12.8  |

| 0x16B | FSKE_SPACE_1               | R/W  | 0x00                 | FSK Encoder Space Freq               | 8.12.9  |

| 0x16C | FSKE_SPACE_0               | R/W  | 0x00                 | FSK Encoder Space Freq               | 8.12.9  |

|       |                            |      |                      | 2 1 1 1 C                            | )       |

|       |                            |      |                      | 42                                   | 99)     |

| 0x180 | FSKD_CTRL                  | R/W  | 0x00                 | FSK Decoder Control                  | 8.13.1  |

| 0x181 | FSKD_MODE                  | R/W  | 0x04                 | FSK Decoder Mode                     | 8.13.2  |

| 0x182 | FSKD_ADJUST                | R/W  | 0xC0                 | FSK Decoder Spec Adjustment          | 8.13.3  |

| 0x183 | FSKD_STATUS                | R    | 0x02                 | FSK Decoder Status                   | 8.13.4  |

| 0x184 | FSKD_THRES_MSB             | R/W  | 0x00                 | FSK Decoder Hysteresis MSB           | 8.13.5  |

| 0x185 | FSKD_THRES_LSB             | R/W  | 0x80                 | FSK Decoder Hysteresis LSB           | 8.13.5  |

| 0x186 | FSKD_JUDGE                 | R/W  | 0x04                 | FSK Decoder judge threshold          | 8.13.6  |

| 0x187 | FSKD_SYNC                  | R/W  | 0x02                 | FSK Decoder Sync                     | 8.13.7  |

| 0x188 | FSKD_CDET                  | R/W  | 0x03                 | FSK Decoder Carrier Detect           | 8.13.8  |

| 0x189 | FSKD_FIFO_CTRL             | R/W  | 0x00                 | FSK Decoder FIFO control             | 8.13.9  |

| 0x18A | FSKD_FIFO_DOUT             | V    | NA                   | FSK Decoder FIFO Data                | 8.13.10 |

| 0x18B | FSKD_FIFO_STATUS           | R    | 0x01                 | FSK Decoder FIFO Status              | 8.13.11 |

| 0x18C | FSKD_ENERGY_HI_TH          | R/W  | 0x0C                 | FSK Decoder Carrier Energy Threshold | 8.13.12 |

| 0x18D | FSKD_ENERGY_LO_TH          | R/W  | 0x06                 | FSK Decoder Carrier Energy Threshold | 8.13.13 |

| 0x18E | FSKD_ENERGY_TC             | R/W  | 0x40                 | FSK Decoder Energy time constant     | 8.13.14 |

|       | G3/ 72.                    |      |                      |                                      |         |

| 0x190 | FSKD_CDB_FREQ_LOW_CNT      | R/W  | 0x2F                 | FSK Carrier Detect Frequency Adjust  | 8.13.16 |

| 0x191 | FSKD_CDB_FREQ_LOW_CNT_LSB  | R/W  | 0x14                 | FSK Carrier Detect Frequency Adjust  | 8.13.16 |

| 0x192 | FSKD_CDB_FREQ_HIGH_CNT     | R/W  | 0x23                 | FSK Carrier Detect Frequency Adjust  | 8.13.17 |

| 0x193 | FSKD_CDB_FREQ_HIGH_CNT_LSB | R/W  | 0xF5                 | FSK Carrier Detect Frequency Adjust  | 8.13.17 |

| 0x194 | FSKD_LIMIT_TH              | R/W  | 0xFF                 | FSK Signal Clamp Threshold           | 8.13.18 |

# nuvoTon

|           | Function                                       | Value<br>At<br>Reset | Mode | Name                | Addr.           |

|-----------|------------------------------------------------|----------------------|------|---------------------|-----------------|

| 8.21.1    | PWM Operation Clock Enable                     | 0x00                 | R/W  | PWM Clock           | 0x1A0           |

| 8.21.2    | PWM Tone1 Control                              | 0x00                 | R/W  | PWM Tone1 Control   | 0x1A2           |

| 8.21.3    | PWM Tone1 Frequency                            | 0x00                 | R/W  | PWM Tone1 Frequency | 0x1A3           |

| 8.21.4    | PWM Tone2 Control                              | 0x00                 | R/W  | PWM Tone2 Control   | 0x1A4           |

| 8.21.5    | PWM Tone2 Frequency                            | 0x00                 | R/W  | PWM Tone2 Frequency | 0x1A5           |

| 8.17.1    | Ring Det. Control                              | 0x00                 | R/W  | RNG_CTRL            | 0x1B0           |

| 8.17.2    | Ring Det. State                                | 0x00                 | R    | RNG_STATE           | 0x1B1           |

| 8.17.3    | Ring Det. Counter                              | 0x00                 | R    | RNG_CNTR_MSB        | 0x1B2           |

| 8.17.3    | Ring Det. Counter                              | 0x00                 | R    | RNG_CNTR_LSB        | 0x1B3           |

| 8.17.4    | Ring Det. Counter latch control                | 0x00                 | R/W  | RNG_LATCH           | 0x1B4           |

| 8.11.1    | Tone Generator Control                         | 0x00                 | R/W  | TONE CTRL           | 0x1C0           |

| 8.11.2    | Tone Frequency A                               | 0x00                 | R/W  | TONE_FREQ_A_MSB     | 0x1C1           |

| 8.11.2    | Tone Frequency A                               | 0x00                 | R/W  | TONE FREQ A LSB     | 0x1C2           |

| 8.11.3    | Tone Frequency B                               | 0x00                 | R/W  | TONE_FREQ_B_MSB     | 0x1C3           |

| 8.11.3    | Tone Frequency B                               | 0x00                 | R/W  | TONE_FREQ_B_LSB     | 0x1C4           |

| 8.11.4    | Tone Level A                                   | 0x00                 | R/W  | TONE_LEVEL_A        | 0x1C5           |

| 8.11.5    | Tone Level B                                   | 0x00                 | R/W  | TONE_LEVEL_B        | 0x1C6           |

| 8.11.6    | Present (on) time of each tone.                | 0x00                 | R/W  | TONE_ON_TIME        | 0x1C7           |

| 8.11.7    | Absent (off) time of each tone.                | 0x00                 | R/W  | TONE_OFF_TIME       | 0x1C8           |

| to 8.11.8 | The number of DTMF digits or tones to generate | 0x00                 | R/W  | TONE_BUF_LEN        | 0x1C9           |

|           |                                                |                      |      |                     | 3               |

| 8.11.10   | Tone Buffer 0x1D0-0x1DB                        | 0x00                 | R/W  | TONE_BUFFER         | 0x1D0-<br>0x1DB |

| 8.10.1    | DTMF Det. Control                              | 0x00                 | R/W  | DTMF_CTRL           | 0x1E0           |

| 8.10.2    | DTMF Det. FIFO Control                         | 0x40                 | R/W  | DTMF_FIFO_CTRL      | 0x1E1           |

| 8.10.3    | DTMF Det. FIFO Information                     | 0x00                 | R    | DTMF_FIFO           | 0x1E2           |

| 8.10.4    | DTMF Det. FIFO Status                          | 0x01                 | R/W  | DTMF_FIFO_STATUS    | 0x1E3           |

| 8.10.5    | DTMF Det. Threshold MSB                        | 0x01                 | R/W  | DTMF_THRES_MSB      | 0x1E4           |

| 8.10.5    | DTMF Det. Threshold LSB                        | 0x00                 | R/W  | DTMF_THRES_LSB      | 0x1E5           |

| 8.10.6    | DTMF Det. Present Detect Time                  | 0x00                 | R/W  | DTMF_PDT            | 0x1E6           |

| 8.10.7    | DTMF Det. Absent Detect Time                   | 0x00                 | R/W  | DTMF_ADT            | 0x1E7           |

| 8.10.8    | DTMF Det. Accept Time                          | 0x00                 | R/W  | DTMF_ACCT           | 0x1E8           |

# nuvoTon

| Addr.           | Name              | Mode | Value<br>At<br>Reset | Function                                       |         |

|-----------------|-------------------|------|----------------------|------------------------------------------------|---------|

| 0x1EA           | DTMF_RX_DATA      | R    | 0x00                 | DTMF Det. Received Data                        | 8.10.10 |

| 0x1EB           | DTMF_RFREQ_MSB    | R    | 0x00                 | DTMF Det. Row Frequency MSB                    | 8.10.11 |

| 0x1EC           | DTMF_RFREQ_LSB    | R    | 0x00                 | DTMF Det. Row Frequency LSB                    | 8.10.11 |

| 0x1ED           | DTMF_CFREQ_MSB    | R    | 0x00                 | DTMF Det. Column Frequency MSB                 | 8.10.12 |

| 0x1EE           | DTMF_CFREQ_LSB    | R    | 0x00                 | DTMF Det. Column Frequency LSB                 |         |

| 0x1F0           | VD_CTRL           | R/W  | 0x00                 | Voice Det. Control                             |         |

| 0x1F1           | VD_STATUS         | R    | 0x00                 | Voice Det. Status                              |         |

| 0x1F2           | VD_THRES_MSB      | R/W  | 0x01                 | Voice Det. Threshold MSB                       |         |

| 0x1F3           | VD_THRES_LSB      | R/W  | 0x00                 | Voice Det. Threshold LSB                       |         |

| 0x1F4           | VD_ENERGY_MSB     | R    | 0x00                 | Voice Det. Energy MSB                          |         |

| 0x1F5           | VD_ENERGY_LSB     | R    | 0x00                 | Voice Det. Energy LSB                          |         |

| 0x200           | CAS_CTRL          | R/W  | 0x40                 | CAS Control                                    |         |

| 0x201           | CAS_THRES_LOW     | R/W  | 0x00                 | CAS Low Threshold                              | 3)      |

| 0x202           | CAS_THRES_LOW_LSB | R/W  | 0x00                 | CAS Low Threshold                              |         |

| 0x203           | CAS_MULT          | R/W  | 0x11                 | CAS High Threshold Multiplier                  |         |

| 0x204           | CAS_PRESENT       | R/W  | 0x40                 | CAS Present Time                               |         |

| 0x205           | CAS_ABSENT        | R/W  | 0x20                 | CAS Absent Time                                |         |

| 0x206           | CAS_STATUS        | R    | 0x00                 | CAS Status                                     |         |

| 0x207           | CAS_MODE          | R/W  | 0x10                 | CAS or Arbitrary Tone Detection Mode           |         |

| 0x208           | ATD_MAX_HFC       | R/W  | 0x01                 | ATD Max High Frequency Cnt                     |         |

| 0x209           | ATD_MAX_HFC_LSB   | R/W  | 0x10                 | ATD Max High Frequency Cnt                     |         |

| 0x20A           | ATD_MIN_HFC       | R/W  | 0x01                 | ATD Min High Frequency Cnt                     |         |

| 0x20B           | ATD_MIN_HFC_LSB   | R/W  | 0x20                 | ATD Min High Frequency Cnt                     |         |

| 0x20C           | ATD_MAX_LFC       | R/W  | 0x01                 | ATD Max Low Frequency Cnt                      |         |

| 0x20D           | ATD_MAX_LFC_LSB   | R/W  | 0x61                 | ATD Max Low Frequency Cnt                      |         |

| 0x20E           | ATD_MIN_LFC       | R/W  | 0x01                 | ATD Min Low Frequency Cnt                      |         |

| 0x20F           | ATD_MIN_LFC_LSB   | R/W  | 0x6F                 | ATD Min Low Frequency Cnt                      |         |

| 0x210-<br>0x241 | ATD_HF_COEFF      | R/W  | 0x00                 | ATD High Frequency IIR coefficient 0x210~0x241 |         |

| 0x242-<br>0x273 | ATD_LF_COEFF      | R/W  | 0x00                 | ATD Low Frequency IIR coefficient 0x242~0x273  |         |

| 0x274           | FSK_COEFF         | R/W  | 0x00                 | FSK IIR Coefficient                            |         |

| 0x275           | FSK_COEFF_ADDR    | R/W  | 0x00                 | FSK IIR Coefficient Address                    |         |

| 0x276           | CAS_MAX_HFC       | R/W  | 0x01                 | CAS Max High Frequency Cnt                     |         |

| 0x277           | CAS_MAX_HFC_LSB   | R/W  | 0x0E                 | CAS Max High Frequency Cnt                     |         |

# nuvoTon

| Addr. | Name                     | Mode | Value<br>At<br>Reset | Function                                 |     |

|-------|--------------------------|------|----------------------|------------------------------------------|-----|

| 0x278 | CAS_MIN_HFC              | R/W  | 0x01                 | CAS Min High Frequency Cnt               |     |

| 0x279 | CAS_MIN_HFC_LSB          | R/W  | 0x21                 | CAS Min High Frequency Cnt               |     |

| 0x27A | CAS_MAX_LFC              | R/W  | 0x01                 | CAS Max Low Frequency Cnt                |     |

| 0x27B | CAS_MAX_LFC_LSB          | R/W  | 0x5D                 | CAS Max Low Frequency Cnt                |     |

| 0x27C | CAS_MIN_LFC              | R/W  | 0x01                 | CAS Min Low Frequency Cnt                |     |

| 0x27D | CAS_MIN_LFC_LSB          | R/W  | 0x75                 | CAS Min Low Frequency Cnt                |     |

|       |                          |      |                      | 90.40                                    |     |

|       |                          |      |                      |                                          |     |

| 0x280 | CPT_CTRL                 | R/W  | 0x07                 | CPT Control                              |     |

| 0x281 | CPT_STATUS               | R    | 0x00                 | CPT Status                               |     |

| 0x282 | CPT_THRES_H_MSB          | R/W  | 0x24                 | CPT High Threshold MSB                   |     |

| 0x283 | CPT_THRES_H_LSB          | R/W  | 0x00                 | CPT High Threshold LSB                   | 2   |

| 0x284 | CPT_THRES_L_MSB          | R/W  | 0x1A                 | CPT Low Threshold MSB                    | 2)) |

| 0x285 | CPT_THRES_L_LSB          | R/W  | 0x00                 | CPT Low Threshold LSB                    |     |

| 0x286 | CPT_ENERGY_MSB           | R    | 0x00                 | CPT Energy MSB                           |     |

| 0x287 | CPT_ENERGY_LSB           | R    | 0x00                 | CPT Energy LSB                           |     |

| 0x290 | TIME_CTRL                | R/W  | 0x00                 | Timer Control                            |     |

| 0x292 | TIME_TARG_MSB            | R/W  | 0x00                 | Timer Target Counter MSB                 |     |

| 0x293 | TIME_TARG_LSB            | R/W  | 0x00                 | Timer Target Counter LSB                 |     |

| 0x294 | TIME_CNT_MSB             | R    | 0x00                 | Timer Current Counter MSB                |     |

| 0x295 | TIME_CNT_LSB             | R    | 0x00                 | Timer Current Counter LSB                |     |

| 0x300 | AEC_CONFIG               | R/W  | 0x96                 | AEC Configuration                        |     |

| 0x301 | AEC_RESET                | R/W  | 0xE8                 | AEC Reset                                |     |

| 0x302 | AEC_EC_BELTA             | R/W  | 0x03                 | AEC EC BELTA                             |     |

| 0x303 | AEC_AS_COEFF             | R/W  | 0x14                 | AEC AS Coefficient                       |     |

| 0x305 | AEC_DT_LONG_TC           | R/W  | 0x09                 | AEC Double Talk long term time constant  |     |

| 0x306 | AEC_DT_SHORT_TC          | R/W  | 0xBB                 | AEC Double Talk short term time constant |     |

| 0x307 | AEC_DT_HANGOVER_TIME_MSB | R/W  | 0x00                 | AEC Double Talk Detector Parameters      |     |

| 0x308 | AEC_DT_HANGOVER_TIME_LSB | R/W  | 0x20                 | AEC Double Talk Detector Parameters      |     |

| 0x309 | AEC_DT_DV_THRESH_MSB     | R/W  | 0x19                 | AEC Double Talk Detector Parameters      |     |

| 0x30A | AEC_DT_DV_THRESH_LSB     | R/W  | 0x98                 | AEC Double Talk Detector Parameters      |     |

| 0x30B | AEC_DT_LONG_THRESH_MSB   | R/W  | 0x00                 | AEC Double Talk Detector Parameters      |     |

| 0x30C | AEC_DT_LONG_THRESH_LSB   | R/W  | 0x00                 | AEC Double Talk Detector Parameters      |     |

| 0x30D | AEC_DT_SHORT_THRESH_MSB  | R/W  | 0x10                 | AEC Double Talk Detector Parameters      |     |

# nuvoTon

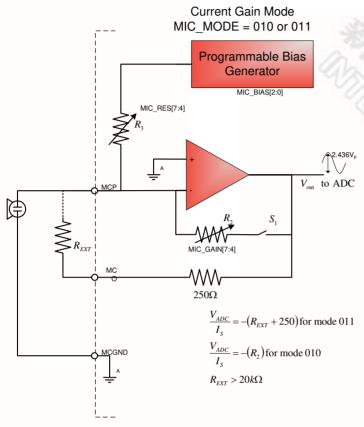

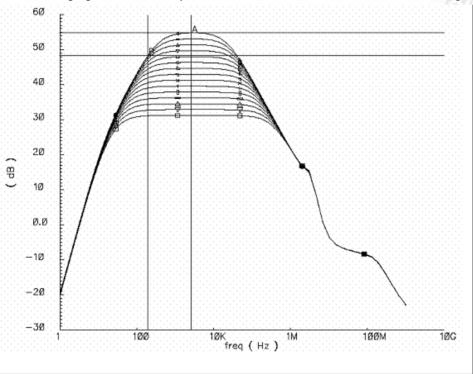

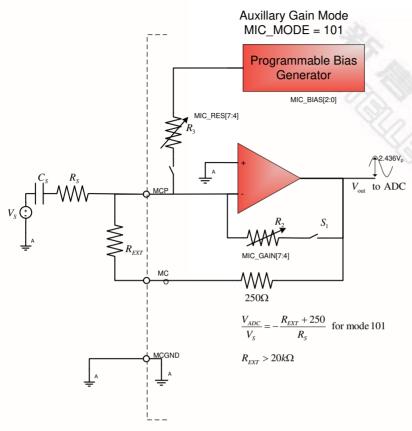

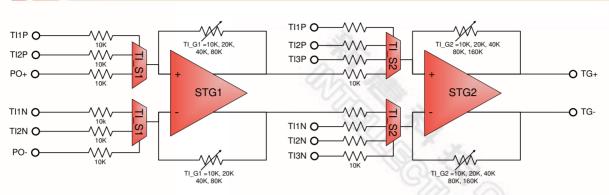

| Addr. | Name                        | Mode | Value<br>At<br>Reset | Function                                        |     |