# TPS2474x 2.5-V to 18-V High Performance Hot Swap and ORing Controller

Check for Samples: TPS24740, TPS24741, TPS24742

#### **Features**

Texas

**INSTRUMENTS**

- 2.5V to 18V Bus Operation (30V abs max)

- Programmable Protection Settings:

- Current Limit: ±5% at 10mV

- Fast Trip: ±10% at 20mV

- Reverse Voltage: ±1mV at -1 mV

- Programable Response Time for Fast Trip and Reverse Voltage

- Programmable FET SOA Protection

- Dual Timer (Inrush/Fault)

- Interchangeable Hot Swap and ORing

- Analog Current Monitor (1% at 25mV)

- Status Flags for Faults and Power Good

- UV and OV Protection

- Independent EN for Hot Swap and ORing

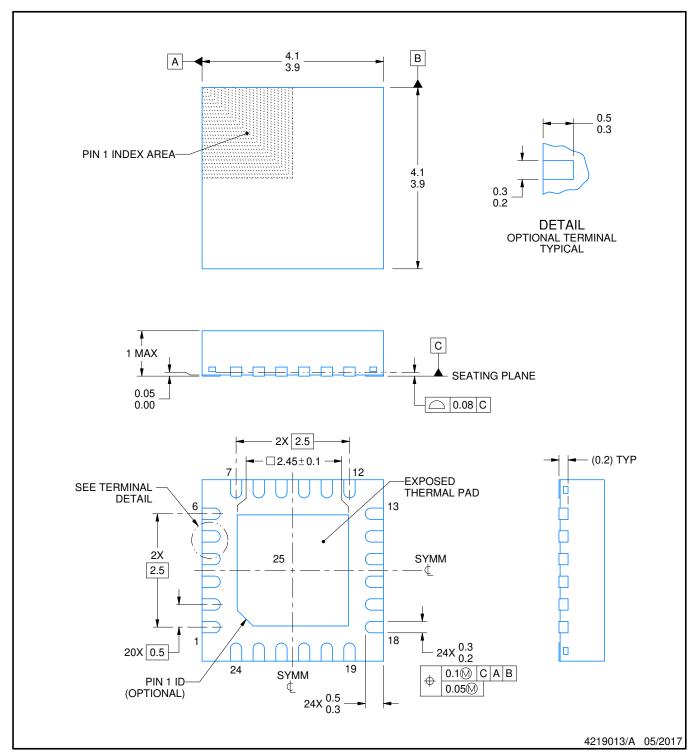

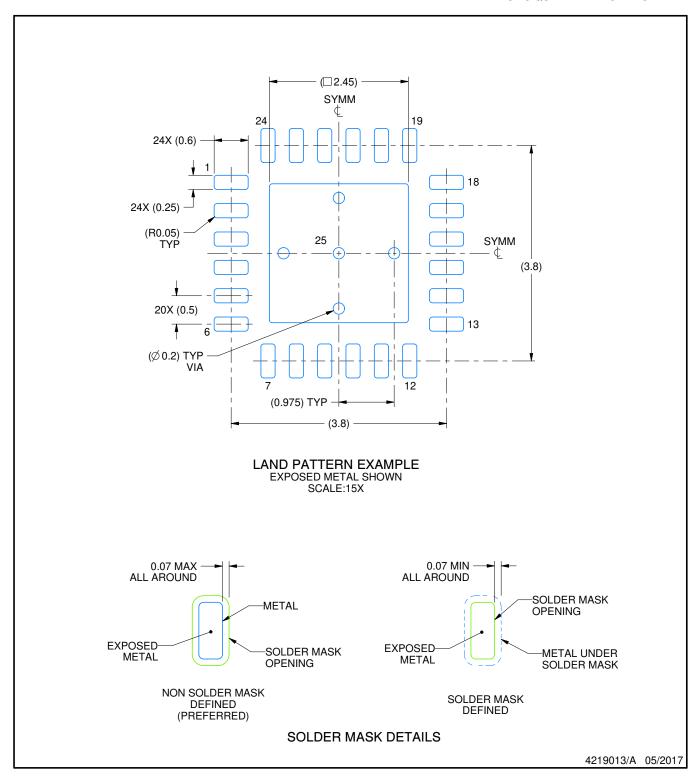

- 4mm × 4mm 24-pin QFN

- 40 = Latch, 41 = Retry, 42 = Fast Latch Off

## **Applications**

- **Enterprise Storage**

- **Power Muxing**

- Redundant Power Supplies

- Battery Back Up

## 3 Description

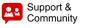

The TPS2474x is an integrated ORing and Hot Swap controller for 2.5 V to 18 V systems. It's precise and programmable protection settings aid in the design of high power, high availability systems where isolating faults is critical.

Programmable current limit, fast shut down, and fault timer protect the load and supply during fault conditions such as a hot - short. The fast shutdown threshold and response time can be tuned to ensure a fast response to real faults, while avoiding nuisance trips. Programmable SOA (Safe Operating Area) protection and the inrush timer keep the MOSFET safe under all operating conditions. After asserting a power good, TPS2474x runs the fault timer during over-current events, but doesn't current limit. It shuts down after the fault timer expires. Two independent timers (inrush/fault) allow the user to customize protection based on system requirements. The ORing function of the TPS2474x allows the user to program the reverse voltage threshold and response time to aid in the design of redundant power supply systems.

#### Device Information<sup>(1)</sup>

| PART NUMBER                      | PACKAGE   | BODY SIZE (NOM)   |

|----------------------------------|-----------|-------------------|

| TPS24740<br>TPS24741<br>TPS24742 | VQFN (24) | 4.00 mm x 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

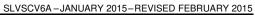

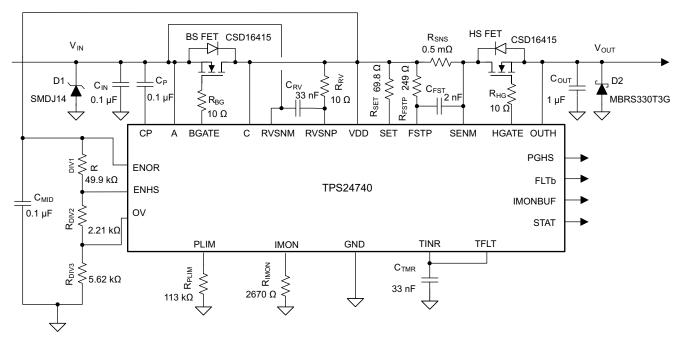

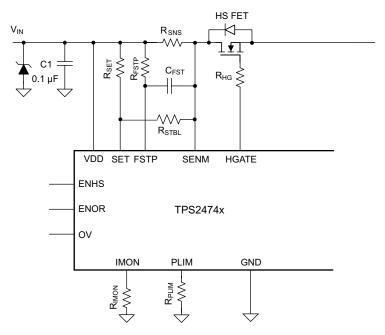

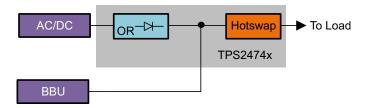

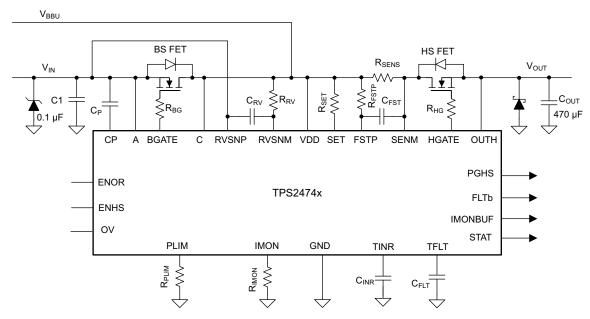

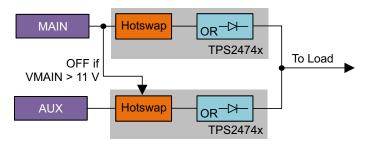

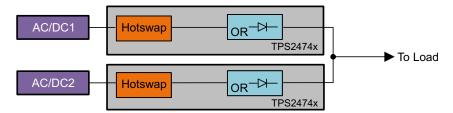

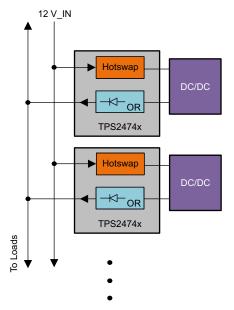

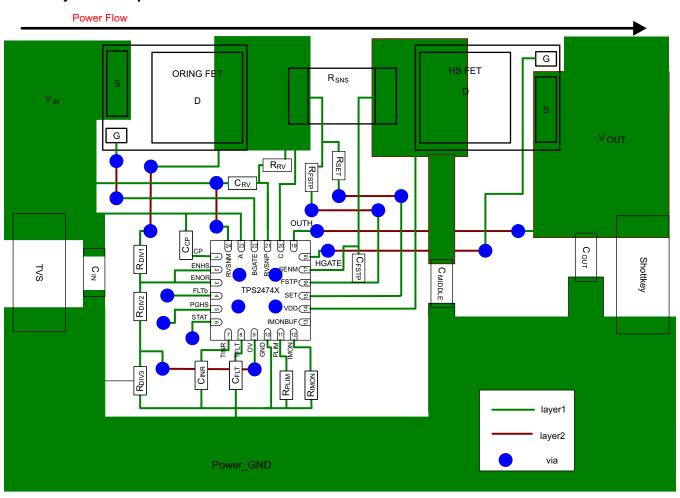

# Simplified Schematics

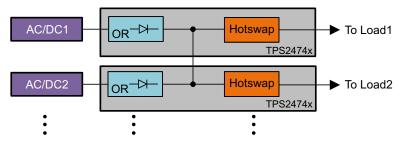

#### TPS2474x in Priority Muxing

## **Table of Contents**

| 1      | Features 1                           |    | 9.2 Functional Block Diagram                     | 13   |

|--------|--------------------------------------|----|--------------------------------------------------|------|

| 2      | Applications 1                       |    | 9.3 Feature Description                          | 14   |

| 3      | Description 1                        |    | 9.4 Device Functional Modes                      | 20   |

| 4      | Simplified Schematics                | 10 | Application and Implementation                   | 23   |

| 5      | Revision History2                    |    | 10.1 Application Information                     | 23   |

| 6      | Device Comparison Table              |    | 10.2 Typical Application                         |      |

| 7      | Pin Configuration and Functions      |    | 10.3 System Examples                             | 41   |

| ,<br>8 | Specifications                       | 11 | Power Supply Recommendations                     | 51   |

| 0      | 8.1 Absolute Maximum Ratings         | 12 | Layout                                           | . 51 |

|        | 8.2 ESD Ratings                      |    | 12.1 Layout Guidelines                           | 51   |

|        | 8.3 Recommended Operating Conditions |    | 12.2 Layout Example                              | 52   |

|        | 8.4 Thermal Information              | 13 | Device and Documentation Support                 | 53   |

|        | 8.5 Electrical Characteristics       |    | 13.1 Related Links                               | 53   |

|        | 8.6 Timing Requirements              |    | 13.2 Trademarks                                  | 53   |

|        | 8.7 Typical Characteristics          |    | 13.3 Electrostatic Discharge Caution             | 53   |

| 9      | Detailed Description                 |    | 13.4 Glossary                                    | 53   |

| •      | 9.1 Overview                         | 14 | Mechanical, Packaging, and Orderable Information | . 53 |

|        |                                      |    |                                                  |      |

## 5 Revision History

## Changes from Original (January 2015) to Revision A

**Page**

## **Device Comparison Table**

| PART NUMBER <sup>(1)</sup> | LATCH / RETRY OPTION |

|----------------------------|----------------------|

| TPS24740                   | Latch                |

| TPS24741                   | Auto – Retry         |

| TPS24742                   | Fast Latch Off       |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

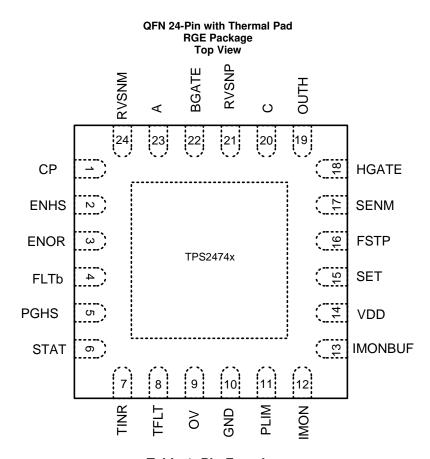

## 7 Pin Configuration and Functions

**Table 1. Pin Functions**

| PIN                                                                                       |     | TYPF <sup>(1)</sup>                                                              | DESCRIPTION                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                      | NO. | I I PE'                                                                          | DESCRIPTION                                                                                                                                                                                                                                |

| А                                                                                         | 23  | I/P                                                                              | Voltage sense input that connects to the OR MOSFET's body diode's anode. Connect to the OR MOSFET source in the typical configuration. A pin is used to supply power to the ORing block of the TPS2474x under certain biasing conditions.  |

| BGATE 22                                                                                  |     | 0                                                                                | Connect to the gate of the external OR MOSFET. Controls the OR MOSFET to emulate a low forward-voltage diode.                                                                                                                              |

| С                                                                                         | 20  | I/P                                                                              | Voltage sense input that connects to the OR MOSFET's body diode's cathode. Connect to the OR MOSFET drain in the typical configuration. C pin is used to supply power to the ORing block of the TPS2474x under certain biasing conditions. |

| СР                                                                                        | 1   | I/O                                                                              | Connect a storage capacitor from CP to A for fast turn-on of blocking Gate.                                                                                                                                                                |

| ENHS 2 I Active-high enable input of Hot-swap. Logic input. Connects to resistor divider. |     | Active-high enable input of Hot-swap. Logic input. Connects to resistor divider. |                                                                                                                                                                                                                                            |

| ENOR                                                                                      | 3   | I                                                                                | Active-high enable input of Oring. Logic input. Connects to resistor divider.                                                                                                                                                              |

Product Folder Links: TPS24740 TPS24741 TPS24742

(1) I = Input; O = Output; P = Power

## **Table 1. Pin Functions (continued)**

| PIN      |    | TYPE <sup>(1)</sup> | DECORIDATION                                                                                                                                               |  |  |  |

|----------|----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME NO. |    | TYPE                | DESCRIPTION                                                                                                                                                |  |  |  |

| FLTb     | 4  | 0                   | Active-low, open-drain output indicating various faults.                                                                                                   |  |  |  |

| FSTP     | 16 | I                   | Fast trip programming set pin for hot-swap. Connect $R_{FSTP}$ from the positive terminal of the Hot Swap sense resistor to the FSTP pin.                  |  |  |  |

| GND      | 10 | _                   | Ground.                                                                                                                                                    |  |  |  |

| HGATE    | 18 | 0                   | Gate driver output for external Hot Swap MOSFET.                                                                                                           |  |  |  |

| IMON     | 12 | I/O                 | Analog current monitor and load current limit program point. Connect R <sub>IMON</sub> to ground.                                                          |  |  |  |

| IMONBUF  | 13 | 0                   | Voltage output proportional to the load current (0V-3.0V).                                                                                                 |  |  |  |

| OUTH     | 19 | I                   | Output voltage sensor for monitoring Hot Swap MOSFET power. Connects to the source termina hot-swap N channel MOSFET.                                      |  |  |  |

| OV       | 9  | I                   | Overvoltage comparator input. Connects to resistor divider. HGATE and BGATE are pulled low when OV exceeds the threshold. Connect to ground when not used. |  |  |  |

| PGHS     | 5  | 0                   | Active-high, open-drain power-good indicator.                                                                                                              |  |  |  |

| PLIM     | 11 | I                   | Power-limiting programming pin. A resistor from this pin to GND sets the maximum power dissipation for the Hot Swap FET.                                   |  |  |  |

| RVSNP    | 21 | I                   | Positive input of the reverse voltage comparator. Connect a resistor from RVSNP to C to set the reverse voltage trip point of the blocking FET.            |  |  |  |

| RVSNM    | 24 | I                   | Negative input of the reverse voltage comparator.                                                                                                          |  |  |  |

| SENM     | 17 | I                   | Current-sensing input for the sensing resistor. Directly connects to the negative terminal of the sensing resistor.                                        |  |  |  |

| SET      | 15 | I                   | Current-limit programming set pin for hot-swap. A resistor is connected from positive terminal of the sensing resistor.                                    |  |  |  |

| STAT     | 6  | 0                   | High when BGATE is ON.                                                                                                                                     |  |  |  |

| TFLT     | 8  | I/O                 | Fault timer, which runs when the device goes from regular operation to an over-current condition.                                                          |  |  |  |

| TINR     | 7  | I/O                 | Inrush timer, which runs during the inrush operation (start-up) if the part is in current limit or power limit.                                            |  |  |  |

| VDD      | 14 | Р                   | Power Supply.                                                                                                                                              |  |  |  |

## 8 Specifications

## 8.1 Absolute Maximum Ratings

Unless otherwise noted, these apply over recommended operating junction temperature:  $-40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$ . (1)

|                 |                                                                                | MIN  | MAX                               | UNIT |

|-----------------|--------------------------------------------------------------------------------|------|-----------------------------------|------|

|                 | CP, BGATE                                                                      | -0.3 | 40                                | V    |

|                 | VDD,SET, FSTP,SENM, OUTH, C, RVSNP, RVSNM, A, ENHS, ENOR, FLTb, PGHS, OV, STAT | -0.3 | 30                                | V    |

|                 | CP, BGATE to A                                                                 | -0.3 | 12                                | ٧    |

|                 | HGATE to OUTH                                                                  | -0.3 | 15                                | ٧    |

| land A Valtage  | SET to VDD                                                                     | -0.3 | 0.3                               | ٧    |

| Input Voltage   | SENM, FSTP to VDD                                                              | -0.6 | 0.3                               | ٧    |

|                 | A to C                                                                         | -30  | 7                                 | ٧    |

|                 | RVSNM, to A, C, RVSNP<br>RVSNP to A, C, RVSNM                                  | -30  | 30                                | ٧    |

|                 | TINR, TFLT, PLIM, IMON,                                                        | -0.3 | 3.6                               | ٧    |

|                 | IMONBUF                                                                        | -0.3 | 12<br>15<br>0.3<br>0.3<br>7<br>30 | ٧    |

| Sink Current    | FLTb, PGHS, STAT                                                               |      | 5                                 | mA   |

| Source Current  | IMON, IMONBUF                                                                  |      | 5                                 | mA   |

| Storage tempera | ature range, T <sub>stg</sub>                                                  | -65  | 150                               | ô    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Submit Documentation Feedback

Copyright © 2015, Texas Instruments Incorporated

## 8.2 ESD Ratings

|                        |               |                                                                     | VALUE | UNIT |

|------------------------|---------------|---------------------------------------------------------------------|-------|------|

| v (1)                  | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (2)              | ±1500 | V    |

| V <sub>(ESD)</sub> (1) | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (3) | ±500  | V    |

Electrostatic discharge (ESD) measures device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

## 8.3 Recommended Operating Conditions

These apply over recommended operating junction temperature:  $-40^{\circ}\text{C} \le T_{\text{J}} \le 125^{\circ}\text{C}$ .

| 117                    |                                      | MIN  | MAX  | UNIT |

|------------------------|--------------------------------------|------|------|------|

|                        | VDD, SENM, SET <sup>(1)</sup> , FSTP | 2.5  | 18   |      |

| Input voltage          | ENHS, ENOR, FLTb, PGHS, STAT, OUTH   | 0    | 18   | V    |

|                        | A, C, RVSNM, RVSNP; (2)              | 0.7  | 18   |      |

| Sink current           | FLTb, PGHS, STAT                     | 0    | 2    | mA   |

| Source current         | IMON                                 | 0    | 1    | mA   |

|                        | PLIM                                 | 4.99 | 500  | kΩ   |

| External registence    | IMON                                 | 1    | 6    | kΩ   |

| External resistance    | RVSNP                                | 10   | 1000 | Ω    |

|                        | FSTP                                 | 10   | 4000 | Ω    |

|                        | SET                                  | 10   | 400  | Ω    |

| D / D                  | w/o R <sub>STBL</sub> (3)            | 10   | 70   |      |

| RIMON / RSET           | With appropriate R <sub>STBL</sub>   | 3    | 10   |      |

|                        | CP, FSTP, RVSNP                      | 1    | 1000 | nF   |

|                        | HGATE, BGATE (4)                     | 0    | 1    | μF   |

| External capacitor     | VDD, SENM, SET(1), FSTP   2.5        |      | nF   |      |

|                        | IMON                                 |      | 30   | pF   |

|                        | IMONBUF                              |      | 100  | pF   |

| Operating junction tem | perature, T <sub>J</sub>             | -40  | 125  | °C   |

<sup>(1)</sup> Do not apply voltage to these pins.

#### 8.4 Thermal Information

|                        | THERMAL METRIC <sup>(1)</sup>                | TPS24740, TPS24741,<br>TPS24742 | UNIT |

|------------------------|----------------------------------------------|---------------------------------|------|

|                        |                                              | RGE (24 PINS)                   |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 34.6                            |      |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 38.4                            |      |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 12.9                            | 9C/M |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.5                             | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 12.9                            |      |

| $R_{\theta JC(bot)}$   | Junction-to-case (bottom) thermal resistance | 3.2                             |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Product Folder Links: TPS24740 TPS24741 TPS24742

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

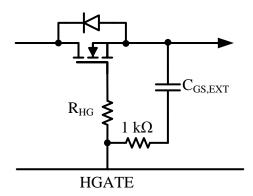

For the HS then ORing application these pins may be below the recommended minimum during start-up. The part is designed to function properly under these scenarios. However the part should not be used with a bus voltage below the recommended voltage. Refer to  $R_{STBL}$  Requirement for  $R_{IMON} / R_{SET} < 10$  describe in section Select  $R_{SNS}$  and  $V_{SNS,CL}$  Setting. External capacitance tied to HGATE, BGATE should be in series with a resistor no less than  $1k\Omega$ .

#### 8.5 Electrical Characteristics

Unless otherwise noted these limits apply to the following:  $-40^{\circ}C \leq T_{J} \leq 125^{\circ}C; \ 2.5V < V_{VDD} \ , \ V_{OUTH} < 18V; \ 0.7 \ V < V_{A} \ , \ V_{C} \ , \ V_{RVSNM} < 18 \ V; \ V_{ENHS} = V_{ENOR} = 2 \ V, \ V_{OV} = 0 \ V; \ V_{BGATE}, \ V_{HGATE}, \ V_{PGHS}, \ V_{STAT}, \ V_{FLTb}, \ and \ V_{IMONBUF} \ are floating; \ C_{CP} = 100 \ nF, \ C_{INR} = 1 \ nF, \ C_{FLT} = 1 \ nF, \ R_{SET} = 44.2 \ \Omega, \ R_{IMON} = 2.98 \ k\Omega, \ R_{FSTP} = 200 \ \Omega, \ R_{RV} = 200 \ \Omega, \ and \ R_{PLIM} = 52 \ k\Omega.$

|                         | PARAMETER                                                                            | TEST CONDITION                                                             | MIN    | TYP   | MAX    | UNIT |

|-------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------|-------|--------|------|

| INPUT SUPPL             | Y (VDD)                                                                              |                                                                            | •      |       |        |      |

| V <sub>UVR</sub>        | UVLO threshold, rising                                                               |                                                                            | 2.2    | 2.32  | 2.45   | V    |

| V <sub>UVhyst</sub>     | UVLO hysteresis                                                                      |                                                                            |        | 0.1   |        | V    |

| I <sub>QON</sub>        | Supply current: I <sub>VDD</sub> +I <sub>A</sub> +I <sub>C</sub> + I <sub>OUTH</sub> | Device on, V <sub>ENHS</sub> = V <sub>ENOR</sub> = 2V                      |        | 4.2   | 6      | mA   |

| HOT SWAP FE             | ET ENABLE (ENHS)                                                                     |                                                                            |        |       |        |      |

| V <sub>ENHS</sub>       | Threshold voltage, rising                                                            |                                                                            | 1.3    | 1.35  | 1.4    | V    |

| V <sub>ENHShyst</sub>   | Hysteresis                                                                           |                                                                            |        | 50    |        | mV   |

| I <sub>ENHS</sub>       | Input Leakage Current                                                                | 0 ≤ V <sub>ENHS</sub> ≤ 30V                                                | -1     |       | 1      | μΑ   |

| BLOCKING (O             | PRING) FET ENABLE (ENOR)                                                             |                                                                            |        |       |        |      |

| V <sub>ENOR</sub>       | Threshold voltage, rising                                                            |                                                                            | 1.3    | 1.35  | 1.4    | V    |

| V <sub>ENORhyst</sub>   | Hysteresis                                                                           |                                                                            |        | 50    |        | mV   |

| I <sub>ENOR</sub>       | Input leakage current                                                                | 0 V ≤ V <sub>ENOR</sub> ≤ 30V                                              | -1     | 0     | 1      | μΑ   |

| OVER VOLTA              | GE (OV)                                                                              |                                                                            |        |       |        |      |

| V <sub>OVR</sub>        | Threshold voltage, rising                                                            |                                                                            | 1.3    | 1.35  | 1.4    | mV   |

| V <sub>OVhyst</sub>     | Hysteresis                                                                           |                                                                            |        | 50    |        | mV   |

| I <sub>ov</sub>         | Input leakage current                                                                | 0 ≤ V <sub>OV</sub> ≤ 30V                                                  | -1     |       | 1      | μΑ   |

| POWER LIMIT             | PROGRAMING (PLIM)                                                                    |                                                                            |        |       |        |      |

| V <sub>PLIM,BIAS</sub>  | Bias voltage                                                                         | Sourcing 10µA                                                              | 0.66   | 0.675 | 0.69   | V    |

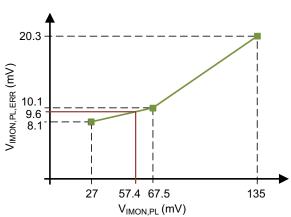

| V PLIM,BIAS             | Regulated IMON voltage during power limit                                            | $R_{PLIM} = 52 \text{ k}\Omega; V_{SENM-OUTH}=12V;$                        | 114.75 | 135   | 155.25 |      |

|                         |                                                                                      | $R_{PLIM} = 105 \text{ k}\Omega; V_{SENM-OUTH} = 12V;$                     | 56.95  | 67    | 77.05  | mV   |

| V <sub>IMON,PL</sub>    |                                                                                      | $R_{PLIM} = 261 \text{ k}\Omega; V_{SENM-OUTH} = 12V;$                     | 18.9   | 27    | 35.1   |      |

|                         |                                                                                      | $R_{PLIM} = 105 \text{ k}\Omega; V_{SENM-OUTH} = 2V;$                      | 341.7  | 402   | 462.3  |      |

|                         |                                                                                      | $R_{PLIM} = 105 \text{ k}\Omega; V_{SENM-OUTH}=18V;$                       | 38.25  | 45    | 51.75  |      |

| SLOW TRIP T             | HRESHOLD (SET)                                                                       |                                                                            |        |       |        |      |

| V <sub>OS_SET</sub>     | Input referred offset (V <sub>SNS</sub> to V <sub>IMON</sub> scaling)                | $R_{SET}$ = 44.2Ω; $R_{IMON}$ =3kΩ to 1.2kΩ (corresponds to                | -150   |       | 150    | μV   |

| V <sub>GE_SET</sub>     | Gain error (V <sub>SNS</sub> to V <sub>IMON</sub> scaling) <sup>(1)</sup>            | V <sub>SNS,CL</sub> =10mV to 25mV)                                         | -0.4%  |       | 0.4%   |      |

| FAST TRIP TH            | RESHOLD PROGRAMMING (FSTP)                                                           |                                                                            |        |       |        |      |

| I <sub>FSTP</sub>       | FSTP input bias current                                                              | V <sub>FSTP</sub> =12V                                                     | 95     | 100   | 105    | μΑ   |

|                         |                                                                                      | $R_{FSTP}$ = 200 $\Omega$ , $V_{SNS}$ when $V_{HGATE} \downarrow$          | 18     | 20    | 22     |      |

| V <sub>FASTRIP</sub>    | Fast trip threshold                                                                  | $R_{FSTP} = 1 \text{ k}\Omega, V_{SNS} \text{ when } V_{HGATE} \downarrow$ | 95     | 100   | 105    | mV   |

|                         |                                                                                      | $R_{FSTP} = 4 \text{ k}\Omega, V_{SNS} \text{ when } V_{HGATE} \downarrow$ | 380    | 400   | 420    |      |

| CURRENT MC              | ONITOR and CURRENT LIMIT PROGRAMING (I                                               | MON)                                                                       |        |       |        |      |

| V <sub>IMON,CL</sub>    | Slow trip threshold at summing node                                                  | V <sub>IMON</sub> ↑, when I <sub>TFLT</sub> starts sourcing                | 660    | 675   | 690    | mV   |

|                         | ONITOR (IMONBUF)                                                                     |                                                                            |        |       |        |      |

| V <sub>OS_IMONBUF</sub> | Buffer offset                                                                        | V <sub>IMON</sub> = 50mV to 675mV, Input referred                          | -3     | 0     | 3      | mV   |

| GAIN <sub>IMONBUF</sub> | Buffer voltage gain                                                                  | ΔV <sub>IMONBUF</sub> F / ΔV <sub>IMON</sub>                               | 2.97   | 2.99  | 3.01   | V    |

| BW <sub>IMONBUF</sub>   | Buffer closed loop bandwidth                                                         | $C_{IMONBUF} = 75pF$                                                       |        | 1     |        | MHz  |

<sup>(1)</sup> Specified by characterization, not production tested.

## **Electrical Characteristics (continued)**

Unless otherwise noted these limits apply to the following: -40°C  $\leq$   $T_{J}$   $\leq$   $125^{\circ}C;$   $2.5V < V_{VDD}$  ,  $V_{OUTH} <$  18V; 0.7 V <  $V_{A}$  ,  $V_{C}$  ,  $V_{RVSNM} <$  18 V;  $V_{ENHS}$  =  $V_{ENOR}$  = 2 V,  $V_{OV}$  = 0 V;  $V_{BGATE}$ ,  $V_{HGATE}$ ,  $V_{PGHS}$ ,  $V_{STAT}$ ,  $V_{FLTb}$ , and  $V_{IMONBUF}$  are floating;  $C_{CP}$  = 100 nF,  $C_{INR}$  = 1 nF,  $C_{FLT}$  = 1 nF,  $R_{SET}$  = 44.2  $\Omega$ ,  $R_{IMON}$  = 2.98 k $\Omega$ ,  $R_{FSTP}$  = 200  $\Omega$ ,  $R_{RV}$  = 200  $\Omega$ , and  $R_{PLIM}$  = 52 k $\Omega$ .

|                               | PARAMETER                         | TEST CONDITION                                                                                                                                  | MIN    | TYP   | MAX    | UNIT |

|-------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|------|

| HOT SWAP G                    | ATE DRIVER (HGATE)                |                                                                                                                                                 |        |       |        |      |

|                               |                                   | 5 ≤ V <sub>VDD</sub> ≤ 16V; measure V <sub>HGATE-OUTH</sub>                                                                                     | 12     | 13.6  | 15.5   | V    |

| V <sub>HGATE</sub>            | HGATE output voltage              | 2.5V <v<sub>VDD &lt; 5V;<br/>16V <v<sub>VDD &lt; 20V measure V<sub>HGATE-OUTH</sub></v<sub></v<sub>                                             | 7      | 7.95  | 15     | V    |

| V <sub>HGATEmax</sub>         | Clamp voltage                     | Inject 10µA into HGATE, measure V <sub>(HGATE - OUTH)</sub>                                                                                     | 12     | 13.9  | 15.5   | V    |

| I <sub>HGATEsrc</sub>         | Sourcing current                  | V <sub>HGAT-OUTH</sub> = 2V-10V                                                                                                                 | 44     | 55    | 66     | μΑ   |

| I <sub>HGATEfastSink</sub>    | Sinking current for fast trip     | V <sub>HGATE-OUTH</sub> = 2V -15V; V <sub>(FSTP - SENM)</sub> = 20mV                                                                            | 0.45   | 1     | 1.6    | Α    |

| I <sub>HGATEsustSink</sub>    | Sustained sinking current         | Sustained, V <sub>HGATE-OUTH</sub> = 2V – 15V; V <sub>ENHS</sub> = 0                                                                            | 30     | 44    | 60     | mA   |

| CURRENT SE                    | NSE NEGATIVE INPUT (SENM)         | ,                                                                                                                                               |        |       |        |      |

| I <sub>SENM</sub>             | Input bias current                | V <sub>SENM</sub> = 12V                                                                                                                         |        | 15    | 20     | μΑ   |

| INRUSH TIME                   | R (TINR)                          | 1                                                                                                                                               | 1      |       |        |      |

| I <sub>TINRsrc</sub>          | Sourcing current                  | V <sub>TINR</sub> = 0V, In power limit or current limit                                                                                         | 8      | 10.25 | 12.5   | μΑ   |

| I <sub>TINRsink</sub>         | Sinking current                   | V <sub>TINR</sub> = 2V, In regular operation                                                                                                    | 1.5    | 2     | 2.5    | μA   |

| V <sub>TINRup</sub>           | Upper threshold voltage           | Raise V <sub>TINR</sub> until HGATE starts sinking                                                                                              | 1.3    | 1.35  | 1.4    | V    |

| V <sub>TINRIr</sub>           | Lower threshold voltage           | Raise $V_{TINR}$ to 2V. Reduce $V_{TINR}$ until $I_{TINR}$ is sourcing.                                                                         | 0.33   | 0.35  | 0.37   | V    |

| R <sub>TINR</sub>             | Bleed down resistance             | V <sub>VDD</sub> = 0V, V <sub>TINR</sub> = 2V                                                                                                   | 70     | 104   | 130    | kΩ   |

| I <sub>TINR-PD</sub>          | Pulldown current                  | V <sub>TINR</sub> = 2V, when V <sub>ENHS</sub> = 0V                                                                                             | 2      | 4.2   | 7      | mA   |

| V <sub>IMON,TINR</sub>        | See <sup>(2)</sup>                | $R_{PLIM} = 52k\Omega$ , $V_{SENM} = 12V$ , $V_{OUTH} = 0$ V. Raise IMON voltage and record IMON when TINR starts sourcing current              | 47.75  | 90    | 132.25 | mV   |

| $V_{\text{IMON,PL}}$          | See <sup>(2)</sup>                | $R_{PLIM}=52k\Omega,~V_{SENM}=12V,~V_{OUTH}=0~V.$ Raise IMON voltage and record IMON when $I_{HGATE}$ starts sinking current.                   | 114.75 | 135   | 155.25 | mV   |

| $\Delta V_{\text{IMON,TINR}}$ | See (2)                           | $\begin{split} R_{PLIM} &= 52k\Omega, \ V_{SENM} = 12V, \ V_{OUTH} = 0 \ V. \\ \Delta V_{IMON,TINR} &= V_{IMON,PL} - V_{IMON,TINR} \end{split}$ | 23     | 45    | 67     | mV   |

| FAULT TIMER                   | (TFLT)                            |                                                                                                                                                 |        |       |        |      |

| I <sub>TFLTsrc</sub>          | Sourcing current                  | V <sub>TFLT</sub> = 0V, PGHS is high and in overcurrent                                                                                         | 8      | 10.25 | 12.5   | μΑ   |

| I <sub>TFLTsink</sub>         | Sinking current                   | V <sub>TFLT</sub> = 2V, Not in overcurrent                                                                                                      | 1.5    | 2     | 2.5    | μΑ   |

| $V_{TFLTup}$                  | Upper threshold voltage           | Raise V <sub>TFLT</sub> until HGATE starts sinking                                                                                              | 1.3    | 1.35  | 1.4    | V    |

| R <sub>TFLT</sub>             | Bleed down resistance             | $V_{VDD} = 0V, V_{TFLT} = 2V$                                                                                                                   | 70     | 104   | 130    | kΩ   |

| I <sub>TFLT-PD</sub>          | Pulldown current                  | V <sub>TFLT</sub> = 2V, when V <sub>ENHS</sub> = 0V                                                                                             | 2      | 5.6   | 7      | mA   |

| HOT SWAP O                    | UTPUT (OUTH)                      |                                                                                                                                                 | •      |       |        |      |

| I <sub>OUTH</sub> , BIAS      | Input bias current                | V <sub>OUTH</sub> = 12V                                                                                                                         |        | 30    | 70     | μΑ   |

| CHARGE PUN                    | IP FOR BGATE (CP)                 |                                                                                                                                                 |        |       |        |      |

| I <sub>CP</sub>               | CP Equivalent charging resistance | V <sub>A</sub> = 12 V , 1mA CP current                                                                                                          | 5      | 8.7   | 12.5   | kΩ   |

|                               |                                   | Max(V <sub>A</sub> , V <sub>C</sub> , V <sub>VDD</sub> ) > 6 V, Measure V <sub>CP-A</sub>                                                       | 9      | 10    | 11     |      |

| $V_{CP}$                      | CP Output voltage                 | 6V > Max(V <sub>A</sub> , V <sub>C</sub> , V <sub>VDD</sub> ) > 4V, Measure V <sub>CP-A</sub>                                                   | 5      | 5.9   | 11     | V    |

|                               |                                   | $Max(V_A, V_C, V_{VDD}) = 2.5 \text{ V}, Measure V_{CP-A}$                                                                                      | 8      | 9.8   | 11     |      |

| BLOCKING/OI                   | RING GATE DRIVER (BGATE)          |                                                                                                                                                 |        |       |        |      |

|                               | DOATE Dulling tons                | V <sub>AC</sub> = 20mV, pulse                                                                                                                   |        | 30    |        | mA   |

| BGATE_CHRG                    | BGATE Pull up current             | V <sub>AC</sub> = 20mV, sustained                                                                                                               | 0.2    | 0.3   | 0.4    | mA   |

|                               | DOATE Circling and the            | Fast turnoff, V <sub>BGATE-A</sub> = 7V                                                                                                         | 0.4    | 0.9   | 1.4    | Α    |

| BGATEsustSink                 | BGATE Sinking current             | Sustained, V <sub>BGATE-A</sub> = 2V to 11V                                                                                                     | 19     | 35    | 65     | mA   |

<sup>(2)</sup> For more detail on the definition and usage of these parameters refer to section Using SoftStart – I<sub>HGATE</sub> and TINR Considerations.

## **Electrical Characteristics (continued)**

Unless otherwise noted these limits apply to the following:  $-40^{\circ}C \leq T_{J} \leq 125^{\circ}C; \ 2.5V < V_{VDD} \ , \ V_{OUTH} < 18V; \ 0.7\ V < V_{A} \ , \ V_{C} \ , \\ V_{RVSNM} < 18\ V; \ V_{ENHS} = V_{ENOR} = 2\ V, \ V_{OV} = 0\ V; \ V_{BGATE}, \ V_{HGATE}, \ V_{PGHS}, \ V_{STAT}, \ V_{FLTb}, \ and \ V_{IMONBUF} \ are floating; \ C_{CP} = 100\ nF, \\ C_{INR} = 1\ nF, \ C_{FLT} = 1\ nF, \ R_{SET} = 44.2\ \Omega, \ R_{IMON} = 2.98\ k\Omega, \ R_{FSTP} = 200\ \Omega, \ R_{RV} = 200\ \Omega, \ and \ R_{PLIM} = 52\ k\Omega.$

|                              | PARAMETER                                                | TEST CONDITION                                                                                                                     | MIN  | TYP  | MAX  | UNIT |

|------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| BLOCKING/OF                  | Ring ANODE (A)                                           |                                                                                                                                    |      |      |      |      |

| I <sub>A</sub>               | Input current <sup>(3)</sup>                             | 2.5 V ≤ V <sub>A</sub> ≤ 18V                                                                                                       |      |      | 3    | mA   |

| $V_{A\_UVLO}$                | Undervoltage lockout                                     | V <sub>A</sub> increasing and V <sub>VDD</sub> =V <sub>C</sub> =0.7V                                                               | 1.85 | 1.93 | 2.05 | V    |

| V <sub>A UVLO hyst</sub>     | Undervoltage lockout hysteresis                          | -                                                                                                                                  |      | 0.1  |      | V    |

|                              | Ring CATHODE (C)                                         |                                                                                                                                    |      |      |      |      |

| I <sub>C</sub>               | Input current <sup>(3)</sup>                             | 2.5 V ≤ V <sub>C</sub> ≤ 18V                                                                                                       |      |      | 3    | mA   |

| V <sub>C_UVLO</sub>          | Undervoltage lockout                                     | V <sub>C</sub> increasing and V <sub>DD</sub> =V <sub>A</sub> =0.7V                                                                | 1.85 | 1.93 | 2.05 | V    |

| V <sub>C_UVHyst</sub>        | Hysteresis                                               |                                                                                                                                    |      | 100  |      | mV   |

| V <sub>FWDTH</sub>           | Forward turn-on voltage                                  | Measure V <sub>AC</sub> when V <sub>BGATE ↑</sub>                                                                                  | 7.5  | 10   | 12.5 | mV   |

|                              | JT OF REVERSE VOLTAGE COMPARATOR (R)                     | VSNP)                                                                                                                              |      |      |      | -    |

| I <sub>RVSNP</sub>           | RVSNP Input bias current                                 | V <sub>RVSNP</sub> = 12V, sinking current; 0.7V < V <sub>A</sub> ,<br>V <sub>RVSNM</sub> < 20V                                     | 93   | 99   | 105  | μΑ   |

| V <sub>RVTRIP1</sub>         | Reverse Comparator Offset                                | R <sub>RV</sub> =10Ω, Measure V <sub>RVSNP-RVSNM</sub> , when BGATE↓                                                               | -1   | 0    | 1    | mV   |

|                              | PUT OF REVERSE VOLTAGE COMPARATOR (F                     |                                                                                                                                    |      |      |      |      |

| I <sub>RVSNM</sub>           | Leakage current                                          |                                                                                                                                    | -2   |      | 2    | μΑ   |

| FAULT INDICA                 | -                                                        |                                                                                                                                    |      |      |      |      |

| V <sub>OL_FLTb</sub>         | Output low voltage                                       | Sinking 2 mA                                                                                                                       |      | 0.11 | 0.25 | V    |

| I <sub>FLTb</sub>            | Input Leakage Current                                    | V <sub>FLTb</sub> = 0V, 30V                                                                                                        | -1   | 0    | 1    | μΑ   |

| V <sub>HSFLT_IMON</sub>      | V <sub>IMON</sub> threshold to detect Hot Swap FET short | V <sub>ENHS</sub> = 0V, Measured V <sub>IMON</sub> ↑ to GND when FLTb ↓                                                            | 88   | 101  | 115  | mV   |

| V <sub>HSFL_hyst</sub>       | Hysteresis                                               | ENTO 7 INVOICE 1                                                                                                                   |      | 25   |      | mV   |

| V <sub>BFET, OPEN, FLT</sub> | A-C threshold to detect OPEN Blocking/ORing              | V <sub>ENOR</sub> =3V, Measure V <sub>A-C</sub> to FLTb↓, V <sub>CP-A</sub> > 7V                                                   | 350  | 410  | 490  | mV   |

|                              |                                                          | Measure V <sub>CP-A</sub> ↓ when FLTb↓, 4V ≤ V <sub>VDD</sub> < 18V                                                                | 5    | 5.5  | 6    | V    |

| V <sub>CP_FLT</sub>          | CP fault threshold                                       | Measure V <sub>CP-A</sub> ↓ when FLTb↓, 2.5V < V <sub>VDD</sub> < 4V                                                               | 3.3  | 3.75 | 4.2  | V    |

|                              |                                                          | 4V ≤ V <sub>VDD</sub> < 18V                                                                                                        |      | 1.5  |      | V    |

| V <sub>CP, FLT, hyst</sub>   | Hysteresis                                               | 2.5V < V <sub>VDD</sub> < 4V                                                                                                       |      | 1.1  |      | V    |

| HOT SWAP PO                  | OWER GOOD OUTPUT (PGHS)                                  | 7                                                                                                                                  |      |      |      |      |

| V <sub>PGHSth</sub>          | PGHS Threshold                                           | Measure V <sub>SENM-OUTH</sub> ↓ when PGHS↑                                                                                        | 170  | 270  | 375  | mV   |

| V <sub>PGHShyst</sub>        | PGHS hysteresis                                          | V <sub>SENM</sub> -outh ↑                                                                                                          |      | 80   |      | mV   |

| V <sub>OL_PGHS</sub>         | PGHS Output low voltage                                  | Sinking 2mA                                                                                                                        |      | 0.11 | 0.25 | V    |

| I <sub>PGHS</sub>            | PHGS Input leakage current                               | V <sub>PGHS</sub> =0V to 30V                                                                                                       | -1   | 0    | 1    | μА   |

| STATUS INDIC                 | -                                                        | Tano                                                                                                                               |      |      |      |      |

|                              |                                                          | $4V \le V_{VDD} < 20V$ , Measure $V_{BGATE - A} \uparrow$ , when STAT $\uparrow$                                                   | 5    | 6    | 7    | ٧    |

| V <sub>STATon</sub>          | Status ON threshold                                      | 2.5V < V <sub>VDD</sub> < 4V , Measure V <sub>BGATE - A</sub> $\uparrow$ , when STAT $\uparrow$                                    | 3.6  | 4    | 4.4  | ٧    |

| V                            | Status OFF threshold                                     | $4V < V_{VDD} < 20V$ , Measure $V_{BGATE  -  A} \downarrow$ , when STAT $\downarrow$                                               | 4    | 5    | 6    | V    |

| V <sub>STAToff</sub>         | Glatus Of F tilleshold                                   | $2.5 \text{V} < \text{V}_{\text{VDD}} < 4 \text{V}$ , Measure $\text{V}_{\text{BGATE} - \text{A}} \uparrow$ , when STAT $\uparrow$ | 2    | 2.7  | 3.4  | ٧    |

| $V_{STAT,LOWoff}$            | STAT Output low voltage                                  | Sinking 2 mA                                                                                                                       |      | 0.11 | 0.25 | V    |

| I <sub>STAT,LEAK</sub>       | STAT Input leakage current                               | V <sub>STAT</sub> = 0 V, 30 V                                                                                                      | -1   | 0    | 1    | μΑ   |

| THERMAL SHU                  | JTDOWN (OTSD)                                            |                                                                                                                                    |      |      |      |      |

| T <sub>OTSD</sub>            | Thermal shutdown threshold                               | Temperature rising                                                                                                                 |      | 140  |      | °C   |

| T <sub>OTSD,HYST</sub>       | Hysteresis                                               |                                                                                                                                    |      | 10   |      | °C   |

<sup>(3)</sup> The TPS2474x is set up to be powered from A, C, or VDD depending on the biasing condition. See Internal Power ORing of TPS24740 To obtain the total current draw from A, C, VDD, and OUTH refer to the spec for Input Supply (VDD)..

## 8.6 Timing Requirements

| 8.6 Himi                 | ng Requirements                         |                                                                      |       |      |      |      |  |

|--------------------------|-----------------------------------------|----------------------------------------------------------------------|-------|------|------|------|--|

|                          | PARAMETER                               | TEST CONDITION                                                       | MIN   | TYP  | MAX  | UNIT |  |

| INPUT SUPF               | PLY (VDD)                               |                                                                      | Т     |      |      |      |  |

| DEGL <sub>UVLO</sub>     | UVLO deglitch                           | Both rising and falling                                              |       | 14   |      | μs   |  |

| HOT SWAP                 | FET ENABLE (ENHS)                       |                                                                      |       |      |      |      |  |

| DEGL <sub>ENHS</sub>     | Deglitch time                           | Both rising and falling                                              | 2.2   | 3.8  | 5.5  | μs   |  |

| BLOCKING                 | (ORING) FET ENABLE (ENOR)               |                                                                      |       |      |      |      |  |

| DEGL <sub>ENOR</sub>     | Deglitch time                           | Both rising and falling                                              | 1.7   | 3.5  | 5    | μs   |  |

| OVER VOLT                | AGE (OV)                                |                                                                      |       |      |      |      |  |

| DEGLOV                   | Deglitch time                           | Both rising and falling                                              | 2.2   | 3.9  | 5.7  | μs   |  |

| HOT SWAP                 | GATE DRIVER (HGATE)                     |                                                                      |       |      |      |      |  |

| t <sub>HGATEdly</sub>    | Turn on delay                           | CP ↑ to I <sub>HGATE</sub> sourcing                                  |       | 1.9  |      | ms   |  |

| FAST TRIP (              | (FSTP)                                  |                                                                      | •     |      |      |      |  |

|                          | - · · · · · · · · · · · · · · · · · · · | $V_{(FSTP - SENM)}$ : -5mV to 5mV, $C_{HGATE} = 0$ pF                |       | 600  |      | ns   |  |

| t <sub>FastOffDly</sub>  | Fast turn-off delay                     | V <sub>(FSTP - SENM)</sub> : -20mV to 20mV C <sub>HGATE</sub> = 0 pF |       | 300  |      |      |  |

| t <sub>FastOffDur</sub>  | Strong pull down current duration       |                                                                      | 53    | 63   | 73   | μs   |  |

| INRUSH TIM               | IER (TINR)                              |                                                                      | 1     |      |      |      |  |

| N <sub>RETRY</sub>       | Number of TINR cycles before retry      | TPS24741 only                                                        |       | 64   |      |      |  |

|                          | Retry duty cycle                        | T <sub>INR</sub> not connected to T <sub>FLT</sub>                   | 0.35% |      |      |      |  |

| RETRY <sub>DUTY</sub>    |                                         | T <sub>INR</sub> connected to T <sub>FLT</sub>                       |       | 0.7% |      |      |  |

| BLOCKING/                | OR <sub>ING</sub> GATE DRIVER (BGATE)   |                                                                      | "     |      |      |      |  |

| t <sub>FastOffDur</sub>  | Strong pull down current duration       |                                                                      | 10    | 15   | 20   | μs   |  |

| t <sub>FastOnDur</sub>   | Strong pull up current duration         |                                                                      | 10    | 20   | 30   | μs   |  |

|                          | IPUT OF REVERSE VOLTAGE COMPA           | ARATOR (RVSNP)                                                       |       |      |      |      |  |

| t <sub>FastOffDly</sub>  | Turn-off delay                          | $V_{(RVSNP - RVSNM)} = -5mV \rightarrow 5mV,$ $C_{BGATE} = 0 pF$     |       | 340  | 340  |      |  |

|                          |                                         | $V_{(RVSNP - RVSNM)} = -20mV \rightarrow +20mV,$ $C_{BGATE} = 0 pF$  |       | 150  |      | ns   |  |

| FAULT INDI               | CATOR (FLTb)                            |                                                                      |       |      |      |      |  |

| t <sub>FLT_degl</sub>    | HS / OR Fault Deglitch                  | Both HS and ORing faults                                             | 2.2   | 3.9  | 5.3  | ms   |  |

| t <sub>FLT_CP_degl</sub> | CP fault deglitch                       |                                                                      | 26.5  | 32   | 37.2 | ms   |  |

|                          | POWER GOOD OUTPUT (PGHS)                |                                                                      |       |      |      |      |  |

| t <sub>PGHSdegl</sub>    | PGHS deglitch time                      | Rising                                                               | 0.7   | 1    | 1.3  | ms   |  |

|                          |                                         | Falling                                                              | 7     | 8    | 9    |      |  |

| STATUS INC               | DICATOR (STAT)                          |                                                                      | 1     |      |      |      |  |

| t <sub>STATdegl</sub>    | STAT Delay (deglitch) time              | Rising or falling edge                                               | 0.4   | 0.95 | 1.5  | ms   |  |

Product Folder Links: TPS24740 TPS24741 TPS24742

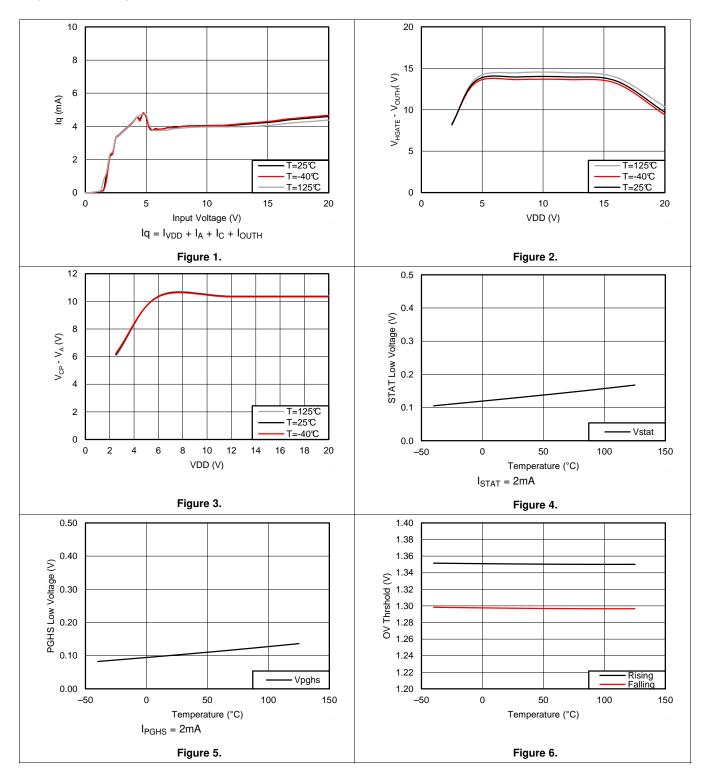

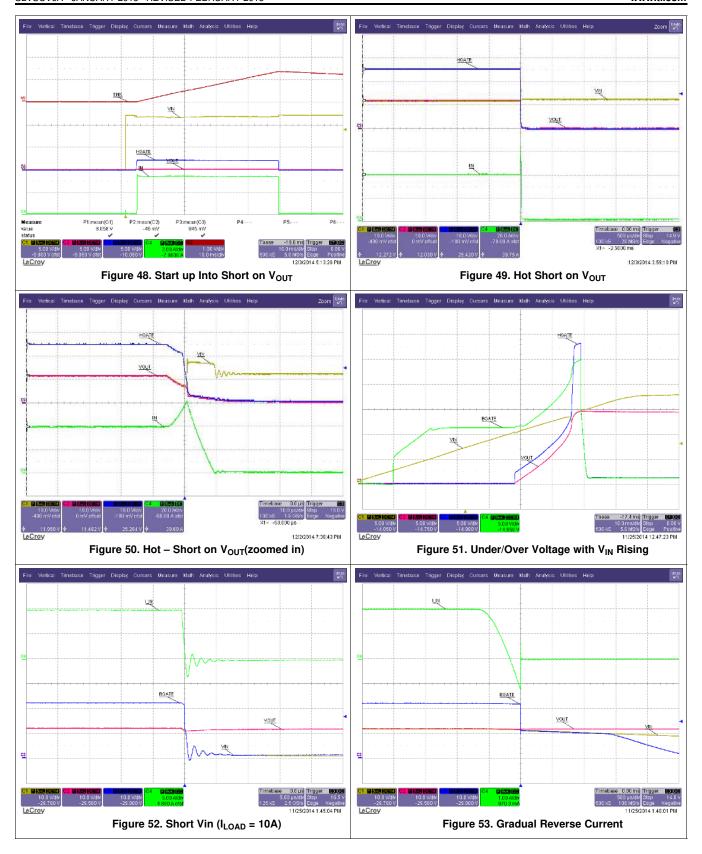

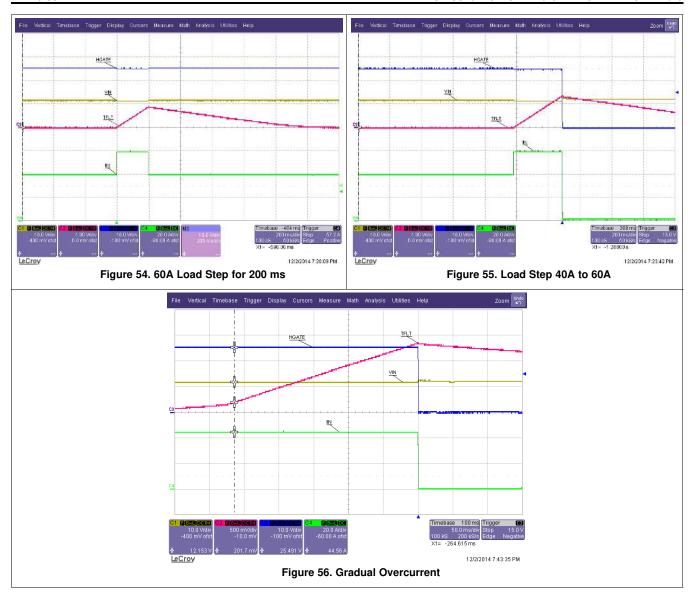

## 8.7 Typical Characteristics

Unless otherwise noted these limits apply to the following:  $V_{VDD} = V_A = V_C = V_{RVSNM} = V_{OUTH} = 12 \text{ V}; V_{ENHS} = V_{ENOR} = 2 \text{ V}, V_{OV} = 0 \text{ V}; V_{BGATE}, V_{HGATE}, V_{PGHS}, V_{STAT}, V_{FLTb}, and V_{IMONBUF}$  are floating;  $C_{CP} = 100 \text{ nF}, C_{INR} = 1 \text{ nF}, C_{FLT} = 1 \text{ nF}, R_{SET} = 44.2 \Omega, R_{IMON} = 2.98 \text{ k}\Omega, R_{FSTP} = 200 \Omega, R_{RV} = 200 \Omega, and R_{PLIM} = 52 \text{ k}\Omega.$

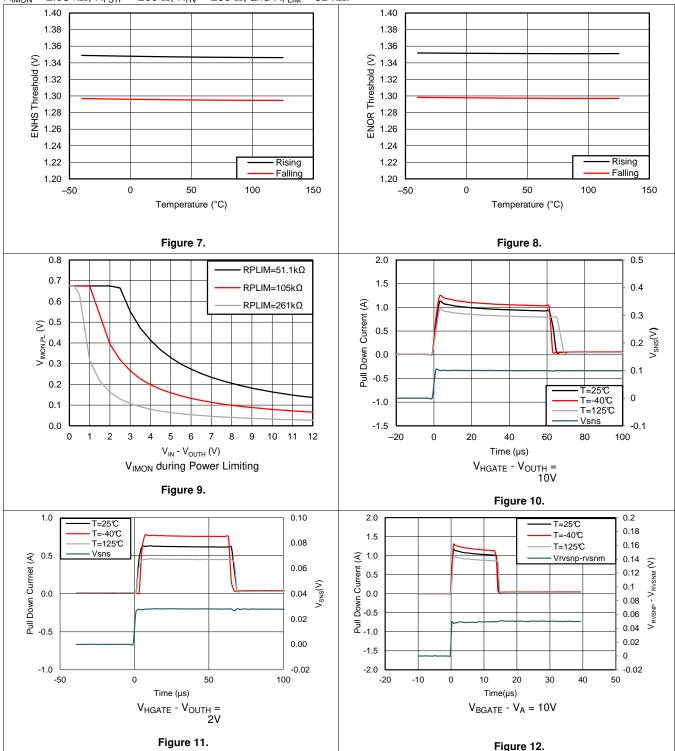

## **Typical Characteristics (continued)**

Unless otherwise noted these limits apply to the following:  $V_{VDD} = V_A = V_C = V_{RVSNM} = V_{OUTH} = 12 \text{ V}; V_{ENHS} = V_{ENOR} = 2 \text{ V}, V_{OV} = 0 \text{ V}; V_{BGATE}, V_{HGATE}, V_{PGHS}, V_{STAT}, V_{FLTb}, and V_{IMONBUF}$  are floating;  $C_{CP} = 100 \text{ nF}, C_{INR} = 1 \text{ nF}, C_{FLT} = 1 \text{ nF}, R_{SET} = 44.2 \Omega, R_{IMON} = 2.98 \text{ k}\Omega, R_{FSTP} = 200 \Omega, R_{RV} = 200 \Omega, and R_{PLIM} = 52 \text{ k}\Omega.$

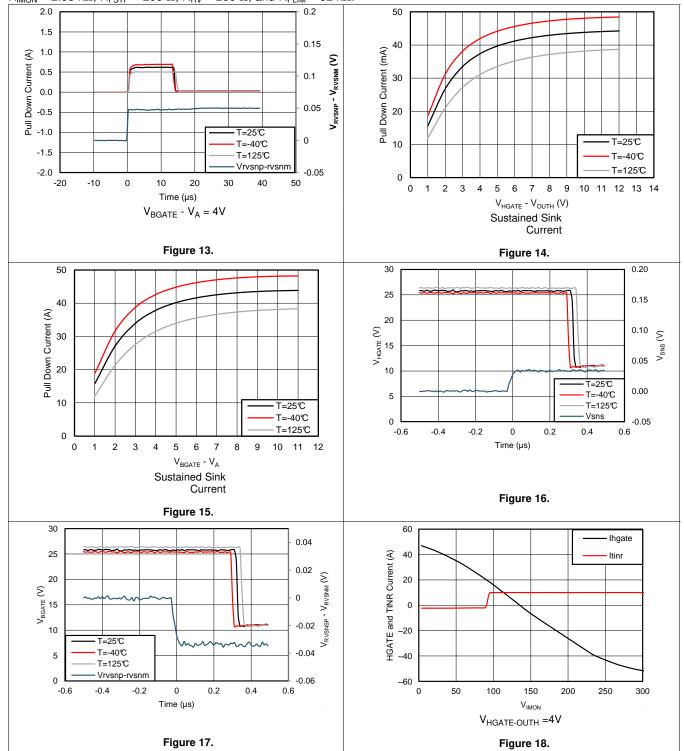

## **Typical Characteristics (continued)**

Unless otherwise noted these limits apply to the following:  $V_{VDD} = V_A = V_C = V_{RVSNM} = V_{OUTH} = 12 \text{ V}; V_{ENHS} = V_{ENOR} = 2 \text{ V}, V_{OV} = 0 \text{ V}; V_{BGATE}, V_{HGATE}, V_{PGHS}, V_{STAT}, V_{FLTb}, and V_{IMONBUF}$  are floating;  $C_{CP} = 100 \text{ nF}, C_{INR} = 1 \text{ nF}, C_{FLT} = 1 \text{ nF}, R_{SET} = 44.2 \Omega, R_{IMON} = 2.98 \text{ k}\Omega, R_{FSTP} = 200 \Omega, R_{RV} = 200 \Omega, and R_{PLIM} = 52 \text{ k}\Omega.$

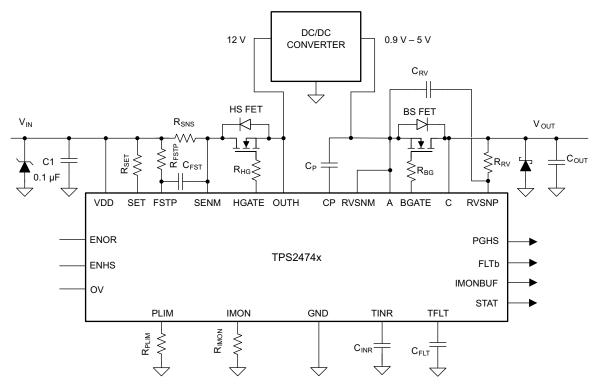

## 9 Detailed Description

#### 9.1 Overview

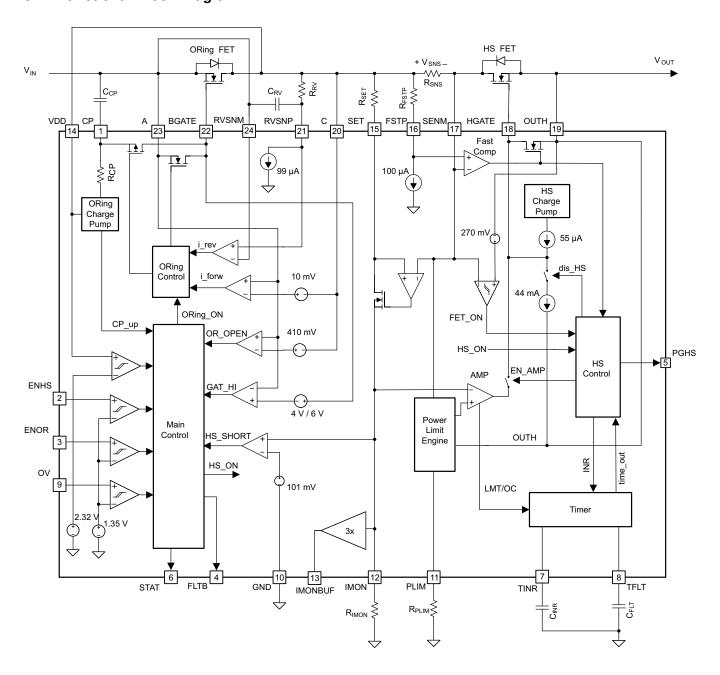

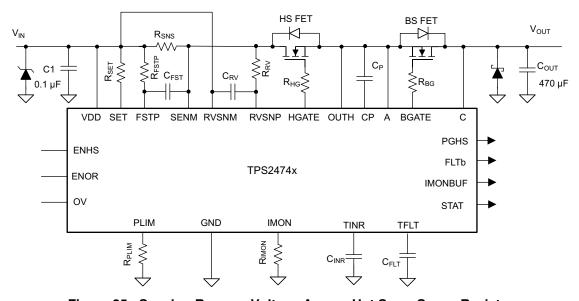

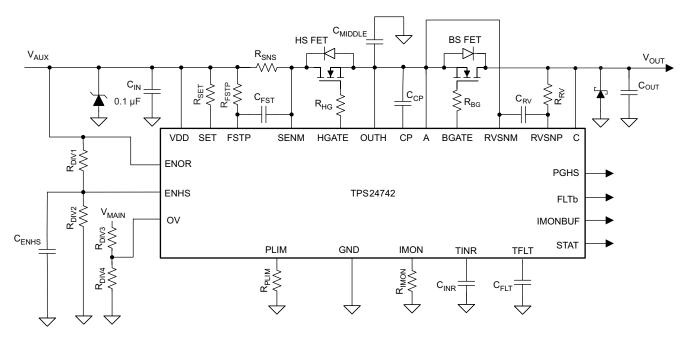

TPS2474x is a Hot Swap and ORing controller with many programmable settings. In addition the ORing and Hot Swap blocks are set-up independently, which allows for the interchangeable order of Hot Swap and ORing. For the ORing controller the RVSNM and RVSNP serve as a way to program the reverse voltage threshold and sense the reverse voltage. The Hot Swap features a programmable current limit, power limit, and fast trip threshold. It also has dual timers: one for inrush and one during over current faults. Finally it features an analog current monitor that can be used to provide current information to a microcontroller.

## 9.2 Functional Block Diagram

## 9.3 Feature Description

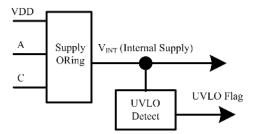

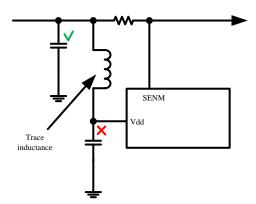

## 9.3.1 Internal Power ORing of TPS24740

The ORing function of the TPS2474x runs from an internal bus  $(V_{INT})$ , which is derived from ORing A, C, and VDD. This ensures that the TPS2474x can stay powered and functions properly, even if the input or output are shorted to GND. The ORing function's UVLO is derived based on the  $V_{INT}$  rail. This does mean that the part can draw up to 3 mA from the A or C pin. Hence it is recommended to keep traces to these pins fairly short and to avoid adding resistors in the path.

Figure 19. Power ORing

#### 9.3.2 Enable and Over-voltage Protection

Both the Hot Swap section and the ORing section can be independently enabled with the ENHS and ENOR pins respectively. The part is enabled when the pin voltage exceeds 1.35V and is disabled when the pin voltage falls under 1.3V providing 50mV of hysteresis. A resistor divider can be connected to these pins to turn on the TSP2474x at a certain bus voltage. Both the ORing and the Hot Swap FETs will be turned off if the OV pin exceeds 1.35V.

#### 9.3.3 Current Limit and Power Limit During Start-up

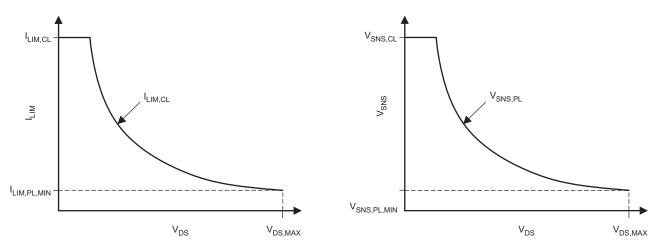

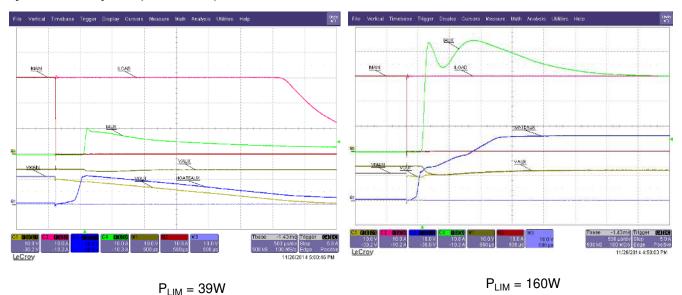

The current limit and power limit of the TPS2474x are programmable to protect the load, power supply, and the Hot Swap MOSFET. During start-up the active control loop will regulate the gate to ensure that the current through the MOSFET and the power dissipation of the MOSFET is below their respective pre-programmed thresholds. The maximum current allowed through the MOSFET ( $I_{LIM}$ ) is determined with Equation 1.  $I_{LIM,CL}$  is the programmed current limit,  $P_{LIM}$  is the programmed power limit, and  $V_{DS}$  is the drain to source voltage across the Hot Swap MOSFET.

$$I_{LIM} = MIN \left( I_{LIM,CL}, \frac{P_{LIM}}{V_{DS}} \right)$$

(1)

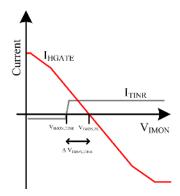

This results in an IV curve shown in Figure 20.  $I_{LIM,PL}$  denotes the maximum allowed MOSFET current ( $I_{DS}$ ) when the part is in power limit. As  $V_{DS}$  increases,  $I_{LIM,PL}$  decreases and  $I_{LIM,PL,MIN}$  denotes the lowest  $I_{LIM,PL}$ , which occurs at the largest  $V_{DS}$  ( $V_{DS,MAX}$ ). The TPS2474x enforce this by regulating the voltage across  $R_{SNS}$  ( $V_{SNS}$ ).  $V_{SNS,PL}$  decreases as  $V_{SNS}$  when power limiting is active. Similarly to  $I_{LIM,PL}$ ,  $V_{SNS,PL}$  decreases as  $V_{DS}$  increases and  $V_{SNS,PL,MIN}$  corresponds to the lowest  $V_{SNS,PL}$ , which occurs at  $V_{DS,MAX}$ .  $V_{SNS,CL}$  is a current limiting sense voltage, which is programmable in the TPS2474x.

Figure 20. Current vs V<sub>DS</sub> and V<sub>SNS</sub> vs V<sub>DS</sub> Programmed by Power Limit Engine

The current and power limit can be programmed using the equations below.

$$V_{SNS,CL} = \frac{0.675 \times R_{SET}}{R_{IMON}}$$

(2)

$$I_{LIM,CL} = \frac{V_{SNS,CL}}{R_{SNS}} = \frac{0.675 \times R_{SET}}{R_{IMON} \times R_{SNS}}$$

(3)

$$P_{LIM} = \frac{84375 \times R_{SET}}{R_{PLIM} \times R_{SNS} \times R_{IMON}}$$

(4)

Note, that the error is largest at  $V_{SNS,PL,MIN}$  due to offset of the internal amplifier. Also the operation at  $V_{DS,MAX}$  is most critical because it corresponds to the short circuit condition and has the biggest impact on start time. Thus it is critical to consider  $V_{SNS,PL,MIN}$  during design. Equation 5 shows the relationship of  $V_{SNS,PL,MIN}$  as a function of  $P_{LIM}$ ,  $I_{LIM,CL}$ ,  $V_{SNS,CL}$ , and  $V_{DS,MAX}$ . Note that  $I_{LIM,CL}$  and  $V_{DS,MAX}$  are usually determined by the system requirements. The designer will have control over  $P_{LIM}$  and  $V_{SNS,CL}$ . In general, there will be a desire to reduce the power limit to allow for smaller MOSFETs and to reduce the  $V_{SNS,CL}$  to improve efficiency (lower  $R_{SNS}$ ). However, this will also reduce  $V_{SNS,PL,MIN}$  and the designer should ensure that it's above the miminum recommended value of 1.5mV.

$$V_{SNS,PL,MIN} = \frac{P_{LIM} \times V_{SNS,CL}}{V_{DS,MAX} \times I_{LIM,CL}}$$

(5)

#### 9.3.4 Two Level Protection During Regular Operation

After the TPS2474x has gone through start-up it will no longer actively control HGATE. Instead it will run the timer when the current is between the current limit and the fast trip threshold. Once the timer has expired the gate will be pulled down. If the current ever exceeds the fast trip threshold, HGATE will be pulled down immediately.

#### 9.3.5 Dual Timer (TFLT and TINR)

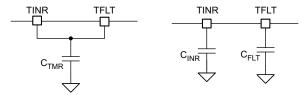

TPS2474x has two timer pins to allow the user to customize the protection. The TINR pin sources 10.25  $\mu$ A when the device is in start-up mode and is actively regulating the gate to limit the MOSFET power or current. It sinks 2  $\mu$ A otherwise. The TFLT pin sources 10.25  $\mu$ A when the device is in regular operation and the FET current exceeds the current limit. It sinks 2  $\mu$ A otherwise. If either of the timer pins exceeds 1.35, the TPS2474x times out. The TPS24740 and TPS24742 latches off. The TPS24741 goes through 64 cycles of TINR and attempts to start-up again.

Since the TINR usually runs when the MOSFET is being stressed, TINR should be sized to maintain the FET within its SOA. In general TFLT runs when the load is drawing more current than expected, which can stress the load and the power supply. Thus TFLT should be programmed to have the right protection settings for the power supply and the load. In some systems the load is allowed to draw current above the current limit for a prolonged time. In that case a large TFLT is required, but a short TINR may still be desired to minimize the worst case FET stress. In other applications a long TINR may be required to due to large downstream capacitances, but drawing excessive current from the power supply for more than 5ms is not desired. In that case a short TFLT and a long TINR should be used. Finally, many applications can use the same TINR and TFLT setting, in which case the pins can be tied together and a single capacitor can be used. The two different options are shown in Figure 21.

Figure 21. Timer Configurations

If two separate timer capacitors are used their values can be computed with Equation 6 and Equation 7:

$$C_{INR} = 7.59 \ \mu F \times T_{INR} \tag{6}$$

$$C_{FLT} = 7.59 \,\mu\text{F} \times T_{FLT} \tag{7}$$

If a single capacitor is used C<sub>TMR</sub> can be computed with Equation 8.

$$C_{TMB} = 6.11 \ \mu F \times T_{TMB} \tag{8}$$

#### 9.3.6 Using SoftStart – I<sub>HGATE</sub> and TINR Considerations

During start-up the TPS2474x regulates the HGATE to keep the FET power dissipation within  $P_{LIM}$ . This is accomplished by an amplifier that monitors the IMON voltage and an internal reference voltage. The TPS24740 will source current into HGATE if  $V_{IMON}$  is lower than the reference voltage and will sink current into HGATE if  $V_{IMON}$  is above the reference voltage. In steady state, the  $V_{IMON}$  will be regulated to the  $V_{IMON,PL}$  point, where  $I_{HGATE}$  equals zero. Note that  $V_{IMON,PL}$  is determined by  $I_{PLIM}$  and the  $I_{NENM-VOUTH}$ .

The same amplifier feeds into the inrush timer circuitry to run the timer when the part is in power limit. The  $V_{IMON}$  threshold at which the timer starts to source current is denoted as  $V_{IMON,\ TINR}$ . Note that  $V_{IMON,TINR}$  is lower than  $V_{IMON,PL}$  to account for tolerances and ensure that the timer is always active when the device is in power limit. The difference between the two thresholds is defined as  $\Delta V_{IMON,\ TINR}$ . A typical curve of the  $I_{HGATE}$  and  $I_{TINR}$  is available in the typical characteristics section.

Figure 22. I<sub>HGATE</sub> Current and TINR Relationship

It is critical to consider  $\Delta V_{IMON,\ TINR}$  and Figure 22 if a soft start circuit is used. Typically, the soft start is implemented by limiting the gate dv/dt with a capacitor, which in turn limits the inrush current to the output capacitor. Often times, the inrush current is kept below  $I_{LIM,PL}$  to keep the timer from running. Note that the  $I_{LIM,PL}$  is based on the  $V_{IMON,PL}$  threshold and thus TINR can be activated even if the inrush current is below  $I_{LIM,PL}$ . To prevent the timer from running unintentionally, it's important that the minimum power limit (typical  $P_{LIM}$  tolerance) is above  $P_{LIM,MIN,SS}$ , which can be computed as shown in Equation 9 below. As an example, consider the usage case where the maximum inrush current ( $I_{INR,MAX}$ ) is 2A, the maximum input voltage ( $V_{IN,MAX}$ ) is 13V and  $R_{SET}$ ,  $R_{IMON}$ , and  $R_{SNS}$  are  $100\Omega$ ,  $2.7k\Omega$ , and  $1m\Omega$  respectively. For that case the power limit should be set to at least 58.3 W +  $P_{LIM}$  tolerance to ensure that the inrush timer does not run.

$$P_{\text{LIM,MIN, SS}} = (I_{\text{INR,MAX}} + \Delta V_{\text{IMON,TINR,MAX}} \times \frac{R_{\text{SET}}}{R_{\text{IMON}} \times R_{\text{SNS}}}) \times V_{\text{IN,MAX}}$$

$$= \left(2A + 67\text{mV} \times \frac{100\Omega}{2.7\text{k}\Omega \times 1\text{m}\Omega}\right) \times 13\text{V} = 58.3\text{W}$$

(9)

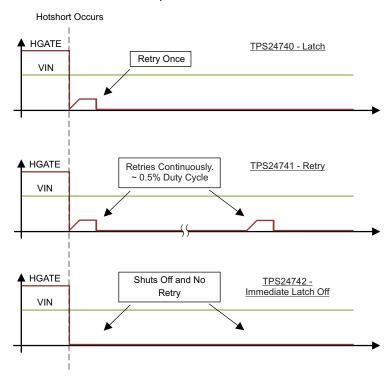

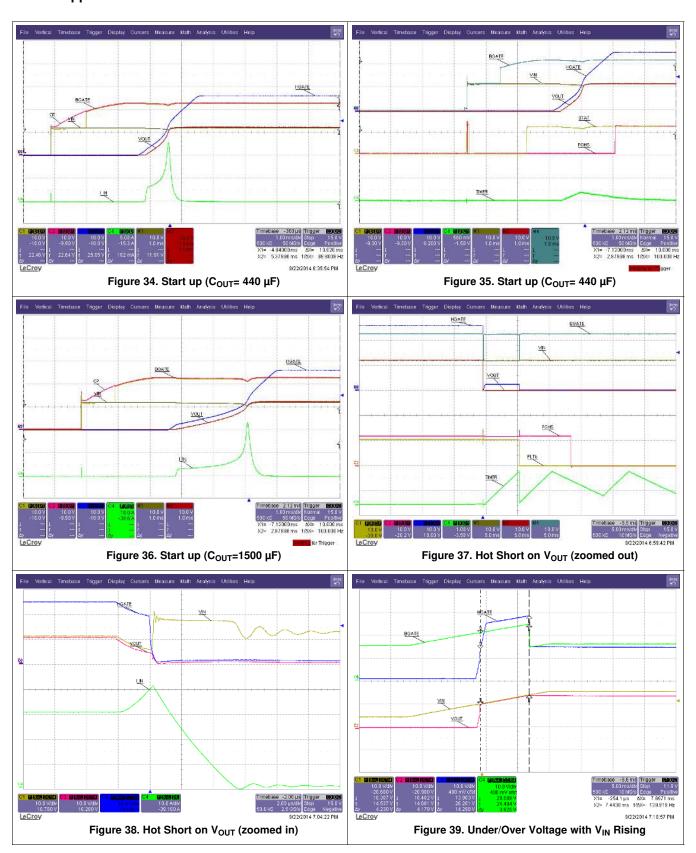

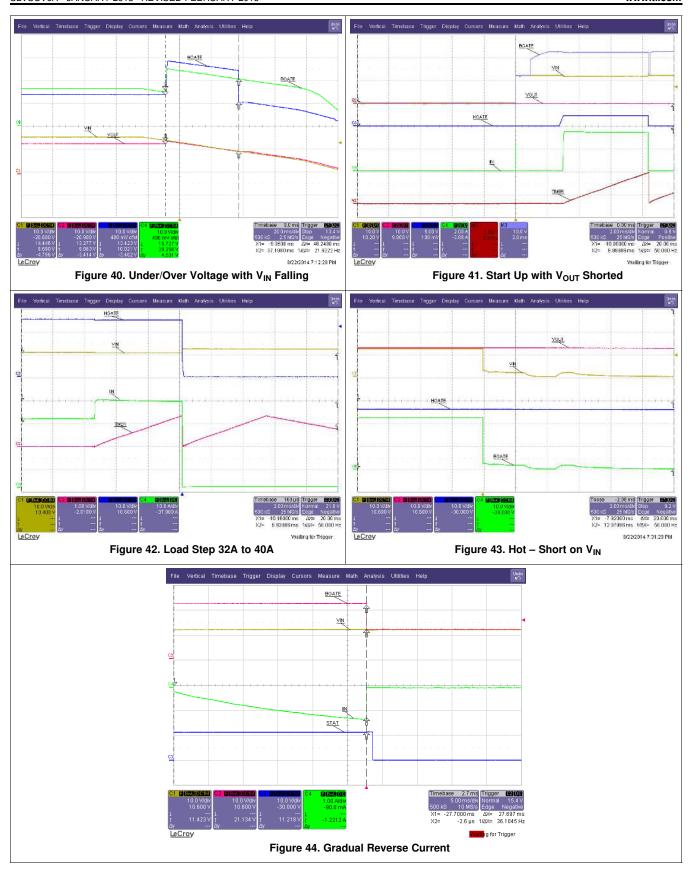

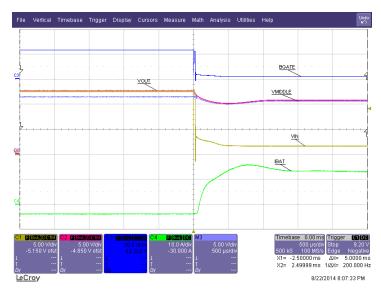

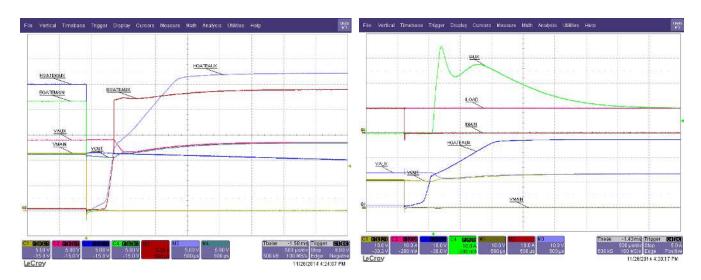

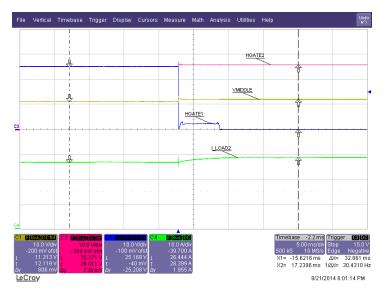

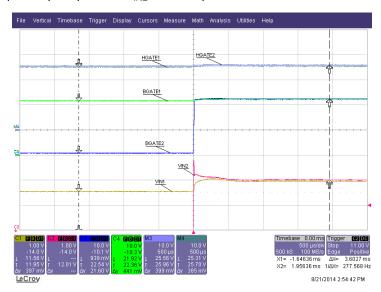

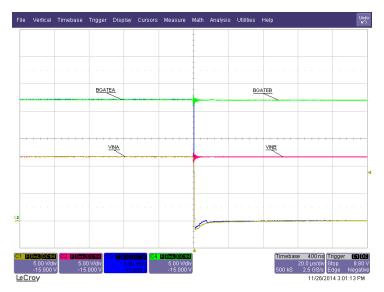

#### 9.3.7 Three Options for Response to a Fast Trip

The TPS24740, TPS24741, and TPS24742 have difference responses to a fast trip event to accommodate different design requirements. When the current exceeds the fast trip threshold, the gate is quickly pulled down to minimize damage that can be caused due to a short circuit. Figure 23 shows the response of the variate devices options to a Hotshort on the output. The TPS24740 (latch) attempts to re-start once after the hot-short is observed and then stay off. The TPS24741 continuously retries with a duty cycle of ~0.5% (0.7% if TFLT and TINR are connected, 0.35% if TFLT and TINR are not connected); and, the TPS24742 shuts off and never retries again. In general the TPS24742 (Fast/immediate Latch Off) places the least amount of stress on the MOSFET, but is the least likely to recover from a nuisance trip.

Figure 23. TPS24740/1/2 Response to a Short Circuit

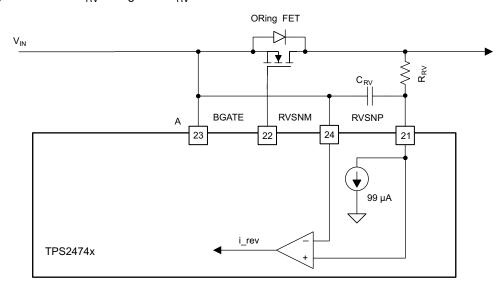

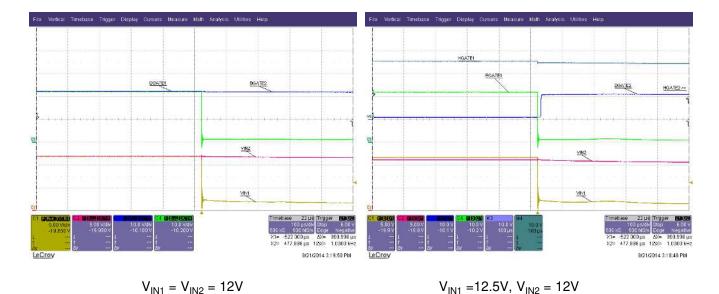

#### 9.3.8 Programmable Reverse Voltage Threshold

The TPS2474x has a programmable reverse voltage threshold. An internal comparator detects a reverse current condition when RVSNP is above RVSNM. This signal is used to shut off the ORing MOSFET.  $R_{RV}$  along with a 99 $\mu$ A current source pre-bias RVSNP to below the real source voltage of the MOSFET and effectively set the reverse voltage threshold.  $C_{RV}$  along with  $R_{RV}$  filters transients across the drain to source of the ORing FET.

Figure 24. Programming and Sensing Reverse Voltage

Note that the RVSNM and RVSNP can be connected at various places. One option is to connect it across the drain to source of the ORing FET (Figure 24), which would result in a reverse current threshold of  $V_{RV}/R_{DSON}$ . Another option is to connect across the  $R_{SNS}$  as shown in Figure 25. This could be useful if a precise threshold is desired and  $R_{SNS}$  is larger than the  $R_{DSON}$  of the ORing FET.

Figure 25. Sensing Reverse Voltage Across Hot Swap Sense Resistor

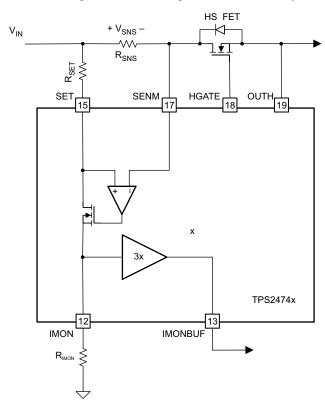

#### 9.3.9 Analog Current Monitor

The TPS2474x also features two analog current monitoring outputs: IMON and IMONBUF. Each has their own advantages and disadvantages. The IMON is more accurate, because it doesn't have the error added from the second stage. However it is a high impedance output and leakage current on that node would result in monitoring error. In addition it can only support 30pF of capacitance and its full scale range is 675mV (this is where current limit kicks in). The IMONBUF takes the IMON signal and buffers it 3x. This introduces more error, but the output is low impedance, has a larger full scale range, and can drive up to 100pF of capacitance.

Figure 26. Current Monitoring Circuitry

## 9.3.10 Power Good Flag

The TPS2474x has a power good flag, which should be used to turn on downstream DC/DC converters. This reduces the stress on the Hot Swap MOSFET during start-up. The PGHS pin of the TPS2474x is asserted (with 1 ms deglitch) when both:

- Hot Swap is enabled and

- VDS of Hot Swap MOSFET is below 240 mV.

PGHS is de-asserted (with 8 ms deglitch) when either:

- Hot Swap is disabled.

- VDS of Hot Swap MOSFET is above 310 mV

- In an overcurrent condition that causes the timer to time out and latch off.

#### 9.3.11 ORing MOSFET Status Indicator

The TPS2474x, features a STAT flag that indicates whether the BGATE (ORing FET driver) is ON or OFF. In general it is good practice to have the ORing FETs ON before drawing any significant load to prevent the ORing FET from overheating.

Copyright © 2015, Texas Instruments Incorporated

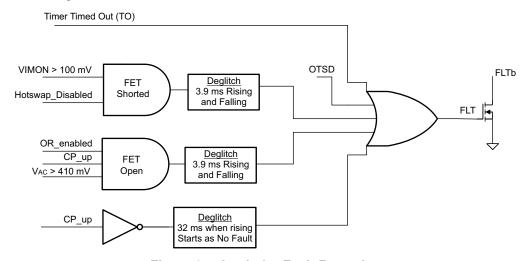

#### 9.3.12 Fault Reporting

TPS 2474x will assert a fault by pulling down on the FLTb pin if any of the following occur:

- Hot Swap MOSFET Shorted Fault (ENHS = LO, but VIMON > 101 mV)

- Hot Swap timer times out.

- ORing MOSFET Open Fault (ENOR = HI, CP up, but V<sub>AC</sub> > 410 mV)

- CP is down for more than 32 ms

- Over Temperature Shut Down (OTSD)

Figure 27 shows the logic for the fault conditions.

Figure 27. Logic for Fault Reporting

#### 9.4 Device Functional Modes

The Hot Swap and ORing section of the TPS2474x are for the most part independent. The only exception is that the Hot Swap is gated by the charge pump being up. This ensures that the ORing FET is ON before the Hot Swap turns on to avoid a possible glitch from a fast ORing turn on.

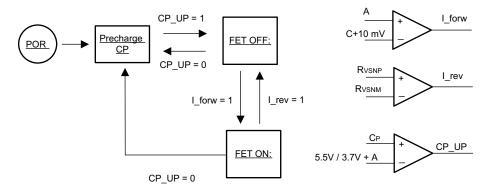

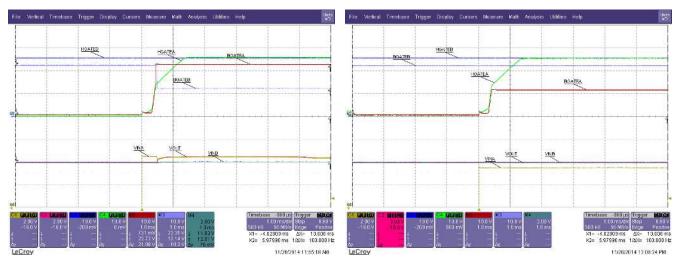

## 9.4.1 ORing Functional Modes

Figure 28 shows the state machine for the ORing portion of the controller. It has three modes listed below:

- Precharge CP: Here the TPS2474x charges the CP node before beginning regular operation. This state is entered after POR/UVLO or if the CP voltage falls below 3.7V. Whenever the CP voltage is above 5.5V the FET OFF state is entered

- **FET OFF:** In this state the ORing FET is OFF and is pulled down to A with a 35mA current source. If a forward voltage drop is detected across the FET ( $V_{AC} > 10 \text{mV}$ ) the TPS2474x enters the FET ON state. There is a 30mA fast pull up that lasts 20µs, followed by a sustained 0.3 mA pull up.

- **FET ON:** In this state the ORing FET is pulled up to the CP voltage. If reverse current is detected (RVSNP > RVSNM) the TPS2474x will enter the OFF state. There is a 0.9A pull down current that lasts 15  $\mu$ s, followed by a sustained 35mA pull down.

## **Device Functional Modes (continued)**

Figure 28. ORing State Machine

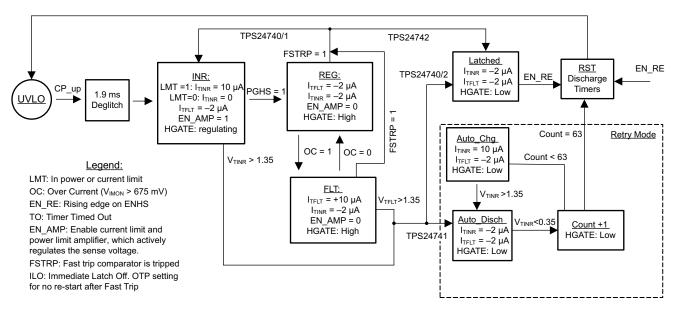

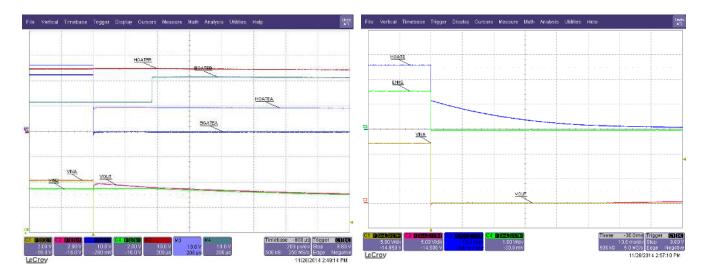

#### 9.4.2 Hot Swap Functional Modes

The state machine for the Hot Swap section is shown in Figure 29. After a POR / UVLO event the Hot Swap waits 1.9ms after the charge pump is up before starting up. Once operational the Hot Swap has the following functional modes:

- Inrush Mode (INR): In this state the Hot Swap controller is actively regulating the HGATE to meet the current limit and power limit settings. The inrush timer is running if the controller is in power or current limiting. If the inrush timer times out the gate will be pulled down. The TPS24740 and TPS24742 will go to latched mode and TPS24741 will go into retry mode.

- Regular Operation Mode (REG): In this mode everything is operating properly so both the timers are discharged and the HGATE is high. If there is an overcurrent condition (V<sub>SNS</sub> > V<sub>SNS,CL</sub>), the device will go into fault mode. If there is a fast trip condition ( $V_{SNS} > V_{FSTP}$ ), the gate will be pulled down with a 1A / 63 µs pulse. The TPS24742 will go to the latched state and the TPS24740 and TPS24741 will go back to inrush for a retry.

- Fault Mode (FLT): In this mode the TPS2474x runs the fault timer. Once the timer expires the TPS24740 and TPS24742 will go to latch mode while TPS24741 will go to retry mode. If the overcurrent condition is removed the controller will go back to the regular operation mode.

- Latched Mode (Latched): In the latched mode the HGATE is low, the timer is being discharged, and the FLTb is asserted. If there is a rising edge on ENHS the part will discharge the timers and go to the inrush mode.

- Retry Mode (Retry): Here the part charges and discharges the inrush timer 64 times before attempting another retry.

Product Folder Links: TPS24740 TPS24741 TPS24742

## **Device Functional Modes (continued)**

Figure 29. Hot Swap State Machine

## 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

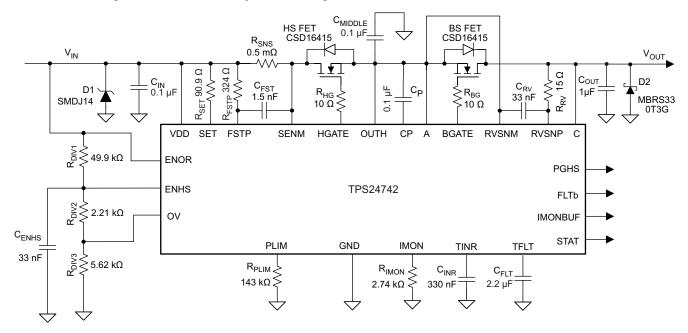

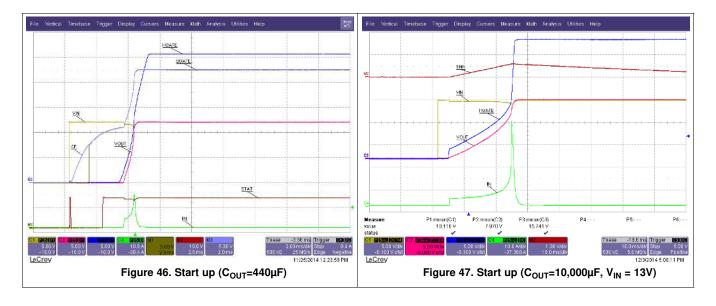

## 10.1 Application Information