# THCV219

V-by-One® HS High-speed video data transmitter

#### **General Description**

THCV219 is designed to support video data transmission between the host and display.

One high-speed lane can carry up to 32bit data and 3 bits of synchronizing signals at a pixel clock frequency from 7.5MHz to 75MHz.

It has one high-speed data lane and, maximum serial data rate is 3.0Gbps/lane.

| Width | Link  | TTL Clock Freq. |

|-------|-------|-----------------|

| 24bit | Si/So | 10MHz to 100MHz |

| 32bit | Si/So | 7.5MHz to 75MHz |

Si/So: Single-in/Single-out,

#### **Features**

- Color depth selectable: 24(8\*3)/32(10\*3)bit

- Single Link

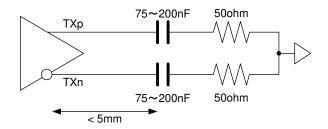

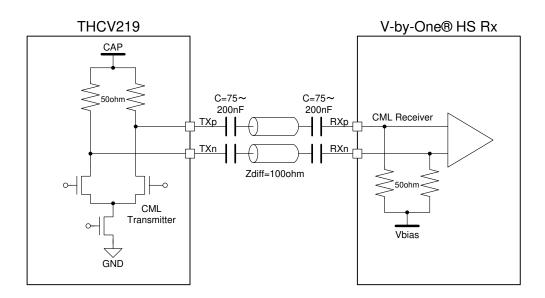

- AC coupling for high speed lines

- Wide Range Supply Voltage 2.3~3.6V

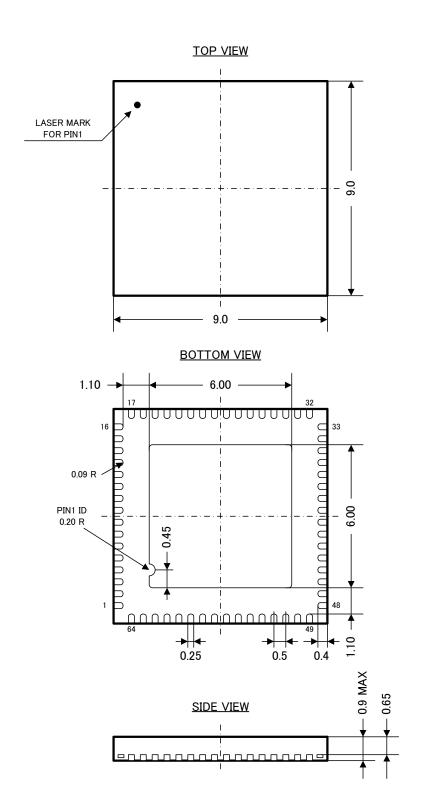

- Package: 64 pin QFN

- Wide frequency range

- Spread Spectrum Clocking tolerant Up to 30kHz/±0.5% (center spread)

- V-by-One® HS standard Version 1.4 compliant

- AEC-Q100 ESD Protection

#### **Block Diagram**

# Contents Page

| General Description                  |    |

|--------------------------------------|----|

| Features                             | 1  |

| Block Diagram                        | 1  |

| Pin Configuration                    | 3  |

| Pin Description                      | 4  |

| Functional Description               | 5  |

| Absolute Maximum Ratings*            |    |

| Recommended Operating Conditions     |    |

| Supply Current                       |    |

| Electrical Specifications            | 11 |

| AC Timing Diagrams and Test Circuits | 12 |

| Data Mapping                         | 15 |

| Package                              |    |

| Notices and Requests                 | 17 |

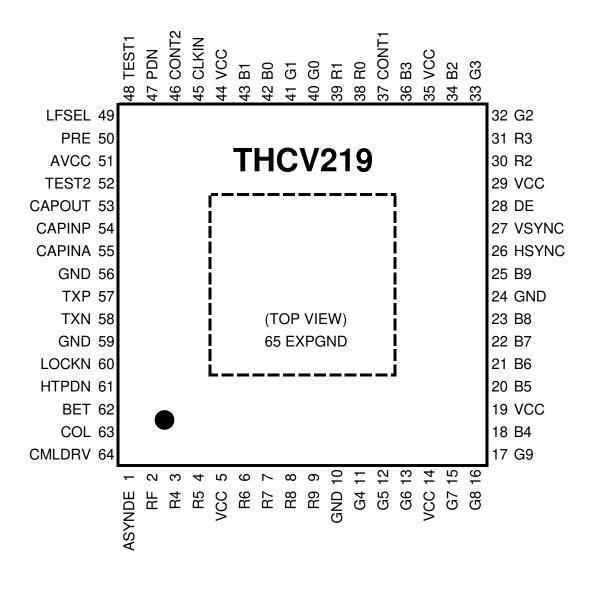

### Pin Configuration

### Pin Description

| R9-R0   9,87,6,4   3,31,30,39,38   3   pixel data inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pin Name | Pin#        | type* | Description                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|-------|----------------------------------------------------------------------|

| B9-B0   25,23,22,12,00   13,36,34,43,42   15,200   18,36,34,43,42   18,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,200   19,2   | R9-R0    |             | 13    | pixel data inputs                                                    |

| SP-BU   18,36,34,43,42   S   Discrete data inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | G9-G0    |             | В     | pixel data inputs                                                    |

| DE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | B9-B0    |             | 13    | pixel data inputs                                                    |

| VSYNC   27   13   Vsync input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CONT1,2  | 37,46       | 13    | User defined data inputs. Active only in 32bit mode.                 |

| HSYNC CLKIN 45 B Pixel clock input TXN/P 58.57 CO High-speed CML signal output.  LOCKN 60 BL Lock detect input. Must be connected to Rx LOCKN with a 10kΩ pull-up resistor.  HtPDN 61 BL Wust be connected to Rx HTPDN with a 10kΩ pull-up resistor.  Hot plug detect input. Must be connected to Rx HTPDN with a 10kΩ pull-up resistor.  PDN 47 BL Power down input. H: Normal operation L: Power down Pre-Emphasis level select input. H: Normal operation L: Pre-Emphasis Disable  CMLDRV 64 B CMLDRV 64 B CML Outputs drive strength select input. H: Normal drive strength L: Weak drive strength  COL** 63 B Data width setting. H: 24bit L: 32bit Frequency range setting. H: Cow frequency operation L: Normal Operation  Asynchronous DE input.  AsynDE BET 62 B Field-BET entry. H: Field BET operation (ASYNDE function disable) L: De input invert operation (ASYNDE function enable) Input clock triggering edge select input for latching input data H: Rising edge L: Falling edge Field-BET entry. H: Field BET Operation L: Normal Operation.  TEST1 48 TEST1 48 Test pin, must be "L" for normal operation.  TEST2 52 Test pin, must be "L" for normal operation.  Decoupling capacitor pins.  CAPINP 54 - Reference Input for PLL circuit.Must be tied CAPOUT.  CAPINA 55 - Reference Input for PLL circuit.Must be tied CAPOUT.  PS Analog Power supply Pin GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DE       | 28          | 13    | DE input                                                             |

| CLKIN 45 IS Pixel clock input  TXMP 58,57 CO High-speed CML signal output.  LOCKN 60 ISL Lock detect input. Must be connected to Rx LOCKN with a 10kΩ pull-up resistor.  HTPDN 61 ISL Hot plug detect input. Must be connected to Rx HTPDN with a 10kΩ pull-up resistor.  PDN 47 ISL Hot plug detect input. Must be connected to Rx HTPDN with a 10kΩ pull-up resistor.  PPN 47 ISL Hot plug detect input. Hot plug detect i | VSYNC    | 27          | 13    | Vsync input                                                          |

| TXNP 58,57 CO High-speed CML signal output.  LOCKN 60 BL Lock detect input. Must be connected to Rx LOCKN with a 10kΩ pull-up resistor.  HTPDN 61 BL Hot plug detect input. Must be connected to Rx HTPDN with a 10kΩ pull-up resistor.  PDN 47 BL Hot plug detect input. Must be connected to Rx HTPDN with a 10kΩ pull-up resistor.  PDN 47 BL Hormal operation L: Power down  PRE 50 BL Pre-Emphasis level select input. H: Normal operation L: Pre-Emphasis Disable  CMLDRV 64 BL CML Outputs drive strength select input. H: Normal operation Bata width setting. H: 24bit L: 32bit  LFSEL** 49 BL Frequency range setting. H: Low frequency operation L: Normal Operation  ASYNDE 1 BL Hormal operation (ASYNDE function disable) L: DE input invert operation (ASYNDE function enable) Input clock triggering edge select input for latching input data H: Rising edge L: Falling edge  BET 62 BL Field-BET entry. H: Field BET Operation L: Normal Operation.  TEST1 48 - Test pin, must be "L" for normal operation.  Decoupling capacitor pins.  CAPOUT 53 - Tiest pin, must be "L" for normal operation.  Decoupling capacitor pins.  This pin should be connected to external decoupling capacitors. Recommended Capacitance is 2.2uF  CAPINP 54 - Reference Input for Analog circuit.Must be tied CAPOUT.  VCC 51,41,19,29, 35,44  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | HSYNC    | 26          | 13    | Hsync input                                                          |

| LOCKN 60 I3L Lock detect input.  Must be connected to Rx LOCKN with a 10kΩ pull-up resistor.  HTPDN 61 I3L Must be connected to Rx HTPDN with a 10kΩ pull-up resistor.  PDN 47 I3L Ho read power down input.  H: Normal operation L: Power down  Pre-Emphasis level select input.  H: Pre-Emphasis Enable L: Pre-Emphasis Disable  CMLDRV 64 I3 CML Outputs drive strength select input.  H: Normal drive strength L: Weak drive strength  Data width setting.  H: 24bit L: 32bit  Frequency range setting.  H: Low frequency operation L: Normal Operation  Asynchronous DE input.  H: Normal operation (ASYNDE function disable)  L: DE input invert operation (ASYNDE function enable)  Input clock triggering edge select input for latching input data  H: Rising edge L: Falling edge  Field-BET entry.  H: Field BET operation L: Normal Operation  TEST1 48 - Test pin, must be "L" for normal operation.  TEST2 52 - Test pin, must be "L" for normal operation.  Decoupling capacitor pins.  This pin should be connected to external decoupling capacitors.  Recommended Capacitance is 2.2uF  CAPINP 54 - Reference Input for PLL circuit. Must be tied CAPOUT.  VCC 514,19,29, 35,44 PS Digital Power supply Pins  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CLKIN    | 45          | 13    | Pixel clock input                                                    |

| LOCKN 60 I3L Lock detect input. Must be connected to Rx LOCKN with a 10kΩ pull-up resistor.  HTPDN 61 I3L Must be connected to Rx HTPDN with a 10kΩ pull-up resistor.  PDN 47 I3L Ht. Normal operation L: Power down PRE 50 I3 Pre-Emphasis level select input. H: Normal operation L: Pre-Emphasis Disable  CMLDRV 64 I3 CML Outputs drive strength select input. H: Normal drive strength L: Weak drive strength  Data width setting. H: 24bit L: 32bit  Frequency range setting. H: Low frequency operation L: Normal Operation Asynchronous DE input. H: Normal operation (ASYNDE function disable) L: DE input invert operation (ASYNDE function enable) Input clock triggering edge select input for latching input data H: Rising edge L: Falling edge  BET 62 I3 Field-BET entry. H: Field BET Operation L: Normal Operation  TEST1 48 - Test pin, must be "L" for normal operation.  TEST2 52 - Test pin, must be "L" for normal operation.  CAPOUT 53 - Test pin, must be "L" for normal operation.  CAPOUT 54 - Reference Input for PLL circuit. Must be tied CAPOUT.  CAPINP 54 - Reference Input for PLL circuit. Must be tied CAPOUT.  VCC 5,14,19,29, 35,44 PS Digital Power supply Pins  AVCC 51 PS Analog Power supply Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TXN/P    | 58,57       | CO    | High-speed CML signal output.                                        |

| HTPDN 61 3L Hot plug detect input. Must be connected to Rx HTPDN with a 10kΩ pull-up resistor.  PDN 47 3L Power down input. H: Normal operation L: Power down  PRE 50 13 Pre-Emphasis level select input. H: Pre-Emphasis Disable  CMLDRV 64 13 CML Outputs drive strength select input. H: Normal drive strength select input. H: Normal drive strength L: Weak drive strength  COL** 63 13 Data width setting. H: 24bit L: 32bit  LFSEL** 49 13 Frequency range setting. H: Low frequency operation L: Normal Operation  ASYNDE 1 13 H: Normal operation (ASYNDE function disable)  LDE input invert operation (ASYNDE function enable)  Input clock triggering edge select input for latching input data H: Rising edge L: Falling edge  Field-BET entry.  EBET 62 13 H: Field BET Operation L: Normal Operation  TEST1 48 - Test pin, must be "L" for normal operation.  TEST2 52 - Test pin, must be "L" for normal operation.  CAPOUT 53 - This pin should be connected to external decoupling capacitors. Recommended Capacitance is 2.2uF  CAPINP 54 - Reference Input for PLL circuit.Must be tied CAPOUT.  VCC 514, 19,29, 35,44 PS Digital Power supply Pin  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LOCKN    | 60          | I3L   | ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' '                                |

| PDN 47 I3L Power down input. H: Normal operation L: Power down  PRE 50 I3 Pre-Emphasis level select input. H: Pre-Emphasis Disable  CMLDRV 64 I3 CML Outputs drive strength select input. H: Normal drive strength L: Weak drive strength  COL** 63 I3 Data width setting. H: 24bit L: 32bit  LFSEL** 49 I3 Frequency range setting. H: Low frequency operation L: Normal Operation  ASYNDE I I3 H: Normal operation (ASYNDE function disable) L: DE input invert operation (ASYNDE function enable)  RF 2 I3 Input clock triggering edge select input for latching input data H: Rising edge L: Falling edge  BET 62 I3 Field-BET entry. H: Field BET Operation L: Normal Operation  TEST1 48 - Test pin, must be "L" for normal operation.  CAPOUT 53 - This pin should be connected to external decoupling capacitors. Recommended Capacitance is 2.2uF  CAPINP 54 - Reference Input for PLL circuit.Must be tied CAPOUT.  VCC 51,4,19,29, 35,44 PS Digital Power supply Pins  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | HTPDN    | 61          | I3L   | Hot plug detect input.                                               |

| PRE 50 B Pre-Emphasis level select input. H : Pre-Emphasis Enable L : Pre-Emphasis Disable  CML Outputs drive strength select input. H : Normal drive strength select input. H : Normal drive strength L : Weak drive strength  Data width setting. H : 24bit L : 32bit  LFSEL**  49 B Frequency range setting. H : Low frequency operation L: Normal Operation  Asynchronous DE input. H : Normal operation (ASYNDE function disable) L: DE input invert operation (ASYNDE function enable)  RF 2 B Input lock triggering edge select input for latching input data H : Rising edge L : Falling edge H : Field BET Operation L : Normal Operation  TEST1 48 - Test pin, must be "L" for normal operation.  TEST2 52 - Test pin, must be "L" for normal operation.  CAPOUT 53 - This pin should be connected to external decoupling capacitors. Recommended Capacitance is 2.2uF  CAPINP 54 - Reference Input for PLL circuit.Must be tied CAPOUT.  VCC 514,19,29, 35,44  AVCC 51 PS Analog Power supply Pin  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PDN      | 47          | I3L   | Power down input.                                                    |

| CMLDRV 64 B CML Outputs drive strength select input. H: Normal drive strength L: Weak drive strength Data width setting. H: 24bit L: 32bit  EFSEL** 49 B Frequency range setting. H: Low frequency operation L: Normal Operation  AsynDE 1 B H: Normal operation (ASYNDE function disable) L: DE input invert operation (ASYNDE function enable)  RF 2 B Input clock triggering edge select input for latching input data H: Rising edge L: Falling edge  BET 62 B Field-BET entry. H: Field BET Operation L: Normal Operation  TEST1 48 - Test pin, must be "L" for normal operation.  TEST2 52 - Test pin, must be "L" for normal operation.  CAPOUT 53 - This pin should be connected to external decoupling capacitors. Recommended Capacitance is 2.2uF  CAPINP 54 - Reference Input for PLL circuit.Must be tied CAPOUT.  CAPINA 55 - Reference Input for Analog circuit.Must be tied CAPOUT.  VCC 5,14,19,29, 35,44 PS Digital Power supply Pin  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PRE      | 50          | 13    | Pre-Emphasis level select input.                                     |

| COL** 63 B Data width setting. H: 24bit L: 32bit  LFSEL** 49 B Frequency range setting. H: Low frequency operation L: Normal Operation  AsynDE 1 B H: Normal operation (AsynDE function disable) L: DE input invert operation (AsynDE function enable)  RF 2 B Input clock triggering edge select input for latching input data H: Rising edge L: Falling edge  BET 62 B Field-BET entry. H: Field BET Operation L: Normal Operation  TEST1 48 - Test pin, must be "L" for normal operation.  TEST2 52 - Test pin, must be "L" for normal operation.  CAPOUT 53 - This pin should be connected to external decoupling capacitors. Recommended Capacitance is 2.2uF  CAPINP 54 - Reference Input for PLL circuit.Must be tied CAPOUT.  CAPINA 55 - Reference Input for Analog circuit.Must be tied CAPOUT.  VCC 5,14,19,29, 35,44 PS Digital Power supply Pins  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CMLDRV   | 64          | 13    | CML Outputs drive strength select input.                             |

| LFSEL**  49  13  Frequency range setting. H: Low frequency operation L: Normal Operation  Asynchronous DE input. H: Normal operation (ASYNDE function disable) L: DE input invert operation (ASYNDE function enable)  Input clock triggering edge select input for latching input data H: Rising edge L: Falling edge  BET  62  13  BET  62  13  Frequency range setting. H: Low frequency operation L: Normal Operation  Input clock triggering edge select input for latching input data H: Rising edge L: Falling edge  Field-BET entry. H: Field BET Operation L: Normal Operation  TEST1  48  - Test pin, must be "L" for normal operation.  Decoupling capacitor pins.  CAPOUT  53  - This pin should be connected to external decoupling capacitors. Recommended Capacitance is 2.2uF  CAPINA  55  - Reference Input for PLL circuit.Must be tied CAPOUT.  VCC  5,14,19,29, 35,44  PS  Digital Power supply Pins  AVCC  51  PS  Analog Power supply Pin  GND  10,24,56,59  PS  Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | COL**    | 63          | 13    | Data width setting.                                                  |

| ASYNDE 1 1   13   Asynchronous DE input. H: Normal operation (ASYNDE function disable) L: DE input invert operation (ASYNDE function enable)  RF 2   13   Input clock triggering edge select input for latching input data H: Rising edge L: Falling edge  BET 62   13   Field BET operation L: Normal Operation  TEST1 48 - Test pin, must be "L" for normal operation.  TEST2 52 - Test pin, must be "L" for normal operation.  CAPOUT 53 - This pin should be connected to external decoupling capacitors. Recommended Capacitance is 2.2uF  CAPINA 55 - Reference Input for PLL circuit.Must be tied CAPOUT.  VCC 5,14,19,29, 35,44   PS Digital Power supply Pins  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LFSEL**  | 49          | 13    | Frequency range setting.                                             |

| H: Rising edge L: Falling edge  BET 62 13 Field-BET entry. H: Field BET Operation L: Normal Operation  TEST1 48 - Test pin, must be "L" for normal operation.  TEST2 52 - Test pin, must be "L" for normal operation.  CAPOUT 53 - This pin should be connected to external decoupling capacitors.  Recommended Capacitance is 2.2uF  CAPINP 54 - Reference Input for PLL circuit.Must be tied CAPOUT.  CAPINA 55 - Reference Input for Analog circuit.Must be tied CAPOUT.  VCC 5,14,19,29, 35,44 PS Digital Power supply Pins  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ASYNDE   | 1           | 13    | Asynchronous DE input. H: Normal operation (ASYNDE function disable) |

| BET 62   B Field-BET entry. H : Field BET Operation L : Normal Operation  TEST1 48 - Test pin, must be "L" for normal operation.  TEST2 52 - Test pin, must be "L" for normal operation.  Decoupling capacitor pins.  CAPOUT 53 - This pin should be connected to external decoupling capacitors. Recommended Capacitance is 2.2uF  CAPINP 54 - Reference Input for PLL circuit.Must be tied CAPOUT.  CAPINA 55 - Reference Input for Analog circuit.Must be tied CAPOUT.  VCC 5,14,19,29, 35,44 PS Digital Power supply Pins  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RF       | 2           | 13    |                                                                      |

| TEST1 48 - Test pin, must be "L" for normal operation.  TEST2 52 - Test pin, must be "L" for normal operation.  Decoupling capacitor pins.  This pin should be connected to external decoupling capacitors. Recommended Capacitance is 2.2uF  CAPINP 54 - Reference Input for PLL circuit.Must be tied CAPOUT.  CAPINA 55 - Reference Input for Analog circuit.Must be tied CAPOUT.  VCC 5,14,19,29, 35,44 PS Digital Power supply Pins  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BET      | 62          | 13    | · · · · · · · · · · · · · · · · · · ·                                |

| CAPOUT  53  - This pin should be connected to external decoupling capacitors. Recommended Capacitance is 2.2uF  CAPINP  54  - Reference Input for PLL circuit.Must be tied CAPOUT.  CAPINA  55  - Reference Input for Analog circuit.Must be tied CAPOUT.  VCC  5,14,19,29, 35,44  PS  Digital Power supply Pins  AVCC  51  PS  Analog Power supply Pin  GND  10,24,56,59  PS  Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TEST1    | 48          | -     |                                                                      |

| CAPOUT  53  - This pin should be connected to external decoupling capacitors.  Recommended Capacitance is 2.2uF  CAPINP  54  - Reference Input for PLL circuit.Must be tied CAPOUT.  CAPINA  55  - Reference Input for Analog circuit.Must be tied CAPOUT.  VCC  5,14,19,29, 35,44  PS  Digital Power supply Pins  AVCC  51  PS  Analog Power supply Pin  GND  10,24,56,59  PS  Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TEST2    | 52          | -     | Test pin, must be "L" for normal operation.                          |

| CAPINA 55 - Reference Input for Analog circuit.Must be tied CAPOUT.  VCC 5,14,19,29, 35,44 PS Digital Power supply Pins  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CAPOUT   | 53          | -     | This pin should be connected to external decoupling capacitors.      |

| CAPINA 55 - Reference Input for Analog circuit.Must be tied CAPOUT.  VCC 5,14,19,29, 35,44 PS Digital Power supply Pins  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CAPINP   | 54          | -     | Reference Input for PLL circuit.Must be tied CAPOUT.                 |

| AVCC 35,44 PS Digital Power supply Pins  AVCC 51 PS Analog Power supply Pin  GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CAPINA   | 55          | -     | Reference Input for Analog circuit.Must be tied CAPOUT.              |

| AVCC 51 PS Analog Power supply Pin GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VCC      |             | PS    | Digital Power supply Pins                                            |

| GND 10,24,56,59 PS Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AVCC     |             | PS    | Analog Power supply Pin                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GND      | 10,24,56,59 | PS    |                                                                      |

| LAI GIAD   00   1 0   Exposed 1 ad Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EXPGND   | 65          | PS    | Exposed Pad Ground                                                   |

<sup>\*</sup>type symbol

I3=3.3v CMOS input, I3L=Low Speed 3.3v CMOS input

CO=CML output, PS=Power Supply

<sup>\*\*</sup>COL, LFSEL pin

COL pin and/or LFSEL pin level shall not be changed during operation. If ether pin level is changed during operation, PDN shall be toggled (H-> L -> H) after the change.

### **Functional Description**

#### **Functional Overview**

With V-by-One® HS proprietary encoding scheme and CDR (Clock and Data Recovery) architecture, THCV219 enables transmission of 8/10 bit RGB, 2bits of user-defined data (CONT), synchronizing signals HSYNC, VSYNC, and DE by a pair cable with minimal external components.

THCV219 inputs CMOS/TTL data (including video data, CONT, HSYNC, VSYNC, and DE) and serializes video data and synchronizing signals separately, depending on the polarity of DE. DE is a signal which indicates whether video or synchronizing data are active. When DE is high, it serializes video data inputs into differential data streams. And it transmits serialized synchronizing data when DE is low.

THCV219 can operate for a wide range of a serial bit rate from 600Mbps to 3.0Gbps.

It does not need any external frequency reference, such as a crystal oscillator.

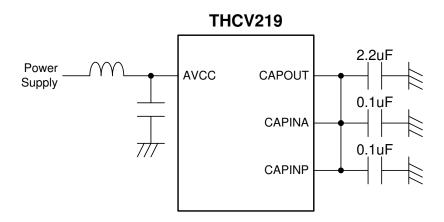

#### Internal Reference Output/Input Function (CAPOUT, CAPINA, CAPINP)

An internal regulator produces the 1.2V (CAPOUT). This 1.2V linear regulator can not supply any other external loads. Bypass CAPOUT to GND with 2.2uF.

CAPINP supplies reference voltage for internal PLL, and CAPINA supplies reference voltage for any internal analog circuit. Bypass CAPINP/CAPINA to GND with 0.1uF to remove high frequency noise. CAPOUT, CAPINA and CAPINP must be tied together.

Analog power supply AVCC is supposed to be stabilized with de-coupling capacitor and series noise filter (for example, ferrite bead).

Figure 1. Connection of CAPOUT, CAPINA, CAPINP and Decoupling Capacitor

#### **Data Enable**

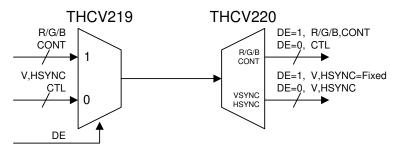

Figure 2 is the conceptual diagram of the basic operation of the chipset.THCV220 in Figure 2 is an example of V-by-One® HS Receiver.

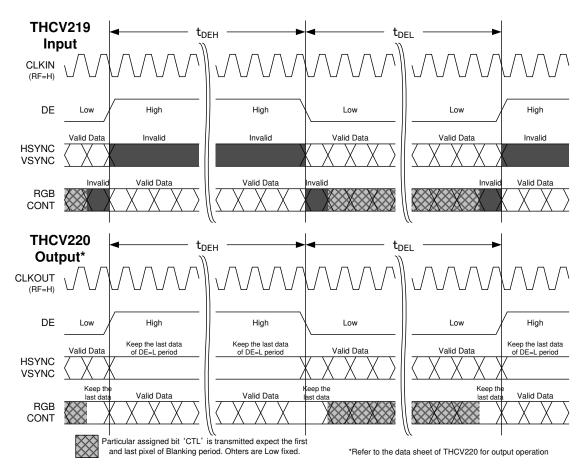

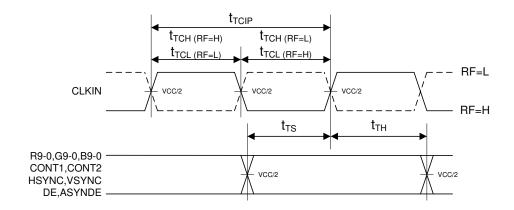

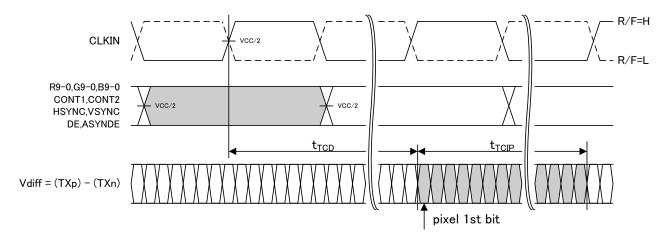

There are some requirements for DE. Figure 3 shows the timing diagram of it.

CTL are particular assigned bit among R/G/B,CONT that can carry arbitrary data during DE=0 period.

Figure 2. Conceptual diagram of the basic operation of the chipset

Figure 3. Data and synchronizing signals transmission timing diagram

Table 1. DE requirement

| symbol | Parameter        | min.   | typ. | max. | Unit |

|--------|------------------|--------|------|------|------|

| tDEH   | DE=High Duration | 2tTCIP |      |      | sec  |

| tDEL   | DE=Low Duration  | 2tTCIP |      |      | sec  |

#### **ASYNDE**

If ASYNDE input is Low, DE input is inverted before V-by-One® HS processing. RGB/CONT Data is transmitted during DE input=Low. Please be careful this inverted DE is outputted from V-by-One® HS receiver, which may cause polarity mismatch against following system requirement.

#### **Color Depth and Frequency Range Select function**

The mode selected by the combination of the COL and LFSEL pin settings is shown in Table 2.

The 32bit mode and 24bit mode correspond to the 4Byte mode and 3Byte mode in the V-by-One® HS standard, respectively.

Low Frequency mode is a THine proprietary feature. To use this mode, a Receiver device with this function must be used. The Receiver device must also be set to Low Frequency mode.

| COL | LFSEL | Description              | Freq. Range(Hz) |

|-----|-------|--------------------------|-----------------|

|     | L     | 32bit                    | 15 to 75M       |

| L   | Н     | 32bit Low frequency mode | 7.5 to 30M      |

| П   | L     | 24bit                    | 20 to 100M      |

| H   | Н     | 24bit Low frequency mode | 10 to 40M       |

Table 2. operation mode select

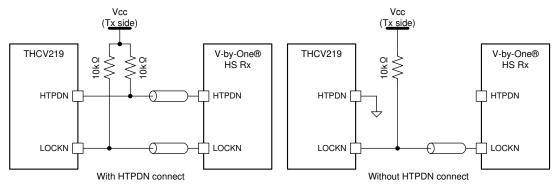

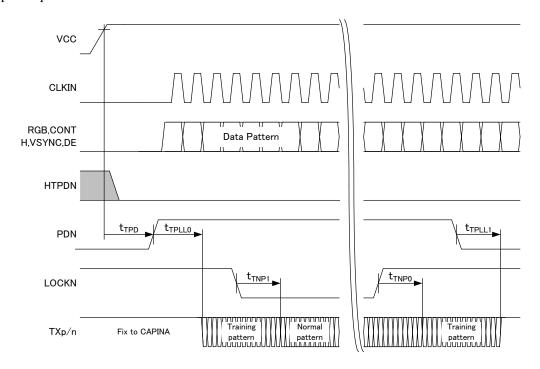

#### **Hot-Plug Function**

HTPDN indicates connecting condition between the Transmitter and the Receiver. HTPDN of the transmitter side is high when the Receiver is not active or not connected. Then Transmitter can enter into the power down mode. HTPDN is set to Low by the Receiver when Receiver is active and connects to the Transmitter, and then Transmitter must start up and transmit CDR training pattern for link training. HTPDN is open drain output at the receiver side. Pull-up resistor is needed at the transmitter side.

HTPDN connection between the Transmitter and the Receiver can be omitted as an application option. In this case, HTPDN at the Transmitter side should always be taken as Low.

#### **Lock Detect Function**

LOCKN indicates whether the CDR PLL is in the lock state or not. LOCKN at the Transmitter input is set to High by pull-up resistor when Receiver is not active or at the CDR PLL training state. LOCKN is set to Low by the Receiver when CDR lock is done. Then the CDR training mode finishes and Transmitter shifts to the normal mode. LOCKN is open drain output at the receiver side. Pull-up resistor is needed at the transmitter side.

When HTPDN is included in an application, the LOCKN signal should only be considered when the HTPDN is pulled low by the Receiver.

Figure 4. Hot-plug and Lock detect scheme

### **Pre-emphasis and Drive Select Function**

Pre-emphasis can equalize severe signal degradation caused by long-distance or high-speed transmission. The PRE pin selects the strength of pre-emphasis.

CMLDRV controls CML output swing level. See Table 3.

Table 3. Pre-emphasis and Drive Select function table

|     |        | Description    |              |  |

|-----|--------|----------------|--------------|--|

| PRE | CMLDRV | Swing level    | Pre-emphasis |  |

| -   | L      | 400mV diff p-p | 0dP          |  |

| L   | Н      | 600mV diff p-p | 0dB          |  |

| ш   | L      | 400mV diff p-p | 6dB          |  |

| Н   | Н      | 600mV diff p-p | 3.5dB        |  |

#### **Power Down Function**

Setting the PDN pin low places THCV219 in the power-down mode. Internal circuitry turns off and the TXP/N outputs turn to High level.

Table 4. Power Down function table

| PDN | Description      |

|-----|------------------|

| L   | Power Down       |

| Н   | Normal Operation |

#### **Field BET Operation**

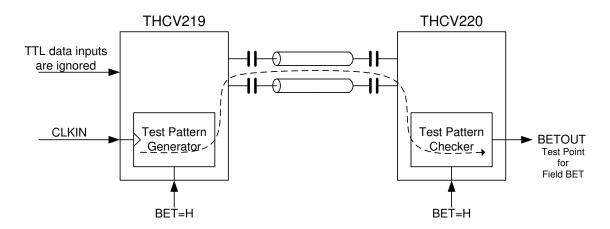

In order to help users to check validity of CML high-speed serial line, THCV219 has an operation mode in which they act as a bit error tester (BET). In this mode, THCV219 internally generates test pattern which is then serialized onto the CML high-speed line. THCV220 which is an example or Rx device also has BET function mode. THCV220 receives the data stream and checks bit errors.

This "Field BET" mode is activated by setting BET= H both on THCV219 and THCV220. The generated data pattern is then 8b/10b encoded, scrambled, and serialized onto the CML channel. As for THCV220, the internal test pattern check circuit gets enabled and reports result on a certain pin named BETOUT. The BETOUT pin goes LOW whenever bit errors occur, or it stays HIGH when there is no bit error. Please refer to Table 5.

| THCV219 | THCV220 | Condition           |

|---------|---------|---------------------|

| BET     | BET     | Condition           |

| L       | L       | Normal Operation    |

| Н       | Н       | Field BET Operation |

Table 5. Field BET operation pin settings

Table 6. THCV220 Field BET result

| BETOUT | Output             |

|--------|--------------------|

| L      | Bit error occurred |

| Н      | No error           |

Figure 5. Field BET Configuration

### Absolute Maximum Ratings\*

| Parameter                      | min. | typ. | max.       | Unit |

|--------------------------------|------|------|------------|------|

| Supply Voltage(VCC,AVCC)       | -0.3 | -    | +4.0       | V    |

| CMOS Input Voltage             | -0.3 | •    | VCC+0.3    | V    |

| CML Transmitter Output Voltage | -0.3 | •    | CAPINA+0.3 | V    |

| Output Current                 | -30  | •    | 30         | mA   |

| Storage Temperature            | -55  | 1    | +125       | ပ္   |

| Junction Temperature           | -    | -    | +125       | °C   |

| Reflow Peak Temperature/Time   | -    | -    | +260/10sec | °C   |

<sup>\* &</sup>quot;Absolute Maximum Ratings" are those values beyond which the safety of the device can not be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

### **Recommended Operating Conditions**

| Parameter                 | min. | typ. | max. | Unit |

|---------------------------|------|------|------|------|

|                           | 2.3  | 2.5  | 2.7  | V    |

| Supply Voltage(VCC,AVCC)  | 2.6  | 2.8  | 3.0  | V    |

|                           | 3.0  | 3.3  | 3.6  | V    |

| CAPOUT and CAPINA Voltage | -    | 1.20 | -    | V    |

| Operating Temperature     | -40  | -    | 85   | °C   |

### Supply Current

Over recommended operating supply and temperature ranges unless otherwise specified.

| symbol                           | Parameter                  | conditions             | min. | typ. | max. | Unit |

|----------------------------------|----------------------------|------------------------|------|------|------|------|

| ITCCW Transmitter Supply Current | Transmitter Supply Current | COL=L                  | -    | -    | 100  | mA   |

|                                  | Transmitter Supply Current | PRE=H                  |      |      |      |      |

| III CCS                          | Transmitter Power Down     | PDN=L                  | -    | 1.2  | 10   | mA   |

|                                  | Supply Current             | All Inputs =Fixed LorH |      |      |      |      |

## **Electrical Specifications**

### CMOS DC Specifications

Over recommended operating supply and temperature ranges unless otherwise specified.

| symbol | Parameter               | conditions | min. | typ. | max. | Unit |

|--------|-------------------------|------------|------|------|------|------|

| IIH    | Input Leak Current High |            | -10  | -    | +10  | uA   |

| IIL    | Input Leak Current Low  |            | -10  | -    | +10  | uA   |

VCC=3.3±0.3V

| symbol | Parameter                 | conditions | min. | typ. | max. | Unit |

|--------|---------------------------|------------|------|------|------|------|

| VIH    | High Level Input Voltage  | 13         | 2.0  | -    | VCC  | V    |

| VIII   | night Level input voltage | 13L        | 2.1  | -    | VCC  | V    |

| VIII   | Love Love Llovet Voltage  | 13         | 0    | -    | 0.8  | V    |

| VIL    | Low Level Input Voltage   | 13L        | 0    | -    | 0.7  | V    |

VCC=2.8±0.2V

| symbol | Parameter                | conditions                     | min.  | typ. | max. | Unit |

|--------|--------------------------|--------------------------------|-------|------|------|------|

| VIH    | High Level Input Voltage | 13                             | 1.8 - | VCC  | V    |      |

| VIII   | High Level input voltage | gn Level input voltage I3L 1.9 | 1.9   | -    | VCC  | V    |

| VIL    | Low Level Input Voltage  | 13 0                           |       | 0.7  | V    |      |

| VIL    | Low Level input voltage  | I3L                            | 0     |      | 0.6  | V    |

VCC=2.5±0.2V

| symbol | Parameter                   | conditions      | min. | typ. | max. | Unit |

|--------|-----------------------------|-----------------|------|------|------|------|

| VIH    | High Level Input Voltage    | 13              | 1.7  | =    | VCC  | V    |

| VIII   | riigii Levei iriput voitage | Voltage I3L 1.6 | 1.6  | -    | VCC  | V    |

| VIL    | Low Lovel Input Valtage     | 13              | 0    | -    | 0.7  | V    |

| VIL    | Low Level Input Voltage     | I3L             | 0 -  | 0.5  | V    |      |

### CML DC Specifications

Over recommended operating supply and temperature ranges unless otherwise specified.

| symbol | Parameter                              | conditions        | min. | typ. | max. | Unit |

|--------|----------------------------------------|-------------------|------|------|------|------|

| VTOD   | CML Differential Mode Output Voltage   | CMLDRV=L          | 133  | 200  | 267  | mV   |

| VIOD   | CIVIL DITTETETHIAT Mode Output Voltage | CMLDRV=H          | 200  | 300  | 400  | mV   |

|        |                                        | PRE=L             | - 0  | -    | %    |      |

| PRE    | CML Pre-emphasis Level                 | PRE=H, CMLDRV=L   | -    | 100  | -    | %    |

|        |                                        | PRE=H, CMLDRV=H   | -    | 50   | -    | %    |

|        | CML Common Mode Output Voltage         | PRE=L             |      |      | V    |      |

| VTOC   |                                        | PRE=H, CMLDRV=L   |      | V    |      |      |

|        |                                        | PRE=H, CMLDRV=H   |      | V    |      |      |

| ITOH   | CML Output Leak Current High           | PDN=L, TXP/N=1.2V | -    | -    | ±30  | uA   |

| ITOS   | CML Output Short Circuit Current       | PDN=L, TXP/N=0V   | -80  | -    | -    | mA   |

### **AC Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified.

| symbol | Parameter                                   | conditions     | min.      | typ.          | max.         | Unit |

|--------|---------------------------------------------|----------------|-----------|---------------|--------------|------|

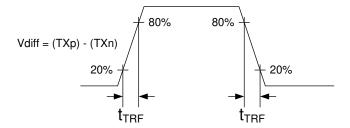

| tTRF   | CML Output Rise and Fall Time(20%-80%)      |                | 50        | -             | 150          | ps   |

|        |                                             | COL=H, LFSEL=L | 10        | -             | 50           | ns   |

| tTCIP  | CLKIN Period                                | COL=H, LFSEL=H | 25        | -             | 100          | ns   |

| UUIF   | CLAIN F GIIOG                               | COL=L, LFSEL=L | 13.34     | -             | 66.66        | ns   |

|        |                                             | COL=L, LFSEL=H | 0.35tTCIP | -             | 133.33       | ns   |

| tTCH   | CLK IN High Time                            |                | 0.35tTCIP | 0.5tTCIP      | 0.65tTCIP    | ns   |