# 280ps High-Speed Comparator, Ultra-Low Dispersion with LVDS Outputs

### **General Description**

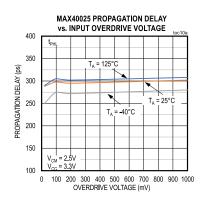

The MAX40025 and MAX40026 are single-supply, high-speed comparators with a typical propagation delay of 280ps. The overdrive dispersion is extremely low (typical 25ps), making these comparators ideal for time-of-flight distance measurement applications.

The input common mode range of 1.5V to  $V_{DD}$  + 0.1V is compatible with the output swings of several widely used high-speed trans-impedance amplifiers, such as the MAX40658.

The output stage is LVDS (Low-Voltage Differential Signaling), which helps to minimize power dissipation and interfaces directly with many FPGAs and CPUs. Complementary outputs help in suppression of common-mode noise on each output line.

The MAX40025 is offered in a space-saving, tiny, 1.218mm x 0.818mm, 6-bump wafer-level package (WLP), while the MAX40026 is available in a 2mm x 2mm 8-pin TDFN side-wettable package and meets AEC-Q100 automotive qualification requirements. The MAX40025/MAX40026 operate over -40°C to +125°C temperature range and run from a single supply voltage of 2.7V to 3.6V.

### **Applications**

- Distance Sensing in LIDAR, RADAR, and SONAR

- Time-of-Flight Sensors

- High-Speed Differential Line Receivers

- High-Speed Triggering in Oscilloscopes

- Communications

- Oscillators

- Threshold Detectors

- High-Speed Level-Shifting

- Test and Measurement

- Automotive Applications

### **Benefits and Features**

- Fast Propagation Delay: 280ps, Typ

- Low Overdrive Dispersion: 25ps (V<sub>OD</sub> = 10mV to 1V)

- Supply Voltage 2.7V to 3.6V

- 39.4mW at 2.7V Supply

- Power-Efficient LVDS Outputs

- -40°C to +125°C Temperature Range

- Automotive AEC-Q100 Qualified (TDFN-8 Version)

- Internal 1.5mV Hysteresis: MAX40026

- Internal 2.5mV Hysteresis: MAX40025A

Ordering Information appears at end of data sheet.

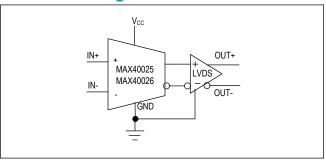

### **Functional Diagram**

# 280ps High-Speed Comparator, Ultra-Low Dispersion with LVDS Outputs

### **Absolute Maximum Ratings**

| V <sub>CC</sub> to GND                   | 0.3V to +3.6V                  |

|------------------------------------------|--------------------------------|

| Either IN+ or IN- to GND                 | $-0.3V$ to $V_{CC} + 0.3V$     |

| Either OUT+ or OUT- to GND               | 0.3V to V <sub>DD</sub> + 0.3V |

| OUT+ to OUT                              | 0.5V to +0.5V                  |

| Current Into Any Pin (Continuous)        | 10mA                           |

| Continuous Power Dissipation (Multilayer | Board) (WLP) $(T_A =$          |

| +70°C, derate 10.51mW/°C above +70°C)    | 816mW                          |

| Continuous Power Dissipation (Multilayer | Board) (TDFN) (T <sub>A</sub> = |

|------------------------------------------|---------------------------------|

| +70°C, derate 9.8mW/°C above +70°C.)     | 784mW                           |

| Operating Temperature Range              | 40°C to +125°C                  |

| Junction Temperature                     | +150°C                          |

| Storage Temperature Range                | 40°C to +150°C                  |

| Soldering Temperature (reflow)           | +260°C                          |

|                                          |                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **WLP**

| Package Code                                           | W60D1+1                        |  |  |  |

|--------------------------------------------------------|--------------------------------|--|--|--|

| Outline Number                                         | 21-100296                      |  |  |  |

| Land Pattern Number                                    | Refer to Application Note 1891 |  |  |  |

| Thermal Resistance, Four-Layer Board:                  |                                |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 95.15°C/W                      |  |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | N/A                            |  |  |  |

### 8-TDFN

| Package Code                                           | T822Y+3          |

|--------------------------------------------------------|------------------|

| Outline Number                                         | <u>21-100185</u> |

| Land Pattern Number                                    | 90-100070        |

| Thermal Resistance, Single-Layer Board:                |                  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 130°C/W          |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 8°C/W            |

| Thermal Resistance, Four-Layer Board:                  |                  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 102°C/W          |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 8°C/W            |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

$(V_{CC}$  = 3.3V,  $V_{CM}$  = 2.5V,  $R_{LOAD}$  = 100 $\Omega$ , connected from OUT+ to OUT-,  $T_A$  = -40°C to +125°C (Note 1))

| PARAMETER                                | SYMBOL                     | CONDITIONS                                                                  | MIN        | TYP | MAX                   | UNITS |  |

|------------------------------------------|----------------------------|-----------------------------------------------------------------------------|------------|-----|-----------------------|-------|--|

| Supply Voltage (Note 2)                  | V <sub>CC</sub>            | Guaranteed by PSRR specification                                            | 2.7        |     | 3.6                   | V     |  |

| Supply Current                           | Icc                        |                                                                             |            | 17  | 23                    | mA    |  |

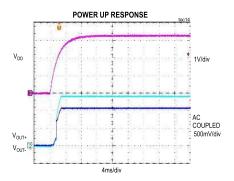

| Power-Up Time                            | t <sub>ON</sub>            | Measured using supply current >75% of final value                           |            | 20  |                       | μs    |  |

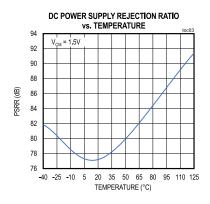

| Power Supply Rejection<br>Ratio (Note 2) | PSRR                       | 2.7V ≤ V <sub>CC</sub> ≤ 3.6V                                               | 50         | 80  |                       | dB    |  |

| Input Common Mode<br>Range (Note 2)      | V <sub>CM</sub>            | Guaranteed by CMRR specification                                            | 1.5        |     | V <sub>CC</sub> + 0.1 | V     |  |

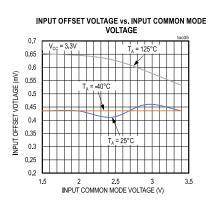

| Input Offset Voltage (Note 2)            | V <sub>OS</sub>            | Over the Input common mode range                                            |            | 0.5 | 5                     | mV    |  |

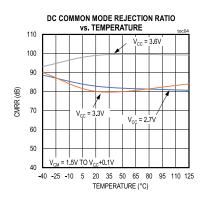

| Common Mode<br>Rejection Ratio (Note 2)  | CMRR                       | Over the Input common mode range                                            | 52         | 80  |                       | dB    |  |

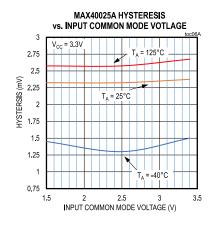

| Input Hysteresis                         | V/                         | MAX40025A                                                                   |            | 2.5 |                       | mV    |  |

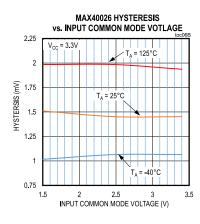

| input riysteresis                        | $V_{HYS}$                  | MAX40026                                                                    |            | 1.5 |                       | IIIV  |  |

| Input Bias Current                       | I <sub>B</sub>             | Over the Input common mode range. Inputs shorted together.                  |            | 1.3 | 10                    | μA    |  |

| Input Offset Current                     | I <sub>OS</sub>            | $V_{IN+} = V_{IN-}$                                                         |            | 0.1 | 4                     | μA    |  |

| Input Capacitance                        | C <sub>IN</sub>            | Either input, over entire Input common mode range                           |            | 2   |                       | pF    |  |

| Output Differential<br>Voltage           | V <sub>OUTDIFF</sub>       | IV <sub>OUT+</sub> - V <sub>OUT-</sub> I                                    | 247        | 350 | 454                   | mV    |  |

| Output Differential<br>Voltage Match     |                            | V <sub>OUT+</sub> - V <sub>OUT-</sub>                                       | -50        |     | +50                   | mV    |  |

| Output Common-Mode<br>Voltage            | V <sub>СМОИТ</sub>         | Either output polarity                                                      | 1.125 1.23 |     | 1.375                 | V     |  |

| Output Common-Mode<br>Voltage Match      |                            | Either output polarity                                                      | -50        |     | +50                   | mV    |  |

| Output Common-Mode<br>Transient          |                            | Either output transition polarity                                           |            | 18  |                       | mVp-p |  |

| Output Short-Circuit                     | I <sub>SC</sub>            | Either output shorted to ground, either polarity                            |            |     | 24                    | mA    |  |

| Current                                  |                            | Outputs shorted together, either polarity                                   | -12        |     | +12                   | -     |  |

| Propagation Delay                        | tion Delay t <sub>PD</sub> | 20mV overdrive                                                              |            | 270 |                       |       |  |

|                                          |                            | 100mV overdrive                                                             |            | 280 |                       | ps    |  |

|                                          |                            | 200mV overdrive                                                             |            | 280 |                       | 1     |  |

| Jitter                                   | t <sub>JITTER</sub>        | Measured using square wave with Rise and Fall Time = 150ps, 100mV overdrive |            | 2   |                       | ps    |  |

| Overdrive Discoursies                    |                            |                                                                             |            | 25  |                       |       |  |

| Overdrive Dispersion                     | t <sub>OD-disp</sub>       | 20mV to 100mV                                                               |            | 10  |                       | ps    |  |

| Rise Time                                | t <sub>R</sub>             | From 25% to 75% output swing                                                |            | 150 |                       | ps    |  |

| Fall Time                                | t <sub>F</sub>             | From 75% to 25% output swing                                                |            | 165 |                       | ps    |  |

# 280ps High-Speed Comparator, Ultra-Low Dispersion with LVDS Outputs

### **Electrical Characteristics (continued)**

$(V_{CC} = 3.3V, V_{CM} = 2.5V, R_{LOAD} = 100\Omega, connected from OUT+ to OUT-, T_A = -40^{\circ}C \ to \ +125^{\circ}C \ (Note \ 1))$

| PARAMETER           | SYMBOL                                      | CONDITIONS                                                                              |                                                          | MIN | TYP | MAX | UNITS |

|---------------------|---------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------|-----|-----|-----|-------|

| Output Skew         |                                             | Measured using<br>square wave with<br>Rise and Fall Time<br>= 150ps, 100mV<br>overdrive | Propagation Delay<br>difference between<br>OUT+ and OUT- |     | 10  |     | ps    |

| Maximum Taggla Data | $T_R$ $V_{OUT} = 550$ mV, $V_{OD} = 100$ mV | V <sub>OUT</sub> = 550mV,                                                               | MAX40025                                                 |     | 4   |     | Gbps  |

| Maximum Toggle Rate |                                             |                                                                                         | MAX40026                                                 |     | 3   |     | Gups  |

| Minimum Pulse Width |                                             | both MAX40025/ MA                                                                       | X40026                                                   |     | 330 |     | ps    |

Note 1: Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 2: Specifications are guaranteed by design and characterization and not production tested.

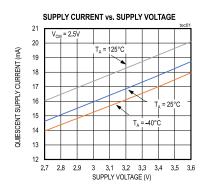

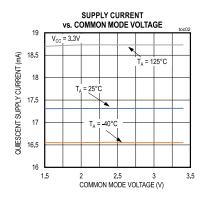

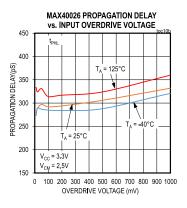

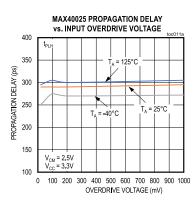

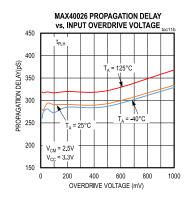

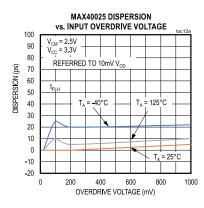

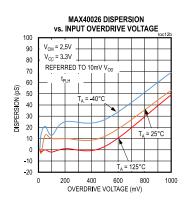

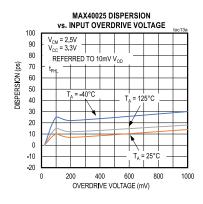

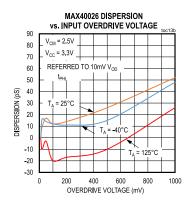

## **Typical Operating Characteristics**

(V<sub>CC</sub> = 3.3V. V<sub>CM</sub> = 2.5V.  $R_{LOAD}$  = 100 $\Omega$ , connected from OUT+ to OUT-.)

### **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 3.3V. V<sub>CM</sub> = 2.5V.  $R_{LOAD}$  = 100 $\Omega$ , connected from OUT+ to OUT-.)

## **Typical Operating Characteristics (continued)**

$(V_{CC}$  = 3.3V.  $V_{CM}$  = 2.5V.  $R_{LOAD}$  = 100Ω, connected from OUT+ to OUT-.)

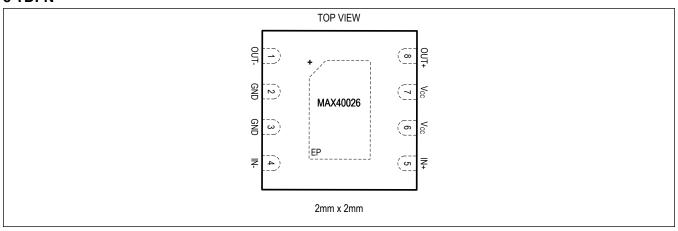

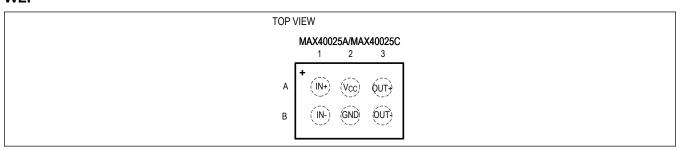

# **Pin Configurations**

### 8 TDFN

### **WLP**

# **Pin Description**

| PI           | IN                              |                 |                                                                                                                                                                            |  |

|--------------|---------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX4002<br>6 | MAX4002<br>5A/<br>MAX4002<br>5C | NAME            | FUNCTION                                                                                                                                                                   |  |

| 1            | ВЗ                              | OUT-            | Inverting LVDS Output. Connect a $100\Omega$ termination resistor between OUT- and OUT+. OUT- is at logic-low if $V_{IN+}$ is at higher voltage compared to $V_{IN-}$ .    |  |

| 2, 3         | B2                              | GND             | Ground. Signal and power return (for TDFN-8: connect pins 2 and 3 together externally).                                                                                    |  |

| 4            | B1                              | IN-             | Inverting Input                                                                                                                                                            |  |

| 5            | A1                              | IN+             | Non-Inverting Input                                                                                                                                                        |  |

| 6,7          | A2                              | V <sub>CC</sub> | Positive Supply. For TDFN-8, connect pins 6 and 7 together externally.                                                                                                     |  |

| 8            | A3                              | OUT+            | Non-Inverting LVDS Output. Connect a $100\Omega$ termination resistor between OUT+ and OUT OUT+ is at logic-high if $V_{IN+}$ is at higher voltage compared to $V_{IN-}$ . |  |

| EP           | _                               | Exposed Paddle  | Exposed Pad (TDFN-8 Only). This pad must be connected to ground.                                                                                                           |  |

# 280ps High-Speed Comparator, Ultra-Low Dispersion with LVDS Outputs

### **Detailed Description**

The MAX40025 and MAX40026 are single-supply, high-speed comparators with a typical propagation delay of 280ps. The overdrive dispersion is extremely low (25ps, typ.), making these comparators ideal for time-of-flight distance measurement applications.

The input common-mode range of 1.5V to  $V_{DD}$  + 0.1V is compatible with the outputs of several widely used high-speed transimpedance amplifiers, such as the MAX40658. The output stage is LVDS (Low-Voltage Differential Signaling), which helps to minimize power dissipation and interfaces directly with many modern FPGAs and CPUs.

The MAX40025 and MAX40026 operate from a +2.7V to +3.6V power supply voltage while typically consuming only 17mA quiescent current at 3.3V. The MAX40025 and MAX40026 are available in space-saving 6-WLP and 8-TDFN packages, respectively.

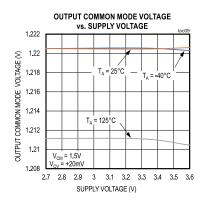

### **LVDS Outputs**

Each LVDS output has a switched 3.25 mA current source. The outputs are differentially terminated with an external  $100\Omega$  resistor, which produces a  $\pm 350$  mV differential output. The power delivered to the  $100\Omega$  load resistor is only 1.1mW while enabling transmission data rates up to a few hundreds of Megabits per second. The output common-mode voltage is maintained at 1.23 V on both outputs, and is independent of power supply voltage. The fully differential LVDS outputs provide high-speed digital signalling with reduced EMI compared to single-ended outputs.

# 280ps High-Speed Comparator, Ultra-Low Dispersion with LVDS Outputs

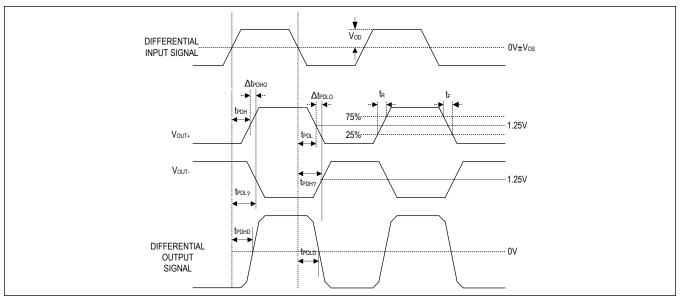

## **System Timing Definitions**

# **Table 1. Timing Definitions**

| SYMBOL             | SPECIFICATION                             | DESCRIPTION                                                                                                                                                                                                                |

|--------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OD</sub>    | Overdrive<br>Voltage                      | Differential voltage applied across inputs during test                                                                                                                                                                     |

| t <sub>PDH</sub>   | Propagation<br>Delay High on<br>OUT+      | Propagation delay measured from the time the differential input signal changes polarity (± input V <sub>OS</sub> ) to the 50% point in the output low-to-high transition on OUT+                                           |

| t <sub>PDL</sub>   | Propagation<br>Delay Low on<br>OUT-       | Propagation delay measured from the time the differential input signal changes polarity ( $\pm$ input V <sub>OS</sub> ) to the 50% point in the output high-to-low transition on OUT-                                      |

| Δt <sub>PDHO</sub> | Propagation<br>Delay Skew on<br>High      | Difference in propagation delay on output transition from low to high on OUT+ to propagation delay from high to low on OUT-                                                                                                |

| Δt <sub>PDLO</sub> | Propagation<br>Delay Skew on<br>Low       | Difference in propagation delay on output transition from high to low on OUT+ to propagation delay from low to high on OUT-                                                                                                |

| t <sub>R</sub>     | Output Rise Time                          | Time taken by either OUT+ or OUT- to rise from 25% of final output voltage to 75% of final output voltage                                                                                                                  |

| t <sub>F</sub>     | Output Fall Time                          | Time taken by either OUT+ or OUT- to fall from 75% of final output voltage to 25% of final output voltage                                                                                                                  |

| t <sub>PD</sub> _  | Propagation<br>Delay Low on<br>OUT-       | Propagation delay measured from the time the differential input signal changes polarity ( $\pm$ input V <sub>OS</sub> ) to the 50% point in the output high-to-low transition on OUT-                                      |

| t <sub>PDH</sub>   | Propagation Delay High on OUT-            | Propagation delay measured from the time the differential input signal changes polarity (± input V <sub>OS</sub> ) to the 50% point in the output low-to-high transition on OUT-                                           |

| t <sub>PDHD</sub>  | Differential<br>Propagation<br>Delay High | Propagation delay measured from the time the differential input signal changes polarity (± input V <sub>OS</sub> ) to the 50% point in the output differential signal across OUT+ to OUT- while switching low to high      |

| t <sub>PDLD</sub>  | Differential<br>Propagation<br>Delay Low  | Propagation delay measured from the time the differential input signal changes polarity ( $\pm$ input V <sub>OS</sub> ) to the 50% point in the output differential signal across OUT+ to OUT- while switching high to low |

| V <sub>OH</sub>    | Output Voltage<br>High                    | Comparator output high state voltage level                                                                                                                                                                                 |

| V <sub>OL</sub>    | Output Voltage<br>Low                     | Comparator output low state voltage level                                                                                                                                                                                  |

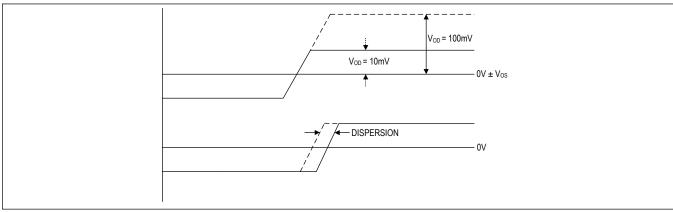

Figure 1. System Timing Diagram

### **Propagation Delay**

The propagation delay is defined as the delay between the differential comparator input voltage changing polarity and the output(s) reaching the mid-point of the high-to-low or low-to-high transition. The low-to-high propagation delay is  $t_{PDH}$  on OUT+ and  $t_{PDH}$  on OUT-, whereas the high-to-low propagation delay is  $t_{PDL}$  on OUT+ and  $t_{PDL}$  on OUT-. These high-to-low and low-to-high timing parameters will differ slightly due to mismatches between the two complementary outputs. As a result, this difference in propagation delay is considered to be a skew for a given combination of low-to-high transitions on OUT+ and high-to-low transitions on OUT-.

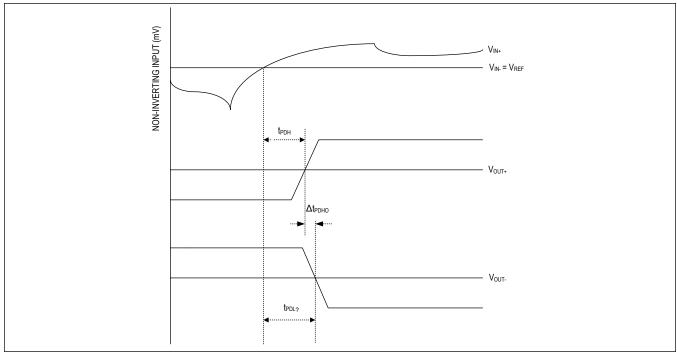

Figure 2. Propagation Delay

### **Propagation Delay Dispersion**

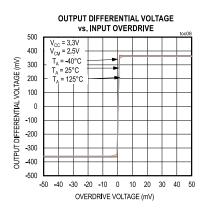

Dispersion, or variation of the propagation delay under different conditions, is affected by the amount of overdrive voltage applied to the comparator inputs. As can be seen in the <u>Typical Operating Characteristics</u>, the dispersion is typically under 25ps for 10mV to 1V, a wide range of input overdrive values.

Figure 3. Amplitude Overdrive Dispersion

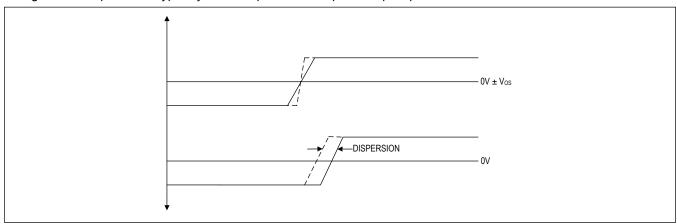

Dispersion is also affected by the input slew rate. As the slew rate of the input signal changes, the propagation delay also changes. The dispersion is typically under 15ps from 0.4V/µs to 1V/µs input slew rates.

Figure 4. Slew Rate Dispersion

### **Hysteresis**

Adding a small amount hysteresis to a comparator in a noisy environment is useful when input signals are slow-moving and have small noise levels superimposed on them. However, hysteresis must be used carefully when signals are small because it can cause valid signals to be ignored. Figure 5 shows the input signal and output response for a comparator with hysteresis applied.

Figure 5. Hysteresis Transfer Function

The MAX40025C is optimized for detecting very small, fast-changing signals and therefore has no internal hysteresis. The MAX40025A has fixed internal 2.5mV hysteresis and the MAX40026 has fixed internal 1.5mV hysteresis, which improves their usefulness for detecting larger differential input signals in the presence of noise. This helps to avoid the external components and potential stability degradation associated with external positive feedback paths.

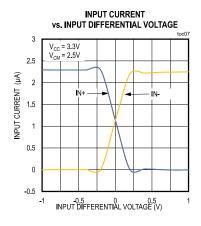

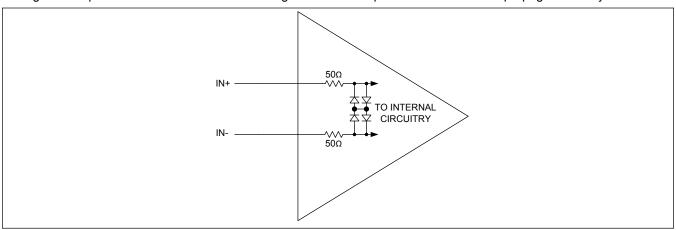

### **Input Stage Circuitry**

The MAX40025/MAX40026 include internal protection circuitry that prevents damage to the precision input stage from large differential input voltages. This protection circuitry consists of two groups of two front-to-back diodes between IN+ and IN-, as well as two  $50\Omega$  resistors (<u>Figure 6</u>). The diodes limit the differential voltage applied to the comparator's internal circuitry to no more than  $2V_F$ , where  $V_F$  is the diode's forward-voltage drop (about 0.7V at +25°C).

For a large differential input voltage (exceeding 2V<sub>F</sub>), this protection circuitry increases the input bias current at IN+ (source) and IN- (sink).

INPUT CURRENT =

$$\frac{\left(V_{\text{IN}+} - V_{\text{IN}-}\right) - 2 \times V_{F}}{2 \times 50}$$

Input currents with large differential input voltages should not be confused with input bias currents ( $I_B$ ). As long as the differential input voltage is less than  $2V_F$ , this input current is less than  $2I_B$ .

The input circuitry allows the MAX40025/MAX40026's input common-mode range to extend 100mV beyond the positive power-supply rail. The output remains in the correct logic state if one or both inputs are within the common-mode range. Taking either input outside the common-mode range causes the input to saturate and the propagation delay to increase.

Figure 6. Input Stage Circuitry

### **Applications Information**

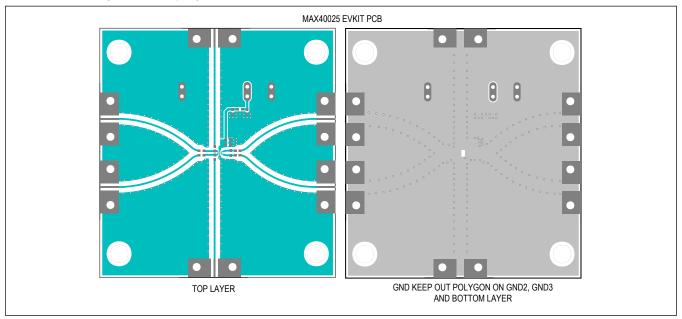

#### **Critical Layout Guidelines**

Some critical Layout guidelines are listed below.

- Use a PC board with a low-impedance ground plane.

- Mount one or more 10nF ceramic capacitors between GND and V<sub>CC</sub>, as close to the pins as possible. Multiple bypass

capacitors help to reduce the effect of trace impedance and capacitor ESR.

- Choose bypass capacitors for minimum inductance and ESR.

- Use a 100Ω termination resistor for the LVDS output, connected directly between OUT+ and OUT-, if practical. If the

destination LVDS inputs can't be located adjacent to the outputs, use a 100Ω microstrip between the output pins and

the termination resistor, which should be close to the LVDS inputs of the FPGA or other destination component. This

will avoid the creation of stub beyond the termination resistor, which will cause reflections. The added length of the

differential trace has less degrading affects than added stub length.

- Ensure that there is no parasitic coupling between the inputs and the outputs. Such coupling serves as feedback, and can result in oscillation.

- Minimize any parasitic layout inductance.

- It is recommended to use higher performance substrate materials (for example, Rogers).

- A differential micro-strip is the recommended layout for MAX40025/MAX40026 with terminations done close to the inputs and outputs of the MAX40025 or MAX40026. Care must be taken to avoid unwanted stubs by removing ground below the traces that are not part of the 50Ω termination line leading into input pins. The parasitic capacitance created between traces and ground slow down and even distort the signals by creating reflections on the path.

- Below is an example from the MAX40025EVKIT#, where ground has been etched/removed underneath a stub as shown in the layer below top layer.

Figure 7. Layout Guidelines—Ground Keep-Out to Avoid Stubs.

#### Input Slew Rate

With slower slew rates, when the input voltage is near the threshold any parasitic feedback paths can cause oscillation. In addition, the comparator's input noise will cause the output to undergo transitions. Eliminating feedback paths will stop oscillation. To avoid noise-induced chattering, the input slew rate should be greater than 1V/µs.

### **Typical Application Circuits**

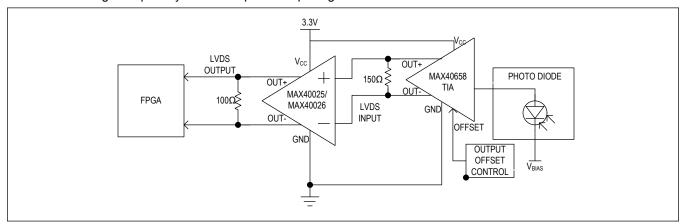

Receiver Section of Differential Time-of-Flight Measurement Circuit:

In <u>Figure 8</u>, the photodiode, shown at the far right, converts light incident upon it into current that drives the input of the MAX40658 Transimpedance Amplifier (TIA). The MAX40658 then converts photodiode current to voltage, amplifies it, and passes a replica of the incident light to input of the MAX40025 high-speed comparator. By default, the MAX40658 has -27mV differential output offset voltage when there is no input current. This offset can be adjusted using the MAX40658's offset pin. The MAX40025 produces differential output pulses whenever an incident light pulse has intensity sufficient to change the polarity of the comparator input signal.

Figure 8. Differential-Ended Output Receiver

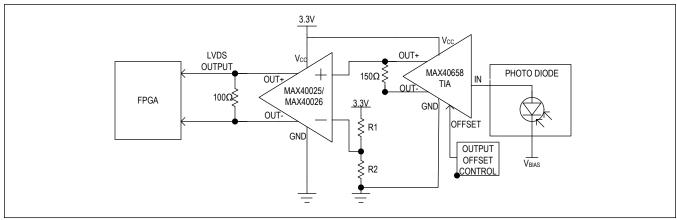

Receiver Section of Single-Ended Time-of-Flight Measurement Circuit:

<u>Figure 9</u> has a single-ended output configuration on the transimpedance amplifier, which drives one input of the comparator. This functionality is the same as that of the differential configuration discussed above, except that the threshold voltage can be adjusted by selecting the values of R1 and R2.

Figure 9. Single-Ended Output Receiver

# 280ps High-Speed Comparator, Ultra-Low Dispersion with LVDS Outputs

# **Ordering Information**

| PART NUMBER     | TEMPERATURE RANGE | PIN-PACKAGE | TOP MARK | HYSTERESIS    |

|-----------------|-------------------|-------------|----------|---------------|

| MAX40025AAWT+   | -40°C to +125°C   | 6-WLP       | +AAC     | 2.5mv         |

| MAX40025CAWT+   | -40°C to +125°C   | 6-WLP       | +AAB     | No Hysterisis |

| MAX40026ATA/VY+ | -40°C to +125°C   | 8-TDFN      | +BAA     | 1.5mV         |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

# 280ps High-Speed Comparator, Ultra-Low Dispersion with LVDS Outputs

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                        | PAGES<br>CHANGED |

|--------------------|---------------|--------------------------------------------------------------------|------------------|

| 0                  | 11/18         | Initial release                                                    | _                |

| 1                  | 12/18         | Updated part numbers in title and equation in Detailed Description | 1–17             |

| 2                  | 1/19          | Updated Pin Configuration Diagram and Pin Description              | 7                |

| 3                  | 2/19          | Updated data sheet for release of MAX40026                         | 1–18             |

| 4                  | 3/19          | Updated data sheet for release of MAX40025A                        | 1–18             |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.