. . . . scale Semiconductor

Technical Data

Document Number: MMA81XXEG Rev 5, 04/2010

**√RoHS**

# Digital X-Axis or Z-Axis Accelerometer

The MMA81XXEG (Z-axis) and MMA82XXEG/MMA82XXTEG (X-axis) are members of Freescale's family of DSI 2.0-compatible accelerometers. These devices incorporate digital signal processing for filtering, trim and data formatting.

#### **Features**

- Available in 20g, 40g, 150g, and 250g (MMA82XXEG, X-axis), 50g and 100g (MMA82XXTEG, X-axis) and 40g, 100g, 150g, and 250g (MMA81XXEG, Z-axis). Additional g-ranges may be available upon request

- · 80 customer-accessible OTP bits

- 10-bit digital data output from 8 to 10 bit DSI output

- 6.3 to 30 V supply voltage

- · On-chip voltage regulator

- · Internal self-test

- · Minimal external component requirements

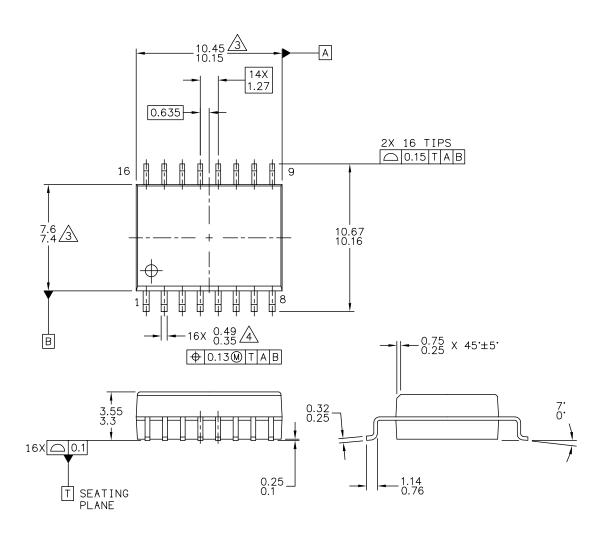

- RoHS compliant (-40 to +125°C) 16-pin SOIC package

- Automotive AEC-Q100 qualified

- DSI 2.0 Compliant

- Z-axis transducer is overdamped

#### **Typical Applications**

- Crash detection (Airbag)

- · Impact and vibration monitoring

- Shock detection.

# MMA81XXEG MMA82XXEG MMA82XXTEG SERIES

SINGLE-AXIS DSI 2.0 ACCELEROMETER

EG SUFFIX (Pb-free) 16-LEAD SOIC CASE 475-01

|              |                | ORDERIN        | NG INFORMATION    |                 |             |

|--------------|----------------|----------------|-------------------|-----------------|-------------|

| Device Name  | X-axis g-Level | Z-axis g-Level | Temperature Range | SOIC 16 Package | Packaging   |

| MMA8225EGR2  | 250            | _              | -40 to +125°C     | 475-01          | Tape & Reel |

| MMA8225EG    | 250            | _              | -40 to +125°C     | 475-01          | Tubes       |

| MMA8215EGR2  | 150            | _              | -40 to +125°C     | 475-01          | Tape & Reel |

| MMA8215EG    | 150            | _              | -40 to +125°C     | 475-01          | Tubes       |

| MMA8210TEGR2 | 100            | _              | -40 to +125°C     | 475-01          | Tape & Reel |

| MMA8210TEG   | 100            | _              | -40 to +125°C     | 475-01          | Tubes       |

| MMA8205TEGR2 | 50             | _              | -40 to +125°C     | 475-01          | Tape & Reel |

| MMA8205TEG   | 50             | _              | -40 to +125°C     | 475-01          | Tubes       |

| MMA8204EGR2  | 40             | _              | -40 to +125°C     | 475-01          | Tape & Reel |

| MMA8204EG    | 40             | _              | -40 to +125°C     | 475-01          | Tubes       |

| MMA8202EGR2  | 20             | _              | -40 to +125°C     | 475-01          | Tape & Reel |

| MMA8202EG    | 20             | _              | -40 to +125°C     | 475-01          | Tubes       |

| MMA8125EGR2  | _              | 250            | -40 to +125°C     | 475-01          | Tape & Reel |

| MMA8125EG    | _              | 250            | -40 to +125°C     | 475-01          | Tubes       |

| MMA8115EGR2  | _              | 150            | -40 to +125°C     | 475-01          | Tape & Reel |

| MMA8115EG    | _              | 150            | -40 to +125°C     | 475-01          | Tubes       |

| MMA8110EGR2  | _              | 100            | -40 to +125°C     | 475-01          | Tape & Reel |

| MMA8110EG    | _              | 100            | -40 to +125°C     | 475-01          | Tubes       |

| MMA8104EGR2  | _              | 40             | -40 to +125°C     | 475-01          | Tape & Reel |

| MMA8104EG    | _              | 40             | -40 to +125°C     | 475-01          | Tubes       |

## SECTION 1 GENERAL DESCRIPTION

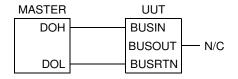

MMA81XXEG/MMA82XXEG/MMA82XXTEG family is a satellite accelerometer which is comprised of a single axis, variable capacitance sensing element with a single channel interface IC. The interface IC converts the analog signal to a digital format which is transmitted in accordance with the DSI-2.0 specification.

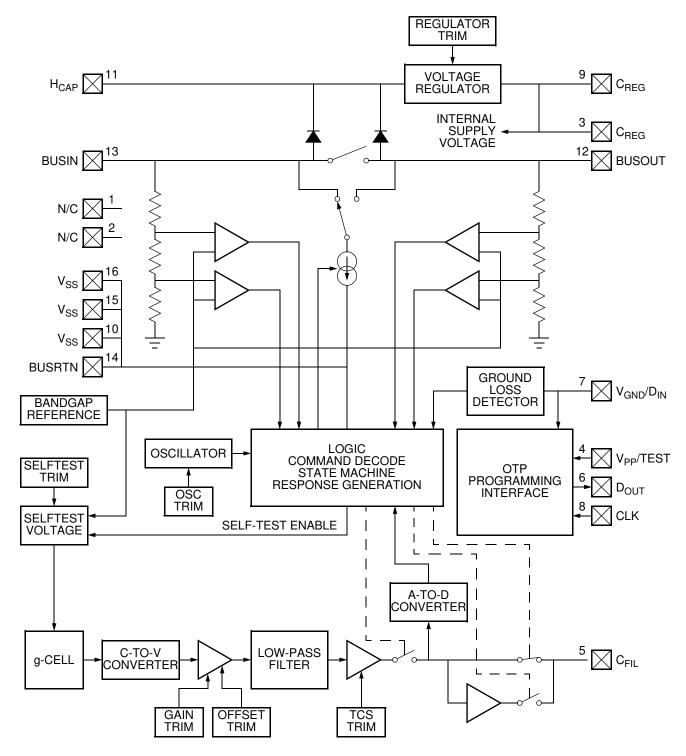

#### 1.1 OVERVIEW

Signal conditioning begins with a Capacitance to Voltage conversion (C to V) followed by a 2-stage switched capacitor amplifier. This amplifier has adjustable offset and gain trimming and is followed by a low-pass switched capacitor filter with Bessel function. Offset and gain of the interface IC are trimmed during the manufacturing process. Following the filter the signal passes to the output stage. The output stage sensitivity incorporates temperature compensation.

The output of the accelerometer signal conditioning is converted to a digital signal by an A/D converter. After this conversion the resultant digital word is converted to a serial data stream which may be transmitted via the DSI bus. Power for the device is derived from voltage applied to the BUSIN/BUSOUT and V<sub>SS</sub> pins. Bus voltage is rectified and applied to an external capacitor connected to the H<sub>CAP</sub> pin. During data transmissions, the device operates from stored charge on the external capacitor. An integrated regulator supplies fixed voltage to internal circuitry.

A self-test voltage may be applied to the electrostatic deflection plate in the sensing element. Self-Test voltage is factory trimmed. Other support circuits include a bandgap voltage reference for the bias sources and the self-test voltage.

A total of 128 bits of One-Time Programmable (OTP) memory, are provided for storage of factory trim data, serial number and device characteristics. Eighty OTP bits are available for customer programming. These eighty OTP bits may be programmed via the DSI Bus or through the serial test/trim interface. OTP integrity is verified through continuous parity checking. Separate parity bits are provided for factory and customer programmed data. In the event that a parity fault is detected, the reserved value of zero is transmitted in response to a Read Acceleration Data command.

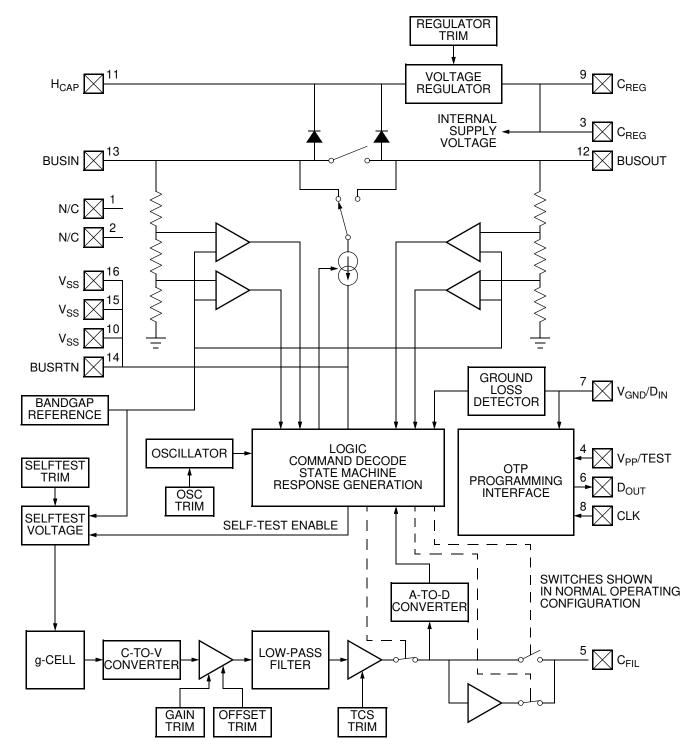

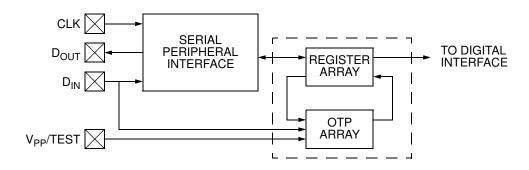

A block diagram illustrating the major elements of the device is shown in Figure 1-1.

Figure 1-1. Overall Block Diagram

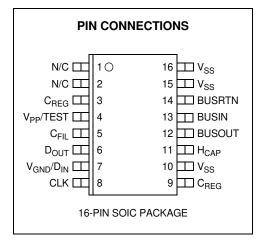

## 1.2 PACKAGE PINOUT

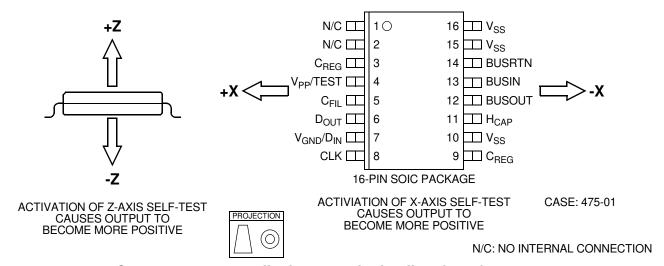

The pinout for this 16-pin device is shown in Figure 1-2.

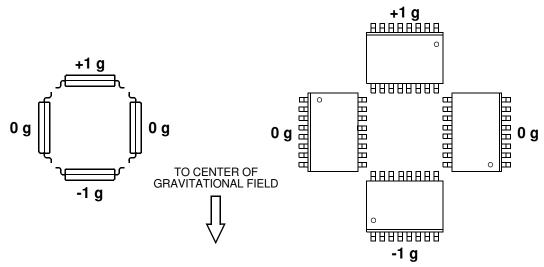

Output response to displacement in the direction of arrows.

Response to static orientation within 1 g field.

Figure 1-2. Device Pinout

## 1.3 PIN FUNCTIONS

The following paragraphs provide descriptions of the general function of each pin.

## 1.3.1 $H_{CAP}$ and $V_{SS}$

Power is supplied to the ASIC through BUSIN or BUSOUT and BUSRTN. The supply voltage is rectified internally and applied to the  $H_{CAP}$  pin. An external capacitor connected to HCAP forms the positive supply for the integrated voltage regulator.  $V_{SS}$  is supply return node. All  $V_{SS}$  pins are internally connected to BUSRTN. To obtain specified performance, all  $V_{SS}$  nodes should be connected to the BUSRTN node on the PWB. To ensure stability of the internal voltage regulator and meet DFMEA requirements, the connection from  $H_{CAP}$  to the external capacitor should be as short as possible and should not be routed elsewhere on the printed wiring assembly.

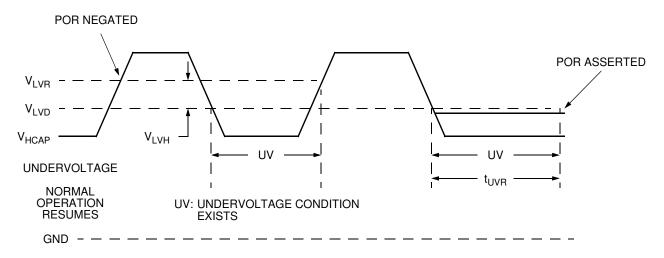

The voltage on  $H_{CAP}$  is monitored. If the voltage falls below a specified level, the device will return the value zero in response to a short word Read Acceleration Data command, and report the undervoltage condition by setting the Undervoltage (U) flag. Should the undervoltage condition persist for more than one millisecond, the internal Power-On Reset (POR) circuit is activated and the device will not respond until the voltage at  $H_{CAP}$  is restored to operating levels and the device has undergone post-reset initialization.

#### 1.3.2 BUSIN

The BUSIN pin is normally connected to the DSI bus and supports bidirectional communication with the master.

The MMA81XXEG, MMA82XXEG and MMA82XXTEG supports reverse initialization for improved system fault tolerance. In the event that the DSI bus cannot support communication between the master and BUSIN pin, communication with the master may be conducted via the BUSOUT pin and the BUSIN pin can be used to access other DSI devices.

#### 1.3.3 **BUSOUT**

The BUSOUT pin is normally connected to the DSI bus for daisy-chained bus configurations. In support of fault tolerance at the system level, the BUSOUT pin can be used as an input for reverse initialization and data communication.

The internal bus switch is always open following reset. The bus switch is closed when data bit D6 is set when an Initialization or Reverse Initialization command is received.

#### 1.3.4 **BUSRTN**

This pin provides the common return for power and signalling.

## 1.3.5 C<sub>REG</sub>

The internal voltage regulator requires external capacitance to the V<sub>SS</sub> pin for stability. This should be a high grade capacitor without excessive internal resistance or inductance. An optional electrolytic capacitor may be required if a longer power down delay is required.

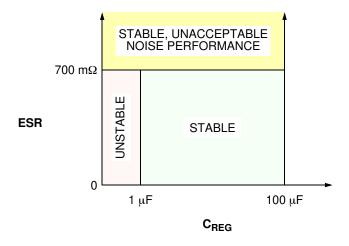

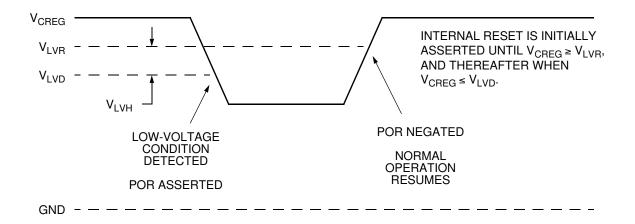

Figure 1-3 illustrates the relationship between capacitance, series resistance and voltage regulator stability. Two C<sub>REG</sub> pins are provided for redundancy. It is recommended that both C<sub>REG</sub> pins are connected to the external capacitor(s) for best system reliability.

Figure 1-3. Voltage Regulator Capacitance and Series Resistance

## 1.3.6 C<sub>FIL</sub>

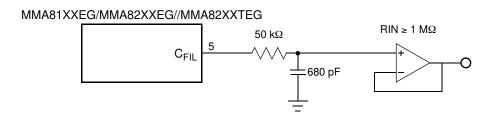

The output of the sensor interface circuitry can be monitored at the  $C_{FIL}$  pin. An internal buffer is provided to provide isolation between external signals and the input to the A/D converter. If  $C_{FIL}$  monitoring is desired, a low-pass filter and a buffer with high input impedance located as close to this pin as possible are required. The circuit configuration shown in Figure 1-5 is recommended.

Figure 1-4. CFIL Filter and Buffer Configuration

This pin may be configured as an input to the A/D converter when the MMA81XXEG, MMA82XXEG and MMA82XXTEG devices are in test mode. Refer to Appendix A for further details regarding test mode operation.

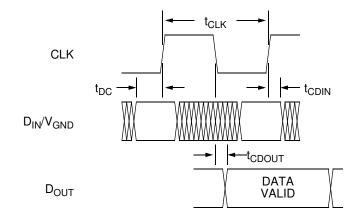

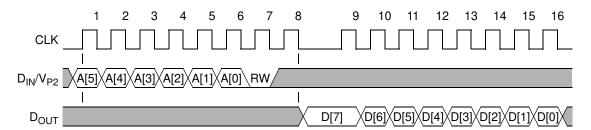

## 1.3.7 Trim/Test Pins (V<sub>PP</sub>/TEST, CLK, DOUT)

These pins are used for programming the device during manufacturing. These pins have internal pull-up or pull-down devices to drive the input when left unconnected. The following termination is recommended for these pins in the end application:

| PIN                   | Termination       |

|-----------------------|-------------------|

| V <sub>PP</sub> /TEST | Connect to ground |

| CLK                   | Leave unconnected |

| D <sub>OLIT</sub>     | Leave unconnected |

Table 1-1

CLK may be connected to ground, however this is not advised if the GLDE bit in DEVCFG2 is set, as a short between the adjacent  $V_{GND}/D_{IN}$  pin and ground prevents ground loss detection.

## 1.3.8 GND Detect Pin (V<sub>GND</sub>/D<sub>IN</sub>)

$V_{GND}/D_{IN}$  may be used to detect an open condition between the satellite module and chassis. The ground loss detector circuit supplies a constant current through  $V_{GND}/D_{IN}$  and measures resulting voltage. This determines the resistance between  $V_{GND}/D_{IN}$  and the system's virtual ground. A fault condition is signalled if the resistance exceeds specified limits. This pin has no internal pull-down device and must be connected as shown in Figure 1-5.

Ground loss detection circuitry is enabled when the GLDE bit is programmed to a logic '1' state in DEVCFG2. Ground loss detection is not available when the master operates in differential mode.  $V_{GND}/D_{IN}$  must be directly connected to BUSRTN if the DSI bus is configured for differential operation.  $V_{GND}/D_{IN}$  connection options are illustrated in Figure 1-5.

When ground loss detection is enabled, a constant current is sourced and the voltage at  $V_{GND}$  is continuously monitored. An open connection between  $V_{SS}$  and chassis ground will cause the voltage to rise. If the voltage indicates that the connection between chassis ground and  $V_{SS}$  has opened, a 14-bit counter is enabled. This counter will reverse if the voltage falls below the detection threshold. Should the counter overflow, a ground loss condition is indicated. The counter acts as a digital low-pass filter, to provide immunity from spurious signals.

This pin functions as the SPI data input when the device is in test mode.

#### **GROUND-LOSS DETECTION DISABLED**

# GROUND-LOSS DETECTION ENABLED (SINGLE-ENDED SYSTEMS ONLY)

#### MMA81XXEG/MMA82XXEG/MMA82XXTEG MMA81XXEG/MMA82XXEG/MMA82XXTEG 16 $V_{SS}$ $\mathsf{V}_{\mathsf{SS}}$ N/C N/C 2 3 4 5 15 15 N/C $V_{SS}$ N/C $V_{SS}$ 14 14 $\mathsf{C}_{\mathsf{REG}}$ **BUSRTN BUSRTN** O BUSRTN $C_{REG}$ 13 13 V<sub>PP</sub>/TEST **BUSIN** V<sub>PP</sub>/TEST **BUSIN** 12 12 BUSOUT $\mathsf{C}_{\mathsf{FIL}}$ BUSOUT CFIL 11 11 $\mathsf{D}_{\mathsf{OUT}}$ **HCAP** $\mathsf{D}_{\mathsf{OUT}}$ $H_{\mathsf{CAP}}$ 10 10 $\mathsf{V}_{\mathsf{SS}}$ V<sub>GND</sub>/D<sub>IN</sub> O BUSRTN V<sub>GND</sub>/D<sub>IN</sub> $V_{SS}$ 9 8 9 CLK $\mathsf{C}_{\mathsf{REG}}$ **CLK** $C_{\mathsf{REG}}$ $1.00 \text{ k}\Omega, 1\%$ O CHASSIS 1 nF

Figure 1-5. V<sub>GND</sub>/D<sub>IN</sub> Connection Options

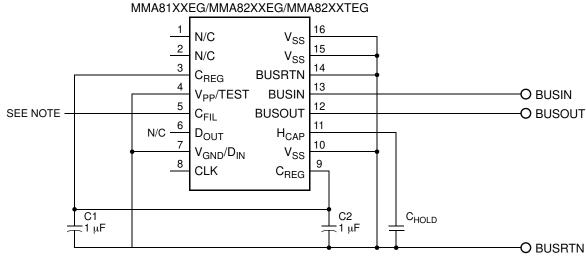

#### 1.4 MODULE INTERCONNECT

A typical satellite module configuration supporting daisy-chain configuration is shown in Figure 1-6. Capacitors C1 and C2 form a filter network for the internal voltage regulator. Two capacitors are shown for redundancy; this configuration improves reliability in the event of an open capacitor connection. A single 1  $\mu$ F capacitor may be used in place of C1 and C2, however connection from the capacitor to both CREG pins is required. CHOLD stores energy during signal transitions on BUSIN and BUSOUT. The value of this capacitor is typically 1  $\mu$ F; however, this depends upon data rates and bus utilization.

NOTE: LEAVE OPEN OR CONNECT TO SIGNAL MONITOR.

Figure 1-6. Typical Satellite Module Diagram

#### 1.5 DEVICE IDENTIFICATION

Thirty-two OTP bits are factory-programmed with a unique serial number during the manufacturing and test. Five additional bits are factory-programmed to indicate the full-scale range and axis of sensitivity. Device identification data may be read at any time while the device is active.

## SECTION 2 SUPPORT MODULES

## 2.1 MASTER OSCILLATOR

A temperature-compensated internal oscillator provides a stable timing reference for the device. The oscillator is factory-trimmed to operate at a nominal frequency of 4 MHz.

#### 2.2 VOLTAGE REGULATION

The internal voltage regulator has minimum voltage level detection, which will hold the device in reset and prevent data transmission should the regulator output fall during operation. The regulator also has an input voltage clamp to limit the power dissipated in the regulator during voltage spikes on the H<sub>CAP</sub> pin which might come from the two or three wire satellite bus.

## 2.3 BESSEL FILTER

180-Hz, 2-pole and 400 Hz 4-pole Bessel filter options are provided. The low-pass filter is implemented within a two stage switched capacitor amplifier. The overall gain of the Bessel filter is set to a fixed value. The output of the Bessel filter output acts as the input to the A/D converter and is also buffered and made available at the C<sub>FII</sub> pin.

#### 2.4 STATUS MONITORING

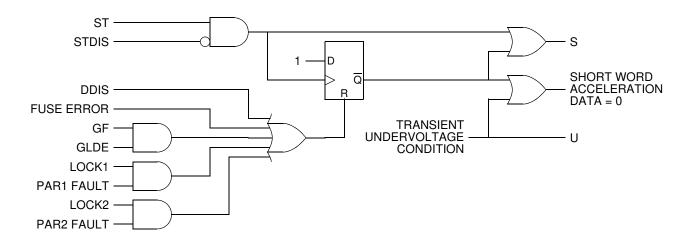

A number of abnormal conditions are detected by MMA81XXEG/MMA82XXEG/MMA82XXTEG and the behavior of the device altered if a fault is detected. Detected fault conditions and consequent device behavior is summarized in the table below. Certain conditions, e.g. ground loss, are qualified by device configuration. Figure 2-1 provides a representation of fault conditions, applicable qualifiers and effects.

**Table 2-1 Fault Condition Response Summary**

| Condition                                | Description                                                                      | Device Behavior                                                                                                        |

|------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Undervoltage, C <sub>REG</sub>           | Internally regulated voltage below operating level                               | Device continuously undergoes reset, bus switch open, no response to DSI commands                                      |

| Sustained Undervoltage, H <sub>CAP</sub> | Voltage at HCAP below operating level for more than 1 ms                         |                                                                                                                        |

| Frame Timeout                            | Bus voltage remains below frame threshold $(t_{TO})$ longer than specified time. |                                                                                                                        |

| Transient Undervoltage, H <sub>CAP</sub> | Voltage at HCAP below operating level for less than 1 ms                         | Undervoltage (U) flag set, short-word Read<br>Acceleration Data response value equals zero                             |

| Fuse Fault                               | OTP fuse threshold failure                                                       | Accelerometer Status (S) flag set, short-word Read                                                                     |

| Parity Fault                             | Parity failure detected in factory or customer programmed OTP data               | Acceleration Data response value equals zero                                                                           |

| Ground Fault                             | Ground loss detected for more than 4.096 ms                                      | Accelerometer Status (S) and Ground Fault (GF) flags set, short-word Read Acceleration Data response value equals zero |

| KEY:       |                                                |

|------------|------------------------------------------------|

| DDIS       | DEVICE DISABLE BIT, DEVCFG2[4]                 |

| FUSE FAULT | OTP FUSE THRESHOLD FAILURE                     |

| GLDE       | GROUND LOSS DETECTION BIT, DEVCFG2[5]          |

| GF         | GROUND FAULT DETECTION CONDITION               |

| LOCK1      | FACTORY PROGRAMMED OTP LOCK BIT                |

| LOCK2      | CUSTOMER PROGRAMMED OTP LOCK BIT               |

| PAR1 FAULT | FACTORY PROGRAMMED OTP PARITY FAULT CONDITION  |

| PAR2 FAULT | CUSTOMER PROGRAMMED OTP PARITY FAULT CONDITION |

| S          | ACCELEROMETER STATUS FLAG                      |

| ST         | SELF-TEST ACTIVATION CONDITION                 |

| STDIS      | SELF-TEST DISABLE                              |

| U          | UNDERVOLTAGE FLAG                              |

Figure 2-1. Status Logic Representation

The signal STDIS in Figure 2-1 is set when self-test lockout is activated through the execution of two consecutive Disable Self-Test Stimulus commands, as described in Section 4.6.6. If self-test lockout has been activated, a DSI Clear command or power-on reset is required to clear a fault condition which results in reset of the D flip-flop.

## **SECTION 3 OTP MEMORY**

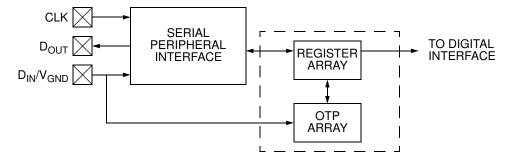

MMA81XXEG/MMA82XXEG/MMA82XXTEG family features One-Time-Programmable (OTP) memory implemented via a fuse array. OTP is organized as an array of 96 bits which contains the trim data, configuration data, and serial number for each device. Sixteen bits of the OTP array may be programmed by the customer through the DSI Bus.

### 3.1 INTERNAL REGISTER ARRAY AND OTP MEMORY

Contents of OTP memory are transferred to a set of registers following power-on reset, after which the OTP array is powered-down. Contents of the register array are static and may be read at any time following the transfer of data from the OTP memory. Write operations to OTP mirror registers are supported when the device is in test mode, however any data stored in the register will be lost when the device is powered down. The mirror registers are also restored when an OTP read operation is performed.

In addition to the registers which mirror OTP memory contents, several other registers are provided. Among these are the OTP Control Registers which controls OTP programming operations and may be used to restore the registers from the OTP memory.

Figure 3-1. OTP Interface Overview

## 3.2 OTP WORD ASSIGNMENT

Customer-accessible OTP bits are shown in Table 3-1. Unprogrammed OTP bits are read as logic '0' values. DEVCFG1, DEVCFG2 and registers REG-8 through REG-F are programmed by the customer. Other bits are programmed and locked during manufacturing. There is no requirement to program any bits in DEVCFG1 or DEVCFG2 for the device to be fully operational.

| Lo      | cation   |       |      |               | Bit Fu  | nction     |      |      |      |  |  |  |

|---------|----------|-------|------|---------------|---------|------------|------|------|------|--|--|--|

| Address | Register | 7     | 6    | 5             | 4       | 3          | 2    | 1    | 0    |  |  |  |

| \$00    | SN0      | S7    | S6   | S5            | S4      | S3         | S2   | S1   | S0   |  |  |  |

| \$01    | SN1      | S15   | S14  | S13           | S12     | S11        | S10  | S9   | S8   |  |  |  |

| \$02    | SN2      | S23   | S22  | S21           | S20     | S19        | S18  | S17  | S16  |  |  |  |

| \$03    | SN3      | S31   | S30  | S29           | S28     | S27        | S26  | S25  | S24  |  |  |  |

| \$04    | TYPE     | ORDER | 0    | AXIS          | 0       | 0          | RNG2 | RNG1 | RNG0 |  |  |  |

| \$05    | RESERVED | 0     | 0    | 0             | 0       | 0          | 0    | 0    | 0    |  |  |  |

| \$06    | DEVCFG1  |       | Cı   | ustomer Defin |         | AT1        | AT0  |      |      |  |  |  |

| \$07    | DEVCFG2  | LOCK2 | PAR2 | GLDE          | DDIS    | AD3        | AD2  | AD1  | AD0  |  |  |  |

| \$08    | REG-8    |       |      |               | Custome | r Defined  |      |      |      |  |  |  |

| \$09    | REG-9    |       |      |               | Custome | er Defined |      |      |      |  |  |  |

| \$0A    | REG-A    |       |      |               | Custome | er Defined |      |      |      |  |  |  |

| \$0B    | REG-B    |       |      |               | Custome | er Defined |      |      |      |  |  |  |

| \$0C    | REG-C    |       |      |               | Custome | er Defined |      |      |      |  |  |  |

| \$0D    | REG-D    |       |      |               | Custome | er Defined |      |      |      |  |  |  |

| \$0E    | REG-E    |       |      |               | Custome | er Defined |      |      |      |  |  |  |

| \$0F    | REG-F    |       |      |               | Custome | r Defined  |      |      |      |  |  |  |

**Table 3-1 Customer Accessible Data**

#### 3.2.1 Device Serial Number

A unique serial number is programmed into each device during manufacturing. The serial number is composed of the following information.

**Table 3-2 Serial Number Assignment**

| Bit Range | Content       |

|-----------|---------------|

| S12 - S0  | Serial Number |

| S31 - S13 | Lot Number    |

Lot numbers begin at 1 for all devices produced and are sequentially assigned. Serial numbers begin at 1 for each lot, and are sequentially assigned. No lot will contain more devices than can be uniquely identified by the 13-bit serial number. Not all allowable lot numbers and serial numbers will be assigned.

## 3.2.2 Type Byte

The Type Byte is programmed at final trim and test to indicate the axis of orientation of the g-cell and the calibrated range of the device.

Table 3-3 Device Type Register

| Loc     | ation    | Bit Function |   |      |   |   |      |      |      |

|---------|----------|--------------|---|------|---|---|------|------|------|

| Address | Register | 7            | 6 | 5    | 4 | 3 | 2    | 1    | 0    |

| \$04    | TYPE     | ORDER        | 0 | AXIS | 0 | 0 | RNG2 | RNG1 | RNG0 |

#### 3.2.2.1 Filter Characteristic Bit (ORDER)

This bit denotes the low-pass filter characteristic.

0 - 400 Hz, 4-pole

1 - 180 Hz, 2-pole

#### 3.2.2.2 Bit 6

Bit 6 is reserved. It will always be read as a logic '0' value.

#### 3.2.2.3 Axis of Sensitivity Bit (AXIS)

The AXIS bit indicates direction of sensitivity

0 - Z-axis

1 - X-axis

#### 3.2.2.4 Bit 4, Bit 3

Bit 4 and Bit 3 are reserved. They will always be read as a logic '0' value.

## 3.2.2.5 Full-Scale Range Bits (RNG2 - RNG0)

These three bits define the calibrated range of the device as follows:

Table 3-4

| RNG2 | RNG1 | RNG0 | Range  |  |  |

|------|------|------|--------|--|--|

| 0    | 0    | 0    | Unused |  |  |

| 0    | 0    | 1    | 20g    |  |  |

| 0    | 1    | 0    | 40g    |  |  |

| 0    | 1    | 1    | 50g    |  |  |

| 1    | 0    | 0    | 100g   |  |  |

| 1    | 0    | 1    | 150g   |  |  |

| 1    | 1    | 0    | 250g   |  |  |

| 1    | 1    | 1    | Unused |  |  |

#### 3.2.3 Configuration Bytes

Two customer-programmable configuration bytes are assigned.

### 3.2.4 Device Configuration Byte 1 (DEVCFG1)

Table 3-5 Device Configuration Byte 1

| Loc     | ation    | Bit Function |               |               |  |  |      |      |  |  |

|---------|----------|--------------|---------------|---------------|--|--|------|------|--|--|

| Address | Register | 7            | 7 6 5 4 3 2 1 |               |  |  |      |      |  |  |

| \$06    | DEVCFG1  |              | Cı            | ustomer Defin |  |  | ATT1 | ATT0 |  |  |

Configuration Byte 1 contains three defined bit functions, plus five bits that can be programmed by the customer to designate any coding desired for packaging axis, model, etc.

## 3.2.5 Attribute Bits (AT1, AT0)

These bits may be assigned by the customer as desired. They are transmitted by MMA81XXEG/MMA82XXEG/MMA82XXTEG in response to Request Status, Disable Self-Test Stimulus or Enable Self-Test Stimulus commands, as described in Section 4.

## 3.2.6 Device Configuration Byte 2 (DEVCFG2)

**Table 3-6 Device Configuration Byte 2**

| Location Bit Function |          |       |      |      |      |     |     |     |     |

|-----------------------|----------|-------|------|------|------|-----|-----|-----|-----|

| Address               | Register | 7     | 6    | 5    | 4    | 3   | 2   | 1   | 0   |

| \$07                  | DEVCFG2  | LOCK2 | PAR2 | GLDE | DDIS | AD3 | AD2 | AD1 | AD0 |

Configuration Byte 2 contains six bits that can be programmed by the customer to control device configuration, along with parity and lock bits for DEVCFG1 and DEVCFG2.

#### 3.2.6.1 Customer Data Lock Bit (LOCK2)

The bits in configuration bytes 1 and 2 are frozen when the LOCK2 bit is programmed. The LOCK2 bit is not included in the parity check. Locking does not take effect after this bit is programmed until the device has been subsequently reset.

- 0 Customer-programmed data area unlocked.

- 1 Programming operations inhibited.

The DDIS bit is not affected by LOCK2 and may be programmed at any time.

#### 3.2.6.2 Customer Data Parity Bit (PAR2)

The PAR2 parity bit is used for detecting changes in configuration bytes 1 and 2 along with registers REG-8 through REG-F (addresses \$06 through \$0F, inclusive). A fault condition is indicated if a change to parity-protected register data is detected. The PAR2 bit follows an "even" parity scheme (number of logical HIGH bits including parity bit is even).

If an internal parity error is detected, the device will respond to Read Acceleration Data commands with zero in the data field, as described in Section 4.5.4. The Status (S) bit will be set in either short word or long word responses to indicate the fault condition.

A parity fault may result from a bit failure within the OTP or the registers which store an image of the OTP during operation. In the latter case, power-on reset will clear the fault when the registers are re-loaded. A parity fault associated with the OTP array is a non-recoverable failure.

The parity status of customer programmed data is not monitored if the LOCK2 bit is not programmed to a logic '1' state.

#### 3.2.6.3 Ground Loss Detection Enable (GLDE)

When this bit is programmed to a logic '1' value, ground loss errors will be reported if a ground fault condition is detected.

- 1 Ground-loss detection circuitry enabled

- 0 Ground-loss detection disabled.

#### 3.2.6.4 Device Disable Bit (DDIS)

This bit may be programmed at any time, regardless of the state of LOCK2. This bit is intended to be programmed when a module has been determined by the DSI Bus Master to be defective. Programming this bit after LOCK2 has been set will cause the device to respond to short word Read Acceleration Data commands with a zero response. Acceleration results are not affected by this bit when long word Read Acceleration Data commands are executed, however the Status (S) bit will be set in the response.

- 1 Device responds to Read Acceleration Data command with zero value

- 0 Device responds normally to Read Acceleration Data command

## 3.2.6.5 Device Address (AD3 - AD0)

These bits define the pre-programmed DSI Bus device address.

#### 3.3 OTP PROGRAMMING

Two different methods of programming the eighty customer defined bits are supported. In test mode, these may be programmed in the same manner as factory programmed OTP bits. Additionally, the Read Write NVM DSI bus command may be used. Test mode programming operations are described in Appendix A.3. Read Write NVM command operation is described in Section 4.6.3.

## SECTION 4 PHYSICAL LAYER AND PROTOCOL

MMA81XXEG/MMA82XXEG/MMA82XXTEG family is compliant with the DSI Bus Standard, Version 2.0. MMA81XXEG/MMA82XXEG/MMA82XXTEG is designed to be compatible with either DSI Version 2 or DSI Version 1.1 compliant bus masters.

#### 4.1 DSI NETWORK PHYSICAL LAYER INTERFACE

Refer to Section 3 of the DSI Bus Standard for information regarding the physical layer interface.

#### 4.2 DSI NETWORK DATA LINK LAYER

Refer to **Section 4** of the DSI Bus Standard for information regarding the DSI network data link layer interface. Both standard and enhanced command structures are supported for short word and long word commands.

#### 4.3 DSI BUS COMMANDS

DSI Bus Commands which are recognized by MMA81XXEG and the MMA82XXEG/MMA82XXTEG are summarized in Table 4-1. Detailed descriptions of each supported command are described in subsequent sections of this document. If a CRC error is detected, or a reserved or unimplemented command is received, the device will not respond.

Following all messages, MMA81XXEG and the MMA82XXEG/MMA82XXTEG disregards the DSI bus voltage level for approximately 18.5 µs. Within this time, all supported commands except Initialization and Reverse Initialization are guaranteed to be executed and the device will be ready for the next message. When the bus voltage falls below the signal high logic level (see Section 5) after the 18.5 µs period has elapsed, the device will respond as appropriate to a command sent to it in the previous message. Exactly one response is attempted; if a noise spike or corrupted transfer occurs, the response is not retried.

If an Initialization or Reverse Initialization command is executed and the Bus Switch (BS) bit is set, MMA81XXEG, MMA82XXEG and MMA82XXTEG will disregard the bus voltage level for a nominal period of 180  $\mu$ s. This interval allows for the bus voltage to recover following closure of the bus switch, while the hold capacitor of a downstream slave charges.

Command Data Binary Size Hex Description C0 D7 D4 D3 C3 C2 C1 D6 D5 D2 D1 D0 В0 0 0 \$0 Initialization I W NV BS B1 PA3 PA2 PA<sub>1</sub> PA0 n 0 0 SW 0 0 1 \$1 Request Status 0 0 0 \$2 1 Read Acceleration Data SW 0 0 \$3 Not Implemented N/A 1 1 Not Applicable Request ID Information SW 0 1 0 0 \$4 Not Applicable 0 1 0 1 \$5 Not Implemented N/A 0 1 1 0 \$6 Not Implemented N/A Not Applicable 0 1 1 1 \$7 Clear SW 1 0 0 0 \$8 Not Implemented N/A Not Applicable Read Write NVM 0 0 1 LW RA3 RA2 RA0 RD2 RD1 1 \$9 RA<sub>1</sub> RD3 RD0 Format Control R/W FD2 FD0 1 0 1 0 \$A LW FA2 FA1 FA0 FD3 FD1 1 0 1 1 \$B Read Register Data LW 0 0 0 0 RA3 RA2 RA1 RA0 1 0 SW 1 0 \$C Disable Self-Test Stimulus 1 1 0 1 \$D Activate Self-Test Stimulus SW 1 1 0 \$E Reserved N/A 1 Not Applicable 1 1 1 1 \$F Reverse Initialization LW NV BS B<sub>1</sub> B0 PA3 PA2 PA<sub>1</sub> PA0

Table 4-1 DSI Bus Command Summary

## Legend:

BS: Bus Switch Control (0: open, 1: close)

NV: Nonvolatile memory control (1: program NVM)

PA3 - PA0: Device address assigned during Initialization or Reverse Initialization

RA3 - RA0: Internal user data register address

FA2 - FA0: Format register address

FD3 - FD0: Format register data content

## 4.4 COMMAND RESPONSE SUMMARIES

The device incorporates an analog-to-digital converter which translates the low-pass filtered acceleration signal to a 10-bit binary value. The 10-bit digital result is referred to as AD9 through AD0 in the response tables which follow.

## 4.4.1 Short Word Response Summary

Short word responses for all commands are summarized below. Detailed DSI command descriptions may be found in Section 4.5.

**Table 4-2 Short-Word Response Summary**

|     | Command                     |             |                |    | Resp   | onse     |     |    |    |  |  |  |

|-----|-----------------------------|-------------|----------------|----|--------|----------|-----|----|----|--|--|--|

| Hex | Description                 | D7          | D6             | D5 | D4     | D3       | D2  | D1 | D0 |  |  |  |

| \$0 | Initialization              |             | Not Applicable |    |        |          |     |    |    |  |  |  |

| \$1 | Request Status              | NV          | U              | ST | BS     | AT1      | AT0 | S  | GF |  |  |  |

| \$2 | Read Acceleration Data      |             |                | Se | ee Sec | tion 4.5 | 5.4 |    |    |  |  |  |

| \$3 | Not Implemented             | No Response |                |    |        |          |     |    |    |  |  |  |

| \$4 | Request ID Information      | V2          | V1             | V0 | 0      | 0        | 1   | 0  | 0  |  |  |  |

| \$5 | Not Implemented             | No Response |                |    |        |          |     |    |    |  |  |  |

| \$6 | Not Implemented             | No Response |                |    |        |          |     |    |    |  |  |  |

| \$7 | Clear                       |             |                |    | No Re  | sponse   | )   |    |    |  |  |  |

| \$8 | Not Implemented             |             |                |    | No Re  | sponse   | )   |    |    |  |  |  |

| \$9 | Read/Write NVM              |             |                |    | Not    | Valid    |     |    |    |  |  |  |

| \$A | Format Control              | Not Valid   |                |    |        |          |     |    |    |  |  |  |

| \$B | Read Register Data          |             |                |    | Not    | Valid    |     |    |    |  |  |  |

| \$C | Disable Self-Test Stimulus  | NV          | U              | ST | BS     | AT1      | AT0 | S  | GF |  |  |  |

| \$D | Activate Self-Test Stimulus | NV          | U              | ST | BS     | AT1      | AT0 | S  | GF |  |  |  |

| \$E | Reserved                    | No Response |                |    |        |          |     |    |    |  |  |  |

| \$F | Reverse Initialization      | Not Valid   |                |    |        |          |     |    |    |  |  |  |

## Legend:

AT1 - AT0: Attribute codes (see Section 4.5.1.3)

NV: State of fuse program control bit

BS: State of Bus Switch (0: open, 1: closed)

S: Accelerometer status flag (1: internal error)

ST: Self-Test flag (1: self-test active)

U - Undervoltage condition

V2 - V0: Version ID

## 4.4.2 Long Word Response Summary

Long word responses for all commands are summarized below. Detailed DSI command descriptions may be found in Section 4.5.

**Table 4-3 Long-Word Response Summary**

|     | Command                     |             |     |     |     |     |     |     | Rosn   | onse   |       |          |     |     |     |     |     |

|-----|-----------------------------|-------------|-----|-----|-----|-----|-----|-----|--------|--------|-------|----------|-----|-----|-----|-----|-----|

|     | 1                           |             |     | 1   | 1   |     | 1   | ı   |        |        | ı     | ı        |     | ı   |     | 1   | Т   |

| Hex | Description                 | D15         | D14 | D13 | D12 | D11 | D10 | D9  | D8     | D7     | D6    | D5       | D4  | D3  | D2  | D1  | D0  |

| \$0 | Initialization              | А3          | A2  | A1  | A0  | 0   | 0   | 0   | BF     | NV     | BS    | B1       | В0  | PA3 | PA2 | PA1 | PA0 |

| \$1 | Request Status              | A3          | A2  | A1  | A0  | 0   | 0   | 0   | 0      | NV     | U     | ST       | BS  | AT1 | AT0 | S   | GF  |

| \$2 | Read Acceleration Data      | A3          | A2  | A1  | A0  | GF  | S   | AD9 | AD8    | AD7    | AD6   | AD5      | AD4 | AD3 | AD2 | AD1 | AD0 |

| \$3 | Not Implemented             | No Response |     |     |     |     |     |     |        |        |       |          |     |     |     |     |     |

| \$4 | Request ID Information      | A3          | A2  | A1  | A0  | 0   | 0   | 0   | 0      | V2     | V1    | V0       | 0   | 0   | 1   | 0   | 0   |

| \$5 | Not Implemented             | No Response |     |     |     |     |     |     |        |        |       |          |     |     |     |     |     |

| \$6 | Not Implemented             | No Response |     |     |     |     |     |     |        |        |       |          |     |     |     |     |     |

| \$7 | Clear                       |             |     |     |     |     |     | !   | No Res | sponse | )     |          |     |     |     |     |     |

| \$8 | Not Implemented             |             |     |     |     |     |     | !   | No Res | sponse | )     |          |     |     |     |     |     |

| \$9 | Read/Write NVM              | A3          | A2  | A1  | A0  |     |     |     |        | Se     | e Sec | tion 4.6 | 5.3 |     |     |     |     |

| \$A | Format Control              | A3          | A2  | A1  | A0  | 0   | 1   | 1   | 0      | R/W    | FA2   | FA1      | FA0 | FD3 | FD2 | FD1 | FD0 |

| \$B | Read Register Data          | A3          | A2  | A1  | A0  | RA3 | RA2 | RA1 | RA0    | RD7    | RD6   | RD5      | RD4 | RD3 | RD2 | RD1 | RD0 |

| \$C | Disable Self-Test Stimulus  | A3          | A2  | A1  | A0  | 0   | 0   | 0   | 0      | NV     | U     | ST       | BS  | AT1 | AT0 | S   | GF  |

| \$D | Activate Self-Test Stimulus | A3          | A2  | A1  | A0  | 0   | 0   | 0   | 0      | NV     | U     | ST       | BS  | AT1 | AT0 | S   | GF  |

| \$E | Reserved                    |             |     | •   | •   |     | •   |     | No Res | sponse | )     |          |     |     |     | •   |     |

| \$F | Reverse Initialization      | A3          | A2  | A1  | A0  | 0   | 0   | 0   | BF     | NV     | BS    | B1       | В0  | PA3 | PA2 | PA1 | PA0 |

#### Legend:

A3 - A0: Device address

AD9 - AD0: 10-bit acceleration data result

AT1 - AT0: Attribute codes (see Section 4.5.1.3)

BF: Bus Fault flag (1: bus fault)

BS: State of Bus Switch (0: open, 1: closed)

FA2 - FA0: Format register address

FD3 - FD0: Format register data content

GF: Ground fault detected

NV: State of fuse program control bit

PA3 - PA0: Device address assigned during Initialization/Reverse Initialization

RA3 - RA 0: Internal user data register address

RD7 - RD0: Internal user data register contents

R/W: Read/Write flag for Format Control Register access

S: Accelerometer Status Flag (1: internal error)

ST: Self-Test Flag (1: self-test active)

U - Undervoltage condition

V2 - V0: Version ID

## 4.5 DSI COMMAND DETAIL

Detailed descriptions of command formats and responses are provided in this section.

#### 4.5.1 DSI COMMAND AND RESPONSE BIT DESCRIPTIONS

The following abbreviations are used in the descriptions of DSI commands and responses.

#### 4.5.1.1 DSI Device Address - (A3 - A0)

DSI device address. This address will be set to the pre-programmed device address following reset, or zero if no pre-programmed address has been assigned. If zero, the device address may be assigned during initialization or reverse initialization.

#### 4.5.1.2 Acceleration Data - (AD9 - AD0)

Ten-bit acceleration result produced by the device. This value is returned by the Read Acceleration Data command, described in Section 4.5.4.

#### 4.5.1.3 Attribute Code Bits (AT1, AT0)

These bits indicate the contents of DEVCFG1 bits 1 and 0 in response to a Request Status, Activate Self-Test Stimulus or Disable Self-Test Stimulus command.

| LOCK2 | DEVGFG1[1] | DEVGFG1[0] | AT1 | AT0 |

|-------|------------|------------|-----|-----|

| 0     | Х          | Х          | 1   | 0   |

| 1     | 0          | 0          | 0   | 0   |

|       | 0          | 1          | 0   | 1   |

|       | 1          | 0          | 1   | 0   |

|       | 1          | 1          | 1   | 1   |

**Table 4-4 Attribute Code Bit Assignments**

## 4.5.1.4 Bank Select (B1, B0)

These bits are assigned during initialization or reverse initialization to select specific fields within the customer accessible data registers. Bank selection affects Read/Write NVM command operation. Invalid combinations of B1 and B0 result in no response from the device to the associated initialization or reverse initialization command.

Refer to Section 4.6.3 for further details regarding register programming and bank selection.

#### 4.5.1.5 Bus Fault Bit (BF)

This bit indicates the success or failure of the bus test which is performed as part of an Initialization or Reverse Initialization command.

- 1 Bus fault detected

- 0 Bus test passed

## 4.5.1.6 Bus Switch Control/Status Bit (BS)

This bit controls the state of the bus switch during an Initialization or Reverse Initialization command. It also indicates the state of the bus switch in response to the Initialization, Request Status, Disable Self-Test Stimulus, Activate Self-Test Stimulus and Reverse Initialization commands.

- 1 Close bus switch, or bus switch closed

- 0 Leave bus switch open, or bus switch opened

## 4.5.1.7 Format Control Register Address (FA2 - FA0)

This three-bit field selects one of eight format control registers. Format control registers are described in Section 4.6.4.3.

#### 4.5.1.8 Format Register Data (FD3 - FD0)

Contents of a format control register. This is the data to be written to the register by a Format Control command, or the contents read from the register in response to a Format Control command.

#### 4.5.1.9 Ground Fault Flag (GF)

If ground loss detection has been enabled and a ground fault condition is detected, this bit will be set in the response to Request Status, Read Acceleration Data, Disable Self-Test Stimulus or Activate Self-Test Stimulus commands. If ground loss detection is not enabled, this bit will always be read as a logic '0' value.

- 1 Ground fault condition detected

- O Ground connection within specified limits, or ground loss detection disabled.

#### 4.5.1.10 Nonvolatile Memory Program Control Bit (NV)

This bit enables programming of customer-programmed OTP locations when set during an Initialization or Reverse Initialization command. Data to be programmed are transferred to the device during subsequent Read Write NVM commands.

- 1 Enable OTP programming

- 0 OTP programming circuitry disabled

#### 4.5.1.11 Assigned Device Address (PA3 - PA0)

This field contains the device address to be assigned during an Initialization or Reverse Initialization command. The address assigned is reported by the device in response to the Initialization or Reverse Initialization command.

#### 4.5.1.12 Register Address (RA3 - RA0)

This field determines the register associated with a Read Write NVM or Read Register Data command. The two Bank Select bits (B1, B0) are used to additionally specify a nibble or bit when a Read Write NVM command is executed.

#### 4.5.1.13 Register Data (RD7 - RD0)

RD3 - RD0 contain data to be written to an OTP location when a Read Write NVM command is executed if the NV bit is set. RD3

- RD0 contain the data read from the selected register in response to a Read Write NVM command if the NV bit is cleared. RD7

- RD0 indicate the contents of the selected register in response to a Read Register Data command.

## 4.5.1.14 Format Control Register Read/Write Bit (R/W)

This bit controls the operation performed by a Format Control command.

- 1 Write Format Control register selected by FA2 FA0

- 0 Read Format Control register unless global command

## 4.5.1.15 Accelerometer Status Flag (S)

This bit provides a cumulative indication of the various error conditions which are monitored by the device.

- 1 Either one or more error conditions have been detected and/or the internal Self-Test stimulus circuitry is active

- 0 No error condition has been detected

The following conditions will cause the status flag to be set:

\*Internal Self-Test stimulus circuitry is active

OTP array parity fault

OTP fuse threshold fault (partially-programmed fuse)

Transient undervoltage condition

Ground fault (if GLDE bit in DEVCFG2 is set)

#### 4.5.1.16 Self-Test State (ST)

This bit indicates whether internal self-test stimulus circuitry is active in response to Request Status, Disable Self-Test Stimulus and Activate Self-Test Stimulus commands.

- 1 Self-Test stimulus active

- 0 Self-Test stimulus disabled

## 4.5.1.17 Undervoltage Flag (U)

This flag is set if the voltage at HCAP is below a specified threshold. Refer to Section 1.3.1 and Section 5 for further details.

#### 4.5.2 Initialization Command

The initialization command conforms to the description provided in **Section 6.2.1** of the DSI Bus Standard, Version 2.0. At power-up the device is fully compliant with the DSI 1.1 protocol. The initialization command must be transmitted as a DSI 1.1 compliant long command structure. Features of the DSI 2.0 protocol can not be accessed until a valid DSI 1.1 compliant initialization sequence is performed and the enhanced mode format registers are properly configured.

Table 4-5 Initialization Command Structure

|    | Data D5 D4 D3 D2 D1 D |    |    |     |     |     |     |    | Add | ress |    |    | Comi | mand |    | CRC    |

|----|-----------------------|----|----|-----|-----|-----|-----|----|-----|------|----|----|------|------|----|--------|

| D7 | D6                    | D5 | D4 | D3  | D2  | D1  | D0  | A3 | A2  | A1   | A0 | C3 | C2   | C1   | C0 |        |

| NV | BS                    | B1 | В0 | PA3 | PA2 | PA1 | PA0 | А3 | A2  | A1   | A0 | 0  | 0    | 0    | 0  | 4 bits |

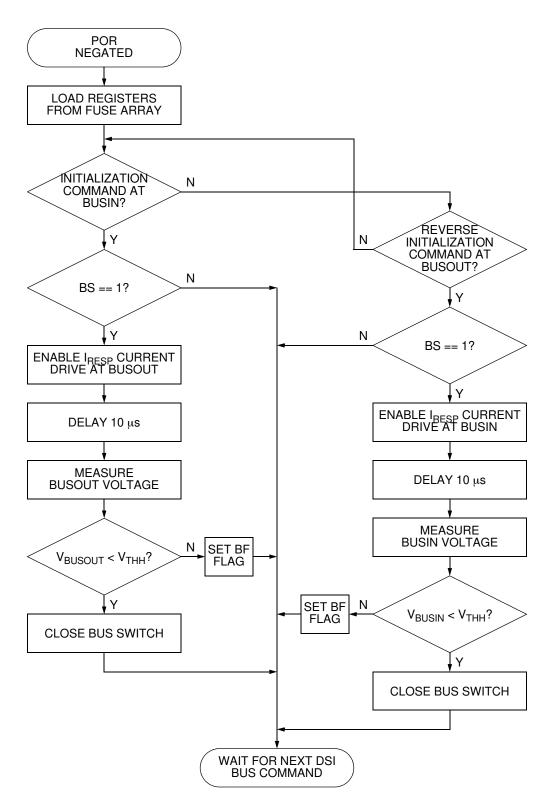

Figure 4-1 illustrates the sequence of operations performed following negation of internal Power-On Reset (POR) and execution of a DSI Initialization command. Initialization commands are recognized only at BUSIN. The BUSOUT node is tested for a bus short to battery high voltage condition, and the Bus Fault (BF) flag set if an error condition is detected. If no bus fault condition is detected and the BS bit is set in the command structure, the bus switch will be closed. If the BS bit is set, the DSI bus voltage level is disregarded for approximately 180 μs following initialization to allow the hold capacitor on a downstream slave to charge.

If the device has been pre-programmed, PA3 - PA0 and A3 - A0 must match the pre-programmed address. If no device address has been previously programmed into the OTP array, PA3 - PA0 contain the device address, while A3 - A0 must be zero. If any addressing condition is not met, the device address is not assigned, the bus switch will remain open and the device will not respond to the Initialization command.

**Table 4-6 Initialization Command Response**

|                                                       |    |    |    |   |   |   | Da | nta |    |    |    |    |    |    |    | CRC    |

|-------------------------------------------------------|----|----|----|---|---|---|----|-----|----|----|----|----|----|----|----|--------|

| D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 |    |    |    |   |   |   |    |     |    |    |    |    |    |    |    |        |

| A3                                                    | A2 | A1 | A0 | 0 | 0 | 0 | BF | NV  | BS | B1 | В0 | A3 | A2 | A1 | A0 | 4 bits |

In the response, bits D15 - D12 and D3 - D0 will contain the device address. If the device was unprogrammed when the initialization command was issued, the device address is assigned as the command executes. Both fields will contain the value PA3 - PA0 to indicate successful device address assignment.

Initialization or reverse initialization commands which attempt to assign device address zero are ignored.

Figure 4-1. Initialization Sequence

## 4.5.3 Request Status Command

The Request Status command may be transmitted as either a DSI long command structure or a DSI short command structure of any length. The data field in the command structure is ignored but is included in the CRC calculation. No action is taken if this command is sent to the DSI Global Device Address.

**Table 4-1 Request Status Command Structure**

|    | Add | ress       |    |    | Comi | mand |    | CRC         |

|----|-----|------------|----|----|------|------|----|-------------|

| А3 | A2  | <b>A</b> 1 | A0 | C3 | C2   | C1   | C0 | CHO         |

| A3 | A2  | A1         | A0 | 0  | 0    | 0    | 1  | 0 to 8 bits |

Table 4-2 Short Response Structure - Request Status Command

| Response |     |     |     |     |     | Res | ponse |    |    |     |    |     |     |    |    |

|----------|-----|-----|-----|-----|-----|-----|-------|----|----|-----|----|-----|-----|----|----|

| Length   | D14 | D13 | D12 | D11 | D10 | D9  | D8    | D7 | D6 | D5  | D4 | D3  | D2  | D1 | D0 |

| 8        |     |     |     |     |     |     |       |    |    |     |    |     |     |    |    |

| 9        |     |     |     |     |     |     |       |    |    |     |    |     |     |    |    |

| 10       |     |     |     |     |     |     |       |    |    |     |    |     |     |    |    |

| 11       |     |     |     |     |     |     |       | NV | U  | ST  | BS | AT1 | AT0 | S  | GF |

| 12       |     |     |     | 0   | 0   | .,, |       |    |    | *** | /  |     | G.  |    |    |

| 13       |     |     |     | 0   | 0   | O   |       |    |    |     |    |     |     |    |    |

| 14       |     | 0   | 0   |     |     |     |       |    |    |     |    |     |     |    |    |

| 15       | 0   | U   |     |     |     |     |       |    |    |     |    |     |     |    |    |

Table 4-3 Long Response Structure - Request Status Command

|     | Data |     |     |     |     |    |    |    |    |    |    |     |     |    | CRC |             |

|-----|------|-----|-----|-----|-----|----|----|----|----|----|----|-----|-----|----|-----|-------------|

| D15 | D14  | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3  | D2  | D1 | D0  | Ono         |

| A3  | A2   | A1  | A0  | 0   | 0   | 0  | 0  | NV | U  | ST | BS | AT1 | AT0 | S  | GF  | 0 to 8 bits |

## 4.5.4 Read Acceleration Data Command

The Read Acceleration Data command may be transmitted as either a DSI long command structure or a DSI short command structure of any length. The data field in the command structure is ignored but is included in the CRC calculation. No action is taken if this command is sent to the DSI Global Device Address.

**Table 4-4 Read Acceleration Data Command Structure**

|    | Add | ress       |    |             | Com | mand |   | CRC         |

|----|-----|------------|----|-------------|-----|------|---|-------------|

| А3 | A2  | <b>A</b> 1 | A0 | C3 C2 C1 C0 |     |      |   | CHO         |

| A3 | A2  | A1         | A0 | 0           | 0   | 1    | 0 | 0 to 8 bits |

Table 4-5 Short Response Structure - Read Acceleration Data Command

| Response |     |     |     |     |     | Res | ponse |     |     |     |     |     |     |     |     |

|----------|-----|-----|-----|-----|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| Length   | D14 | D13 | D12 | D11 | D10 | D9  | D8    | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 8        |     |     |     |     |     |     |       | AD9 | AD8 | AD7 | AD6 | AD5 | AD4 | AD3 | AD2 |

| 9        |     |     |     |     |     |     | AD9   | AD8 | AD7 | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 |

Table 4-5 Short Response Structure - Read Acceleration Data Command

| Response |            |              |     |     |     | Res   | sponse |     |       |      |        |      |       |     |      |

|----------|------------|--------------|-----|-----|-----|-------|--------|-----|-------|------|--------|------|-------|-----|------|

| Length   | D14        | D13          | D12 | D11 | D10 | D9    | D8     | D7  | D6    | D5   | D4     | D3   | D2    | D1  | D0   |

| 10       |            |              |     |     |     |       |        |     |       |      |        |      |       |     |      |

| 11       |            |              |     |     |     |       |        |     |       |      |        |      |       |     |      |

| 12       |            |              |     |     |     | AD9   | AD8    | AD7 | AD6   | AD5  | AD4    | AD3  | AD2   | AD1 | AD0  |

| 13       |            |              |     | GF  | S   | 71.00 | 1,150  | 101 | 1,120 | 7.50 | ,,,,,, | 7120 | 1,102 | ,   | 7.50 |

| 14       |            | DEVCFG1[0]   | ST  | G.  |     |       |        |     |       |      |        |      |       |     |      |

| 15       | DEVCFG1[1] | DE 101 G1[0] |     |     |     |       |        |     |       |      |        |      |       |     |      |

Table 4-6 Long Response Structure - Read Acceleration Data Command

|     | Data |     |     |     |     |     |     |     |     |     |     |     |     | CRC |     |             |

|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------------|

| D15 | D14  | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Ono         |

| A3  | A2   | A1  | A0  | GF  | S   | AD9 | AD8 | AD7 | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | AD0 | 0 to 8 bits |

Data returned in response to a Read Acceleration Data command varies, as illustrated in Table 4-5 and Table 4-6. The result is also affected by the state of the self-test circuitry and internal parity. If the self-test circuitry is enabled, the ST bit will be set in data bit D12 of a short word response. If a transient undervoltage condition, parity fault, ground fault or device disable condition exists, the reserved data value of zero will be reported in response to a short word command structure to indicate that a fault condition has been detected. The data value is not affected by a fault condition when a long word response is reported, however the S and GF bits will be set as appropriate.

If the self-test circuitry is active, acceleration data is reported regardless of parity faults. The Status (S) bit will be set in either short word or long word responses if a parity fault is detected.

#### 4.5.4.1 ACCELERATION DATA REPRESENTATION

Acceleration values may be determined from the 10-bit digital output (DV) as follows:

$a = sensitivity \times (DV - 512)$

Sensitivity is determined by nominal full-scale range (FSR), linear range of digital values and a scaling factor to compensate for sensitivity error.

The linear range of digital values for MMA81XXEG/MMA82XXEG/MMA82XXTEG is 1 to 1023. The digital value of 0 is reserved as an error

indicator.

For the linear ranges of digital values indicated, the nominal value of 1 LSB for each full-scale range is shown in the table below.

Table 4-7 Nominal Sensitivity (10-bit data)

| Full-Scale Range (g) | Nominal Sensitivity (g/digit) |

|----------------------|-------------------------------|

| 250                  | 0.61                          |

| 150                  | 0.366                         |

| 100                  | 0.244                         |

| 50                   | 0.122                         |

| 40                   | 0.0976                        |

| 20                   | 0.0488                        |

#### 4.6 ACCELERATION MEASUREMENT TIMING

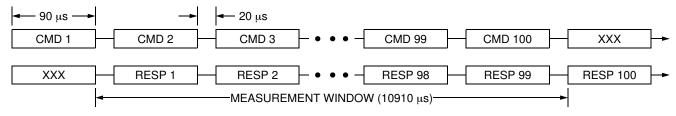

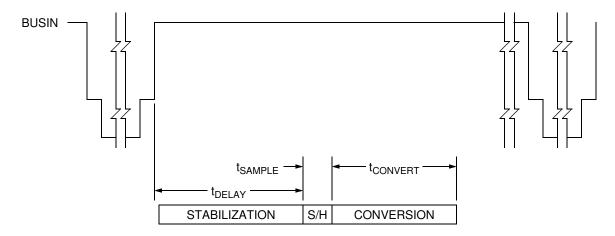

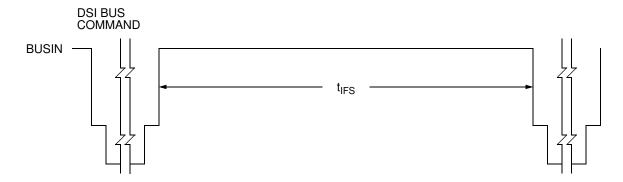

Upon verification of the CRC associated with a Read Acceleration Data command, MMA81XXEG/MMA82XXEG/MMA82XXTEG initiates an analog-to-digital conversion. The conversion occurs during the inter frame separation (IFS) and involves a delay during which the BUSIN line is allowed to stabilize, a sample period and finally the translation of the analog signal level to a digital result.

## 4.6.1 Request ID Information Command

The Request ID Information command may be transmitted as either a DSI long command structure or a DSI short command structure of any length. The data field in the command structure is ignored but is included in the CRC calculation. No action is taken by MMA81XXEG/MMA82XXEG/MMA82XXTEG if this command is sent to the DSI Global Device Address.

**Table 4-8 Request ID Information Command Structure**

|    | Add | ress |    |    | Comi | mand |    | CRC         |

|----|-----|------|----|----|------|------|----|-------------|

| A3 | A2  | A1   | A0 | C3 | C2   | C1   | C0 |             |

| A3 | A2  | A1   | A0 | 0  | 1    | 0    | 0  | 0 to 8 bits |

Table 4-9 Short Response Structure - Request ID Information Command

| Response |     |     |     |     |     | Res | ponse |    |     |     |    |    |    |    |    |

|----------|-----|-----|-----|-----|-----|-----|-------|----|-----|-----|----|----|----|----|----|

| Length   | D14 | D13 | D12 | D11 | D10 | D9  | D8    | D7 | D6  | D5  | D4 | D3 | D2 | D1 | D0 |

| 8        |     |     |     |     |     |     |       |    |     |     |    |    |    |    |    |

| 9        |     |     |     |     |     |     |       |    |     |     |    |    |    |    |    |

| 10       |     |     |     |     |     |     |       |    |     |     |    |    |    |    |    |

| 11       |     |     |     |     |     |     |       | V2 | V1  | V0  | 0  | 0  | 1  | 0  | 0  |

| 12       |     |     |     |     |     | 0   | 0     | ٧Z | V 1 | V 0 |    |    | '  |    |    |

| 13       |     |     |     | 0   | 0   | 0   |       |    |     |     |    |    |    |    |    |

| 14       |     | 0   | 0   |     |     |     |       |    |     |     |    |    |    |    |    |

| 15       | 0   |     |     |     |     |     |       |    |     |     |    |    |    |    |    |

Table 4-10 Long Response Structure - Request ID Information Command

|     |     |     |     |     |     |    | Da | ıta |    |    |    |    |    |    |    | CRC         |

|-----|-----|-----|-----|-----|-----|----|----|-----|----|----|----|----|----|----|----|-------------|

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0 | OHO         |

| A3  | A2  | A1  | A0  | 0   | 0   | 0  | 0  | V2  | V1 | V0 | 0  | 0  | 1  | 0  | 0  | 0 to 8 bits |

## 4.6.2 Clear Command

The Clear command may be transmitted as either a DSI long command structure or a DSI short command structure of any length. The data field in the command structure is ignored but is included in the CRC calculation.

**Table 4-11 Clear Command Structure**

|    | Add | ress       |    |    | Com | mand |    | CRC         |

|----|-----|------------|----|----|-----|------|----|-------------|

| А3 | A2  | <b>A</b> 1 | Α0 | СЗ | C2  | C1   | C0 | CITO        |

| A3 | A2  | A1         | A0 | 0  | 1   | 1    | 1  | 0 to 8 bits |

When a Clear Command is successfully decoded and the address field matches either the assigned device address or the DSI Global Device Address, the bus switch is opened and the device undergoes a full reset operation.

There is no response to the Clear Command.

#### 4.6.3 Read/Write NVM Command

The Read/Write NVM command must be transmitted as a DSI long command structure. No action is taken by MMA81XXEG/MMA82XXEG/MMA82XXTEG if this command is sent to the DSI Global Device Address.

#### Table 4-12 Read Write NVM Command Structure

|     |     |     | Da  | ata |     |     |     |    | Add | ress       |    |    | Comi | mand |    | CRC         |

|-----|-----|-----|-----|-----|-----|-----|-----|----|-----|------------|----|----|------|------|----|-------------|

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | А3 | A2  | <b>A</b> 1 | A0 | C3 | C2   | C1   | C0 | CITO        |

| RA3 | RA2 | RA1 | RA0 | RD3 | RD2 | RD1 | RD0 | A3 | A2  | A1         | A0 | 1  | 0    | 0    | 1  | 0 to 8 bits |

#### Table 4-13 Long Response Structure - Read/Write NVM Command (NV = 1)

|     |     |     |     |     |     |     | Da  | ıta |    |    |    |     |     |     |     | CRC         |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|-----|-----|-----|-----|-------------|

| D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6 | D5 | D4 | D3  | D2  | D1  | D0  | OHO         |

| A3  | A2  | A1  | A0  | RA3 | RA2 | RA1 | RA0 | 1   | 1  | B1 | В0 | RD3 | RD2 | RD1 | RD0 | 0 to 8 bits |

## Table 4-14 Long Response Structure - Read/Write NVM Command (NV = 0)

|     |     |     |     |     |     |    | Da | ıta |    |    |    |    |    |    |    | CRC         |

|-----|-----|-----|-----|-----|-----|----|----|-----|----|----|----|----|----|----|----|-------------|

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0 | OHO         |

| A3  | A2  | A1  | A0  | 0   | 0   | 0  | 0  | 1   | 1  | 1  | 1  | A3 | A2 | A1 | A0 | 0 to 8 bits |

There is no response if the Read/Write NVM Command is received within a DSI short command structure.

OTP data are accessed by fields, where a field is a combination of register address (RA3 - RA0) and bank select (B1, B0) bits. Bank select bits are assigned during an Initialization or Reverse Initialization command. Individual bits with predefined functions (the upper four bits of DEVCFG2) each have their own field address. The remaining OTP data are grouped into four-bit fields. Field addresses are shown in Table 4-15.

The structure of the OTP array results in data being programmed in 16-bit groups. DEVCFG1 and DEVCFG2 are in the same group. As a result, a non-zero device address assigned during Initialization or Reverse Initialization will be permanently programmed into the OTP array when any field within the two device configuration bytes is programmed.

To avoid programming a non-zero device address, ensure that device address 0 is assigned during Initialization or Reverse Initialization before programming any other bit(s) in DEVCFG1 or DEVCFG2.

OTP programming operations occur when the Read/Write NVM command is executed after the NV bit has been set during a preceding Initialization or Reverse Initialization command.

The minimum DSI Bus idle voltage must exceed 14 V when programming the OTP array.

When this command is executed while the NV bit is cleared, the DSI device address will be returned regardless of the state of the register address and bank select bits. The Read Register Data command (described in Section 4.6.5) may be used to access the full range of customer accessible data.

Table 4-15 OTP Field Assignments

| F   | Register | Addres | s   | Bank | Select | Register     | Definition             |

|-----|----------|--------|-----|------|--------|--------------|------------------------|

| RA3 | RA2      | RA1    | RA0 | B1   | В0     | negistei     | Deminion               |

| 0   | 1        | 1      | 0   | 0    | 1      | DEVCFG1[3:0] | User Defined           |

|     |          |        |     | 1    | 0      | DEVCFG1[7:4] |                        |

| 0   | 1        | 1      | 1   | 0    | 0      | DEVCFG2[7]   | LOCK2                  |

|     |          |        |     | 0    | 1      | DEVCFG2[3:0] | DSI Bus Device Address |

|     |          |        |     | 1    | 0      | DEVCFG2[5]   | GLDE                   |

|     |          |        |     | 1    | 1      | DEVCFG2[6]   | PAR2                   |

| 1   | 0        | 0      | 0   | 0    | 1      | REG8[3:0]    | User Defined           |

|     |          |        |     | 1    | 0      | REG8[7:4]    |                        |

| 1   | 0        | 0      | 1   | 0    | 1      | REG9[3:0]    | User Defined           |

|     |          |        |     | 1    | 0      | REG9[7:4]    |                        |

| 1   | 0        | 1      | 0   | 0    | 1      | REGA[3:0]    | User Defined           |

|     |          |        |     | 1    | 0      | REGA[7:4]    |                        |

| 1   | 0        | 1      | 1   | 0    | 1      | REGB[3:0]    | User Defined           |

|     |          |        |     | 1    | 0      | REGB[7:4]    |                        |

| 1   | 1        | 0      | 0   | 0    | 1      | REGC[3:0]    | User Defined           |

|     |          |        |     | 1    | 0      | REGC[7:4]    |                        |

| 1   | 1        | 0      | 1   | 0    | 1      | REGD[3:0]    | User Defined           |

|     |          |        |     | 1    | 0      | REGD[7:4]    |                        |

| 1   | 1        | 1      | 0   | 0    | 1      | REGE[3:0]    | User Defined           |

|     |          |        |     | 1    | 0      | REGE[7:4]    |                        |

| 1   | 1        | 1      | 1   | 0    | 1      | REGF[3:0]    | User Defined           |

|     |          |        |     | 1    | 0      | REGF[7:4]    |                        |

|     |          |        |     | 1    | 1      | DEVCFG[4]    | DDIS                   |

## 4.6.4 Format Control Command

The Format Control command must be transmitted as a DSI long command structure. No change to the format registers occurs if the Format Control Command is received within a DSI short command structure.

If this command is sent to the DSI Global Device Address, the format registers are updated, however there is no response.

The Format Control command conforms to the DSI 2.0 Specification.

**Table 4-16 Format Control Command Structure**

|     |     |     | Da  | ata |     |     |     |    | Add | ress       |    |    | Com | mand |    | CRC         |

|-----|-----|-----|-----|-----|-----|-----|-----|----|-----|------------|----|----|-----|------|----|-------------|

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | А3 | A2  | <b>A</b> 1 | Α0 | C3 | C2  | C1   | C0 | OHO         |

| R/W | FA2 | FA1 | FA0 | FD3 | FD2 | FD1 | FD0 | A3 | A2  | A1         | A0 | 1  | 0   | 1    | 0  | 0 to 8 bits |

## 4.6.4.1 Format Register Read/Write Control Bit (R/W)

- 1 Write Format Control register selected by FA2 FA0

- 0 Read Format Control register unless global command

#### 4.6.4.2 Format Control Register Selection (FA2 - FA0)

This three-bit field selects one of eight format control registers. Format control registers are described in Section 4.6.4.3.

Table 4-17 Long Response Structure - Format Control Command

|     |     |     |     |     |     |    | Da | ita |     |     |     |     |     |     |     | CRC         |

|-----|-----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-------------|

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | OHO         |

| A3  | A2  | A1  | A0  | 0   | 1   | 1  | 0  | R/W | FA2 | FA1 | FA0 | FD3 | FD2 | FD1 | FD0 | 0 to 8 bits |

There is no response if the Format Control Command is received within a DSI short command structure.

#### 4.6.4.3 Format Control Registers

The seven 4-bit format control registers defined in the DSI 2.0 Bus Specification are shown in Table 4-18 below. The default values assigned to each register following reset are indicated.

**Table 4-18 Format Control Registers**

| Forma                            | nt Control Regis | ster |     |     |     | Dofoul | t Value |     |

|----------------------------------|------------------|------|-----|-----|-----|--------|---------|-----|

| Name                             |                  | Addr | ess |     |     | Delaul | t value |     |

| Name                             | Decimal          | FA2  | FA1 | FA0 | FD3 | FD2    | FD1     | FD0 |

| CRC Polynomial - Low Nibble      | 0                | 0    | 0   | 0   | 0   | 0      | 0       | 1   |

| CRC Polynomial - High Nibble     | 1                | 0    | 0   | 1   | 0   | 0      | 0       | 1   |

| Seed - Low Nibble                | 2                | 0    | 1   | 0   | 1   | 0      | 1       | 0   |

| Seed - High Nibble               | 3                | 0    | 1   | 1   | 0   | 0      | 0       | 0   |

| CRC Length (0 to 8)              | 4                | 1    | 0   | 0   | 0   | 1      | 0       | 0   |

| Short Word Data Length (8 to 15) | 5                | 1    | 0   | 1   | 1   | 0      | 0       | 0   |

| Reserved                         | 6                | 1    | 1   | 0   | 0   | 0      | 0       | 0   |

| Format Selection                 | 7                | 1    | 1   | 1   | 0   | 0      | 0       | 0   |

The following restrictions apply to format control register operations, in accordance with the DSI 2.0 Bus Specification:

- Attempting to write a value greater than eight to the CRC Length Register will cause the write to be ignored. The contents

of the register will remain unchanged.

- Attempting to write a value less than eight to the Short Word Data Length register will cause the write to be ignored. The

contents of the register will remain unchanged.

- The contents of the Format Selection register determine whether standard DSI values or the values contained in the remaining format control registers will be used. The values contained in the remaining format control registers become effective when this register is successfully written to '1111'. If the register is currently cleared, and one of the data bits FD3 FD0 is not received as a logic '1', the data in the register will remain all zeroes and the device will continue to use standard DSI format settings. If the register bits FD3 FD0 are all set and one of the bits is received as a logic '0' value, the data in the register will remain '1111' and the values contained in the remaining format control registers will continue to be used.

## 4.6.5 Read Register Data Command

The Read Register Data command must be transmitted as a DSI long command structure.

**Table 4-19 Read Register Data Command Structure**

|    |    |    | Da | ata |     |     |     |    | Add | ress       |    |    | Com | mand |    | CRC         |

|----|----|----|----|-----|-----|-----|-----|----|-----|------------|----|----|-----|------|----|-------------|

| D7 | D6 | D5 | D4 | D3  | D2  | D1  | D0  | А3 | A2  | <b>A</b> 1 | A0 | C3 | C2  | C1   | C0 | OHO         |

| 0  | 0  | 0  | 0  | RA3 | RA2 | RA1 | RA0 | A3 | A2  | A1         | A0 | 1  | 0   | 1    | 1  | 0 to 8 bits |

Table 4-20 Long Response Structure - Read Register Data Command

| Ī |     |     |     |     |     |     |     | Da  | ata |     |     |     |     |     |     |     | CRC         |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------------|

|   | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | OHO         |

|   | A3  | A2  | A1  | A0  | RA3 | RA2 | RA1 | RA0 | RD7 | RD6 | RD5 | RD4 | RD3 | RD2 | RD1 | RD0 | 0 to 8 bits |

There is no response if the Read Register Data Command is received within a DSI short command structure or if this command is sent to the DSI Global Device Address.

The sixteen registers shown in Table 3-1 may be accessed using this command. Register address combinations are listed below.

Table 4-21 Read Register Data Command Address Assignment

| RA3 | RA2 | RA1 | RA0 | Register |

|-----|-----|-----|-----|----------|

| 0   | 0   | 0   | 0   | SN0      |

| 0   | 0   | 0   | 1   | SN1      |

| 0   | 0   | 1   | 0   | SN2      |

| 0   | 0   | 1   | 1   | SN3      |

| 0   | 1   | 0   | 0   | TYPE     |

| 0   | 1   | 0   | 1   | Reserved |

| 0   | 1   | 1   | 0   | DEVCFG1  |

| 0   | 1   | 1   | 1   | DEVCFG2  |

| 1   | 0   | 0   | 0   | REG-8    |

| 1   | 0   | 0   | 1   | REG-9    |

| 1   | 0   | 1   | 0   | REG-A    |

| 1   | 0   | 1   | 1   | REG-B    |

| 1   | 1   | 0   | 0   | REG-C    |

| 1   | 1   | 0   | 1   | REG-D    |

| 1   | 1   | 1   | 0   | REG-E    |

| 1   | 1   | 1   | 1   | REG-F    |

#### 4.6.6 Disable Self-Test Stimulus Command

The Disable Self-Test Stimulus command may be transmitted as either a DSI long command structure or a DSI short command structure of any length. The data field in the command structure is ignored but is included in the CRC calculation.

Table 4-22 Disable Self-Test Stimulus Command Structure

|    | Add | ress       |            |    | Com | mand |   | CRC         |  |  |  |

|----|-----|------------|------------|----|-----|------|---|-------------|--|--|--|

| А3 | A2  | <b>A</b> 1 | <b>A</b> 0 | C3 | C2  | ChC  |   |             |  |  |  |

| A3 | A2  | A1         | A0         | 1  | 1   | 0    | 0 | 0 to 8 bits |  |  |  |

Table 4-23 Short Response Structure - Disable Self-Test Stimulus Command

| Response |     |     |     |     |     | Res | ponse |       |    |    |    |         |      |    |    |

|----------|-----|-----|-----|-----|-----|-----|-------|-------|----|----|----|---------|------|----|----|

| Length   | D14 | D13 | D12 | D11 | D10 | D9  | D8    | D7    | D6 | D5 | D4 | D3      | D2   | D1 | D0 |

| 8        |     |     |     |     |     |     |       |       |    |    |    |         |      |    |    |

| 9        |     |     |     |     |     |     |       |       |    |    |    |         |      |    |    |

| 10       |     |     |     |     |     |     |       |       |    |    |    |         |      |    |    |

| 11       |     |     |     |     |     | 0   |       | NV    | U  | ST | BS | AT1     | AT0  | S  | GF |

| 12       |     |     |     |     |     |     | 0     | ' ' ' |    | 01 |    | / / / / | /110 |    |    |

| 13       |     |     |     | 0   | 0   |     |       |       |    |    |    |         |      |    |    |

| 14       |     | 0 0 |     |     |     |     |       |       |    |    |    |         |      |    |    |

| 15       | 0   | 0   |     |     |     |     |       |       |    |    |    |         |      |    |    |

Table 4-24 Long Response Structure - Disable Self-Test Stimulus Command

|     |     |     |     |     |     |    | Da | ata |    |    |    |     |     |    |    | CRC         |

|-----|-----|-----|-----|-----|-----|----|----|-----|----|----|----|-----|-----|----|----|-------------|

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7  | D6 | D5 | D4 | D3  | D2  | D1 | D0 | OHO         |

| A3  | A2  | A1  | A0  | 0   | 0   | 0  | 0  | NV  | U  | ST | BS | AT1 | AT0 | S  | GF | 0 to 8 bits |

This command will execute if either the device specific address or DSI global device address (address \$0) is provided. A secondary function, self-test lockout, is activated when two consecutive Disable Self-Test Stimulus commands are received. Following self-test lockout, the internal self-test circuitry is disabled until a Clear command is received or the device undergoes power-on reset.

## 4.6.7 Enable Self-Test Stimulus Command

The Enable Self-Test Stimulus command may be transmitted as either a DSI long command structure or a DSI short command structure of any length. The data field in the command structure is ignored but is included in the CRC calculation. No action is taken by the device if this command is sent to the DSI Global Device Address.

Table 4-25 Enable Self-Test Stimulus Command Structure

|    | Add | ress       |    |    | Com        | mand |    | CRC         |

|----|-----|------------|----|----|------------|------|----|-------------|

| А3 | A2  | <b>A</b> 1 | A0 | C3 | C3 C2 C1 C |      | C0 | CHO         |

| A3 | A2  | A1         | A0 | 1  | 1          | 0    | 1  | 0 to 8 bits |

Table 4-26 Short Response Structure - Enable Self-Test Stimulus Command

| Response |     |     |     |     |     | Res | ponse |     |    |    |    |      |      |    |    |

|----------|-----|-----|-----|-----|-----|-----|-------|-----|----|----|----|------|------|----|----|

| Length   | D14 | D13 | D12 | D11 | D10 | D9  | D8    | D7  | D6 | D5 | D4 | D3   | D2   | D1 | D0 |