#### **Power Management IC**

#### **Features**

- High-efficiency multi-rail power supply chip optimized for the use in Advanced Driver Assistance Systems (ADAS)

- Step-down pre-regulator for wide input voltage range from 3.7 V to 35 V (40 V limited time) with low over-all power loss and fast transient performance. Suitable for operation with ceramic capacitors

- High-efficiency step-down post-regulator for second output voltage generation

- Step-up post-regulator with 5 V output voltage

- Voltage monitoring for two external voltage rails including enable signals

- Configurable window watchdog

- 16-bit SPI

- Green Product (RoHS compliant)

## **Potential applications**

- Automotive applications

- Advanced Driver Assistance Systems (ADAS)

- 77 GHz radar ECUs

- Camera ECUs

- Human Machine Interface (HMI) applications

#### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

## Description

The OPTIREG™ PMIC TLF30682QVS01 is a multi-output Power Management IC (PMIC) for automotive applications. The device consists of a battery connected buck regulator (Buck1) providing 3.3 V to external loads and to two low voltage post-regulators. The first post-regulator (Buck2) is a buck regulator providing an output voltage of 1.25 V. The second post-regulator (Boost1) provides an output voltage of 5.0 V and is intended to supply one or two CAN transceivers.

The TLF30682QVS01 supports 16-bit SPI communication to a microcontroller. The SPI commands support reading status information from the device and control of features such as PWM synchronization and control of the power regulators.

#### **Power Management IC**

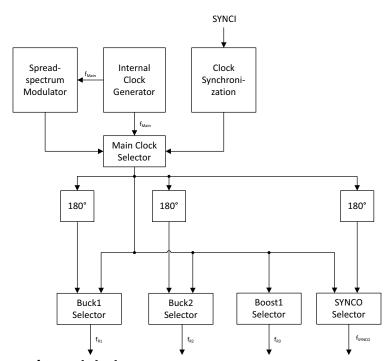

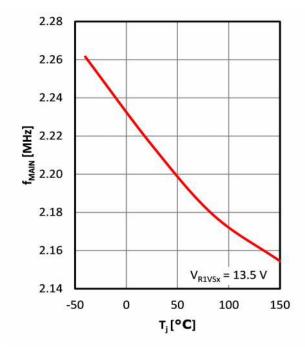

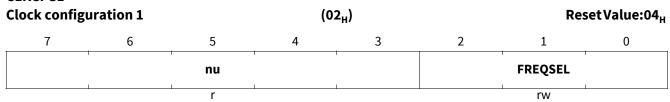

The device operates at a nominal switching frequency of 2.2 MHz. The switching frequency can be selected via SPI with an operating range from 1.8 MHz to 2.5 MHz in steps of 100 kHz. The switching regulators can be synchronized to an external clock signal. The TLF30682 can provide a synchronization signal for other DC/DC regulators in the system.

The TLF30682QVS01 provides two voltage monitoring channels with monitoring inputs and enable outputs. The monitoring channels can be used to control and monitor external voltage regulators. The external voltage regulator can be either LDOs or DC/DC switching regulators.

| Туре          | Package    | Marking  |  |

|---------------|------------|----------|--|

| TLF30682QVS01 | PG-VQFN-48 | TLF30682 |  |

|               |            | S01      |  |

## **Power Management IC**

## **Table of Contents**

|                | Features                                                      | . 1 |

|----------------|---------------------------------------------------------------|-----|

|                | Potential applications                                        | . 1 |

|                | Product validation                                            | . 1 |

|                | Description                                                   | . 1 |

|                | Table of Contents                                             | . 3 |

| 1              | Block diagram                                                 | . 5 |

| 2              | Pin configuration                                             | . 6 |

| 2.1            | Pin assignment                                                |     |

| 2.2            | Pin definitions and functions PG-VQFN-48                      | . 6 |

| 3              | General product characteristics                               | 11  |

| 3.1            | Absolute maximum ratings                                      | 11  |

| 3.2            | Functional range                                              |     |

| 3.3            | Thermal resistance                                            |     |

| 3.4            | Quiescent current consumption                                 |     |

| 3.4.1          | Typical performance characteristics                           |     |

| 4              | Power converters and power management                         |     |

| 4.1            | High voltage step-down regulator – Buck1                      |     |

| 4.1.1          | Functional description Buck1                                  |     |

| 4.1.2          | Electrical characteristics Buck1                              |     |

| 4.1.2.1        | Typical performance characteristics                           |     |

| 4.2            | Post-regulator step-down converter – Buck2                    |     |

| 4.2.1<br>4.2.2 | Functional description Buck2 Electrical characteristics Buck2 |     |

| 4.2.2.1        | Typical performance characteristics                           |     |

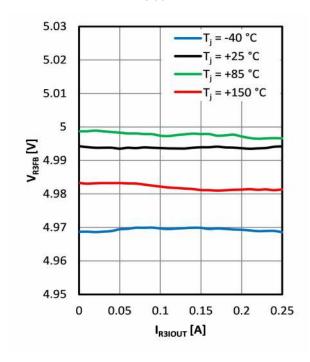

| 4.3            | Post-regulator step-up converter – Boost1                     |     |

| 4.3.1          | Functional description Boost1                                 |     |

| 4.3.2          | Electrical characteristics Boost1                             |     |

| 4.3.2.1        | Typical performance characteristics                           | 26  |

| 4.4            | Support of external voltage rails                             | 27  |

| 5              | Central functions                                             | 28  |

| 5.1            | Supply voltages                                               |     |

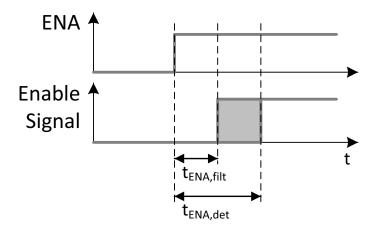

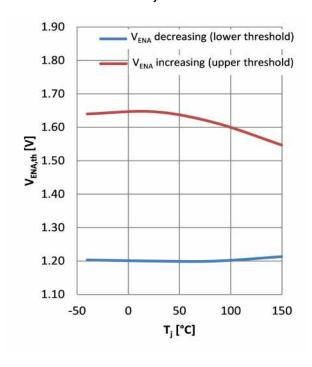

| 5.2            | Enable functionality                                          |     |

| 5.2.1          | ENA pin configurability                                       | 29  |

| 5.2.2          | Typical performance characteristics                           | 30  |

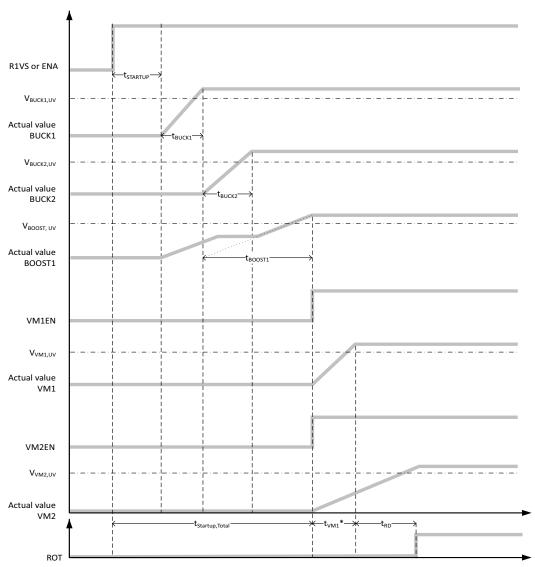

| 5.3            | Power sequencing and soft-start                               |     |

| 5.4            | Switching frequency generation and clock synchronization      |     |

| 5.4.1          | Typical performance characteristics                           |     |

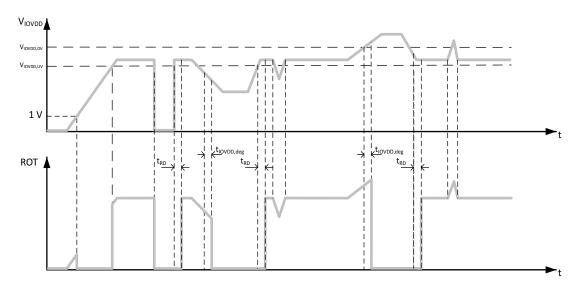

| 5.5            | IOVDD - Overvoltage and undervoltage detection                | 37  |

| 6              | Monitoring functions                                          | 38  |

| 6.1            | Voltage monitoring                                            |     |

| 6.1.1          | Monitoring of R1VSx – battery supply                          |     |

| 6.1.2          | Monitoring of output voltages                                 |     |

| 6.1.3          | Monitoring of external voltage rails                          | 38  |

## **Power Management IC**

| 6.1.4                                                                                               | Monitoring of internal supply voltages and bandgaps                                                                                                                                                                                                                                                                                                                                                                                             | 39                                     |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 6.1.5                                                                                               | Electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                      | 39                                     |

| 6.2                                                                                                 | Thermal protection                                                                                                                                                                                                                                                                                                                                                                                                                              | 41                                     |

| 7                                                                                                   | Microcontroller interface and supervisory functions                                                                                                                                                                                                                                                                                                                                                                                             | 43                                     |

| 7.1                                                                                                 | Microcontroller interface supply – IOVDD pin                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

| 7.1.1                                                                                               | Electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                      | 44                                     |

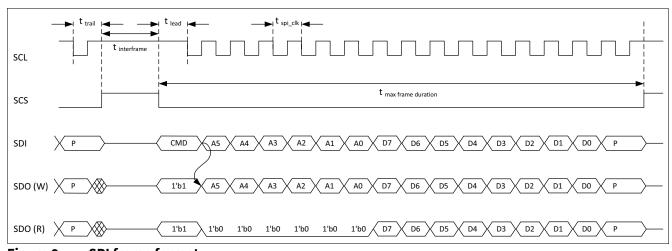

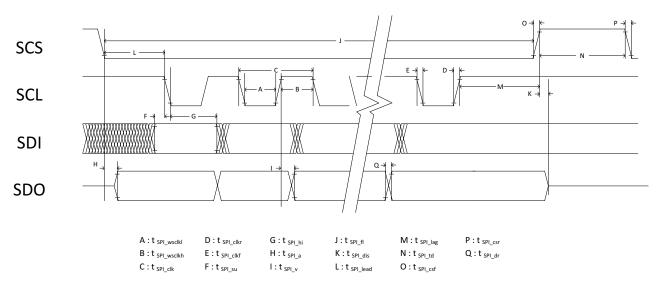

| 7.2                                                                                                 | Serial peripheral interface (SPI)                                                                                                                                                                                                                                                                                                                                                                                                               | 45                                     |

| 7.2.1                                                                                               | SPI introduction                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

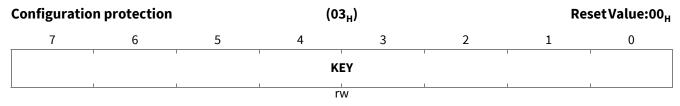

| 7.2.2                                                                                               | SPI write access to protected registers                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| 7.2.3                                                                                               | SPI write initiated state transition request and regulator configuration                                                                                                                                                                                                                                                                                                                                                                        |                                        |

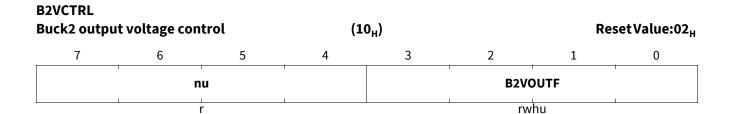

| 7.2.4                                                                                               | Configuration of Buck2 output voltage via SPI                                                                                                                                                                                                                                                                                                                                                                                                   |                                        |

| 7.2.5                                                                                               | Electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

| 7.3                                                                                                 | Reset signal ROT                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

| 7.3.1                                                                                               | Electrical characteristics – ROT pin                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |

| 7.4                                                                                                 | Interrupt signal INT                                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |

| 7.4.1                                                                                               | Electrical characteristics – INT pin                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |

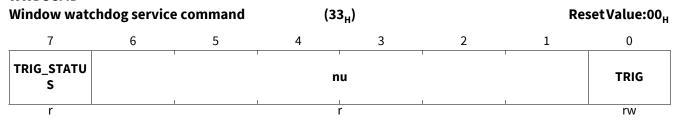

| 7.5                                                                                                 | Window watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

| 7.5.1<br>7.6                                                                                        | Electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

|                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

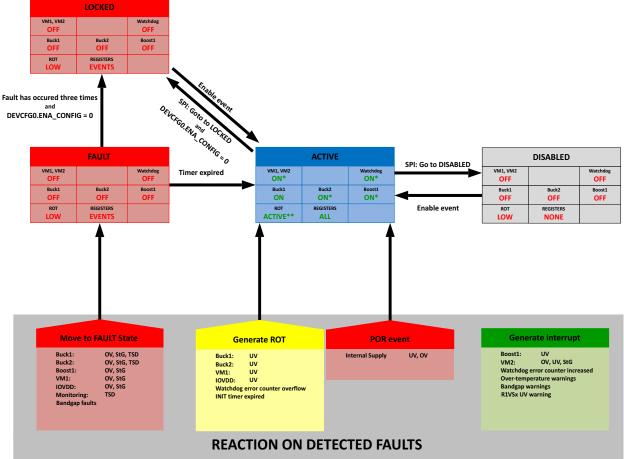

|                                                                                                     | State machine                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                        |

| 8                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

| 8.1                                                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57                                     |

| 8.1<br>8.2                                                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57<br>58                               |

| 8.1<br>8.2<br>8.3                                                                                   | Introduction Operation states State transitions and trigger signals                                                                                                                                                                                                                                                                                                                                                                             | 57<br>58<br>60                         |

| 8.1<br>8.2<br>8.3<br>8.4                                                                            | Introduction Operation states State transitions and trigger signals Electrical characteristics                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>60<br>62                   |

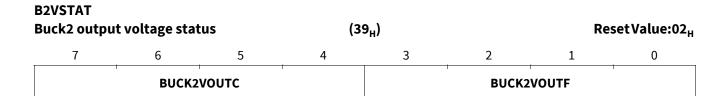

| 8.1<br>8.2<br>8.3<br>8.4                                                                            | Introduction Operation states State transitions and trigger signals Electrical characteristics  SPI registers                                                                                                                                                                                                                                                                                                                                   | 57 58 60 62                            |

| 8.1<br>8.2<br>8.3<br>8.4<br><b>9</b>                                                                | Introduction Operation states State transitions and trigger signals Electrical characteristics  SPI registers SPI register definition                                                                                                                                                                                                                                                                                                           | 57 58 60 62 63                         |

| 8.1<br>8.2<br>8.3<br>8.4<br><b>9</b><br>9.1                                                         | Introduction Operation states State transitions and trigger signals Electrical characteristics  SPI registers SPI register definition Device configuration registers (device start-up default configuration)                                                                                                                                                                                                                                    | 57 58 60 62 63 65                      |

| 8.1<br>8.2<br>8.3<br>8.4<br><b>9</b><br>9.1<br>9.1.1                                                | Introduction Operation states State transitions and trigger signals Electrical characteristics  SPI registers SPI register definition Device configuration registers (device start-up default configuration) Read-only registers for protected configuration registers                                                                                                                                                                          | 57 58 60 62 63 65 65                   |

| 8.1<br>8.2<br>8.3<br>8.4<br><b>9</b><br>9.1<br>9.1.1<br>9.1.2<br>9.1.3                              | Introduction Operation states State transitions and trigger signals Electrical characteristics  SPI registers SPI register definition Device configuration registers (device start-up default configuration) Read-only registers for protected configuration registers Special device configuration registers                                                                                                                                   | 57 58 60 62 63 65 65 69 71             |

| 8.1<br>8.2<br>8.3<br>8.4<br><b>9</b><br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4                            | Introduction Operation states State transitions and trigger signals Electrical characteristics  SPI registers  SPI register definition  Device configuration registers (device start-up default configuration) Read-only registers for protected configuration registers Special device configuration registers General registers                                                                                                               | 57 58 60 62 63 65 65 71 74             |

| 8.1<br>8.2<br>8.3<br>8.4<br><b>9</b><br>9.1<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4                     | Introduction Operation states State transitions and trigger signals Electrical characteristics  SPI registers SPI register definition Device configuration registers (device start-up default configuration) Read-only registers for protected configuration registers Special device configuration registers General registers Event status registers                                                                                          | 57 58 60 62 63 65 65 69 71 74          |

| 8.1<br>8.2<br>8.3<br>8.4<br><b>9</b><br>9.1<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.1.6   | Introduction Operation states State transitions and trigger signals Electrical characteristics  SPI registers SPI register definition Device configuration registers (device start-up default configuration) Read-only registers for protected configuration registers Special device configuration registers General registers Event status registers Device status information registers                                                      | 57 58 60 62 63 65 65 69 71 74 75 86    |

| 8.1<br>8.2<br>8.3<br>8.4<br><b>9</b><br>9.1<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4                     | Introduction Operation states State transitions and trigger signals Electrical characteristics  SPI registers SPI register definition Device configuration registers (device start-up default configuration) Read-only registers for protected configuration registers Special device configuration registers General registers Event status registers Device status information registers Device information registers                         | 57 58 60 62 63 65 65 69 71 74 75 86 91 |

| 8.1<br>8.2<br>8.3<br>8.4<br><b>9</b><br>9.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.1.6<br>9.1.7   | Introduction Operation states State transitions and trigger signals Electrical characteristics  SPI registers SPI register definition Device configuration registers (device start-up default configuration) Read-only registers for protected configuration registers Special device configuration registers General registers Event status registers Device status information registers Device information registers Application information | 57 58 60 62 63 65 65 69 74 75 86 91 93 |

| 8.1<br>8.2<br>8.3<br>8.4<br><b>9</b><br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.1.6<br>9.1.7 | Introduction Operation states State transitions and trigger signals Electrical characteristics  SPI registers SPI register definition Device configuration registers (device start-up default configuration) Read-only registers for protected configuration registers Special device configuration registers General registers Event status registers Device status information registers Device information registers                         | 57 58 60 62 63 65 65 69 74 75 86 91 91 |

# infineon

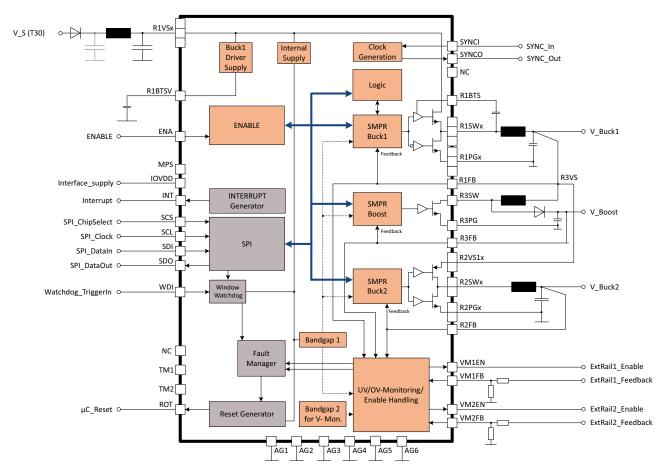

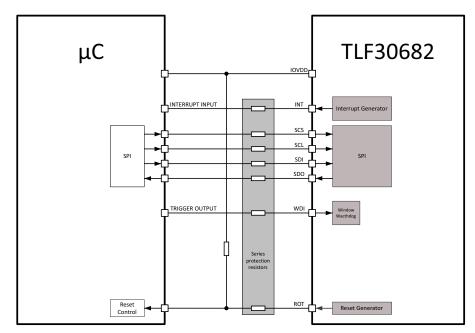

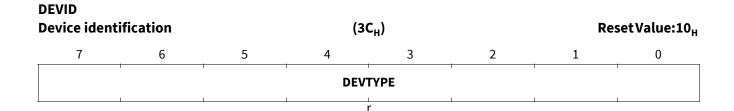

**Block diagram**

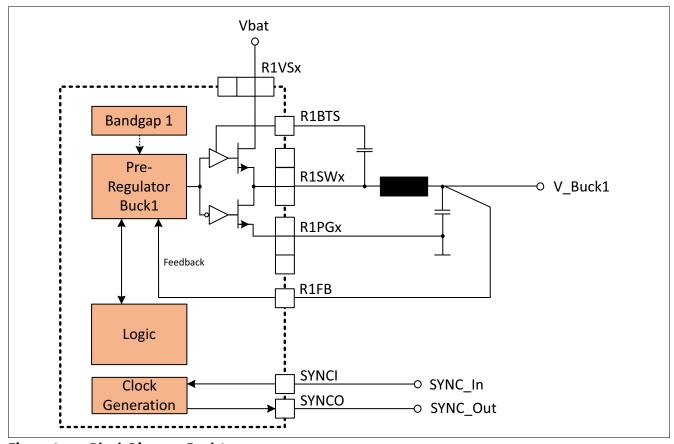

## 1 Block diagram

Figure 1 Block diagram

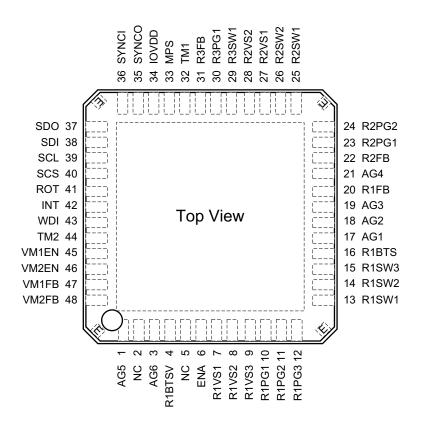

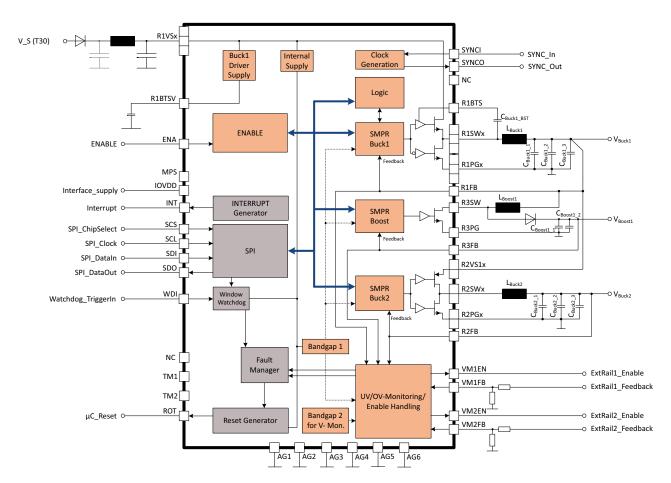

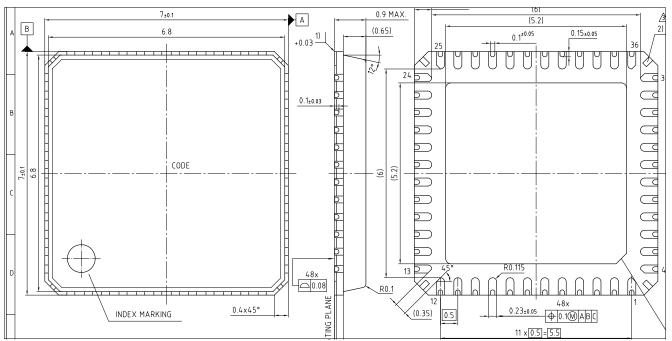

Pin configuration

#### **Pin configuration** 2

#### Pin assignment 2.1

Figure 2 Pin configuration

#### Pin definitions and functions PG-VQFN-48 2.2

| Pin | Symbol | Function                                                                                              |

|-----|--------|-------------------------------------------------------------------------------------------------------|

| 1   | AG5    | Analog ground, pin 5: Connect directly (low ohmic and low inductive) to ground.                       |

| 2   | NC     | Not connected: Leave the pin floating in the application.                                             |

| 3   | AG6    | Analog ground, pin 6: Connect directly (low ohmic and low inductive) to ground.                       |

| 4   | R1BTSV | Decoupling pin for internal supply voltage: Connect a decoupling capacitor between the pin and R1PGx. |

| 5   | NC     | Not connected: Leave the pin floating in the application.                                             |

| 6   | ENA    | Enable input: A valid enable condition at the pin will enable the device.                             |

## **Power Management IC**

| Pin | Symbol | Function                                                                                                                                                                                                                                                          |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | R1VS1  | High voltage regulator supply voltage, pin 1: Connect in parallel with R1VS2 and R1VS3 and then to the supply (battery) voltage via a reverse protection diode. Additionally connect a capacitor between the pin and ground. An EMC filter is recommended.        |

| 8   | R1VS2  | High voltage regulator supply voltage, pin 2:<br>Connect in parallel with R1VS1 and R1VS3 and then to the supply (battery) voltage via a reverse protection diode. Additionally connect a capacitor between the pin and ground. An EMC filter is recommended.     |

| 9   | R1VS3  | <b>High voltage regulator supply voltage, pin 3:</b> Connect in parallel with R1VS1 and R1VS2 and then to the supply (battery) voltage via a reverse protection diode. Additionally connect a capacitor between the pin and ground. An EMC filter is recommended. |

| 10  | R1PG1  | <b>High voltage regulator power ground, pin 1:</b> Connect in parallel with R1PG2 and R1PG3 and then to the Buck1 output capacitor ground terminal to ground.                                                                                                     |

| 11  | R1PG2  | <b>High voltage regulator power ground, pin 2:</b> Connect in parallel with R1PG1 and R1PG3 and then to the Buck1 output capacitor ground terminal to ground.                                                                                                     |

| 12  | R1PG3  | <b>High voltage regulator power ground, pin 3:</b> Connect in parallel with R1PG1 and R1PG2 and to the Buck1 output capacitor ground terminal to ground.                                                                                                          |

| 13  | R1SW1  | High voltage regulator power stage output, pin 1:<br>Connect in parallel with R1SW2 and R1SW3 and then to the pre-regulator (Buck1) output filter inductor.                                                                                                       |

| 14  | R1SW2  | <b>High voltage regulator power stage output, pin 2:</b> Connect in parallel with R1SW1 and R1SW3 and then to the pre-regulator output filter inductor.                                                                                                           |

| 15  | R1SW3  | High voltage regulator power stage output, pin 3:<br>Connect in parallel with R1SW1 and R1SW2 and then to the pre-regulator output filter inductor.                                                                                                               |

| 16  | R1BTS  | Bootstrap supply voltage: Connect via the bootstrap capacitor to the R1SWx pins.                                                                                                                                                                                  |

| 17  | AG1    | Analog ground, pin 1: Connect directly (low ohmic and low inductive) to ground.                                                                                                                                                                                   |

| 18  | AG2    | Analog ground, pin 2: Connect directly (low ohmic and low inductive) to ground.                                                                                                                                                                                   |

| 19  | AG3    | Analog ground, pin 3: Connect directly (low ohmic and low inductive) to ground.                                                                                                                                                                                   |

| 20  | R1FB   | High voltage regulator output voltage feedback pin: Connect to the Buck1 output capacitor.                                                                                                                                                                        |

| 21  | AG4    | Analog ground, pin 4: Connect directly (low ohmic and low inductive) to ground.                                                                                                                                                                                   |

| 22  | R2FB   | Post-regulator output voltage feedback pin: Connect to the Buck2 output capacitor.                                                                                                                                                                                |

## **Power Management IC**

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23  | R2PG1  | Pre-regulator power ground, pin 1:  Connect in parallel with R2PG2 and then to the Buck2 output capacitor ground terminal to ground.                                                                                                                                                                                                                    |

| 24  | R2PG2  | Pre-regulator power ground, pin 2: Connect in parallel with R2PG1 and then to the Buck2 output capacitor ground terminal to ground.                                                                                                                                                                                                                     |

| 25  | R2SW1  | <b>Post-regulator power stage output, pin 1:</b> Connect in parallel with R2SW2 and then to the Buck2 output filter inductor.                                                                                                                                                                                                                           |

| 26  | R2SW2  | Post-regulator power stage output, pin 2: Connect in parallel with R2SW1 and then to the Buck2 output filter inductor.                                                                                                                                                                                                                                  |

| 27  | R2VS1  | Post-regulator supply voltage, pin 1: Connect to the Buck1 output capacitor.                                                                                                                                                                                                                                                                            |

| 28  | R2VS2  | Post-regulator supply voltage, pin 2: Connect to the Buck1 output capacitor.                                                                                                                                                                                                                                                                            |

| 29  | R3SW1  | Regulator 3 power stage output, pin 1:  Connect to Boost1 inductor and external rectifying diode.                                                                                                                                                                                                                                                       |

| 30  | R3PG1  | Regulator 3 power ground, pin 1:  Connect to Boost1 output capacitor ground terminal to ground.                                                                                                                                                                                                                                                         |

| 31  | R3FB   | Regulator 3 output voltage feedback pin: Connect to Boost1 output capacitor.                                                                                                                                                                                                                                                                            |

| 32  | TM1    | Test mode 1 pin:  Not for customer use. Leave the pin floating in the application.                                                                                                                                                                                                                                                                      |

| 33  | MPS    | Microcontroller programming mode pin Connect to ground for normal operation in the application. Optionally the pin can be used for microcontroller programming purposes. For details please refer to the application information section.                                                                                                               |

| 34  | IOVDD  | I/O supply voltage: Connect to the I/O supply voltage of the microcontroller.                                                                                                                                                                                                                                                                           |

| 35  | SYNCO  | Synchronization output signal:  Connect to an optional external switch-mode post-regulator synchronization input.  The signal delivers the internal switching frequency either in phase or shifted by 180° (configurable via SPI). The switch-mode post-regulator synchronizes to the rising edge.  If the pin is not used, it should be left floating. |

| 36  | SYNCI  | Synchronization input signal: Connect to an optional external synchronization signal to synchronize the switching of the internal switch-mode regulators. The feature needs to be enabled via SPI. If the pin is not used, it should be left floating.                                                                                                  |

| 37  | SDO    | Serial peripheral interface, signal data output:  SPI signalling port, connect to SPI port "data input" of microcontroller to send status information during SPI communication.                                                                                                                                                                         |

| 38  | SDI    | Serial peripheral interface, signal data input:  SPI signalling port, connect to SPI port "data output" of microcontroller to receive commands during SPI communication.                                                                                                                                                                                |

## **Power Management IC**

| Pin         | Symbol | Function                                                                                                                                                                                                                                                                                                                      |

|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39          | SCL    | Serial peripheral interface, signal clock: SPI signalling port, connect to SPI port "clock" of microcontroller to clock the device for SPI communication.                                                                                                                                                                     |

| 40          | SCS    | Serial peripheral interface, signal chip select: SPI signalling port, connect to SPI port "chip select" of microcontroller to address the device for SPI communication.                                                                                                                                                       |

| 41          | ROT    | Reset output:  Open drain structure with internal pull up resistor. A "low" signal at this pin indicates a reset event for the microcontroller.  Connect to microcontroller reset input.                                                                                                                                      |

| 42          | INT    | Interrupt signal: Push-pull output. A "low" pulse at this pin indicates an interrupt, and the microcontroller reads the SPI status registers. Connect to a non-maskable interrupt port (NMI) of the microcontroller.                                                                                                          |

| 43          | WDI    | Watchdog input, trigger signal: Input for trigger signal. Connect the "trigger signal output" of the microcontroller to the pin. If the pin is not used it should be left floating (internal pull-down).                                                                                                                      |

| 44          | TM2    | Test mode 2 pin: Not for customer use. Connect the pin to GND in the application.                                                                                                                                                                                                                                             |

| 45          | VM1EN  | Enable signal for external voltage rails 1:  Connect to the enable pin of a optional external voltage regulator 1.  If the optional external regulator is not used, connect to ground.                                                                                                                                        |

| 46          | VM2EN  | Enable signal for external voltage rails 2:  Connect to the enable pin of a optional external voltage regulator 2.  If the optional external regulator is not used, connect to ground.                                                                                                                                        |

| 47          | VM1FB  | Input for optional external voltage monitoring rail 1:  Connect an external resistor divider to adjust the overvoltage threshold and the undervoltage threshold of the monitored external voltage generated by the optional external voltage regulator 1.  If the optional external regulator is not used, connect to ground. |

| 48          | VM2FB  | Input for optional external voltage monitoring rail 2:  Connect an external resistor divider to adjust the overvoltage threshold and the undervoltage threshold of the monitored external voltage generated by the optional external voltage regulator 2.  If the optional external regulator is not used, connect to ground. |

| Cooling Tab | GND    | Cooling tab: Internally connected to GND                                                                                                                                                                                                                                                                                      |

|             | EP1    | Edge pin no 1: Keep the area below the pin free of ground or other signals. Do not solder this pin to ground or any other signal. This pin must be kept free of soldering.                                                                                                                                                    |

|             | EP2    | Edge pin no 2: Keep the area below the pin free of ground or other signals. Do not solder this pin to ground or any other signal. This pin must be kept free of soldering.                                                                                                                                                    |

## **Power Management IC**

| Pin | Symbol | Function                                                                                                                                                                   |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | EP3    | Edge pin no 3:                                                                                                                                                             |

|     |        | Keep the area below the pin free of ground or other signals. Do not solder this pin to ground or any other signal. This pin must be kept free of soldering.                |

|     | EP4    | Edge pin no 4: Keep the area below the pin free of ground or other signals. Do not solder this pin to ground or any other signal. This pin must be kept free of soldering. |

#### **Power Management IC**

# infineon

**General product characteristics**

## **3** General product characteristics

## 3.1 Absolute maximum ratings

## Table 1 Absolute maximum ratings<sup>1)</sup>

$T_{\rm j}$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter | Symbol             |                          | Value | S                       | Unit | Note or<br>Test Condition | Number   |

|-----------|--------------------|--------------------------|-------|-------------------------|------|---------------------------|----------|

|           |                    | Min.                     | Тур.  | Max.                    |      |                           |          |

| Pin       |                    |                          |       |                         |      |                           |          |

| MPS       | $V_{MPS}$          | -0.3                     | -     | 6.0                     | V    | _                         | P_3.1.1  |

| IOVDD     | $V_{\text{IOVDD}}$ | -0.3                     | -     | 6.0                     | V    | -                         | P_3.1.2  |

| SCS       | $V_{SCS}$          | -0.3                     | -     | 6.0                     | V    | _                         | P_3.1.3  |

| SCL       | $V_{SCL}$          | -0.3                     | -     | 6.0                     | V    | -                         | P_3.1.4  |

| SDI       | $V_{SDI}$          | -0.3                     | -     | 6.0                     | V    | -                         | P_3.1.5  |

| SDO       | $V_{SDO}$          | -0.3                     | -     | 6.0                     | V    | _                         | P_3.1.6  |

| WDI       | $V_{ m WDI}$       | -0.3                     | -     | 6.0                     | V    | -                         | P_3.1.7  |

| INT       | $V_{INT}$          | -0.3                     | -     | 6.0                     | V    | -                         | P_3.1.10 |

| AG1       | $V_{AG1}$          | -0.3                     | _     | 0.3                     | V    | _                         | P_3.1.13 |

| AG2       | $V_{AG2}$          | -0.3                     | -     | 0.3                     | V    | -                         | P_3.1.14 |

| AG3       | $V_{AG3}$          | -0.3                     | -     | 0.3                     | V    | -                         | P_3.1.15 |

| AG4       | $V_{AG4}$          | -0.3                     | -     | 0.3                     | V    | -                         | P_3.1.16 |

| AG5       | $V_{AG5}$          | -0.3                     | -     | 0.3                     | V    | -                         | P_3.1.17 |

| AG6       | $V_{AG6}$          | -0.3                     | -     | 0.3                     | V    | -                         | P_3.1.18 |

| SYNCI     | $V_{SYNCI}$        | -0.3                     | -     | 6.0                     | V    | -                         | P_3.1.19 |

| SYNCO     | $V_{SYNCO}$        | -0.3                     | _     | 6.0                     | V    | _                         | P_3.1.20 |

| TM1       | $V_{TM1}$          | -0.3                     | _     | 6.0                     | ٧    | _                         | P_3.1.22 |

| ENA       | $V_{ENA}$          | -0.3                     | -     | 35                      | V    | 2)                        | P_3.1.23 |

| ENA       | I <sub>ENA</sub>   | -5.0                     | _     | _                       | mA   | _                         | P_3.1.24 |

| R1BTS     | $V_{R1BTS}$        | V <sub>R1SWx</sub> - 0.3 | _     | $V_{R1SWx} + 6.0$       | V    | -                         | P_3.1.25 |

| R1BTSV    | $V_{R1BTSV}$       | -0.3                     | _     | 6.0                     | V    | -                         | P_3.1.26 |

| R1VS1     | $V_{R1VS1}$        | -0.3                     | -     | 35                      | ٧    | 2)                        | P_3.1.27 |

| R1VS2     | $V_{R1VS2}$        | -0.3                     | _     | 35                      | ٧    | 2)                        | P_3.1.28 |

| R1VS3     | $V_{R1VS3}$        | -0.3                     | -     | 35                      | V    | 2)                        | P_3.1.29 |

| R1SW1     | $V_{R1SW1}$        | -0.3                     | _     | V <sub>R1VSx</sub> +2.0 | V    | _                         | P_3.1.30 |

| R1SW2     | $V_{R1SW2}$        | -0.3                     | _     | V <sub>R1VSx</sub> +2.0 | V    | -                         | P_3.1.31 |

| R1SW3     | $V_{R1SW3}$        | -0.3                     | _     | V <sub>R1VSx</sub> +2.0 | V    | _                         | P_3.1.32 |

| R1PG1     | $V_{R1PG1}$        | -0.3                     | _     | 0.3                     | V    | _                         | P_3.1.33 |

| R1PG2     | $V_{R1PG2}$        | -0.3                     | -     | 0.3                     | ٧    | _                         | P_3.1.34 |

#### **Power Management IC**

#### **General product characteristics**

#### **Table 1** Absolute maximum ratings<sup>1)</sup> (cont'd)

$T_{\rm j}$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                | Symbol                  | Values |      |      | Unit | Note or           | Number   |

|------------------------------------------|-------------------------|--------|------|------|------|-------------------|----------|

|                                          |                         | Min.   | Тур. | Max. |      | Test Condition    |          |

| R1PG3                                    | $V_{R1PG3}$             | -0.3   | _    | 0.3  | V    | _                 | P_3.1.35 |

| R1FB                                     | $V_{R1FB}$              | -0.3   | _    | 7.0  | V    | -                 | P_3.1.36 |

| R2VS1                                    | V <sub>R2VS1</sub>      | -0.3   | _    | 7.0  | V    | _                 | P_3.1.37 |

| R2VS2                                    | $V_{R2VS2}$             | -0.3   | _    | 7.0  | V    | _                 | P_3.1.38 |

| R2SW1                                    | V <sub>R2SW1</sub>      | -0.3   | _    | 7.0  | V    | -                 | P_3.1.39 |

| R2SW2                                    | $V_{R2SW2}$             | -0.3   | _    | 7.0  | V    | -                 | P_3.1.40 |

| R2PG1                                    | $V_{R2PG1}$             | -0.3   | _    | 0.3  | V    | _                 | P_3.1.41 |

| R2PG2                                    | $V_{R2PG2}$             | -0.3   | _    | 0.3  | V    | -                 | P_3.1.42 |

| R2FB                                     | $V_{R2FB}$              | -0.3   | _    | 7.0  | V    | _                 | P_3.1.43 |

| R3SW1                                    | $V_{\rm R3SW1}$         | -0.3   | _    | 7.0  | V    | _                 | P_3.1.44 |

| R3PG1                                    | $V_{R3PG1}$             | -0.3   | _    | 0.3  | V    | -                 | P_3.1.45 |

| R3FB                                     | $V_{R3FB}$              | -0.3   | _    | 7.0  | V    | -                 | P_3.1.46 |

| VM1FB                                    | $V_{\text{VM1FB}}$      | -0.3   | _    | 6.0  | V    | -                 | P_3.1.47 |

| VM1EN                                    | $V_{\text{VM1EN}}$      | -0.3   | _    | 6.0  | V    | -                 | P_3.1.48 |

| VM2FB                                    | $V_{\rm VM2FB}$         | -0.3   | _    | 6.0  | V    | -                 | P_3.1.49 |

| VM2EN                                    | $V_{\rm VM2EN}$         | -0.3   | _    | 6.0  | V    | -                 | P_3.1.50 |

| ROT                                      | $V_{ROT}$               | -0.3   | _    | 6.0  | V    | -                 | P_3.1.51 |

| TM2                                      | $V_{\text{TM2}}$        | -0.3   | _    | 6.0  | V    | -                 | P_3.1.52 |

| Temperatures                             |                         |        |      |      |      |                   |          |

| Junction temperature                     | $T_{\rm j}$             | -40    | _    | 150  | °C   | -                 | P_3.1.53 |

| Storage temperature                      | $T_{\rm stg}$           | -55    | _    | 150  | °C   | -                 | P_4.1.9  |

| ESD susceptibility                       |                         |        |      |      |      |                   |          |

| ESD susceptibility all pins              | V <sub>ESD,HBM</sub>    | -2     | _    | 2    | kV   | HBM <sup>3)</sup> | P_4.1.10 |

| ESD susceptibility all pins              | $V_{\rm ESD,CDM}$       | -500   | _    | 500  | V    | CDM <sup>4)</sup> | P_4.1.12 |

| ESD susceptibility of corner pins to GND | V <sub>ESD,Corner</sub> | -750   | -    | 750  | V    | CDM <sup>4)</sup> | P_4.1.13 |

- 1) Not subject to production test, specified by design.

- 2) Maximum rating is extended to 40 V for an overall time of 7 minutes during the lifetime of the product (load dump requirement)

- 3) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS001 (1.5k  $\Omega$ , 100 pF)

- 4) ESD susceptibility, Charged Device Model "CDM" according JEDEC JESD22-C101

#### **Notes**

1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Power Management IC**

#### **General product characteristics**

2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

### 3.2 Functional range

Note:

Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

Table 2 Functional Range

| Parameter                                  | Symbol             | Values |      |      | Unit | Note or        | Number  |

|--------------------------------------------|--------------------|--------|------|------|------|----------------|---------|

|                                            |                    | Min.   | Тур. | Max. |      | Test Condition |         |

| Supply Voltage Range for Normal Operation  | V <sub>R1VSx</sub> | 5.0    | -    | 35   | V    | 1)             | P_3.2.1 |

| Supply Voltage Range for Reduced Operation | V <sub>R1VSx</sub> | 3.7    | -    | 5.0  | V    | 1)2)           | P_4.2.5 |

| Junction Temperature                       | T <sub>j</sub>     | -40    | _    | 150  | °C   | _              | P_4.2.9 |

<sup>1)</sup> When first powered up, a proper startup of the device can only be assured by applying minimum 6 V at pins R1VSx for at least 2 ms. The device may start at even lower voltages.

<sup>2)</sup> The current capability of Buck1 is reduced to limit the current stress in the device.

## **Power Management IC**

#### **General product characteristics**

#### 3.3 Thermal resistance

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to **www.jedec.org**.

Table 3 Thermal resistance<sup>1)</sup>

| Parameter                                   | Symbol             | Values |      |      | Unit | Note or                                                | Number  |

|---------------------------------------------|--------------------|--------|------|------|------|--------------------------------------------------------|---------|

|                                             |                    | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                  |         |

| Junction to case                            | $R_{\rm thJC}$     | _      | -    | 12.2 | K/W  | -                                                      | P_4.3.1 |

| Junction to soldering point (pin)           | R <sub>thJSP</sub> | 20.1   | -    | 22.1 | K/W  | JEDEC 2s2p,<br>measured to pin 1, 3,<br>17, 18, 19, 21 | P_3.3.1 |

| Junction to soldering point (pin)           | R <sub>thJSP</sub> | 34.9   | -    | 37.6 | K/W  | JEDEC 1s0p,<br>measured to pin 1, 3,<br>17, 18, 19, 21 | P_3.3.2 |

| Junction to soldering point (soldering pad) | R <sub>thJSP</sub> | 11.0   | -    | 14.7 | K/W  | JEDEC 2s2p                                             | P_3.3.3 |

| Junction to soldering point (soldering pad) | R <sub>thJSP</sub> | 13.1   | -    | 18.0 | K/W  | JEDEC 1s0p                                             | P_4.3.2 |

| Junction to ambient                         | R <sub>thJA</sub>  | _      | 37   | -    | K/W  | 2)                                                     | P_4.3.3 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Specified  $R_{thJA}$  value is according to JEDEC JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The product (Chip and Package) was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with two inner copper layers (2 × 70  $\mu$ m Cu, 2 × 35  $\mu$ m Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

### **Power Management IC**

#### **General product characteristics**

## 3.4 Quiescent current consumption

## Table 4 Quiescent current consumption

$T_{\rm j}$  = -40°C to 150°C,  $V_{\rm R1VSx}$  = 9 V to 25 V (unless otherwise specified)

| Parameter      | Symbol               |      | Value | S    | Unit | Note or                                                                                                      | Number  |

|----------------|----------------------|------|-------|------|------|--------------------------------------------------------------------------------------------------------------|---------|

|                |                      | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                                                                        |         |

| ACTIVE state   | $I_{ m q,OP}$        | _    | -     | 20   | mA   | $T_j \le 85^{\circ}\text{C}$<br>9 V $\le V_{\text{R1VSx}} \le 25 \text{ V}$<br>No load, Watchdog<br>disabled | P_3.4.1 |

| DISABLED state | $I_{\rm q,DIS}$      | -    | 13    | 17.5 | μΑ   | $T_j \le 85^{\circ}\text{C}$<br>9 V $\le V_{\text{R1VSx}} \le 25 \text{ V}$                                  | P_3.4.2 |

| DISABLED state | $I_{\mathrm{q,DIS}}$ | -    | 11    | 13.5 | μΑ   | $T_{\rm j} = 25^{\circ}{\rm C}$<br>$V_{\rm R1VSx} = 13.5 {\rm V}$                                            | P_3.4.3 |

| FAULT state    | $I_{\mathrm{q,FLT}}$ | -    | 1     | 2    | mA   | $T_j \le 85^{\circ}\text{C}$<br>9 V $\le V_{\text{R1VSx}} \le 25 \text{ V}$                                  | P_3.4.4 |

| LOCKED state   | I <sub>q,LCK</sub>   | -    | 35    | 50   | μΑ   | $T_j \le 85^{\circ}\text{C}$<br>9 V $\le V_{\text{R1VSx}} \le 25 \text{ V}$                                  | P_3.4.5 |

**General product characteristics**

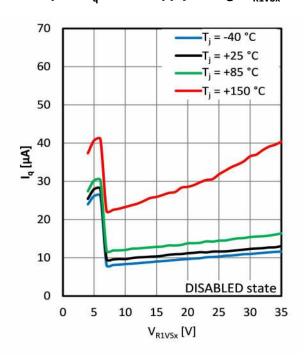

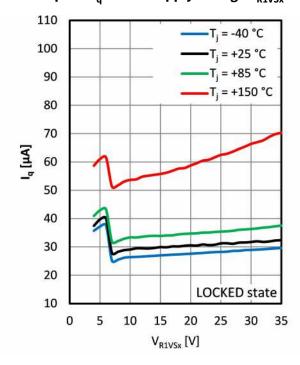

## 3.4.1 Typical performance characteristics

## DISABLED state - Quiescent current consumption $I_q$ versus supply voltage $V_{R1VSx}$

## LOCKED state - Quiescent current consumption $I_q$ versus supply voltage $V_{R1VSx}$

Power converters and power management

### 4 Power converters and power management

#### 4.1 High voltage step-down regulator - Buck1

#### 4.1.1 Functional description Buck1

The high-voltage step-down regulator (Buck1) converts the battery voltage (R1VSx) to the Buck1 voltage.

A synchronous current-mode-controlled buck converter with internal power switches is integrated for this purpose. The output rail VBuck1 can be used as direct supply rail as well as pre-regulated rail for post-regulators.

The N-/N-MOS power stage is driven by an integrated driver circuit supplied by an external boot-strap capacitor. The integrated dead-time optimization prevents cross-conduction, minimizes dead-time and increases system efficiency. The output voltage is set with an internal voltage divider. Internal compensation allows for fast loop performance across a wide range of output capacitance. External tuning of the loop is not required. The design supports both ceramic and electrolytic capacitors. For detailed information on the selection of the external power stage components, namely the inductor and input/output filter capacitors, please refer to **Chapter 10**.

The converter offers various configuration options. It offers a selectable switching frequency, which can be configured via the SPI. Synchronization of the switching frequency with the other integrated converters as well as an external synchronization signal is included. Various protection features, such as overcurrent and overtemperature detection, prevent damage to the converter due to fault conditions.

Figure 3 Block Diagram Buck1

#### **Power Management IC**

#### Power converters and power management

#### **Modulation concept**

The converter uses several modulation schemes depending on the operation mode. A PWM scheme is used for most of the operating area. It supports synchronization to internal and external clock sources. For light-load and high-line operation, pulse-skipping operation is used. This allows for an improved system efficiency and ensures a minimum turn-on time to ensure correct operation of the switches.

The transition between PWM and pulse-skipping is automatically handled by the converter and does not require any configuration. The current and voltage thresholds for this transition are dependent on the selected power stage components.

#### **Loop compensation**

The converter uses a cascaded current-mode, voltage-mode control scheme. The inductor current is controlled by an inner current-loop, while the output voltage is regulated by the external voltage compensation loop. The compensation loop can operate with a range of power stages. For detailed information on the selection of the external components, please refer to **Chapter 10**. The dynamic performance of the system is a function of the power stage components and the internal compensation loop. Follow the design considerations in **Chapter 10** for optimum performance.

#### **Cycle-by-cycle current limitation**

The device features cycle-by-cycle current limitation to protect the switches and external components in case of a fault condition. If a defined current threshold is reached, then the peak current monitoring turns off the high-side switch. The device also monitors the current in the low side switch. If the current in the low side switch exceeds the overcurrent threshold at the end of the switching period, then the high side switch is not turned on in the following switching period. This allows the device to work as a constant current source.

If the current in the inductor exceeds the overcurrent protection threshold for a defined time,  $T_{\text{R1OCP}}$ , then an overcurrent time-out event is signalized with an interrupt (**OCSF1.BUCK10CW**). It is up to the user to decide, how to react in this situation, for example by shutting down the converter.

#### **Overtemperature protection**

The converter includes an overtemperature warning and shutdown function to protect the device against damage. If the junction temperature exceeds the overtemperature warning threshold, an overtemperature warning flag is set (OTSF1.BUCK10TW) and an interrupt is generated. If the junction temperature continues to rise and exceeds the overtemperature shutdown threshold, then the converter shuts down and generates a thermal shut-down (TSD) event. The OTSF0.BUCK10T status flag is set and can be read by the microcontroller after re-entering ACTIVE state.

The current status of the overtemperature warning can be accessed at **OTSTATO.BUCK1OTW**, while **OTSF1.BUCK1OTW** contains the latched information.

#### **Soft-start**

The integrated soft-start feature limits the in-rush current and allows for smooth start-up of the converter. Power-sequencing together with the other output rails is supported. Please refer to **Chapter 5.3** for more information.

#### **Power Management IC**

Power converters and power management

#### **Electrical characteristics Buck1** 4.1.2

#### **Electrical characteristics Buck1** Table 5

$T_{\rm i}$  = -40°C to 150°C,  $V_{\rm R1VSx}$  = 3.7 V to 35 V, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                  | Symbol                    |      | Value | s    | Unit | Note or                                                                                                                 | Number     |

|--------------------------------------------|---------------------------|------|-------|------|------|-------------------------------------------------------------------------------------------------------------------------|------------|

|                                            |                           | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                                                                                   |            |

| Input voltage - TLF30682<br>S01            | V <sub>R1VSx</sub>        | 3.7  | 12    | 35   | V    | V <sub>R1FB</sub> = 3.3 V                                                                                               | P_4.1.2.1  |

| Output voltage – TLF30682<br>S01           | $V_{R1FB}$                | _    | 3.3   | -    | V    | -                                                                                                                       | P_4.1.2.2  |

| Output voltage tolerance                   | $V_{\rm R1FB,TOL}$        | -2   | _     | +2   | %    |                                                                                                                         | P_4.1.2.9  |

| Maximum output current                     | I <sub>R1IOUT</sub>       | 3.5  | 1     | _    | Α    | $5.0 \text{ V} \le V_{\text{R1VSx}} \le 35 \text{ V}$                                                                   | P_4.1.2.10 |

| Maximum output current –<br>derated        | I <sub>R1IOUT,DR</sub>    | 2.0  | -     | -    | Α    | $3.7 \text{ V} \le V_{\text{R1VSx}} < 5.0 \text{ V}$                                                                    | P_4.1.2.11 |

| High-side switch on-<br>resistance         | R <sub>DSOn,R1HS</sub>    | 45   | 77    | 145  | mΩ   | $5.0 \text{ V} \le V_{\text{R1VSx}} \le 35 \text{ V}$                                                                   | P_4.1.2.16 |

| High-side switch on-<br>resistance derated | R <sub>DSOn,R1HS,DR</sub> | _    | -     | 160  | mΩ   | $3.7 \text{ V} \le V_{\text{R1VSx}} < 5.0 \text{ V}$                                                                    | P_4.1.2.17 |

| Low-side switch on-<br>resistance          | R <sub>DSOn,R1LS</sub>    | 35   | 72    | 135  | mΩ   | $5.0V \le V_{R1VSx} \le 35 \text{ V}$                                                                                   | P_4.1.2.18 |

| Low-side switch on-<br>resistance derated  | R <sub>DSOn,R1LS,DR</sub> | _    | -     | 150  | mΩ   | $3.7V \le V_{R1VSx} < 5.0V$                                                                                             | P_4.1.2.19 |

|                                            |                           | -    | _     | _    |      | -                                                                                                                       | P_4.1.2.20 |

| Overcurrent protection threshold           | I <sub>R1OCP</sub>        | 4.1  | 4.5   | 6.0  | А    | -                                                                                                                       | P_4.1.2.21 |

| Overcurrent time out                       | $t_{R1OCP}$               | 95   | 100   | 115  | μs   | -                                                                                                                       | P_4.1.2.23 |

|                                            |                           | _    | _     | _    |      | -                                                                                                                       | P_4.1.2.24 |

| Minimum ON time                            |                           | 50   | 58    | 72   | ns   | Minimum ON time for internal HS control signal. The actual ON time on the R1SWx pins depends on the application design. | P_4.1.2.25 |

| Overtemperature warning threshold          | $T_{\rm j,R1OT,WRN}$      | 130  | 145   | 160  | °C   | <sup>1)</sup> T <sub>j</sub> increasing                                                                                 | P_4.1.2.26 |

| Overtemperature warning threshold          | $T_{\rm j,R1OT,WRN}$      | 120  | 135   | 150  | °C   | <sup>1)</sup> T <sub>j</sub> decreasing                                                                                 | P_4.1.2.27 |

| Overtemperature shutdown threshold         | $T_{\rm j,R1OT,FLT}$      | 175  | 190   | 205  | °C   | <sup>1)</sup> T <sub>j</sub> increasing                                                                                 | P_4.1.2.28 |

| Overtemperature shutdown threshold         | $T_{\rm j,R1OT,FLT}$      | 165  | 180   | 195  | °C   | <sup>1)</sup> T <sub>j</sub> decreasing                                                                                 | P_4.1.2.29 |

| Bootstrap capacitor                        | $C_{R1BST}$               | _    | 100   | _    | nF   | _                                                                                                                       | P_4.1.2.30 |

#### **Power Management IC**

#### Power converters and power management

#### **Table 5 Electrical characteristics Buck1** (cont'd)

$T_{\rm j}$  = -40°C to 150°C,  $V_{\rm R1VSx}$  = 3.7 V to 35 V, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                    | Symbol           |      | Value | Values |    | Note or               | Number     |

|------------------------------|------------------|------|-------|--------|----|-----------------------|------------|

|                              |                  | Min. | Тур.  | Max.   |    | <b>Test Condition</b> |            |

| External power stage comp    | onents           |      |       |        |    |                       |            |

| Effective inductance         | $L_{R1}$         | 2.64 | 3.3   | 4.0    | μΗ | 2)                    | P_4.1.2.33 |

| Effective output capacitance | $C_{R1}$         | 75   | 100   | 240    | μF | 2)3)                  | P_4.1.2.35 |

| ESR of output capacitance    | R <sub>R1C</sub> | 1    | 5     | 30     | mΩ | -                     | P_4.1.2.36 |

- 1) Not subject to production test, specified by design.

- 2) See Chapter 10 for additional information on the allowed L,C combinations.

- 3) Effective capacitance including de-rating over the temperature range, bias voltage and aging. Electrolytic and ceramic capacitors are supported.

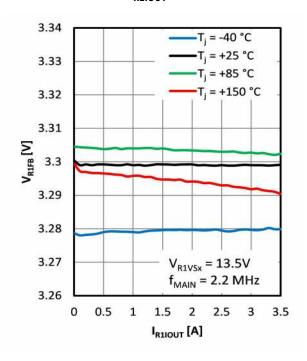

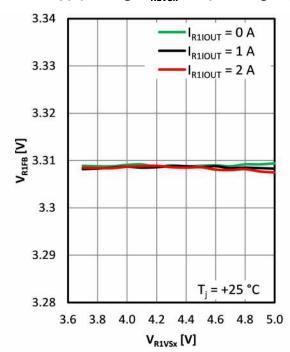

#### 4.1.2.1 Typical performance characteristics

## Buck1 output voltage V<sub>R1FB</sub> versus load current I<sub>R1IOUT</sub>

## Buck1 output voltage $V_{R1FB}$ versus supply voltage $V_{R1VSx}$ (drop-out region)

#### **Power Management IC**

Power converters and power management

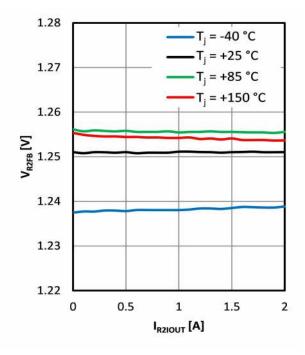

#### 4.2 Post-regulator step-down converter – Buck2

#### 4.2.1 Functional description Buck2

The low-voltage step-down regulator (Buck2) converts the output voltage of Buck1 into the VBuck2 voltage.

A synchronous current-mode-controlled buck converter with internal P-/N-MOS power stage is integrated for this purpose. The output voltage is set with an internal voltage divider. Internal compensation allows for fast loop performance across a wide range of output capacitance. External tuning of the loop is not required. The design supports both ceramic and electrolytic capacitors. For detailed information on the selection of the external power stage components, namely the inductor and input/output filter capacitors, please refer to Chapter 10.

Synchronization of the switching frequency with the other integrated converters as well as an external synchronization signal is included. Various protection features, for example overcurrent, overtemperature and overvoltage detection, prevent damage to the converter due to fault conditions.

#### **Loop compensation**

Due to the integrated loop compensation no external components are required for loop compensation.

The dynamic performance of the system is a function of the power stage components and the internal compensation loop. Follow the design considerations in **Chapter 10** for optimum performance.

#### Cycle-by-cycle current limitation

The device features cycle-by-cycle current limitation to protect the switches and external components in case of a fault condition. If a defined current threshold is reached, then the peak current monitoring turns off the high-side switch. The device also monitors the current in the low side switch. If the current in the low side switch exceeds the overcurrent threshold at the end of the switching period, then the high side switch is not turned on in the following switching period. This allows the device to work as a constant current source.

If this operation mode persists for a defined time, an overcurrent time-out event,  $t_{\rm R2OCP}$ , is signalized with an interrupt (OCSF1.BUCK2OCW). It is up to the user to decide how to react in this situation, by, for example shutting down the converter.

#### Overtemperature protection

The converter includes an overtemperature warning and shutdown function to protect the device against damage. If the junction temperature exceeds the overtemperature warning threshold, an overtemperature warning flag is set (OTSF1.BUCK2OTW) and an interrupt is generated. If the junction temperature continues to rise and exceeds the overtemperature shutdown threshold, then the converter shuts down and generates a thermal shut-down (TSD) event. The OTSF0.BUCK2OT status flag is set and can be read by the microcontroller after re-entering ACTIVE state.

The current status of the overtemperature warning can be accessed at **OTSTATO.BUCK2OTW**, while **OTSF1.BUCK2OTW** contains the latched information.

#### **Output voltage adjustment via SPI**