# Low Power, Unity Gain, Fully Differential Amplifier and ADC Driver

Data Sheet AD8476

#### **FEATURES**

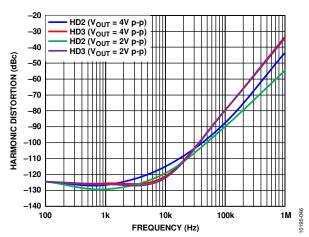

Very low power 330 μA supply current Extremely low harmonic distortion

- -126 HD2 at 10 kHz

- -128 HD3 at 10 kHz

Fully differential or single-ended inputs/outputs

Differential output designed to drive precision ADCs

Drives switched capacitor and Σ-Δ ADCs

Rail-to-rail outputs

VOCM pin adjusts output common mode Robust overvoltage up to 18 V beyond supplies High performance

Suitable for driving 16-bit converter up to 250 kSPS

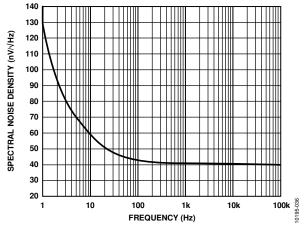

39 nV/√Hz output noise

1 ppm/°C gain drift maximum

200  $\mu V$  maximum output offset

10 V/μs slew rate

6 MHz bandwidth

Single supply: 3 V to 18 V Dual supplies: ±1.5 V to ±9 V

#### **APPLICATIONS**

**ADC** driver

Differential instrumentation amplifier building block Single-ended-to-differential converter

**Battery-powered instruments**

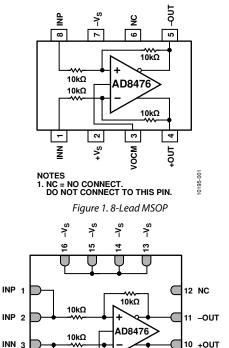

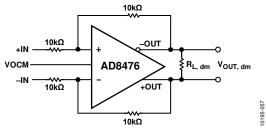

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. 16-Lead LFCSP

10kΩ

VOCM

#### **GENERAL DESCRIPTION**

The AD8476 is a very low power, fully differential precision amplifier with integrated gain resistors for unity gain. It is an ideal choice for driving low power, high performance ADCs as a single-ended-to-differential or differential-to-differential amplifier. It provides a precision gain of 1, common-mode level shifting, low temperature drift, and rail-to-rail outputs for maximum dynamic range.

The AD8476 also provides overvoltage protection from large industrial input voltages up to  $\pm 23$  V while operating on a dual 5 V supply. Power dissipation on a single 5 V supply is only 1.5 mW.

The AD8476 works well with SAR,  $\Sigma$ - $\Delta$ , and pipeline converters. The high current output stage of the part allows it to drive the

switched capacitor front-end circuits of many ADCs with minimal error.

Considering its low power consumption and high precision, the slew-enhanced AD8476 has excellent speed, settling to 16-bit precision for 250 kSPS acquisition times.

The AD8476 is available in space-saving 16-lead, 3 mm  $\times$  3 mm LFCSP and 8-lead MSOP packages. It is fully specified over the  $-40^{\circ}$ C to  $+125^{\circ}$ C temperature range.

# **TABLE OF CONTENTS**

| Features1                                     |

|-----------------------------------------------|

| Applications1                                 |

| Functional Block Diagram1                     |

| General Description1                          |

| Revision History                              |

| Specifications                                |

| Absolute Maximum Ratings5                     |

| Thermal Resistance                            |

| Maximum Power Dissipation5                    |

| ESD Caution5                                  |

| Pin Configuration and Function Descriptions6  |

| Typical Performance Characteristics           |

| Terminology                                   |

| Theory of Operation                           |

|                                               |

| REVISION HISTORY                              |

| REVISION HISTORY                              |

| 5/12—Rev. A to Rev. B                         |

|                                               |

| 5/12—Rev. A to Rev. B  Added LFCSP Throughout |

| 5/12—Rev. A to Rev. B  Added LFCSP Throughout |

| 5/12—Rev. A to Rev. B  Added LFCSP Throughout |

| 5/12—Rev. A to Rev. B  Added LFCSP Throughout |

10/11—Revision 0: Initial Version

| Overview                                | 17 |

|-----------------------------------------|----|

| Circuit Information                     | 17 |

| DC Precision                            | 17 |

| Input Voltage Range                     | 18 |

| Driving the AD8476                      | 18 |

| Power Supplies                          | 18 |

| Applications Information                | 19 |

| Typical Configuration                   | 19 |

| Single-Ended-to-Differential Conversion | 19 |

| Setting the Output Common-Mode Voltage  | 19 |

| Low Power ADC Driving                   | 20 |

| Outline Dimensions                      | 21 |

| Ordering Guide                          | 22 |

## **SPECIFICATIONS**

$V_S$  = +5 to ±5 V, VOCM = midsupply,  $V_{OUT}$  =  $V_{+OUT}$  –  $V_{-OUT}$ ,  $R_L$  = 2 k $\Omega$  differential, referred to output (RTO),  $T_A$  = 25°C, unless otherwise noted.

Table 1.

|                                  |                                                                          |                     | B Grade |                     | A Grade             |      |                           |        |

|----------------------------------|--------------------------------------------------------------------------|---------------------|---------|---------------------|---------------------|------|---------------------------|--------|

| Parameter                        | Test Conditions/Comments                                                 | Min                 | Тур     | Max                 | Min                 | Тур  | Max                       | Unit   |

| DYNAMIC PERFORMANCE              |                                                                          |                     |         |                     |                     |      |                           |        |

| -3 dB Small Signal Bandwidth     | V <sub>оит</sub> = 200 mV p-p                                            |                     | 6       |                     |                     | 6    |                           | MHz    |

| –3 dB Large Signal Bandwidth     | $V_{OUT} = 2 V p-p$                                                      |                     | 1       |                     |                     | 1    |                           | MHz    |

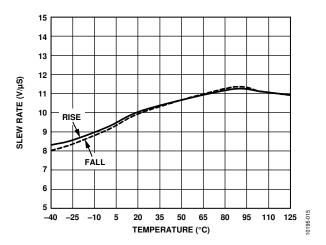

| Slew Rate                        | $V_{OUT} = 2 V step$                                                     |                     | 10      |                     |                     | 10   |                           | V/µs   |

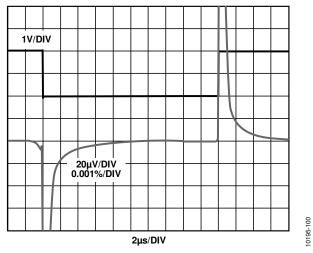

| Settling Time to 0.01%           | $V_{OUT} = 2 V step$                                                     |                     | 1.0     |                     |                     | 1.0  |                           | μs     |

| Settling Time to 0.001%          | V <sub>OUT</sub> = 2 V step                                              |                     | 1.6     |                     |                     | 1.6  |                           | μs     |

| NOISE/DISTORTION <sup>1</sup>    | -                                                                        |                     |         |                     |                     |      |                           |        |

| THD + N                          | f = 10 kHz, V <sub>OUT</sub> = 2 V p-p,<br>22 kHz filter                 |                     | -102    |                     |                     | -102 |                           | dB     |

| HD2                              | $f = 10 \text{ kHz, } V_{OUT} = 2 \text{ V p-p}$                         |                     | -126    |                     |                     | -126 |                           | dB     |

| HD3                              | $f = 10 \text{ kHz}, V_{OUT} = 2 \text{ V p-p}$                          |                     | -128    |                     |                     | -128 |                           | dB     |

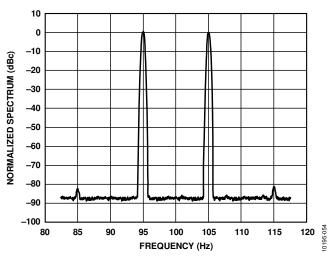

| IMD3                             | $f_1 = 95 \text{ kHz}, f_2 = 105 \text{ kHz}, V_{OUT} = 2 \text{ V p-p}$ |                     | -82     |                     |                     | -82  |                           | dBc    |

| Output Voltage Noise             | f = 0.1 Hz to 10 Hz                                                      |                     | 6       |                     |                     | 6    |                           | μV p-p |

| Spectral Noise Density           | f = 10 kHz                                                               |                     | 39      |                     |                     | 39   |                           | nV/√Hz |

| GAIN                             |                                                                          |                     | 1       |                     |                     | 1    |                           | V/V    |

| Gain Error                       | $R_L = \infty$                                                           |                     |         | 0.02                |                     |      | 0.04                      | %      |

| Gain Drift                       | $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                 |                     |         | 1                   |                     |      | 1                         | ppm/°C |

| Gain Nonlinearity                | $V_{OUT} = 4 V p-p$                                                      |                     | 5       |                     |                     | 5    |                           | ppm    |

| OFFSET AND CMRR                  |                                                                          |                     |         |                     |                     |      |                           |        |

| Differential Offset <sup>2</sup> |                                                                          |                     | 50      | 200                 |                     | 50   | 500                       | μV     |

| vs. Temperature                  | $-40^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$          |                     |         | 900                 |                     |      | 900                       | μV     |

| Average TC                       | $-40^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$          |                     | 1       | 4                   |                     | 1    | 4                         | μV/°C  |

| vs. Power Supply (PSRR)          | $V_S = \pm 2.5 \text{ V to } \pm 9 \text{ V}$                            | 90                  |         |                     | 90                  |      |                           | dB     |

| Common-Mode Offset <sup>2</sup>  |                                                                          |                     | 50      |                     |                     | 50   |                           | μV     |

| Common-Mode Rejection<br>Ratio   | $V_{IN,cm} = \pm 5 \text{ V}$                                            | 90                  |         |                     | 80                  |      |                           | dB     |

| INPUT CHARACTERISTICS            |                                                                          |                     |         |                     |                     |      |                           |        |

| Input Voltage Range <sup>3</sup> | Differential input                                                       | $-V_{s} + 0.05$     |         | $+V_{S}-0.05$       | $-V_s + 0.05$       |      | $+V_{S}-0.05$             | ٧      |

|                                  | Single-ended input                                                       | $2(-V_S + 0.05)$    |         | 2(+V - 0.05)        | $2(-V_S + 0.05)$    |      | 2(+V <sub>S</sub> - 0.05) | V      |

| Impedance <sup>4</sup>           | $V_{cm} = V_s/2$                                                         |                     |         |                     |                     |      |                           |        |

| Single-Ended Input               |                                                                          |                     | 13.3    |                     |                     | 13.3 |                           | kΩ     |

| Differential Input               |                                                                          |                     | 20      |                     |                     | 20   |                           | kΩ     |

| Common-Mode Input                |                                                                          |                     | 10      |                     |                     | 10   |                           | kΩ     |

| OUTPUT CHARACTERISTICS           |                                                                          |                     |         |                     |                     |      |                           |        |

| Output Swing                     | $V_{S} = +5 \text{ V}$                                                   | $-V_s + 0.125$      |         | $+V_{S}-0.14$       | $-V_s + 0.125$      |      | $+V_{S}-0.14$             |        |

|                                  | $V_s = \pm 5 \text{ V}$                                                  | $-V_s + 0.155$      |         | $+V_{s}-0.18$       | $-V_s + 0.155$      |      | $+V_{s}-0.18$             |        |

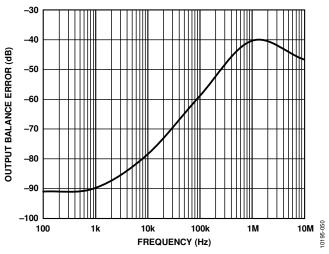

| Output Balance Error             | $\Delta V_{\text{OUT,cm}}/\Delta V_{\text{OUT,dm}}$                      | 90                  |         |                     | 80                  |      |                           | dB     |

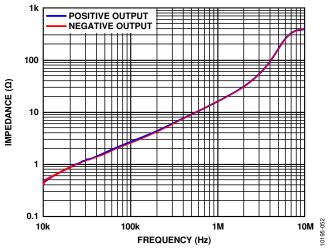

| Output Impedance                 |                                                                          |                     | 0.1     |                     |                     | 0.1  |                           | Ω      |

| Capacitive Load                  | Per output                                                               |                     | 20      |                     |                     | 20   |                           | pF     |

| Short-Circuit Current Limit      | · ·                                                                      |                     | 35      |                     |                     | 35   |                           | mA     |

| VOCM CHARACTERISTICS             |                                                                          |                     |         |                     |                     |      |                           |        |

| VOCM Input Voltage Range         |                                                                          | -V <sub>s</sub> + 1 |         | +V <sub>s</sub> - 1 | -V <sub>s</sub> + 1 |      | $+V_{s}-1$                | V      |

| VOCM Input Impedance             |                                                                          |                     | 500     | -                   | -                   | 500  | •                         | kΩ     |

| VOCM Gain Error                  |                                                                          |                     |         | 0.05                |                     |      | 0.05                      | %      |

|                                   |                                                          |     | B Grad | e    |     | A Grade | 2    |      |

|-----------------------------------|----------------------------------------------------------|-----|--------|------|-----|---------|------|------|

| Parameter                         | Test Conditions/Comments                                 | Min | Тур    | Max  | Min | Тур     | Max  | Unit |

| POWER SUPPLY                      |                                                          |     |        |      |     |         |      |      |

| Specified Supply Voltage          |                                                          |     | ±5     |      |     | ±5      |      | V    |

| Operating Supply Voltage<br>Range |                                                          | 3   |        | 18   | 3   |         | 18   | V    |

| Supply Current                    | $V_S = +5 \text{ V}, T_A = 25^{\circ}\text{C}$           |     | 300    | 330  |     | 300     | 330  | μΑ   |

|                                   | $V_S = \pm 5 \text{ V, } T_A = 25^{\circ}\text{C}$       |     | 330    | 380  |     | 330     | 380  | μΑ   |

| Over Temperature                  | $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$ |     | 400    | 500  |     | 400     | 500  | μΑ   |

| TEMPERATURE RANGE                 |                                                          |     |        |      |     |         |      |      |

| Specified Performance Range       |                                                          | -40 |        | +125 | -40 |         | +125 | °C   |

$<sup>^1</sup>$  Includes amplifier voltage and current noise, as well as noise of internal resistors.  $^2$  Includes input bias and offset current errors.  $^3$  The input voltage range is a function of the voltage supplies and ESD diodes.  $^4$  Internal resistors are trimmed to be ratio matched but have  $\pm 20\%$  absolute accuracy.

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                    | Rating                 |

|----------------------------------------------|------------------------|

| Supply Voltage                               | ±10 V                  |

| Maximum Voltage at Any Input Pin             | +V <sub>S</sub> + 18 V |

| Minimum Voltage at Any Input Pin             | -V <sub>S</sub> - 18 V |

| Storage Temperature Range                    | −65°C to +150°C        |

| Specified Temperature Range                  | -40°C to +125°C        |

| Package Glass Transition Temperature $(T_G)$ | 150°C                  |

| ESD (Human Body Model)                       | 2500 V                 |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

The  $\theta_{JA}$  values in Table 3 assume a 4-layer JEDEC standard board with zero airflow.

**Table 3. Thermal Resistance**

| Package Type               | θ <sub>JA</sub> | Unit |

|----------------------------|-----------------|------|

| 8-Lead MSOP                | 209.0           | °C/W |

| 16-Lead LFCSP, 3 mm × 3 mm | 78.5            | °C/W |

#### MAXIMUM POWER DISSIPATION

The maximum safe power dissipation for the AD8476 is limited by the associated rise in junction temperature (T<sub>1</sub>) on the die. At approximately 150°C, which is the glass transition temperature, the properties of the plastic change. Even temporarily exceeding this temperature limit may change the stresses that the package exerts on the die, permanently shifting the parametric performance of the amplifiers. Exceeding a temperature of 150°C for an extended period may result in a loss of functionality.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

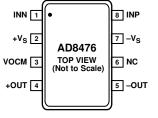

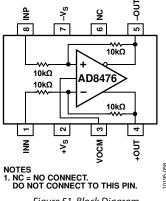

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

1. PINS LABELED NC CAN BE ALLOWED

TO FLOAT, BUT IT IS BETTER TO CONNECT

THESE PINS TO GROUND. AVOID ROUTING

HIGH SPEED SIGNALS THROUGH THESE

PINS BECAUSE NOISE COUPLING MAY RESULT.

Figure 3. 8-Lead MSOP Pin Configuration

**Table 4. 8-Lead MSOP Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                                          |

|---------|-----------------|------------------------------------------------------|

| 1       | INN             | Negative Input .                                     |

| 2       | +V <sub>S</sub> | Positive Supply.                                     |

| 3       | VOCM            | Output Common-Mode Adjust.                           |

| 4       | +OUT            | Noninverting Output.                                 |

| 5       | -OUT            | Inverting Output.                                    |

| 6       | NC              | This pin is not connected internally (see Figure 3). |

| 7       | −V <sub>S</sub> | Negative Supply.                                     |

| 8       | INP             | Positive Input.                                      |

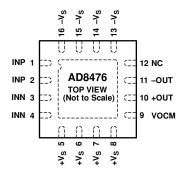

- NOTES

1. PINS LABELED NC CAN BE ALLOWED TO FLOAT,

BUT IT IS BETTER TO CONNECT THESE PINS TO

GROUND. AVOID ROUTING HIGH SPEED SIGNALS

THROUGH THESE PINS BECAUSE NOISE COUPLING

MAY RESULT.

2. SOLDER THE EXPOSED PADDLE ON THE BACK OF

THE PACKAGE TO A GROUND PLANE.

Figure 4. 16-Lead LFCSP Pin Configuration

**Table 5. 16-Lead LFCSP Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                                                             |

|---------|-----------------|-------------------------------------------------------------------------|

| 1       | INP             | Positive Input.                                                         |

| 2       | INP             | Positive Input.                                                         |

| 3       | INN             | Negative Input.                                                         |

| 4       | INN             | Negative Input .                                                        |

| 5       | +V <sub>S</sub> | Positive Supply.                                                        |

| 6       | +V <sub>S</sub> | Positive Supply.                                                        |

| 7       | +V <sub>S</sub> | Positive Supply.                                                        |

| 8       | +V <sub>S</sub> | Positive Supply.                                                        |

| 9       | VOCM            | Output Common-Mode Adjust.                                              |

| 10      | +OUT            | Noninverting Output.                                                    |

| 11      | -OUT            | Inverting Output.                                                       |

| 12      | NC              | This pin is not connected internally (see Figure 4).                    |

| 13      | -V <sub>S</sub> | Negative Supply.                                                        |

| 14      | -V <sub>S</sub> | Negative Supply.                                                        |

| 15      | -V <sub>S</sub> | Negative Supply.                                                        |

| 16      | -V <sub>S</sub> | Negative Supply.                                                        |

|         | EPAD            | Solder the exposed paddle on the back of the package to a ground plane. |

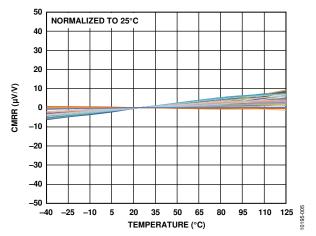

## TYPICAL PERFORMANCE CHARACTERISTICS

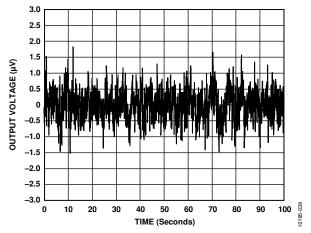

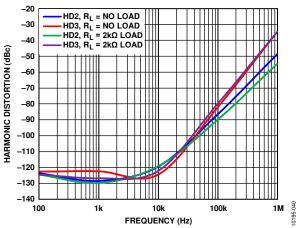

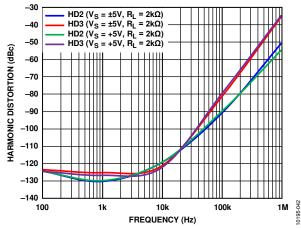

$V_S = +5$  V, G = 1, VOCM connected to 2.5 V,  $R_L = 2$  k $\Omega$  differentially,  $T_A = 25$ °C, referred to output (RTO), unless otherwise noted.

Figure 5. CMRR vs. Temperature

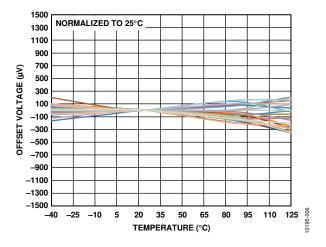

Figure 6. System Offset Temperature Drift

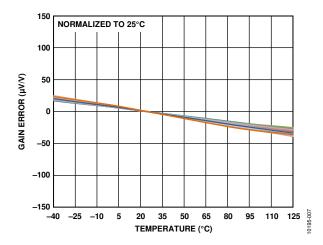

Figure 7. Gain Error vs. Temperature

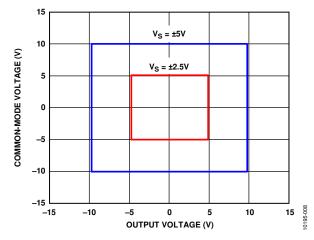

Figure 8. Input Common-Mode Voltage vs. Output Voltage,  $V_S = \pm 5 V$  and  $\pm 2.5 V$

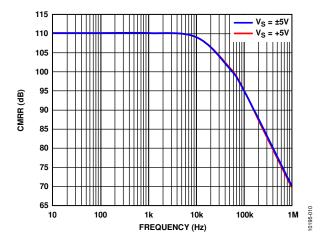

Figure 9. Common-Mode Rejection vs. Frequency

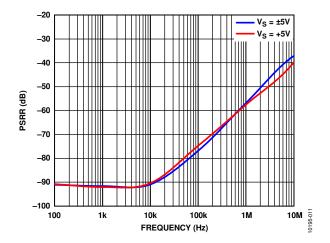

Figure 10. Power Supply Rejection vs. Frequency

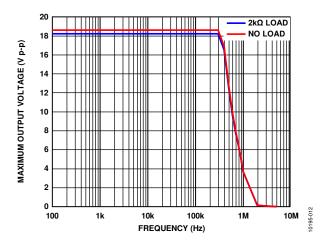

Figure 11. Maximum Output Voltage vs. Frequency

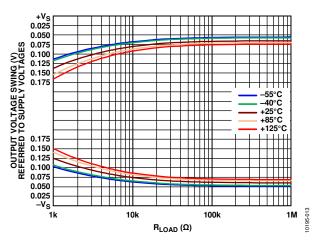

Figure 12. Output Voltage Swing vs.  $R_{LOAD}$  vs. Temperature,  $V_S = \pm 5 V$

Figure 13. Slew Rate vs. Temperature

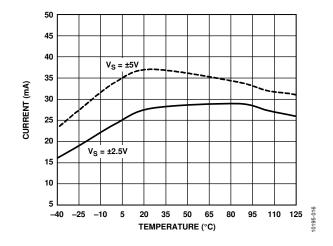

Figure 14. Short-Circuit Current vs. Temperature

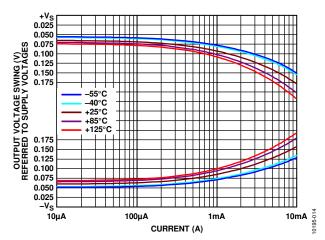

Figure 15. Output Voltage Swing vs. Load Current vs. Temperature,  $V_S = +5 \text{ V}$

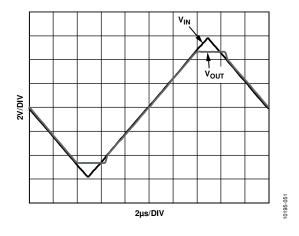

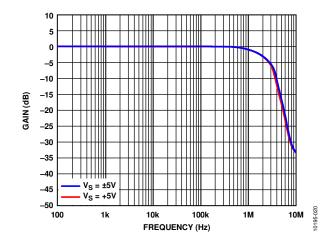

Figure 16. Overdrive Recovery,  $V_S = +5 V$

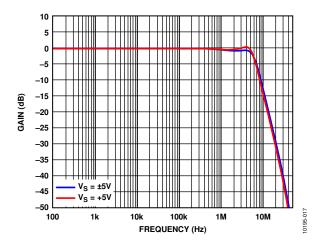

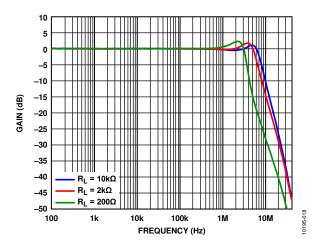

Figure 17. Small Signal Frequency Response for Various Supplies

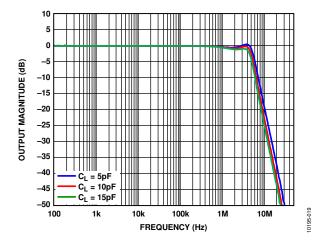

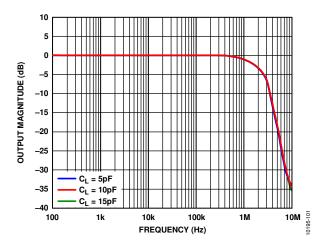

Figure 18. Small Signal Frequency Response for Various Loads

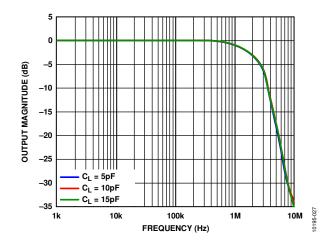

Figure 19. Small Signal Frequency Response for Various Capacitive Loads

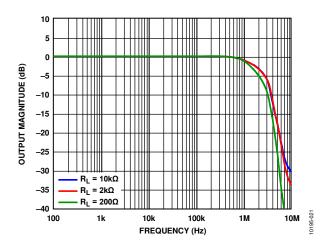

Figure 20. Large Signal Frequency Response for Various Supplies

Figure 21. Large Signal Frequency Response for Various Loads

Figure 22. Large Signal Frequency Response for Various Capacitive Loads

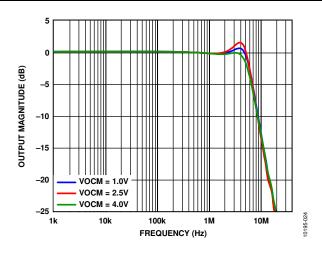

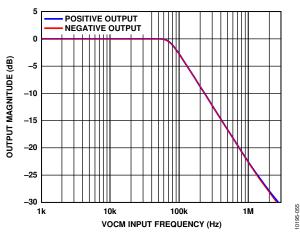

Figure 23. Small Signal Frequency Response for Various VOCM Levels

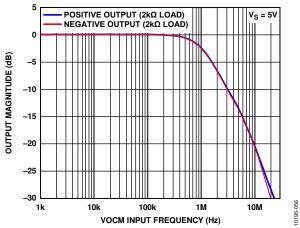

Figure 24. VOCM Small Signal Frequency Response

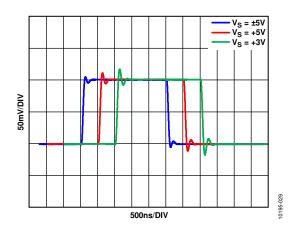

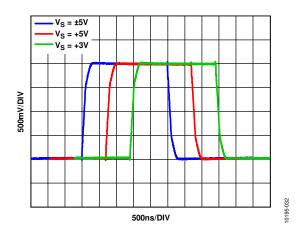

Figure 25. Small Signal Pulse Response for Various Supplies

Figure 26. Large Signal Frequency Response for Various VOCM Level

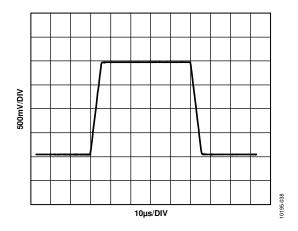

Figure 27. VOCM Large Signal Frequency Response

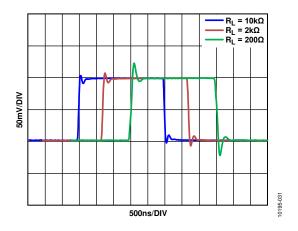

Figure 28. Large Signal Pulse Response for Various Supplies

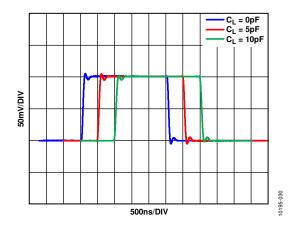

Figure 29. Small Signal Step Response for Various Resistive Loads,  $V_S = \pm 5 V$

Figure 30. Small Signal Step Response for Various Capacitive Loads,  $V_S = \pm 5 V$

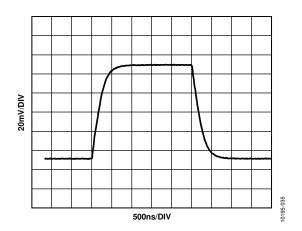

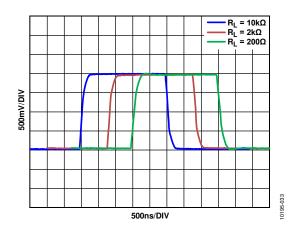

Figure 31. VOCM Small Signal Step Response

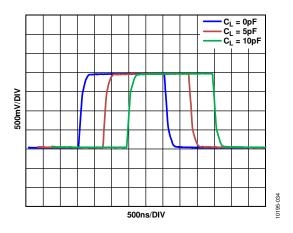

Figure 32. Large Signal Step Response for Various Resistive Loads,  $V_S = \pm 5 V$

Figure 33. Large Signal Step Response for Various Capacitive Loads,  $V_S = \pm 5 \text{ V}$

Figure 34. VOCM Large Signal Step Response

Figure 35. 0.1 Hz to 10 Hz Voltage Noise

Figure 36. Harmonic Distortion vs. Frequency at Various Loads

Figure 37. Harmonic Distortion vs. Frequency at Various Supplies

Figure 38. Voltage Noise Density vs. Frequency

Figure 39. Harmonic Distortion vs. Frequency at Various V<sub>OUT,dm</sub>

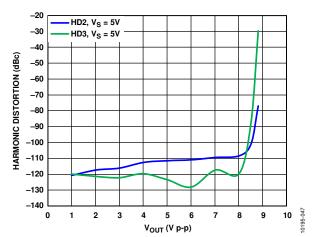

Figure 40. Harmonic Distortion vs.  $V_{OUT,dm}$ , f = 10 kHz

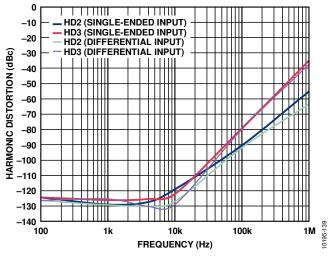

Figure 41. Harmonic Distortion vs. Input Drive

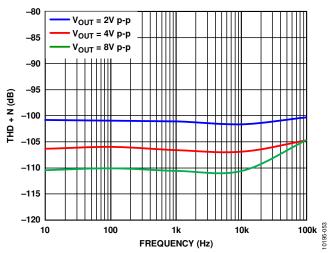

Figure 42. Total Harmonic Distortion + Noise vs. Frequency

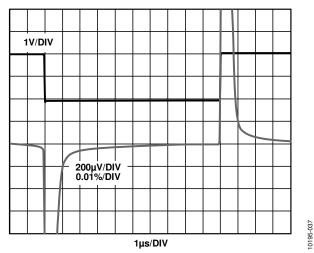

Figure 43. Settling Time to 0.01% of 2 V Step

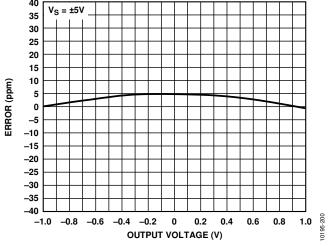

Figure 44. Gain Nonlinearity

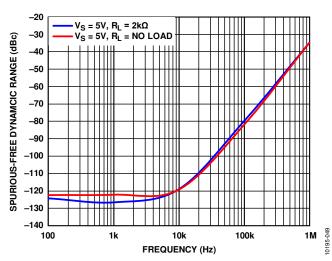

Figure 45. Spurious-Free Dynamic Range vs. Frequency at Various Loads

Figure 46. Settling Time to 0.001% of 2 V Step

Figure 47. Output Balance Error vs. Frequency

Figure 48. 100 kHz Intermodulation Distortion

Figure 49. Output Impedance vs. Frequency

## **TERMINOLOGY**

Figure 50. Signal and Circuit Definitions

#### **Differential Voltage**

Differential voltage refers to the difference between two node voltages. For example, the output differential voltage (or equivalently, output differential mode voltage) is defined as

$$V_{OUT, dm} = (V_{+OUT} - V_{-OUT})$$

where  $V_{+OUT}$  and  $V_{-OUT}$  refer to the voltages at the +OUT and -OUT terminals with respect to a common ground reference. Similarly, the differential input voltage is defined as

$$V_{IN, dm} = (V_{+IN} - V_{-IN})$$

#### Common-Mode Voltage

Common-mode voltage refers to the average of two node voltages with respect to the local ground reference. The output common-mode voltage is defined as

$$V_{OUT, cm} = (V_{+OUT} + V_{-OUT})/2$$

#### **Balance**

Output balance is a measure of how close the output differential signals are to being equal in amplitude and opposite in phase. Output balance is most easily determined by placing a well-matched resistor divider between the differential voltage nodes and comparing the magnitude of the signal at the divider midpoint with the magnitude of the differential signal. By this definition, output balance is the magnitude of the output common-mode voltage divided by the magnitude of the output differential mode voltage.

$$Output \; Balance \; Error = \left| \frac{\Delta V_{OUT,\; cm}}{\Delta V_{OUT,\; dm}} \right|$$

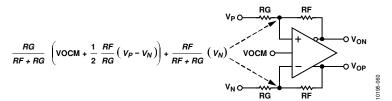

## THEORY OF OPERATION

#### **OVERVIEW**

The AD8476 is a fully differential amplifier, with integrated laser-trimmed resistors, that provides a precision gain of 1. The internal differential amplifier of the AD8476 differs from conventional operational amplifiers in that it has two outputs whose voltages are equal in magnitude, but move in opposite directions (180° out of phase).

The AD8476 is designed to greatly simplify single-ended-to-differential conversion, common-mode level shifting and precision driving of differential signals into low power, differential input ADCs. The VOCM input allows the user to set the output common-mode voltage to match with the input range of the ADC. Like an operational amplifier, the VOCM function relies on high open-loop gain and negative feedback to force the output nodes to the desired voltages.

Figure 51. Block Diagram

#### **CIRCUIT INFORMATION**

The AD8476 amplifier uses a voltage feedback topology; therefore, the amplifier exhibits a nominally constant gain bandwidth product. Like a voltage feedback operational amplifier, the AD8476 also has high input impedance at its internal input terminals (the summing nodes of the internal amplifier) and low output impedance.

The AD8476 employs two feedback loops, one each to control the differential and common-mode output voltages. The differential feedback loop, which is fixed with precision laser-trimmed on-chip resistors, controls the differential output voltage.

### **Output Common-Mode Voltage (VOCM)**

The internal common-mode feedback controls the common-mode output voltage. This architecture makes it easy for the user to set the output common-mode level to any arbitrary value independent of the input voltage. The output common-mode voltage is forced by the internal common-mode feedback loop to be equal to the voltage applied to the VOCM input. The VOCM pin can be left unconnected, and the output common-mode voltage self-biases to midsupply by the internal feedback control.

Due to the internal common-mode feedback loop and the fully differential topology of the amplifier, the AD8476 outputs are precisely balanced over a wide frequency range. This means that the amplifier's differential outputs are very close to the ideal of being identical in amplitude and exactly 180° out of phase.

#### **DC PRECISION**

The dc precision of the AD8476 is highly dependent on the accuracy of its integrated gain resistors. Using superposition to analyze the circuit shown in Figure 52, the following equation shows the relationship between the input and output voltages of the amplifier:

$$\begin{split} &V_{IN,cm} \Big( R_P - R_N \Big) + V_{IN,dm} \frac{1}{2} \Big( 2 R_P R_N + R_P + R_N \Big) \\ &= V_{OUT,cm} \Big( R_P - R_N \Big) + V_{OUT,dm} \frac{1}{2} \Big( 2 + R_P + R_N \Big) \end{split}$$

where:

$$\begin{split} R_P &= \frac{RFP}{RGP} \;,\; R_N = \frac{RFN}{RGN} \\ V_{IN,dm} &= V_P - V_N \\ V_{IN,cm} &= \frac{1}{2} (V_P + V_N) \end{split}$$

The differential closed-loop gain of the amplifier is

$$\frac{V_{OUT,dm}}{V_{IN,dm}} = \frac{2R_{p}R_{N} + R_{p} + R_{N}}{2 + R_{p} + R_{N}}$$

and the common rejection of the amplifier is

$$\frac{V_{OUT,dm}}{V_{IN,cm}} = \frac{2(R_P - R_N)}{2 + R_P + R_N}$$

$$V_P \circ \frac{RGP}{V_N \circ RGN} \circ V_{ON} \circ V_{OP}$$

Figure 52. Functional Circuit Diagram of the AD8476 at a Given Gain

The preceding equations show that the gain accuracy and the common-mode rejection (CMRR) of the AD8476 are determined primarily by the matching of the feedback networks (resistor ratios). If the two networks are perfectly matched, that is, if  $R_P$  and  $R_N$  equal RF/RG, then the resistor network does not generate any CMRR errors and the differential closed loop gain of the amplifier reduces to

$$\frac{v_{OUT,dm}}{v_{IN,dm}} = \frac{RF}{RG}$$

The AD8476 integrated resistors are precision wafer-laser-trimmed to guarantee a minimum CMRR of 90 dB (32  $\mu V/V$ ), and gain error of less that 0.02%. To achieve equivalent precision and performance using a discrete solution, resistors must be matched to 0.01% or better.

#### **INPUT VOLTAGE RANGE**

The AD8476 can measure input voltages as large as the supply rails. The internal gain and feedback resistors form a divider, which reduces the input voltage seen by the internal input nodes of the amplifier. The largest voltage that can be measured properly is constrained by the output range of the amplifier and the capability of the amplifier's internal summing nodes. This voltage is defined by the input voltage, and the ratio between the feedback and the gain resistors.

Figure 53 shows the voltage at the internal summing nodes of the amplifier, defined by the input voltage and internal resistor network. If  $V_N$  is grounded, the expression shown reduces to

$$V_{PLUS} = V_{MINUS} = \frac{RG}{RF + RG} \Biggl( VOCM + \frac{1}{2} \frac{RF}{RG} V_P \Biggr)$$

The internal amplifier of the AD8476 has rail-to-rail inputs. To obtain accurate measurements with minimal distortion, the voltage at the internal inputs of the amplifier must stay below  $+V_S-1\ V$  and above  $-V_S$ .

The AD8476 provides overvoltage protection for excessive input voltages beyond the supply rails. Integrated ESD protection diodes at the inputs prevent damage to the AD8476 up to  $+V_S+18~V$  and  $-V_S-18~V$ .

#### **DRIVING THE AD8476**

Care should be taken to drive the AD8476 with a low impedance source: for example, another amplifier. Source resistance can unbalance the resistor ratios and, therefore, significantly degrade the gain accuracy and common-mode rejection of the AD8476. For the best performance, source impedance to the AD8476 input terminals should be kept below 0.1  $\Omega$ . Refer to the DC Precision section for details on the critical role of resistor ratios in the precision of the AD8476.

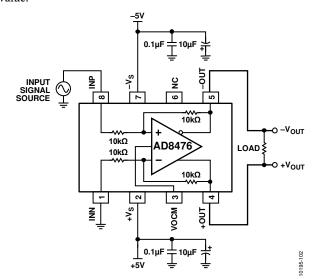

#### **POWER SUPPLIES**

The AD8476 operates over a wide range of supply voltages. It can be powered on a single supply as low as 3 V and as high as 18 V. The AD8476 can also operate on dual supplies from  $\pm 1.5$  V to  $\pm 9$  V

A stable dc voltage should be used to power the AD8476. Note that noise on the supply pins can adversely affect performance. For more information, see the PSRR performance curve in Figure 10.

Place a bypass capacitor of 0.1  $\mu F$  between each supply pin and ground, as close as possible to each supply pin. Use a tantalum capacitor of 10  $\mu F$  between each supply and ground. It can be farther away from the supply pins and, typically, it can be shared by other precision integrated circuits.

Figure 53. Voltages at the Internal Op Amp Inputs of the AD8476

## APPLICATIONS INFORMATION

#### TYPICAL CONFIGURATION

The AD8476 is designed to facilitate single-ended-to-differential conversion, common-mode level shifting, and precision processing of signals so that they are compatible with low voltage ADCs.

Figure 54 shows a typical connection diagram of the AD8476.

#### SINGLE-ENDED-TO-DIFFERENTIAL CONVERSION

Many industrial systems have single-ended inputs from input sensors; however, the signals are frequently processed by high performance differential input ADCs for higher precision. The AD8476 performs the critical function of precisely converting single-ended signals to the differential inputs of precision ADCs, and it does so with no need for external components.

To convert a single-ended signal to a differential signal, connect one input to the signal source and the other input to ground (see Figure 54). Note that either input can be driven by the source with the only effect being that the outputs have reversed polarity. The AD8476 also accepts truly differential input signals in precision systems with differential signal paths.

#### SETTING THE OUTPUT COMMON-MODE VOLTAGE

The VOCM pin of the AD8476 is internally biased by a precision voltage divider comprising of two 1  $M\Omega$  resistors between the supplies. This divider level shifts the output to midsupply. Relying on the internal bias results in an output common-mode voltage that is within 0.05% of the expected value.

Figure 54. Typical Configuration—8-Lead MSOP

In cases where control of the output common-mode level is desired, an external source or resistor divider can be used to drive the VOCM pin. If driven directly from a source, or with a resistor divider of unequal resistor values, the resistance seen by the VOCM pin should be less than 1 k $\Omega$ . If an external voltage divider consisting of equal resistor values is used to set VOCM to midsupply, higher values can be used because the external resistors are placed in parallel with the internal resistors. The output common-mode offset listed in the Specifications section assumes that the VOCM input is driven by a low impedance voltage source.

Because of the internal divider, the VOCM pin sources and sinks current, depending on the externally applied voltage and its associated source resistance.

It is also possible to connect the VOCM input to the common-mode level output of an ADC; however, care must be taken to ensure that the output has sufficient drive capability. The input impedance of the VOCM pin is  $500~k\Omega$ . If multiple AD8476 devices share one ADC reference output, a buffer may be necessary to drive the parallel inputs.

Table 6. Differential Input ADCs1

| ADC    | Resolution | Throughput Rate | <b>Power Dissipation</b> |

|--------|------------|-----------------|--------------------------|

| AD7674 | 16 Bits    | 100 kSPS        | 25 mW                    |

| AD7684 | 16 Bits    | 100 kSPS        | 6 mW                     |

| AD7687 | 16 Bits    | 250 kSPS        | 12.5 mW                  |

| AD7688 | 16 Bits    | 500 kSPS*       | 21.5 mW                  |

<sup>&</sup>lt;sup>1</sup> Depending on measurement/application type, check that the AD8476 meets settling time requirements.

#### LOW POWER ADC DRIVING

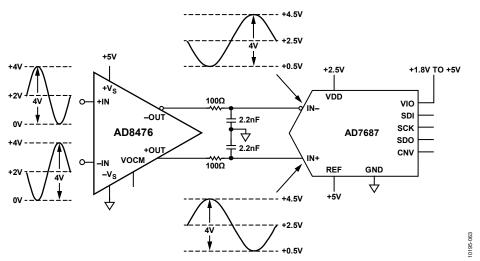

The AD8476 is designed to be a low power driver for ADCs with up to 16-bit precision and sampling rates of up to 250 kSPS. The circuit in Figure 56 shows the AD8476 driving the AD7687, a 16-bit, 250 kSPS fully differential SAR ADC. The filter between the AD8476 and the ADC reduces high frequency noise and reduces switching transients from the sampling of the ADC.

Choose the values of this filter with care. Optimal values for the filter may need to be determined empirically, but the guidelines discussed herein are provided to help the user. For optimum performance, this filter should be fast enough to settle full-scale to 0.5 LSB of the ADC within the acquisition time specified in the ADC data sheet, in this case, the AD7687. If the filter is slower than the acquisition time, distortion can result that looks like harmonics. If the filter is too fast, the noise bandwidth of the amplifier increases, thereby reducing the SNR of your system.

Additional considerations help determine the values of the individual components. THD of the ADC is likely to increase with source resistance. This is stated in the ADC data sheet. To reduce this effect, try to use smaller resistance and larger capacitance. Large capacitance values much greater than 2 nF are hard for the amplifier to drive. Higher capacitance also increases the effect of changes in output impedance.

It is also important to consider the signal frequency range of interest. The AD8476 THD decreases with higher frequency (see Figure 42) and output impedance increases with higher

frequency (see Figure 49). This higher output impedance yields slower settling, thus be certain to choose your capacitance so that the filter still meets the settling requirement at the maximum frequency of interest.

In the application shown, a 100  $\Omega$  resistors and 2.2 nF capacitors at each output were chosen. For driving the AD7687, this combination yields an SNR loss of 2.5 dB and good THD performance for a 20 kHz fundamental frequency, with an ADC throughput rate of 250kSPS. The filter bandwidth can be determined by the following equation:

Figure 55. FFT of AD8476 Driving the AD7687

Figure 56. AD8476 Conditioning and Level Shifting a Differential Voltage to Drive Single-Supply ADC

## **OUTLINE DIMENSIONS**

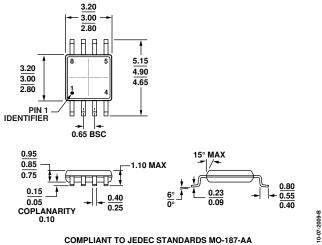

Figure 57. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MO-229-WEEE.

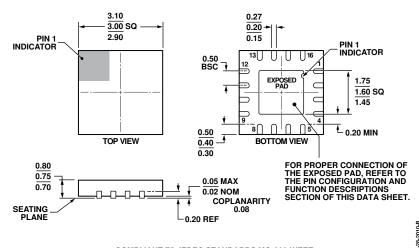

Figure 58. 16-Lead Lead Frame Chip Scale Package [LFCSP\_WQ] 3 mm × 3 mm Body, Very Very Thin Quad (CP-16-25) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                              | Package Option | Branding |

|--------------------|-------------------|--------------------------------------------------|----------------|----------|

| AD8476BCPZ-R7      | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-25       | Y45      |

| AD8476BCPZ-RL      | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-25       | Y45      |

| AD8476BCPZ-WP      | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-25       | Y45      |

| AD8476ACPZ-R7      | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-25       | Y44      |

| AD8476ACPZ-RL      | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-25       | Y44      |

| AD8476ACPZ-WP      | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-25       | Y44      |

| AD8476BRMZ         | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]         | RM-8           | Y47      |

| AD8476BRMZ-R7      | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]         | RM-8           | Y47      |

| AD8476BRMZ-RL      | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]         | RM-8           | Y47      |

| AD8476ARMZ         | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]         | RM-8           | Y46      |

| AD8476ARMZ-R7      | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]         | RM-8           | Y46      |

| AD8476ARMZ-RL      | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]         | RM-8           | Y46      |

| AD8476-EVALZ       |                   | Evaluation Board                                 |                |          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

# **NOTES**

**NOTES**