Rev 1; 9/04

# **DALLAS** SEMICONDUCTOR **I<sup>2</sup>C, 32-Bit Binary Counter Watchdog RTC with** Trickle Charger and Reset Input/Output

## **General Description**

**Applications**

The DS1374 is a 32-bit binary counter designed to continuously count time in seconds. An additional counter generates a periodic alarm or serves as a watchdog timer. If disabled, this counter can be used as 3 bytes of nonvolatile (NV) RAM. Separate output pins are provided for an interrupt and a square wave at one of four selectable frequencies. A precision temperature-compensated reference and comparator circuit monitor the status of V<sub>CC</sub> to detect power failures, provide a reset output, and automatically switch to the backup supply when necessary. Additionally, the reset pin is monitored as a pushbutton input for externally generating a reset. The device is programmed serially through an I<sup>2</sup>C<sup>™</sup> serial interface.

## \_Features

- ♦ 32-Bit Binary Counter

- Second Binary Counter Provides Time-of-Day Alarm, Watchdog Timer, or NV RAM

- Separate Square-Wave and Interrupt Output Pins

- ♦ I<sup>2</sup>C Serial Interface

- Automatic Power-Fail Detect and Switch Circuitry

- Single-Pin Pushbutton Reset Input/Open-Drain Reset Output

- Low-Voltage Operation

- Trickle-Charge Capability

- ♦ -40°C to +85°C Operating Temperature Range

- ◆ 10-Pin µSOP, 16-Pin SO

- Available in a Surface-Mount Package with an Integrated Crystal (DS1374C)

- Underwriters Laboratory (UL) Recognized

Portable Instruments Point-of-Sale Equipment Medical Equipment Telecommunications

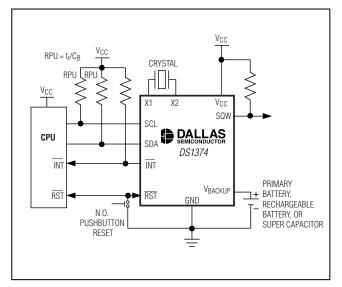

## **Typical Operating Circuit**

## **Ordering Information**

| TEMP RANGE     | PIN-<br>PACKAGE                                                                        | TOP MARK                                                                                                                                                                                             |

|----------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -40°C to +85°C | 10 µSOP                                                                                | DS1374-18                                                                                                                                                                                            |

| -40°C to +85°C | 10 µSOP                                                                                | DS1374-3                                                                                                                                                                                             |

| -40°C to +85°C | 10 µSOP                                                                                | DS1374-33                                                                                                                                                                                            |

| -40°C to +85°C | 16 SO, 0.300"                                                                          | DS1374C-18                                                                                                                                                                                           |

| -40°C to +85°C | 16 SO, 0.300"                                                                          | DS1374C-3                                                                                                                                                                                            |

| -40°C to +85°C | 16 SO, 0.300"                                                                          | DS1374C-33                                                                                                                                                                                           |

|                | -40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C | TEMP RANGE         PACKAGE           -40°C to +85°C         10 μSOP           -40°C to +85°C         10 μSOP           -40°C to +85°C         10 μSOP           -40°C to +85°C         16 SO, 0.300" |

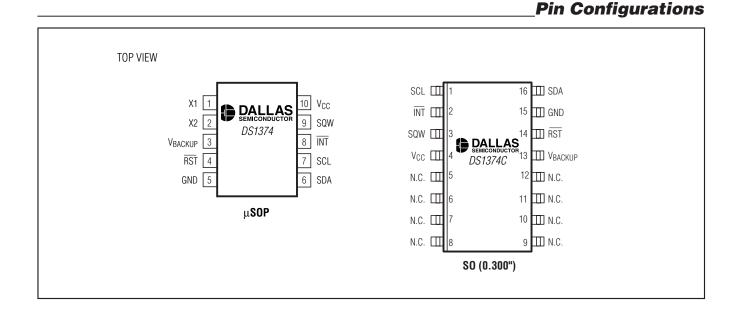

Pin Configurations appear at the end of the data sheet.

*I<sup>2</sup>C* is a trademark of Philips Corp. Purchase of *I<sup>2</sup>C* components of Maxim Integrated Products, Inc., or one of its sublicensed Associated Companies, conveys a license under the Philips *I<sup>2</sup>C* Patent Rights to use these components in an *I<sup>2</sup>C* system, provided that the system conforms to the *I<sup>2</sup>C* Standard Specification as defined by Philips.

# BALLAS ////X//

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

Voltage Range on V\_CC Pin Relative to Ground .....-0.3V to +6.0V Voltage Range on SDA, SCL, and WDS

Relative to Ground .....-0.3V to V<sub>CC</sub> + 0.3V Operating Temperature Range .....-40°C to +85°C Storage Temperature Range ......55°C to +125°C Soldering Temperature Range .....See the Handling, PC Board Layout, and Assembly section.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **RECOMMENDED DC OPERATING CONDITIONS**

(V<sub>CC</sub> = V<sub>CC MIN</sub> to V<sub>CC MAX</sub>,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                             | SYMBOL          | CONDITIONS | MIN                   | ТҮР  | МАХ                       | UNITS |

|-----------------------------------------------------------------------|-----------------|------------|-----------------------|------|---------------------------|-------|

|                                                                       |                 | DS1374-33  | 2.97                  | 3.3  | 5.50                      |       |

| Supply Voltage<br>(Notes 2, 3)                                        | Vcc             | DS1374-3   | 2.7                   | 3.0  | 3.3                       | V     |

|                                                                       |                 | DS1374-18  | 1.71                  | 1.8  | 1.89                      |       |

| Input Logic 1                                                         | VIH             | (Note 2)   | 0.7 x V <sub>CC</sub> |      | $V_{CC} + 0.3$            | V     |

| Input Logic 0                                                         | VIL             | (Note 2)   | -0.3                  |      | +0.3 x<br>V <sub>CC</sub> | V     |

| Pullup Resistor Voltage (INT,<br>SQW, SDA, SCL), V <sub>CC</sub> = 0V | V <sub>PU</sub> | (Note 2)   |                       |      | 5.5                       | V     |

|                                                                       |                 | DS1374-33  | 2.70                  | 2.88 | 2.97                      |       |

| Power-Fail Voltage<br>(Note 2)                                        | VPF             | DS1374-3   | 2.45                  | 2.6  | 2.7                       | V     |

|                                                                       |                 | DS1374-18  | 1.51                  | 1.6  | 1.71                      |       |

| Backup Supply Voltage                                                 |                 | DS1374-33  | 1.3                   | 3.0  | V <sub>CC</sub><br>MAX    | V     |

| (Notes 2, 3, 4)                                                       | VBACKUP         | DS1374-3   | 1.3                   | 3.0  | 3.7                       | v     |

## DC ELECTRICAL CHARACTERISTICS

(V\_{CC} = V\_{CC MIN} to V\_{CC MAX}, T\_A = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                      | SYMBOL     | CONDITIONS                                   | MIN  | ТҮР  | MAX | UNITS |  |

|------------------------------------------------|------------|----------------------------------------------|------|------|-----|-------|--|

|                                                | R1         | (Note 5)                                     |      | 250  |     |       |  |

| Trickle-Charge Current-Limiting<br>Resistors   | R2         | (Note 6)                                     |      | 2000 |     | Ω     |  |

| 163131013                                      | R3         | (Note 7)                                     |      | 250  |     |       |  |

| Input Leakage                                  | ILI        | (Note 8)                                     | -1   |      | +1  |       |  |

| I/O Leakage                                    | ILO        | (Note 9)                                     | -1   |      | +1  | μA    |  |

| RST Pin I/O Leakage                            | ILORST     | (Note 10)                                    | -200 |      | +1  |       |  |

| SDA Logic 0 Output ( $V_{OL} = 0.4V$ )         | IOLSDA     |                                              |      |      | 3.0 | mA    |  |

| RST, SQW, and INT Logic 0<br>Outputs (Note 11) |            | $V_{CC} > 2V; V_{OL} = 0.4V$                 |      |      | 3.0 | mA    |  |

|                                                | IOL1       | $1.71V < V_{CC} < 2V; V_{OL} = 0.2 V_{CC}$   |      |      | 3.0 | IIIA  |  |

|                                                |            | $1.3V < V_{CC} < 1.71V; V_{OL} = 0.2 V_{CC}$ |      |      | 250 | μA    |  |

|                                                |            | DS1374-18                                    |      | 75   | 150 |       |  |

| Active Supply Current<br>(Notes 11, 12)        | ICCA       | DS1374-3                                     |      | 110  | 200 | μA    |  |

| (10103 11, 12)                                 |            | DS1374-33                                    |      | 180  | 300 |       |  |

|                                                |            | DS1374-18                                    |      | 60   | 100 |       |  |

| Standby Current (Notes 11, 13)                 | lccs       | DS1374-3                                     |      | 80   | 125 | μA    |  |

|                                                |            | DS1374-33                                    |      | 115  | 175 |       |  |

| VBACKUP Leakage Current<br>(VBACKUP = 3.7V)    | IBACKUPLKG |                                              |      |      | 100 | nA    |  |

## DC ELECTRICAL CHARACTERISTICS

(VCC = 0V, VBACKUP = 3.7V,  $T_A = -40^{\circ}C$  to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                               | SYMBOL    | CONDITIONS     | MAX | ТҮР | МАХ  | UNITS |

|---------------------------------------------------------|-----------|----------------|-----|-----|------|-------|

| V <sub>BACKUP</sub> Current (OSC ON);<br>SQW OFF        | IBKOSC1   | (Note 14)      |     | 400 | 700  | nA    |

| V <sub>BACKUP</sub> Current (OSC ON);<br>SQW ON (32kHz) | IBKOSC2   | (Notes 14, 15) |     | 600 | 1000 | nA    |

| VBACKUP Data-Retention Current<br>(OSC OFF)             | IBACKUPDR |                |     | 25  | 100  | nA    |

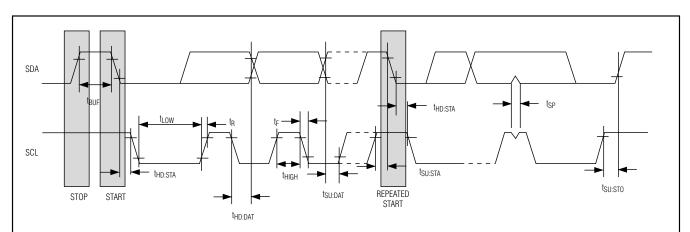

# AC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = V<sub>CC MIN</sub> to V<sub>CC MAX</sub>,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 1) (Figure 1)

| PARAMETER                                                            | SYMBOL              | CONDITIONS    | MIN T             | YP MAX | UNITS |  |

|----------------------------------------------------------------------|---------------------|---------------|-------------------|--------|-------|--|

|                                                                      | £                   | Fast mode     | 100               | 400    |       |  |

| SCL Clock Frequency (Note 16)                                        | fscl                | Standard mode | 0                 | 100    | kHz   |  |

| Bus Free Time Between STOP                                           | tour                | Fast mode     | 1.3               |        |       |  |

| and START Conditions                                                 | tBUF                | Standard mode | 4.7               |        | μs    |  |

| Hold Time (Repeated) START                                           | tup 07.             | Fast mode     | 0.6               |        |       |  |

| Condition (Note 17)                                                  | <sup>t</sup> HD:STA | Standard mode | 4.0               |        | μs    |  |

| Low Period of SCL Clock                                              | t. 0.11             | Fast mode     | 1.3               |        |       |  |

| LOW PERIOD OF SCE CIOCK                                              | tlow                | Standard mode | 4.7               |        | μs    |  |

| High Dariad of SCL Clask                                             | t                   | Fast mode     | 0.6               |        |       |  |

| High Period of SCL Clock                                             | thigh               | Standard mode | 4.0               |        | μs    |  |

| Data Hald Time (Natas 19, 10)                                        | tup p               | Fast mode     | 0                 | 0.9    |       |  |

| Data Hold Time (Notes 18, 19)                                        | <sup>t</sup> HD:DAT | Standard mode | 0                 | 0.9    | μs    |  |

| Data Satur Time (Nata 20)                                            | +                   | Fast mode     | 100               |        | ns    |  |

| Data Setup Time (Note 20)                                            | <sup>t</sup> SU:DAT | Standard mode | 250               |        | ns    |  |

| Chart Catura Times                                                   |                     | Fast mode     | 0.6               |        |       |  |

| Start Setup Time                                                     | tsu:sta             | Standard mode | 4.7               |        | μs    |  |

| Rise Time of Both SDA and SCL                                        | ta                  | Fast mode     | 20 +              | 300    | 20    |  |

| Signals (Note 16)                                                    | tR                  | Standard mode | 0.1CB             | 1000   | ns    |  |

| Fall Time of Both SDA and SCL                                        | +                   | Fast mode     | 20 +              | 300    | 20    |  |

| Signals (Note 16)                                                    | tF                  | Standard mode | 0.1C <sub>B</sub> | 300    | ns    |  |

| Satur Time for STOD Condition                                        | touro               | Fast mode     | 0.6               |        |       |  |

| Setup Time for STOP Condition                                        | tsu:sto             | Standard mode | 4.7               |        | μs    |  |

| Capacitive Load for Each Bus Line                                    | CB                  | (Note 16)     |                   | 400    | pF    |  |

| I/O Capacitance (SDA, SCL)                                           | CI/O                | (Note 21)     |                   | 10     | pF    |  |

| Pulse Width of Spikes That Must<br>be Suppressed by the Input Filter | tsp                 | Fast mode     |                   | 30     | ns    |  |

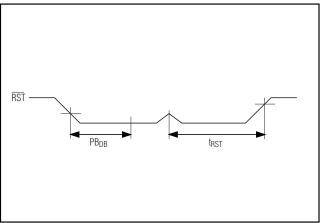

| Pushbutton Debounce                                                  | PBDB                | (Figure 2)    | 2                 | 250    | ms    |  |

| Reset Active Time                                                    | tRST                | (Figure 2)    | 2                 | 250    | ms    |  |

| Oscillator Stop Flag (OSF) Delay                                     | tosf                | (Note 22)     | 1                 | 00     | ms    |  |

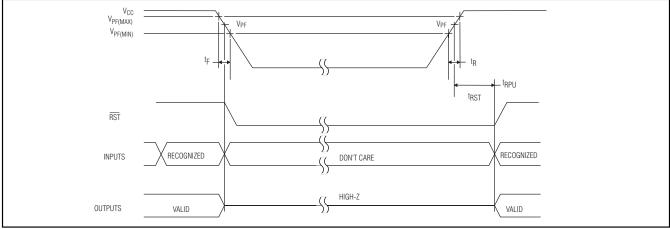

## **POWER-UP/POWER-DOWN CHARACTERISTICS**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$  (Figure 3)

| PARAMETER                                                                  | SYMBOL         | CONDITIONS | MIN | ТҮР | МАХ | UNITS |

|----------------------------------------------------------------------------|----------------|------------|-----|-----|-----|-------|

| V <sub>CC</sub> Detect to Recognize Inputs (V <sub>CC</sub> Rising)        | trpu           | (Note 23)  |     | 250 |     | ms    |

| V <sub>CC</sub> Fall Time; V <sub>PF(MAX)</sub> to<br>V <sub>PF(MIN)</sub> | tF             |            | 300 |     |     | μs    |

| V <sub>CC</sub> Rise Time; V <sub>PF(MIN)</sub> to<br>VPF(MAX)             | t <sub>R</sub> |            | 0   |     |     | μs    |

WARNING: Under no circumstances are negative undershoots, of any amplitude, allowed when the device is in write protection.

- Note 1: Limits at -40°C are guaranteed by design and not production tested.

- **Note 2:** All voltages are referenced to ground.

- Note 3: VBACKUP should not exceed VCC MAX or 3.7V, whichever is greater.

- Note 4: The use of the  $250\Omega$  trickle-charge resistor is not allowed at V<sub>CC</sub> > 3.63V and should not be enabled.

- **Note 5:** Measured at  $V_{CC}$  = typ,  $V_{BACKUP}$  = 0V, register 09h = A5h.

- **Note 6:** Measured at  $V_{CC} = typ$ ,  $V_{BACKUP} = 0V$ , register 09h = A6h.

- **Note 7:** Measured at  $V_{CC}$  = typ,  $V_{BACKUP}$  = 0V, register 09h = A7h.

- Note 8: SCL only.

- Note 9: SDA and SQW and INT.

- **Note 10:** The  $\overline{\text{RST}}$  pin has an internal 50k $\Omega$  pullup resistor to V<sub>CC</sub>.

- Note 11: Trickle charger disabled.

- Note 12: I<sub>CCA</sub>—SCL clocking at max frequency = 400kHz.

- Note 13: Specified with I<sup>2</sup>C bus inactive.

- Note 14: Measured with a 32.768kHz crystal attached to the X1 and X2 pins.

- Note 15: WDSTR = 1. BBSQW = 1 is required for operation when V<sub>CC</sub> is below the power-fail trip point (or absent).

- Note 16: C<sub>B</sub>—total capacitance of one bus line in pF.

- Note 17: After this period, the first clock pulse is generated.

- Note 18: The maximum t<sub>HD:DAT</sub> only has to be met if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

- Note 19: A device must internally provide a hold time of at least 300ns for the SDA signal (referred to as the VIHMIN of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- **Note 20:** A fast-mode device can be used in a standard-mode system, but the requirement  $t_{SU:DAT} \ge to 250$ ns must be met. This is automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line  $t_{R} \max + t_{SU:DAT} = 1000 + 250 = 1250$ ns before the SCL line is released.

- Note 21: Guaranteed by design. Not production tested.

- Note 22: The parameter  $t_{OSF}$  is the period of time the oscillator must be stopped for the OSF flag to be set over the voltage range of  $0V \le V_{CC} \le V_{CC}$  MAX and  $1.3V \le V_{BACKUP} \le 3.7V$ .

- Note 23: This delay applies only if the oscillator is enabled and running. If the EOSC bit is 1, the startup time of the oscillator is added to this delay.

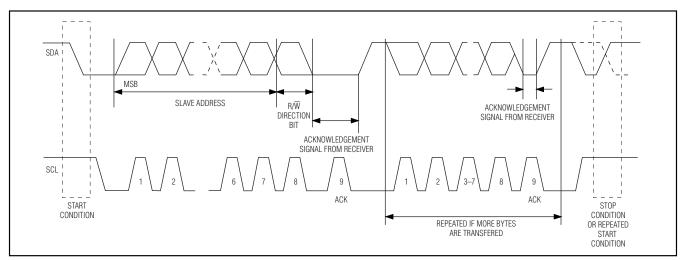

Figure 1. Data Transfer on I<sup>2</sup>C Serial Bus

Figure 2. Pushbutton Reset Timing

Figure 3. Power-Up/Power-Down Timing

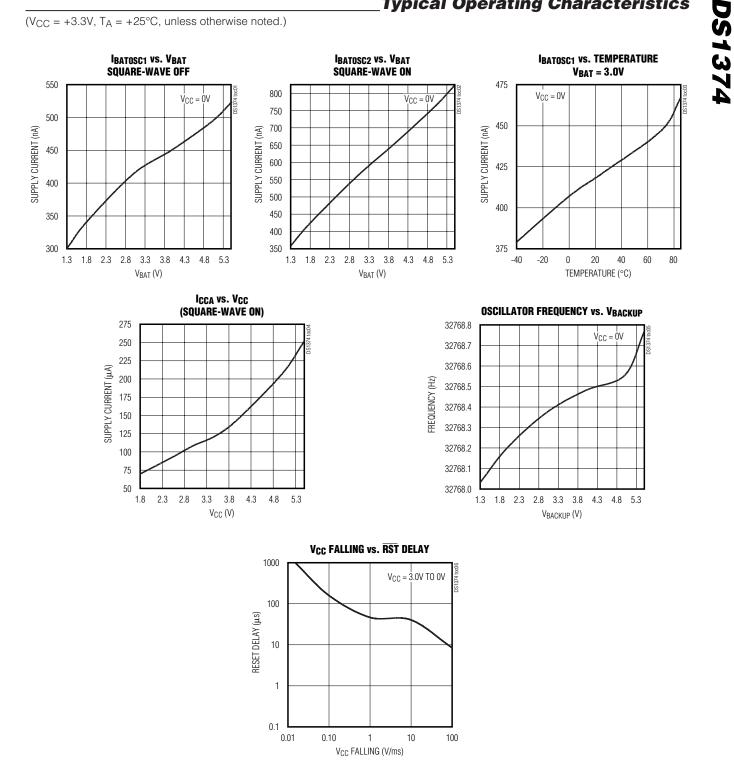

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

## **Typical Operating Characteristics**

## **Pin Description**

| PII  | N    | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| μSOP | SO   | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1, 2 | _    | X1, X2          | Connections for a Standard 32.768kHz Quartz Crystal. The internal oscillator circuitry is designed for operation with a crystal having a specified load capacitance ( $C_L$ ) of 6pF. Pin X1 is the input to the oscillator and can optionally be connected to an external 32.768kHz oscillator. The output of the internal oscillator, pin X2, is floated if an external oscillator is connected to pin X1.                                |

| 3    | 13   | VBACKUP         | Connection for a Secondary Power Supply. Supply voltage must be held between 1.3V and 3.7V (-18 and -3) or 1.3V and 5.5V (-33) for proper operation. This pin can be connected to a primary cell such as a lithium button cell. Additionally, this pin can be connected to a rechargeable cell or a super cap when used with the trickle-charge feature. UL recognized to ensure against reverse charging when used with a lithium battery. |

| 4    | 14   | RST             | Active-Low, Open-Drain Output with a Debounced Pushbutton Input. This pin can be activated by a pushbutton reset request, a watchdog alarm condition, or a power-fail event. It has an internal $50k\Omega$ pullup resistor.                                                                                                                                                                                                                |

| 5    | 15   | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6    | 16   | SDA             | Serial Data Input/Output. SDA is the input/output for the 2-wire serial interface. The SDA pin is open drain and requires an external pullup resistor.                                                                                                                                                                                                                                                                                      |

| 7    | 1    | SCL             | Serial Clock Input. SCL is the clock input for the 2-wire serial interface and is used to synchronize data movement on the serial interface.                                                                                                                                                                                                                                                                                                |

| 8    | 2    | ĪNT             | Interupt. This pin is used to output the alarm interrupt or the watchdog reset signal. It is active-low open drain and requires an external pullup resistor.                                                                                                                                                                                                                                                                                |

| 9    | 3    | SQW             | Square-Wave Output. This pin is used to output the programmable square-wave signal. It is open drain and requires an external pullup resistor.                                                                                                                                                                                                                                                                                              |

| 10   | 4    | V <sub>CC</sub> | DC Power for Primary Power Supply                                                                                                                                                                                                                                                                                                                                                                                                           |

| _    | 5–12 | N.C.            | No Connection. Must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                 |

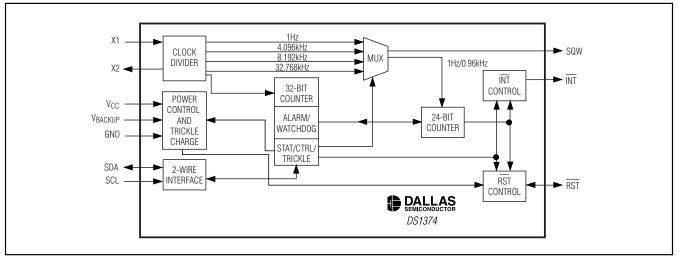

Figure 4. Functional Diagram

# BALLAS ANALY

#### Table 1. Crystal Specifications\*

| PARAMETER            | SYMBOL         | MIN | ТҮР    | МАХ | UNITS |

|----------------------|----------------|-----|--------|-----|-------|

| Nominal<br>Frequency | f <sub>O</sub> |     | 32.768 |     | kHz   |

| Series<br>Resistance | ESR            |     |        | 45  | kΩ    |

| Load<br>Capacitance  | CL             |     | 6      |     | pF    |

\*The crystal, traces, and crystal input pins should be isolated from RF generating signals. Refer to Application Note 58: Crystal Considerations for Dallas Real-Time Clocks for additional specifications.

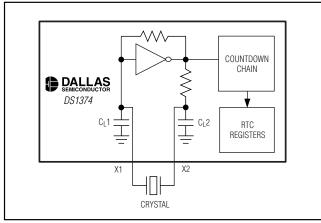

Figure 5. Oscillator Circuit Showing Internal Bias Network

## **Detailed Description**

The DS1374 is a real-time clock with an I<sup>2</sup>C serial interface. It provides elapsed seconds from a user-defined starting point in a 32-bit counter (Figure 4). A 24-bit counter can be configured as either a watchdog counter or an alarm counter. An on-chip oscillator circuit uses a customer-supplied 32.768kHz crystal to keep time. A power-control circuit switches operation from V<sub>CC</sub> to V<sub>BACKUP</sub> and back when power on V<sub>CC</sub> is cycled. If a rechargeable backup supply is used, a trickle charger can be enabled to charge the backup supply while V<sub>CC</sub> is on.

## **Oscillator Circuit**

The DS1374 uses an external 32.768kHz crystal. The oscillator circuit does not require any external resistors or capacitors to operate. Table 1 specifies several crystal parameters for the external crystal. Figure 5 shows a functional schematic of the oscillator circuit. The startup time is usually less than 1 second when using a crystal with the specified characteristics.

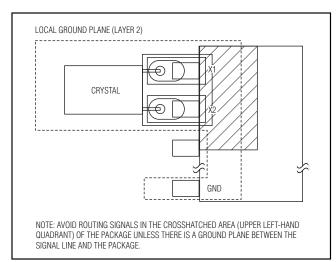

Figure 6. Layout Example

## Clock Accuracy

Clock accuracy is dependent upon the accuracy of the crystal and the accuracy of the match between the capacitive load of the oscillator circuit and the capacitive load for which the crystal was trimmed. Additional error is added by crystal frequency drift caused by temperature shifts. External circuit noise coupled into the oscillator circuit can result in the clock running fast. Figure 6 shows a typical PC board layout for isolating the crystal and oscillator from noise. Refer to *Application Note 58: Crystal Considerations with Dallas Real-Time Clocks* for detailed information.

#### DS1374C Only

The DS1374C integrates a standard 32,768Hz crystal into the package. Typical accuracy at nominal V<sub>CC</sub> and  $25^{\circ}$ C is approximately 10ppm. See *Application Note 58* for information about crystal accuracy vs. temperature.

#### Address Map

Table 2 shows the address map for the DS1374 registers. During a multibyte access, the address pointer wraps around to location 00h when it reaches the end of the register space (08h). On an I<sup>2</sup>C START, STOP, or address pointer incrementing to location 00h, the current time is transferred to a second set of registers. These secondary registers read the time information, while the clock continues to run. This eliminates the need to reread the registers in case of an update of the main registers during a read.

## Time-of-Day Counter

The time-of-day counter is a 32-bit up counter. The contents can be read or written by accessing the

#### Table 2. Address Map

| ADDRESS | BIT 7                 | BIT 6 | BIT 5  | BIT 4               | BIT 3        | BIT 2 | BIT 1 | BIT 0 | FUNCTION               |

|---------|-----------------------|-------|--------|---------------------|--------------|-------|-------|-------|------------------------|

| 00H     |                       |       |        | Time-of-Day Counter |              |       |       |       |                        |

| 01H     |                       |       |        | Time-of-Day Counter |              |       |       |       |                        |

| 02H     |                       |       |        | Time-of-Day Counter |              |       |       |       |                        |

| 03H     |                       |       |        | Time-of-Day Counter |              |       |       |       |                        |

| 04H     | WD/ALM Counter Byte 0 |       |        |                     |              |       |       |       | Watchdog/Alarm Counter |

| 05H     |                       |       | V      | VD/ALM Co           | unter Byte   | 1     |       |       | Watchdog/Alarm Counter |

| 06H     |                       |       | V      | VD/ALM Co           | unter Byte 2 | 2     |       |       | Watchdog/Alarm Counter |

| 07H     | EOSC                  | WACE  | WD/ALM | BBSQW               | WDSTR        | RS2   | RS1   | AIE   | Control                |

| 08H     | OSF                   | 0     | 0      | 0                   | 0            | 0     | 0     | AF    | Status                 |

| 09H     | TCS3                  | TCS2  | TCS1   | TCS0                | DS1          | DS0   | ROUT1 | ROUT0 | Trickle Charger        |

Note: Unless otherwise specified, the state of the registers is not defined when power is first applied.

address range 00h–03h. When the counter is read, the current time of day is latched into a register, which is output on the serial data line while the counter continues to increment.

#### \_Watchdog/Alarm Counter

The contents of the watchdog/alarm counter, which is a separate 24-bit down counter, are accessed in the address range 04h–06h. When this counter is written, the counter and a seed register are loaded with the desired value. When the counter is to be reloaded, it uses the value in the seed register. When the counter is read, the current counter value is latched into a register, which is output on the serial data line while the counter continues to decrement.

If the counter is not needed, it can be disabled and used as a 24-bit cache of NV RAM by setting the WACE bit in the control register to logic 0. If all 24 bits of the watchdog/alarm counter are written to zero when WACE = 1, the counter is disabled and the AF bit is not set.

When the WD/ALM bit in the control register is set to a logic 0, the WD/ALM counter decrements every second until it reaches zero. At this point, the AF bit in the status register is set and the counter is reloaded and restarted. If AF is set when the watchdog function is enabled, the output selected by WDSTR immediately becomes active.

When the WD/ALM bit is set to logic 1, the WD/ALM counter decrements every 1/4096 of a second (approximately every 244 $\mu$ s) until it reaches zero, sets the AF bit in the status register, and stops. If WDSTR = 0, the RST pin pulses low for 250ms, and accesses to the DS1374 are inhibited. At the end of the 250ms pulse, the AF bit is cleared to zero, the RST pin becomes high impedance, and read/write access to the DS1374 is enabled. If AIE =

1 and WDSTR = 1, the  $\overline{INT}$  pin pulses low for 250ms. The pulse cannot be truncated by writing either AF or AIE to zero during the low time of the  $\overline{INT}$  pin. If the WD/ALM counter is written during the 250ms pulse, the counter starts decrementing upon the pulse completion. At the completion, the AF bit clears to zero and the  $\overline{INT}$  pin becomes high impedance. The WD/ALM counter can be reloaded and restarted before the counter reaches zero by reading or writing any of the WD/ALM counter registers.

#### Power-Up/Power-Down Reset and \_\_\_\_\_Pushbutton Reset Functions

A precision temperature-compensated reference and comparator circuit monitors the status of V<sub>CC</sub>. When an out-of-tolerance condition occurs, an internal power-fail signal is generated that forces the RST pin low and blocks read/write access to the DS1374. When V<sub>CC</sub> returns to an in-tolerance condition, the RST pin is held low for 250ms to allow the power supply to stabilize. If the EOSC bit is set to a logic 1 (to disable the oscillator in battery-backup mode), the reset signal is kept active for 250ms plus the startup time of the oscillator.

The DS1374 provides for a pushbutton switch to be connected to the RST output pin. When the DS1374 is not in a reset cycle, it continuously monitors the RST signal for a low-going edge. If an edge is detected, the DS1374 debounces the switch by pulling the RST pin low and inhibits read/write access. After the internal 250ms timer has expired, the device continues to monitor the RST line. If the line is still low, the DS1374 continues to monitor the line, looking for a rising edge. Upon detecting release, the DS1374 forces the RST pin low and holds it low for an additional 250ms.

| Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|--------|-------|-------|-------|-------|-------|

| EOSC  | WACE  | WD/ALM | BBSQW | WDSTR | RS2   | RS1   | AIE   |

#### **Special Purpose Registers**

The DS1374 has two additional registers (07h–08h) that control the WD/ALM counter and the square-wave, interrupt, and reset outputs.

#### **Control Register (07h)**

**Bit 7/Enable Oscillator (EOSC).** When set to logic 0, the oscillator is started. When set to logic 1, the oscillator is stopped. When this bit is set to logic 1, the oscillator is stopped and the DS1374 is placed into a low-power standby mode (IDDR). This bit is clear (logic 0) when power is first applied. When the DS1374 is powered by V<sub>CC</sub>, the oscillator is always on regardless of the state of the EOSC bit.

**Bit 6/WD/ALM Counter Enable (WACE).** When set to logic 1, the WD/ALM counter is enabled. When set to logic 0, the WD/ALM counter is disabled, and the 24 bits can be used as NV RAM. This bit is clear (logic 0) when power is first applied.

**Bit 5/WD/ALM Counter Select (WD/ALM).** When set to logic 0, the counter decrements every second until it reaches zero and is then reloaded and restarted. When set to logic 1, the WD/ALM counter decrements every 1/4096 of a second (approximately every 244µs) until it reaches zero, sets the AF bit in the status register, and stops. If any of the WD/ALM counter registers are accessed before the counter reaches zero, the counter is reloaded and restarted. This bit is clear (logic 0) when power is first applied.

**Bit 4/Battery-Backed Square-Wave Enable (BBSQW).** This bit, when set to logic 1, enables the square-wave output when V<sub>CC</sub> is absent and when the DS1374 is being powered by the V<sub>BACKUP</sub> pin. When BBSQW is logic 0, the SQW pin goes high impedance when V<sub>CC</sub> falls below the power-fail trip point. This bit is disabled

(logic 0) when power is first applied.

**Bit 3/Watchdog Reset Steering Bit (WDSTR).** This bit selects which output pin the watchdog-reset signal occurs on. When the WDSTR bit is set to logic 0, a 250ms pulse occurs on the RST pin if WD/ALM = 1 and the WD/ALM counter reaches zero. The 250ms reset pulse occurs on the INT pin when the WDSTR bit is set to logic 1. This bit is logic 0 when power is first applied.

**Bits 2, 1/Rate Select (RS2 and RS1).** These bits control the frequency of the square-wave output when the square wave has been enabled. Table 3 shows the square-wave frequencies that can be selected with the RS bits. These bits are both set (logic 1) when power is first applied.

**Bit 0/Alarm Interrupt Enable (AIE).** When set to logic 1, this bit permits the alarm flag (AF) bit in the status register to assert INT (when INTCN = 1). When set to logic 0 or INTCN is set to logic 0, the AF bit does not initiate the INT signal. If the WD/ALM bit is set to logic 1 and the AF flag is set, writing AIE to zero does not truncate the 250ms pulse on the INT pin. The AIE bit is at logic 0 when power is first applied. The INT output is available while the device is powered by either supply.

| TCS3 | TCS2 | TCS1 | TCS0 | DS1 | DS0 | ROUT1 | ROUT0 | FUNCTION                        |

|------|------|------|------|-----|-----|-------|-------|---------------------------------|

| Х    | Х    | Х    | Х    | 0   | 0   | Х     | Х     | Disabled                        |

| Х    | Х    | Х    | Х    | 1   | 1   | Х     | Х     | Disabled                        |

| Х    | Х    | Х    | Х    | Х   | Х   | 0     | 0     | Disabled                        |

| 1    | 0    | 1    | 0    | 0   | 1   | 0     | 1     | No diode, 250 $\Omega$ resistor |

| 1    | 0    | 1    | 0    | 1   | 0   | 0     | 1     | One diode, $250\Omega$ resistor |

| 1    | 0    | 1    | 0    | 0   | 1   | 1     | 0     | No diode, $2k\Omega$ resistor   |

| 1    | 0    | 1    | 0    | 1   | 0   | 1     | 0     | One diode, $2k\Omega$ resistor  |

| 1    | 0    | 1    | 0    | 0   | 1   | 1     | 1     | No diode, $4k\Omega$ resistor   |

| 1    | 0    | 1    | 0    | 1   | 0   | 1     | 1     | One diode, $4k\Omega$ resistor  |

| 0    | 0    | 0    | 0    | 0   | 0   | 0     | 0     | Power-on reset value            |

#### Table 4. Trickle Charge Register

BALLAS ////X//

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| OSF   | 0     | 0     | 0     | 0     | 0     | 0     | AF    |

#### Table 3. Square-Wave Output Frequency

| RS2 | RS1 | SQUARE-WAVE OUTPUT FREQUENCY |

|-----|-----|------------------------------|

| 0   | 0   | 1Hz                          |

| 0   | 1   | 4.096kHz                     |

| 1   | 0   | 8.192kHz                     |

| 1   | 1   | 32.768kHz                    |

#### **Status Register (08h)**

**Bit 7/Oscillator Stop Flag (OSF).** A logic 1 in this bit indicates that the oscillator either is stopped or was stopped for some period of time and can be used to judge the validity of the timekeeping data. This bit is set to logic 1 any time the oscillator stops. The following are examples of conditions that can cause the OSF bit to be set:

- 1) The first time power is applied.

- 2) The voltage present on V<sub>CC</sub> is insufficient to support oscillation.

- 3) The EOSC bit is turned off.

- 4) External influences on the crystal (i.e., noise, leak-age, etc.).

This bit remains at logic 1 until written to logic 0.

**Bit 0/Alarm Flag (AF).** A logic 1 in the alarm flag bit indicates that the WD/ALM counter reached zero. If WD/ALM is set to zero and the AIE bit = 1, the INT pin goes low and stays low until AF is cleared. AF is

cleared when written to logic 0. This bit can only be written to logic 0. Attempting to write logic 1 leaves the value unchanged. If WD/ALM is set to 1 and the AIE bit = 1, the INT pin pulses low for 250ms when the WD/ALM counter reaches zero and sets AF = 1. At the pulse completion, the DS1374 clears the AF bit to zero. If the 250ms pulse is active, writing AF to zero does not truncate the pulse.

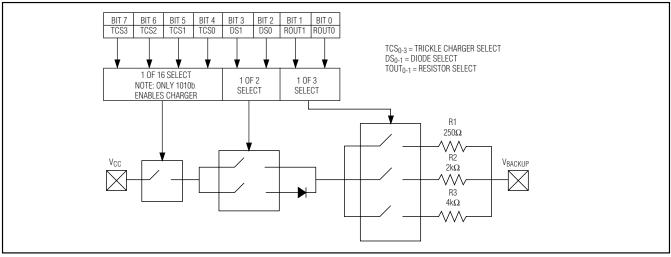

#### Trickle-Charge Register (10h)

The simplified schematic in Figure 7 shows the basic components of the trickle charger. The trickle-charge select (TCS) bits (bits 4–7) control the selection of the trickle charger. To prevent accidental enabling, only a pattern of 1010 enables the trickle charger. All other patterns disable the trickle charger. The trickle charger is disabled when power is first applied. The diode select (DS) bits (bits 2, 3) select whether or not a diode is connected between V<sub>CC</sub> and V<sub>BACKUP</sub>. If DS is 01, no diode is selected; if DS is 10, a diode is selected. The ROUT bits (bits 0, 1) select the value of the resistor connected between V<sub>CC</sub> and V<sub>BACKUP</sub>. Table 4 shows the resistor selected by the resistor select (DS) bits.

**Warning:** The ROUT value of 250 $\Omega$  must not be selected whenever V<sub>CC</sub> is greater than 3.63V.

The user determines diode and resistor selection according to the maximum current desired for battery or super cap charging. The maximum charging current can be calculated as illustrated in the following example.

Figure 7. Programmable Trickle Charger

Figure 8. I<sup>2</sup>C Data Transfer Overview

Assume that a system power supply of 3.3V is applied to V<sub>CC</sub> and a super cap is connected to V<sub>BACKUP</sub>. Also assume the trickle charger has been enabled with a diode and resistor R2 between V<sub>CC</sub> and V<sub>BACKUP</sub>. The maximum current I<sub>MAX</sub> would therefore be calculated as follows:

$I_{MAX} = (3.3V \text{ - diode drop}) \ / \ \text{R2} \approx (3.3V \text{ - } 0.7V) \ / \ 2k\Omega \approx 1.3 \text{mA}$

As the super cap changes, the voltage drop between  $V_{CC}$  and  $V_{BACKUP}$  decreases and therefore the charge current decreases.

#### I<sup>2</sup>C Serial Data Bus

The DS1374 supports the I<sup>2</sup>C bus protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data is a receiver. The device that controls the message is called a master. The devices that are controlled by the master are slaves. A master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions must control the bus. The DS1374 operates as a slave on the I<sup>2</sup>C bus. Connections to the bus are made through the open-drain I/O lines SDA and SCL. A standard mode (100kHz max clock rate) and a fast mode (400kHz max clock rate) are defined within the bus specifications. The DS1374 works in both modes.

The following bus protocol has been defined (Figure 8):

- Data transfer can be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is high. Changes in the

#### data line while the clock line is high can be interpreted as control signals.

Accordingly, the following bus conditions have been defined:

**Bus not busy:** Both data and clock lines remain high.

**Start data transfer:** A change in the state of the data line from high to low, while the clock line is high, defines a START condition.

**Stop data transfer:** A change in the state of the data line from low to high, while the clock line is high, defines a STOP condition.

**Data valid:** The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the high period of the clock signal. The data on the line must be changed during the low period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between the START and the STOP conditions is not limited, and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit. A standard mode (100kHz clock rate) and a fast mode (400kHz clock rate) are defined within the I<sup>2</sup>C bus specifications.

**Acknowledge:** Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit.

| SLAVE<br>ADDRESS                                                                 | R/M |        | STER<br>ESS (n) |   | DATA (n) |                                               | DATA (n + 1) |   | DATA (n + x) |   |  |

|----------------------------------------------------------------------------------|-----|--------|-----------------|---|----------|-----------------------------------------------|--------------|---|--------------|---|--|

| S 1101000                                                                        | 0   | A XXXX | XXXX            | А | XXXXXXXX | А                                             | XXXXXXXX     | А | XXXXXXXX     | Р |  |

| S - START<br>A - ACKNOWLEDGE<br>P - STOP<br>R/₩ - READ/WRITE OR<br>DIRECTION BIT |     |        |                 |   |          | DATA TRANSFERRED<br>(X+1 Bytes + Acknowledge) |              |   |              |   |  |

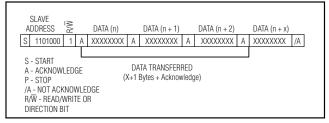

Figure 9. I<sup>2</sup>C Write Protocol

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable low during the high period of the acknowledge-related clock pulse. Setup and hold times must be considered. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line high to enable the master to generate the STOP condition.

Figures 9 and 10 detail how data transfer is accomplished on the 2-wire bus. Depending on the state of the R/W bit, two types of data transfer are possible:

Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte.

Data transfer from a slave transmitter to a master receiver. The master transmits the first byte (the slave address). The slave then returns an acknowledge bit. Next follows a number of data bytes transmitted by the slave to the master. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a "not acknowledge" is returned.

The master device generates the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus is not released.

The DS1374 can operate in the following two modes:

**Slave Receiver Mode (Write Mode):** Serial data and clock data are received through SDA and SCL. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware

Figure 10. I<sup>2</sup>C Read Protocol

after reception of the slave address and direction bit. The slave address byte is the first byte received after the master generates a START condition. The slave address byte contains the 7-bit DS1374 address, which is 1101000, followed by the direction bit  $(R/\overline{W})$ , which is zero for a write. After receiving and decoding the slave address byte, the DS1374 outputs an acknowledge on SDA. After the DS1374 acknowledges the slave address + write bit, the master transmits a register address to the DS1374. This sets the register pointer on the DS1374, with the DS1374 acknowledging the transfer. The master can then transmit zero or more bytes of data, with the DS1374 acknowledging each byte received. The register pointer increments after each data byte is transferred. The master generates a STOP condition to terminate the data write.

Slave Transmitter Mode (Read Mode): The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit indicates that the transfer direction is reversed. Serial data is transmitted on SDA by the DS1374, while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit. The slave address byte is the first byte received after the START condition is generated by the master. The slave address byte contains the 7-bit DS1374 address, which is 1101000, followed by the direction bit (R/W), which is 1 for a read. After receiving and decoding the slave address byte, the DS1374 outputs an acknowledge on SDA. The DS1374 then begins to transmit data starting with the register address pointed to by the register pointer. If the register pointer is not written to before the initiation of a read mode, the first address that is read is the last one stored in the register pointer. The DS1374 must receive a not acknowledge to end a read.

#### Handling, PC Board Layout, and Assembly

The DS1374C package contains a quartz tuning-fork crystal. Pick-and-place equipment can be used, but precautions should be taken to ensure that excessive shocks are avoided. Ultrasonic cleaning should be avoided to prevent damage to the crystal.

Avoid running signal traces under the package, unless a ground plane is placed between the package and the signal line. All no connect (N.C.) pins must be connected to ground.

The SO package can be reflowed as long as the peak temperature does not exceed 240°C. Peak reflow temperature (≥ 230°C) duration should not exceed 10 seconds, and the total time above 200°C should not exceed 40 seconds (30 seconds nominal). Exposure to reflow is limited to 2 times maximum.

Moisture-sensitive packages are shipped from the factory dry-packed. Handling instructions listed on the package label must be followed to prevent damage during reflow. Refer to the IPC/JEDEC J-STD-020B standard for moisture-sensitive device (MSD) classifications.

#### **Chip Information**

TRANSISTOR COUNT: 11,036 PROCESS: CMOS SUBSTRATE CONNECTED TO GROUND

#### **Thermal Information**

Theta-JA: 221°C/W (µSOP) Theta-JC: 39°C/W (µSOP) Theta-JA: 73°C/W (16 SO) Theta-JC: 23°C/W (16 SO)

## Package Information

(For the latest package outline information, go to www.maxim-ic.com/DallasPackInfo.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

15

**MAXIM** is a registered trademark of Maxim Integrated Products. Printed USA

© 2004 Maxim Integrated Products

DALLAS is a registered trademark of Dallas Semiconductor Corporation.