### Small engine management IC

Order now

**Technical** documents

**Family**

RoHS

### **Features**

- Power supplies

- Voltage pre-regulator with external FET

- 5 V sensor supply (tracking 5 V supply input)

- 5 V communication supply (tracking 5 V supply input)

- Permanent supply feature

- dedicated KEY input

- After-run functionality

- 4 low side drivers for inductive loads with overtemperature and overcurrent protection and open load/short to GND in off diagnosis

- 3 low-side power stages

- 1 low-side power stage with current measurement feature (O<sub>2</sub>-heater)

- Window watchdog module

- Serial Peripheral Interface (SPI)

- Green Product (RoHS compliant)

# **Potential applications**

All automotive applications, in particular

- Motorcycles, 2- and 3-wheelers and scooters

- Watercraft, marines and jet-skis

- Snow mobiles

### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

# **Description**

The TLE8082ES is a companion IC to TLE8080-xEM or TLE8088EM that includes enhanced functions and features to support OBDII-compliant EURO5/BHARATVI 2-/3-wheeler combustion engine systems with the focus on enhanced Electronic Fuel Injection (EFI) technologies.

It is protected against overtemperature and overcurrent and provides diagnostic features for each integrated power stage. The TLE8082ES integrates a pre-regulator for external FETs, a sensor supply, a communication supply for on-board transceivers, an SPI interface and four power stages to drive different load types used in engine management systems.

The IC is a compact and cost optimized solution to meet modern emission standards and regulations of engine management systems.

# Small engine management IC

# Description

| Product type | Package     | Marking   |

|--------------|-------------|-----------|

| TLE8082ES    | PG-TSDSO-24 | TLE8082ES |

# Small engine management IC

# Table of contents

# **Table of contents**

|                          | Features                                      | 1  |

|--------------------------|-----------------------------------------------|----|

|                          | Potential applications                        | 1  |

|                          | Product validation                            | 1  |

|                          | Description                                   | 1  |

|                          | Table of contents                             | 3  |

| 1                        | Block diagram                                 | 6  |

| 2                        | Pin configuration                             | 7  |

| 3                        | General product characteristics               | q  |

| 3.1                      | Maximum ratings                               |    |

| 3.2                      | Electrostatic Discharge Robustness            |    |

| 3.3                      | Thermal resistance                            |    |

| 3.4                      | Functional range                              |    |

|                          |                                               |    |

| 4                        | Operation behavior                            |    |

| 4.1                      | Operation states                              |    |

| 4.1.1                    | State diagram                                 |    |

| 4.1.2                    | Sleep state                                   |    |

| 4.1.3                    | Wake-up state                                 |    |

| 4.1.4                    | Power on reset (POR) state                    |    |

| 4.1.5                    | Normal operation watchdog (WD) inactive state |    |

| 4.1.6                    | Normal operation watchdog (WD) safe state     |    |

| 4.1.7                    | Normal operation watchdog (WD) ready state    |    |

| 4.1.8                    | Afterrun watchdog (WD) ready state            |    |

| 4.1.9                    | Afterrun watchdog (WD) safe state             |    |

| 4.1.10                   | External reset state                          |    |

| 4.1.11                   | Error state                                   |    |

| 4.1.12                   | Reset timer state                             |    |

| 4.2<br>4.2.1             | Power On reset                                |    |

| 4.2.1<br>4.2.2           | External reset (NRIO)                         |    |

| 4.2.2<br>4.2.3           | V5VI undervoltage reset                       |    |

| 4.2.3<br>4.2.4           | Watchdog reset function                       |    |

| 4.2. <del>4</del><br>4.3 | Key detection                                 |    |

| 4.3<br>4.4               | Electrical characteristics operation behavior |    |

|                          | ·                                             |    |

| 5                        | Power supply and voltage monitoring function  |    |

| 5.1                      | Supply functions                              |    |

| 5.1.1                    | V5VI supply input                             |    |

| 5.1.2                    | Charge pump                                   | 23 |

# Small engine management IC

# Table of contents

| 5.1.3  | 6.5V Pre-regulator with external MOSFET                |

|--------|--------------------------------------------------------|

| 5.1.4  | 5 V Sensor supply                                      |

| 5.1.5  | 5 V Communication supply                               |

| 5.2    | Voltage monitoring                                     |

| 5.3    | Overtemperature protection                             |

| 5.3.1  | T5V Overtemperature monitoring                         |

| 5.3.2  | COM5V Overtemperature monitoring                       |

| 5.4    | Electrical characteristics power supplies              |

| 6      | <b>Watchdog</b>                                        |

| 6.1    | Watchdog period                                        |

| 6.2    | Trigger of the watchdog - watchdog (WD) command        |

| 6.3    | Watchdog operation and error definition                |

| 6.4    | Watchdog state machine                                 |

| 6.5    | Watchdog error counter                                 |

| 6.6    | Electrical characteristics watchdog                    |

| 7      | <b>Power stages</b>                                    |

| 7.1    | Outputs 1 to 3 - inductive load drivers                |

| 7.2    | Output 4 - O2 heater driver                            |

| 7.3    | Protection and diagnosis of low-side output stages     |

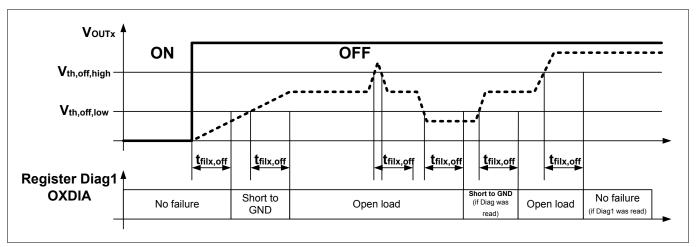

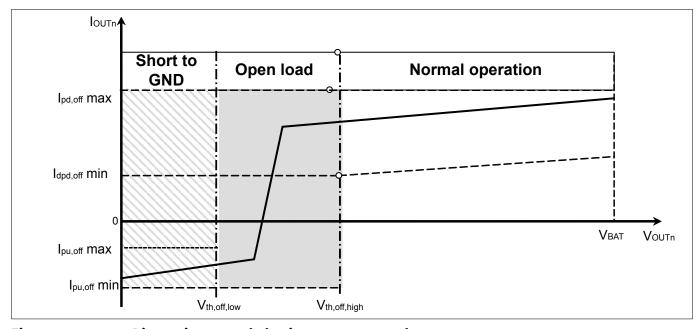

| 7.3.1  | Diagnosis in OFF-state                                 |

| 7.3.2  | Priority of diagnosis bit setting                      |

| 7.4    | Electrical characteristics power stages                |

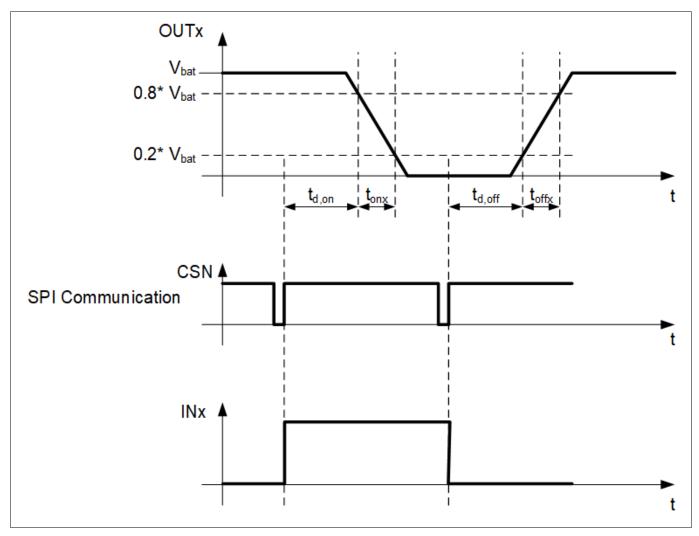

| 7.5    | Switching time definition                              |

| 8      | Inputs and outputs                                     |

| 8.1    | Electrical characteristics inputs and outputs          |

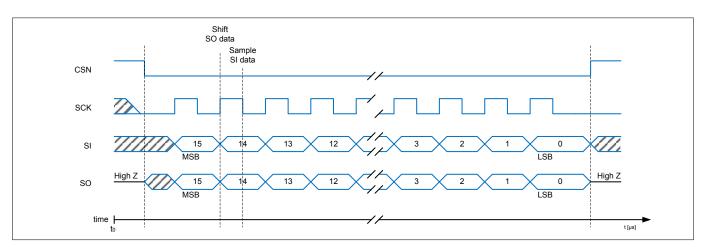

| 9      | Serial Peripheral Interface (SPI)                      |

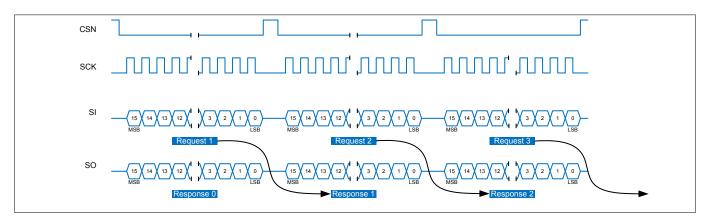

| 9.1    | Parallel SPI operation together with TLE8080ES         |

| 9.2    | SPI mode definition                                    |

| 9.3    | SPI data frame                                         |

| 9.4    | SPI send and response scheme                           |

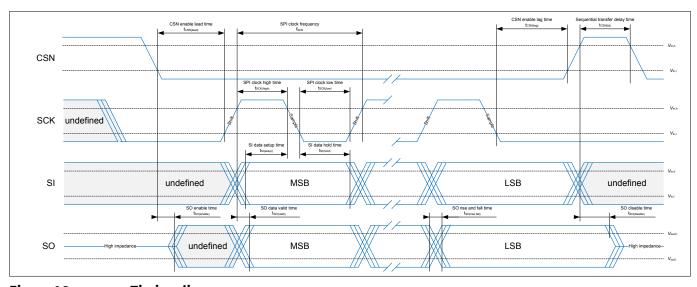

| 9.5    | SPI timing diagram                                     |

| 9.6    | Electrical characteristics SPI                         |

| 10     | <b>Registers</b>                                       |

| 10.1   | Register Overview - TLE8082 (ascending Offset Address) |

| 10.1.1 | Control Register Test                                  |

| 10.1.2 | General Diagnosis Register                             |

| 10.1.3 | Output Stage Diagnosis Register 53                     |

| 10.1.4 | Watchdog Register                                      |

| 10.1.5 | Configuration Register                                 |

| 11     | Application information                                |

# Small engine management IC

# Table of contents

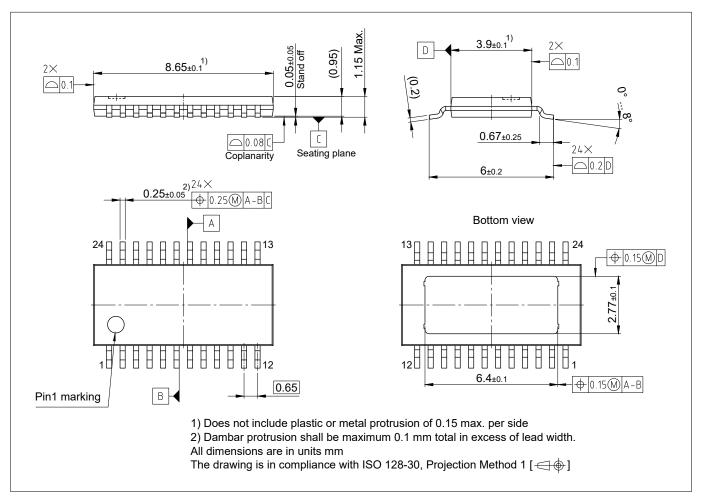

| 12 | Package information | 59 |

|----|---------------------|----|

|    | Revision history    | 60 |

|    | Disclaimer          | გ1 |

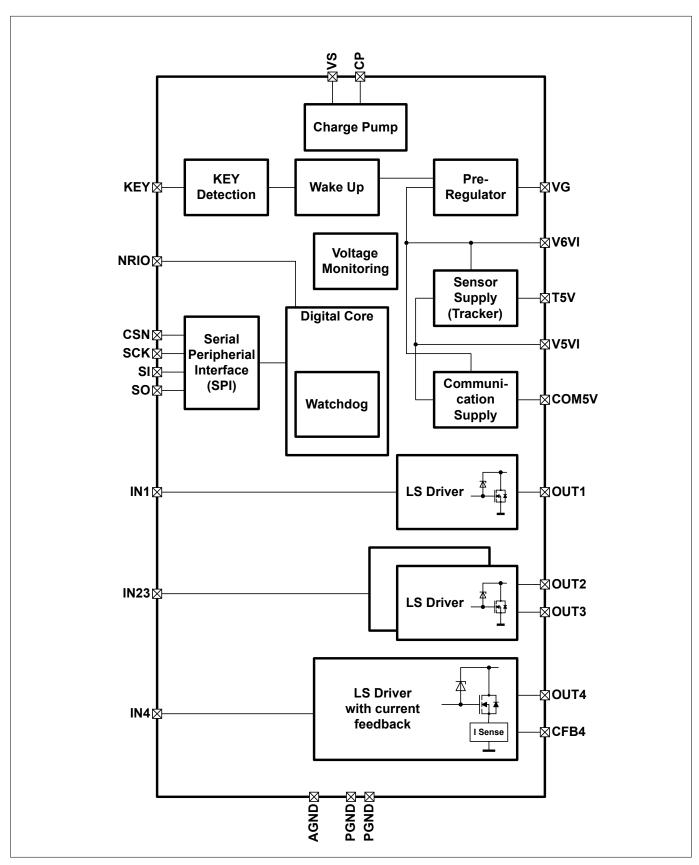

**Block diagram**

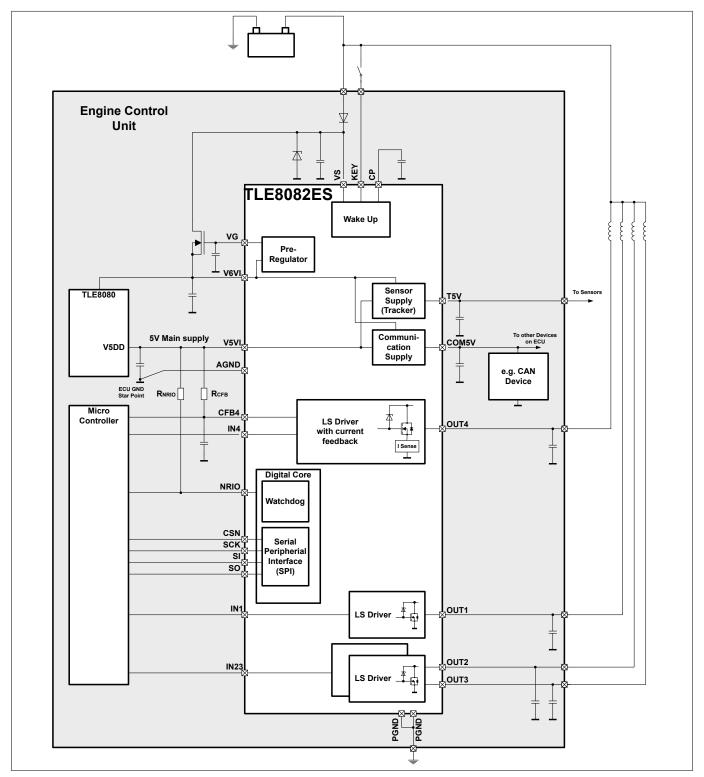

# 1 Block diagram

Figure 1 Block diagram

### **Small engine management IC**

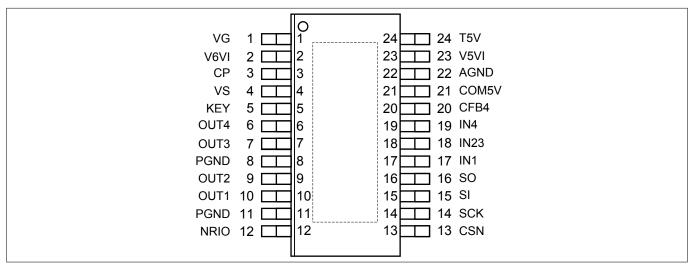

**Pin configuration**

# 2 Pin configuration

Figure 2 Pin configuration

Table 1 Pin definition and functions

| Pin# | Pin name | Function | Description                                                                                                                                       |

|------|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VG       | OUT      | <b>Control Output of Pre-Regulator:</b> connect gate of external MOSFET, add external capacitor                                                   |

| 2    | V6VI     | IN       | <b>Pre-Regulator Control Input:</b> connect source of external MOSFET, supply input for sensor and communication supplies, add external capacitor |

| 3    | СР       | OUT      | Charge-Pump Output: add external capacitor                                                                                                        |

| 4    | VS       | IN       | Battery Supply Input                                                                                                                              |

| 5    | KEY      | IN       | KEY Input                                                                                                                                         |

| 6    | OUT4     | OUT      | Low-Side Power Stage 4                                                                                                                            |

| 7    | OUT3     | OUT      | Low-Side Power Stage 3                                                                                                                            |

| 8    | PGND     | GND      | Power Ground: connect to cooling tab, must be connected externally                                                                                |

| 9    | OUT2     | OUT      | Low-Side Power Stage 2                                                                                                                            |

| 10   | OUT1     | OUT      | Low-Side Power Stage 1                                                                                                                            |

| 11   | PGND     | GND      | Power Ground: connect to cooling tab, must be connected externally                                                                                |

| 12   | NRIO     | IN/OUT   | Reset Input/Output: open drain low active, add pull up resistor                                                                                   |

| 13   | CSN      | IN       | SPI Slave Chip Select Input                                                                                                                       |

| 14   | SCK      | IN       | SPI Slave Clock Input                                                                                                                             |

| 15   | SI       | IN       | SPI Slave Data Input                                                                                                                              |

| 16   | SO       | OUT      | SPI Slave Data Output                                                                                                                             |

| 17   | IN1      | IN       | Control Input of Power Stage 1                                                                                                                    |

| 18   | IN23     | IN       | Control Input of Power Stage 2 and 3                                                                                                              |

| 19   | IN4      | IN       | Control Input of Power Stage 4                                                                                                                    |

# Small engine management IC

# Pin configuration

### Table 1 Pin definition and functions (continued)

| Pin# | Pin name | Function | Description                                                                           |

|------|----------|----------|---------------------------------------------------------------------------------------|

| 20   | CFB4     | OUT      | <b>Current Feedback Output of Power Stage 4</b>                                       |

| 21   | COM5V    | OUT      | 5 V Communication Supply Output: add external capacitor                               |

| 22   | AGND     | GND      | Signal Ground                                                                         |

| 23   | V5VI     | IN       | <b>5 V Main Supply Input:</b> reference voltage for sensor and communication supplies |

| 24   | T5V      | OUT      | 5 V Sensor Supply Output: add external capacitor                                      |

### **Small engine management IC**

**General product characteristics**

# **3** General product characteristics

# 3.1 Maximum ratings

### Table 2 Maximum ratings

$T_J$  = -40°C to 150°C; all voltages with respect to AGND = PGND, positive current flowing into pin (unless otherwise specified).

| Parameter                                          | Symbol                | Values |      |      | Unit | Note or condition                                                                                                                                | P-Number |

|----------------------------------------------------|-----------------------|--------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                    |                       | Min.   | Тур. | Max. |      |                                                                                                                                                  |          |

| Battery<br>supply pin VS                           | V <sub>VS,mr</sub>    | -0.3   | -    | 40   | V    |                                                                                                                                                  | DS-34    |

| Charge pump<br>pin CP                              | V <sub>CP,mr</sub>    | -0.3   | _    | 40   | V    | In addition, the maximum ratings parameter <b>Charge pump pin CP to pin VS</b> must be observed.                                                 | DS-35    |

| Charge pump<br>pin CP to pin<br>VS                 | V <sub>CP_VS,mr</sub> | -0.3   | _    | 6    | V    | $V_{\text{CP\_VS,mr}} = V_{\text{CP}} - V_{\text{VS}}$<br>In addition, the maximum ratings parameter <b>Charge pump pin CP</b> must be observed. | DS-36    |

| Key<br>detection<br>input pin KEY                  | V <sub>KEY,mr</sub>   | -0.3   | _    | 40   | V    |                                                                                                                                                  | DS-37    |

| Preregulator gate output pin VG                    | $V_{ m VG,mr}$        | -0.3   | _    | 40   | V    | In addition, the maximum ratings parameter <b>Preregulator gate output pin VG to pin CP</b> must be observed.                                    | DS-38    |

| Preregulator<br>gate output<br>pin VG to pin<br>CP | V <sub>VG_CP,mr</sub> | -40    | _    | 0.3  | V    | V <sub>VG_CP,mr</sub> = V <sub>VG_VCP</sub> In addition, the maximum ratings parameter <b>Preregulator gate output pin VG</b> must be observed.  | DS-40    |

| 6V input pin<br>V6VI                               | V <sub>V6VI,mr</sub>  | -0.3   | -    | 40   | V    |                                                                                                                                                  | DS-41    |

| Sensor<br>supply<br>output pin<br>T5V              | V <sub>T5V,mr</sub>   | -1     | _    | 40   | V    |                                                                                                                                                  | DS-42    |

| 5V supply input V5VI                               | V <sub>V5VI,mr</sub>  | -0.3   | -    | 5.5  | V    |                                                                                                                                                  | DS-43    |

| Analog<br>ground pin<br>AGND                       | $V_{AGND,mr}$         | -0.3   | _    | 0.3  | V    | related to PGND                                                                                                                                  | DS-44    |

| Communicati<br>on supply<br>output<br>COM5V        | V <sub>COM5V,mr</sub> | -0.3   | _    | 5.5  | V    |                                                                                                                                                  | DS-45    |

### **Small engine management IC**

### **General product characteristics**

#### **Maximum ratings (continued)** Table 2

$T_J = -40$ °C to 150°C; all voltages with respect to AGND = PGND, positive current flowing into pin (unless otherwise specified).

| Parameter                                | Symbol                  | Values |      |      | Unit | Note or condition                                                                                                                         | P-Number |

|------------------------------------------|-------------------------|--------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                          |                         | Min.   | Тур. | Мах. |      |                                                                                                                                           |          |

| Current<br>feedback<br>ouput pin<br>CFB4 | V <sub>CFB4,mr</sub>    | -0.3   | _    | 5.5  | V    |                                                                                                                                           | DS-46    |

| Direct input<br>pin IN1                  | V <sub>IN1,mr</sub>     | -0.3   | -    | 5.5  | V    |                                                                                                                                           | DS-47    |

| Direct drive<br>input pin<br>IN23        | V <sub>IN23,mr</sub>    | -0.3   | _    | 5.5  | V    |                                                                                                                                           | DS-264   |

| Direct drive input pin IN4               | V <sub>IN4,mr</sub>     | -0.3   | -    | 5.5  | V    |                                                                                                                                           | DS-48    |

| SPI output<br>pin SO                     | V <sub>SO,mr</sub>      | -0.3   | -    | 5.5  | V    | In addition, the maximum ratings parameter <b>SPI output pin SO to pin V5VI</b> must be observed.                                         | DS-49    |

| SPI output<br>pin SO to pin<br>V5VI      | V <sub>SO,V5VI,mr</sub> | -5.5   | -    | 0.3  | V    | $V_{\rm SO,V5VI,mr} = V_{\rm SO} - V_{\rm V5VI}$<br>In addition, the maximum ratings parameter <b>SPI output pin SO</b> must be observed. | DS-266   |

| SPI input pin                            | V <sub>SI,mr</sub>      | -0.3   | -    | 5.5  | V    |                                                                                                                                           | DS-50    |

| SPI clock<br>input pin SCK               | V <sub>SCK,mr</sub>     | -0.3   | -    | 5.5  | V    |                                                                                                                                           | DS-51    |

| SPI chip<br>select input<br>pin CSN      | V <sub>CSN,mr</sub>     | -0.3   | -    | 5.5  | V    |                                                                                                                                           | DS-52    |

| Reset input<br>output pin<br>NRIO        | V <sub>NRIO,mr</sub>    | -0.3   | -    | 5.5  | V    |                                                                                                                                           | DS-53    |

| Power stage output OUT1                  | V <sub>OUT1,mr</sub>    | -0.3   | -    | 50   | V    | repetitive clamping allowed                                                                                                               | DS-54    |

| Power stage output OUT2                  | V <sub>OUT2,mr</sub>    | -0.3   | -    | 50   | V    | repetitive clamping allowed                                                                                                               | DS-55    |

| Power stage output OUT3                  | V <sub>OUT3,mr</sub>    | -0.3   | -    | 35   | V    | repetitive clamping allowed                                                                                                               | DS-56    |

| Power stage output OUT4                  | V <sub>OUT4,mr</sub>    | -0.3   | -    | 35   | V    | repetitive clamping allowed                                                                                                               | DS-57    |

Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute Note:

### **Small engine management IC**

### **General product characteristics**

Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

### 3.2 Electrostatic Discharge Robustness

### Table 3 Electrostatic Discharge Robustness

| Parameter                                   | Symbol               | Values |      |      | Unit | Note or condition                                                                                 | P-Number |

|---------------------------------------------|----------------------|--------|------|------|------|---------------------------------------------------------------------------------------------------|----------|

|                                             |                      | Min.   | Тур. | Max. | 1    |                                                                                                   |          |

| HBM ESD<br>robustness<br>for global<br>pins | $V_{HBM,glo}$        | -4     | _    | 4    | kV   | acc. ANSI/ESDA/JEDEC JS-001 (1.5 k $\Omega$ , 100 pF) for pins VS, V6VI, T5V, KEY, OUT1-4 to PGND | DS-58    |

| HBM ESD<br>robustness<br>for local pins     | $V_{HBM,loc}$        | -2     | -    | 2    | kV   | acc. ANSI/ESDA/JEDEC JS-001 (1.5 k $\Omega$ , 100 pF) remaining pins                              | DS-59    |

| CDM ESD robustness corner pins              | V <sub>CDM,cor</sub> | -750   | _    | 750  | V    | acc. JESD22-C101<br>corner pins 1, 12, 13, 24                                                     | DS-60    |

| CDM ESD<br>robustness<br>remaining<br>pins  | $V_{CDM}$            | -500   | _    | 500  | V    | acc. JESD22-C101 remaining pins                                                                   | DS-61    |

Note:

A "local" pin carries a signal or power which does not leave the application board. It remains on the application PCB as a signal between two components.

A "global" pin carries a signal or power which enters or leaves the application board without any active component in between.

### 3.3 Thermal resistance

### Table 4 Thermal resistance

| Parameter                           | Symbol              | Values |      |      | Unit | Note or condition | P-Number |

|-------------------------------------|---------------------|--------|------|------|------|-------------------|----------|

|                                     |                     | Min.   | Тур. | Max. |      |                   |          |

| Thermal resistance junction to case | R <sub>th,j-c</sub> | -      | 1.3  | 1.5  | K/W  |                   | DS-288   |

# Small engine management IC

# **General product characteristics**

# 3.4 Functional range

### Table 5 Functional range

| Parameter                                            | Symbol              | Values |      |      | Unit | Note or condition | P-Number |

|------------------------------------------------------|---------------------|--------|------|------|------|-------------------|----------|

|                                                      |                     | Min.   | Тур. | Max. |      |                   |          |

| Supply<br>voltage in<br>normal<br>operation<br>range | $V_{ m VS,nop}$     | 6      | -    | 40   | V    |                   | DS-62    |

| Supply<br>voltage in<br>low battery<br>condition     | V <sub>VS,low</sub> | 3.5    | _    | 6    | V    |                   | DS-63    |

| Operating temperature range                          | T <sub>J</sub>      | -40    | _    | 150  | °C   |                   | DS-64    |

| Storage<br>temperature<br>range                      | $T_{ m stg}$        | -55    | _    | 150  | °C   |                   | DS-65    |

**Operation behavior**

# 4 Operation behavior

### 4.1 Operation states

The TLE8082ES implements 11 operations states:

- Sleep state

- Wake-up state

- · Power on reset (POR) state

- Normal operation watchdog (WD) inactive state

- Normal operation watchdog (WD) safe state

- Normal operation watchdog (WD) ready state

- Afterrun watchdog safe state

- · Afterrun watchdog ready state

- External reset state

- Error state and

- Reset timer state

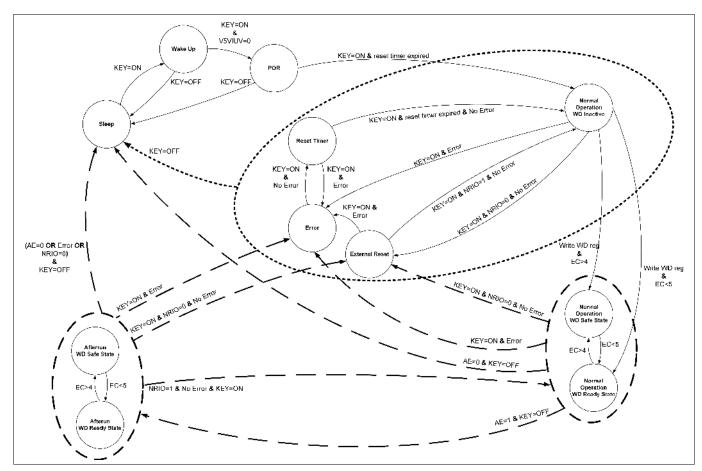

# 4.1.1 State diagram

The state diagram is valid for VS voltage levels above the **VS reset threshold** (see DS-278 and DS-279). The device starts in sleep mode after power up.

Figure 3 Operation state diagram

### **Small engine management IC**

### **Operation behavior**

Table 6 State diagram terms and descriptions

| Term              | Description                                          |

|-------------------|------------------------------------------------------|

| KEY               | Key on detection, see <i>Chapter 4.3</i>             |

|                   | ON: high voltage level at pin KEY                    |

|                   | OFF: low voltage level at pin KEY                    |

| V5VIUV            | 5 V undervoltage detection at pin V5VI               |

|                   | Diag0.V5VIUV = 0: voltage in operational range       |

|                   | Diag0.V5VIUV = 1: undervoltage at pin V5VI           |

| AE                | Afterrun setting                                     |

|                   | Config.AE = 0: afterrun disabled                     |

|                   | Config.AE = 1: afterrun enabled                      |

| NRIO              | logic status of NRIO pin                             |

|                   | NRIO = 0: logic low level                            |

|                   | NRIO = 1: logic high level                           |

| Write WD register | SPI write access to watchdog register                |

| Watchdog reset    | see Chapter 4.2.4                                    |

| Error             | watchdog reset OR Diag0.V5VIUV = 1 (boolean OR)      |

| No error          | no watchdog reset AND Diag0.V5VIUV = 0 (boolean AND) |

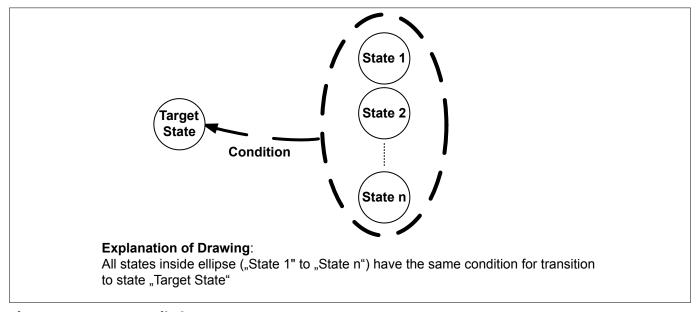

Figure 4 Detailed states movement

### **Small engine management IC**

**Operation behavior**

### 4.1.2 Sleep state

In the Sleep state, the TLE8082ES is inactive. The current consumption in Sleep state at pin VS is **VS sleep current**.

Table 7 Sleep state

| Function                                                   | Status           | Note                         |  |

|------------------------------------------------------------|------------------|------------------------------|--|

| Pre-regulator; 5 V Sensor supply, 5 V Communication supply | disabled         | no internal supply available |  |

| Power stages                                               | disabled         |                              |  |

| SPI                                                        | no communication |                              |  |

| Register                                                   | reset            |                              |  |

| Watchdog                                                   | reset            |                              |  |

| Key input pin KEY                                          | low              | driven from outside          |  |

| Reset output pin NRIO                                      | not defined      | no internal supply available |  |

### **Small engine management IC**

### **Operation behavior**

### 4.1.3 Wake-up state

In the Wake-up state, all function of the TLE8082ES are ramping up.

### Table 8 Wake-up state

| Function                                                   | Status           | Note                                                                        |  |

|------------------------------------------------------------|------------------|-----------------------------------------------------------------------------|--|

| Pre-regulator, 5 V Sensor supply, 5 V Communication supply | ramp up          | Sensor and communication supply referring to voltage at pin V5VI            |  |

| Power stages                                               | disabled         |                                                                             |  |

| SPI                                                        | no communication |                                                                             |  |

| Register                                                   | reset            |                                                                             |  |

| Key input pin KEY                                          | high             | driven from outside                                                         |  |

| Reset output pin NRIO                                      | active low       | after V5VI supply ramp up;<br>pull down transistor driven by V5VI<br>supply |  |

# 4.1.4 Power on reset (POR) state

In the POR state, the pin NRIO is kept low for the **Power On reset time**.

### Table 9 POR state

| Function                                                      | Status           | Note  output voltage according to Electrical characteristics external supplies (see <i>Table 19</i> ) |  |

|---------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------|--|

| Pre-regulator, 5 V Sensor supply, 5 V<br>Communication supply | ramped up        |                                                                                                       |  |

| Power stages                                                  | disabled         |                                                                                                       |  |

| SPI                                                           | no communication |                                                                                                       |  |

| Register                                                      | reset            |                                                                                                       |  |

| Watchdog                                                      | reset            |                                                                                                       |  |

| Key input pin KEY                                             | high             | driven from outside                                                                                   |  |

| Reset output pin NRIO                                         | active low       | pull down transistor driven by V5VI supply                                                            |  |

### **Small engine management IC**

**Operation behavior**

### 4.1.5 Normal operation watchdog (WD) inactive state

In the Normal operation WD inactive state, all functions are working according to their definitions.

Table 10 Normal Operation WD inactive state

| Function                                                   | Status                                                                                          | Note                |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------|--|

| Pre-regulator, 5 V Sensor supply, 5 V Communication supply | output voltage according to Electrical characteristics external supplies (see <i>Table 19</i> ) |                     |  |

| Power stages                                               | disabled                                                                                        |                     |  |

| SPI                                                        | communication enabled                                                                           |                     |  |

| Register                                                   | normal access                                                                                   |                     |  |

| Watchdog                                                   | waiting for watchdog command                                                                    |                     |  |

| Key input pin KEY                                          | high                                                                                            | driven from outside |  |

| Reset output pin NRIO                                      | high                                                                                            |                     |  |

### 4.1.6 Normal operation watchdog (WD) safe state

In the Normal operation WD safe state, all functions are working according to their definitions.

Table 11 Normal operation WD safe state

| Function                                                   | Status                                                                                          | Note                |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------|--|

| Pre-regulator, 5 V Sensor supply, 5 V Communication supply | output voltage according to Electrical characteristics external supplies (see <i>Table 19</i> ) |                     |  |

| Power stages                                               | disabled                                                                                        |                     |  |

| SPI                                                        | communication enabled                                                                           |                     |  |

| Register                                                   | normal access                                                                                   |                     |  |

| Watchdog                                                   | watchdog period running, EC>4                                                                   |                     |  |

| Key input pin KEY                                          | high                                                                                            | driven from outside |  |

| Reset output pin NRIO                                      | high                                                                                            |                     |  |

### **Small engine management IC**

**Operation behavior**

### 4.1.7 Normal operation watchdog (WD) ready state

In the Normal operation WD ready state, all functions are working according to their definitions.

Table 12 Normal operation WD ready state

| Function                                                   | Status                                                                                          | Note                |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------|--|

| Pre-regulator, 5 V Sensor supply, 5 V Communication supply | output voltage according to Electrical characteristics external supplies (see <i>Table 19</i> ) |                     |  |

| Power stages                                               | controlled by microcontroller                                                                   |                     |  |

| SPI                                                        | communication enabled                                                                           |                     |  |

| Register                                                   | normal access                                                                                   |                     |  |

| Watchdog                                                   | watchdog period running, EC<5                                                                   |                     |  |

| Key input pin KEY                                          | high                                                                                            | driven from outside |  |

| Reset output pin NRIO                                      | output pin NRIO high                                                                            |                     |  |

### 4.1.8 Afterrun watchdog (WD) ready state

In the Afterrun WD ready state state, all functions are working according to their definitions. The only difference to the Normal operation states is that ramp down is controlled by the microcontroller via SPI communication. The bit AE is set to "1".

Table 13 Afterrun WD ready state

| Function                                                   | Status                                                                                          | Note                |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------|--|

| Pre-regulator, 5 V Sensor supply, 5 V Communication supply | output voltage according to Electrical characteristics external supplies (see <i>Table 19</i> ) |                     |  |

| Power stages                                               | controlled by microcontroller                                                                   |                     |  |

| SPI                                                        | communication enabled                                                                           |                     |  |

| Register                                                   | normal access                                                                                   |                     |  |

| Watchdog                                                   | watchdog period running, EC<5                                                                   |                     |  |

| Key input pin KEY                                          | low                                                                                             | driven from outside |  |

| Reset output pin NRIO                                      | high                                                                                            |                     |  |

### **Small engine management IC**

**Operation behavior**

### 4.1.9 Afterrun watchdog (WD) safe state

In the Afterrun WD safe state, all functions are working according to their definitions. The only difference to the Normal operation states is that ramp down is controlled by the microcontroller via SPI communication. The bit AE is set to "1".

Table 14 Afterrun WD safe state

| Function                                                   | Status                                                                                          | Note                |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------|--|

| Pre-regulator, 5 V Sensor supply, 5 V Communication supply | output voltage according to Electrical characteristics external supplies (see <i>Table 19</i> ) |                     |  |

| Power stages                                               | disabled                                                                                        |                     |  |

| SPI                                                        | communication enabled                                                                           |                     |  |

| Register                                                   | normal access                                                                                   |                     |  |

| Watchdog                                                   | dog watchdog period running, EC>4                                                               |                     |  |

| Key input pin KEY                                          | low                                                                                             | driven from outside |  |

| Reset output pin NRIO                                      | high                                                                                            |                     |  |

### 4.1.10 External reset state

If an external device requests a reset at the pin NRIO, the external reset state is entered.

Table 15 External reset state

| Function                                                   | Status                                                                                                     | Note                                             |  |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|

| Pre-regulator, 5 V Sensor supply, 5 V Communication supply | output voltage according to Electrical characteristics external supplies (see <i>Table 19</i> )            |                                                  |  |

| Power stages                                               | disabled                                                                                                   |                                                  |  |

| SPI                                                        | communication disabled                                                                                     |                                                  |  |

| Register                                                   | Diag 0 register bits V5VIUV, V5VIOV, WDRES, NRIORES according to the status of the device, remaining reset |                                                  |  |

| Watchdog                                                   | WD inactive state                                                                                          |                                                  |  |

| Key input pin KEY                                          | high                                                                                                       | driven from outside                              |  |

| Reset output pin NRIO                                      | low                                                                                                        | pull down transistor<br>driven by V5VI<br>supply |  |

### **Small engine management IC**

### **Operation behavior**

### 4.1.11 Error state

If an error of the system is detected, the error state is entered.

### Table 16 Error state

| Function                                                   | Status                                                                                          | Note                                             |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Pre-regulator, 5 V Sensor supply, 5 V Communication supply | output voltage according to Electrical characteristics external supplies (see <i>Table 19</i> ) |                                                  |

| Power stages                                               | disabled                                                                                        |                                                  |

| SPI                                                        | communication disabled                                                                          |                                                  |

| Register                                                   | Diag 0 register bits V5VIUV, V5VIOV, WDRES, NRIORES acc. status of the device, remaining reset  |                                                  |

| Watchdog                                                   | WD inactive state                                                                               |                                                  |

| Key input pin KEY                                          | high                                                                                            | driven from outside                              |

| Reset output pin NRIO                                      | active low                                                                                      | pull down transistor<br>driven by V5VI<br>supply |

### 4.1.12 Reset timer state

After all errors have been disappeared, the reset timer state is entered.

Table 17 Reset timer state

| Function                                                   | Status                                                                                          | Note                                             |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|--|

| Pre-regulator, 5 V Sensor supply, 5 V Communication supply | output voltage according to Electrical characteristics external supplies (see <i>Table 19</i> ) |                                                  |  |

| Power stages                                               | disabled                                                                                        |                                                  |  |

| SPI                                                        | communication disabled                                                                          |                                                  |  |

| Register                                                   | Diag 0 register bits V5VIUV, V5VIOV, WDRES, NRIORES acc. status of the device, remaining reset  |                                                  |  |

| Watchdog                                                   | WD inactive state                                                                               |                                                  |  |

| Key input pin KEY                                          | high                                                                                            | driven from outside                              |  |

| Reset output pin NRIO                                      | active low                                                                                      | pull down transistor<br>driven by V5VI<br>supply |  |

### Small engine management IC

### **Operation behavior**

#### 4.2 Reset

The TLE8082ES implements following resets:

- Power on reset

- Operation reset:

- external reset (NRIO)

- V5VI undervoltage reset

- watchdog reset

#### 4.2.1 **Power On reset**

After an internal and external V5VI supply ramp up, a power on reset (POR) is performed. The pin NRIO is kept low for **Power On reset time**.

The status of the device after a POR is described in **Chapter 4.1.4**.

#### 4.2.2 **External reset (NRIO)**

The pin NRIO is an input/output pin. The output consists of an open drain pull down transistor. The pull down transistor is supplied by the pin V5VI.

An external reset (NRIO externally pulled to low) can only be detected if the pin is internally not pulled low e.g. in error state (see Operation states).

An input filter for the low level detection at the pin NRIO is implemented to suppress disturbances. The filter time is **NRIO** input filter time. If an external reset is detected, the bit NRIORES in register DIAGO is set. The bit is cleared after an SPI readout.

#### 4.2.3 **V5VI undervoltage reset**

If an undervoltage according to V5VI Undervoltage monitoring (see Chapter 5.2) is detected, the pin NRIO is switched to low. After recovery, the pin NRIO is kept low for **Operation reset time**.

The device status is changed according to the definition in Operation states (see *Chapter 4.1*).

#### 4.2.4 Watchdog reset function

The watchdog reset is generated by the watchdog (see Chapter 6) and bit WDRES in register DIAGO is set. After readout of DIAGO the bit WDRES is reset. The pin NRIO is kept low for **Operation reset time**.

The status of the device is changed according to the Operation states (see *Chapter 4.1*).

#### 4.3 **Key detection**

The TLE8082ES implements a voltage detection function at the pin KEY.

An "ON" is detected with a voltage at pin KEY higher than **Key On detection threshold** for a time longer than **Key detection filter time.** The TLE8082ES starts working according to the description in Operation states (see **Chapter 4.1**).

An "OFF" is detected with a voltage at pin KEY lower than **Key On detection threshold** for a time longer than **Key detection filter time.** The TLE8082ES reacts according to the Operation states (see *Chapter 4.1*).

For noise suppression, a **Key On detection hysteresis** is implemented. The key on detection status is indicated by the bit KEY in register DIAGO.

### **Small engine management IC**

**Operation behavior**

# 4.4 Electrical characteristics operation behavior

### Table 18 Electrical characteristics operation behavior

$T_J$  = -40°C to 150°C;  $V_{VS}$  = 10 - 18 V;  $V_{V5VI}$  = 5 V; all voltages with respect to AGND = PGND, positive current flowing into pin (unless otherwise specified).

| Parameter Sy                                  | Symbol                   | Symbol Values |      | Unit | Note or condition | P-Number                                             |        |

|-----------------------------------------------|--------------------------|---------------|------|------|-------------------|------------------------------------------------------|--------|

|                                               |                          | Min.          | Тур. | Max. |                   |                                                      |        |

| Key On<br>detection<br>threshold -<br>rising  | V <sub>KEY,th,rise</sub> | 3.5           | -    | 4.5  | V                 |                                                      | DS-276 |

| Key On<br>detection<br>threshold -<br>falling | V <sub>KEY,th,fall</sub> | 2.5           | _    | 4.5  | V                 |                                                      | DS-277 |

| Key On<br>detection<br>hysteresis             | V <sub>KEY,hys</sub>     | 0.35          | -    | 1.5  | V                 |                                                      | DS-110 |

| Key input current                             | I <sub>KEY</sub>         | _             | -    | 200  | μΑ                | V <sub>KEY</sub> = 4.5 V                             | DS-111 |

| Key<br>detection<br>filter time               | t <sub>KEY,f</sub>       | 100           | -    | 500  | μѕ                |                                                      | DS-112 |

| VS sleep<br>current                           | I <sub>VS,sleep</sub>    | -             | -    | 0.5  | μΑ                | $V_{\rm VS}$ = 14 V, $T_{\rm j}$ = 25°C, sleep state | DS-113 |

| VS operation current                          | I <sub>VS,op</sub>       | _             | -    | 16   | mA                | V <sub>VS</sub> = 14 V                               | DS-292 |

| Power On reset time                           | $t_{\rm res,POR}$        | 10            | -    | 15   | ms                |                                                      | DS-114 |

| Operation reset time                          | t <sub>res,op</sub>      | 1             | -    | 2    | ms                |                                                      | DS-115 |

| NRIO input filter time                        | t <sub>fil,NRIO</sub>    | 8             | -    | 16   | μs                |                                                      | DS-116 |

| VS reset<br>threshold -<br>rising             | V <sub>VS,res,rise</sub> | 2             | _    | 4    | V                 |                                                      | DS-278 |

| VS reset<br>threshold -<br>falling            | V <sub>VS,res,fall</sub> | 2             | -    | 3.5  | V                 |                                                      | DS-279 |

### **Small engine management IC**

Power supply and voltage monitoring function

#### Power supply and voltage monitoring function 5

#### **Supply functions** 5.1

The TLE8082ES implements:

- one internal charge pump

- one pre-regulator controlling an external n-channel MOSFET

- one 5 V sensor supply with reverse supply protection

- one 5 V communication supply

#### 5.1.1 V5VI supply input

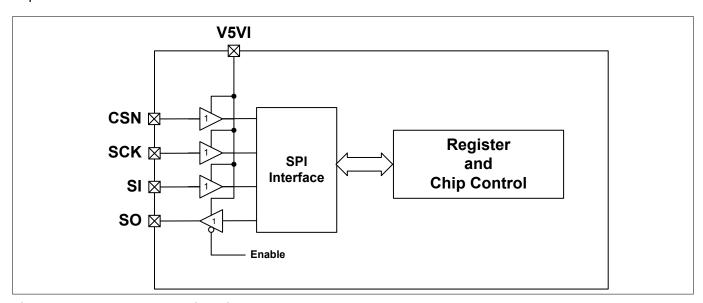

The V5VI supply input is used as reference voltage for the 5 V sensor and 5 V communication supply. Additionally, it supplies the SPI output buffer and power stage gate drivers.

The 5 V main supply of the electronic control unit (ECU) has to be connected to the pin V5VI.

#### 5.1.2 Charge pump

An internal charge pump is implemented for low drop operation. An external capacitor at CP pin must be connected to AGND.

#### 5.1.3 6.5V Pre-regulator with external MOSFET

The pre-regulator regulates the voltage at pin V6VI to **Pre-regulator output voltage** via the gate voltage of an external n-channel MOSFET. In normal operation, the maximum output level of pin VG is defined by Preregulator voltage drop VS to VG - normal operation and Pre-regulator delta voltage VG to VS - low battery.

The drain of the external MOSFET and the pin VS are connected to the same supply node, normally battery supply.

The function of the pre-regulator is verified with Infineon MOSFET IPD30N06S2L-23.

For stable operation and ripple reduction capacitors are recommended at pin V6VI, pin VG, and pin CP.

#### 5.1.4 5 V Sensor supply

The output T5V of the 5 V sensor supply follows the voltage level at pin V5VI. The sensor supply is supplied out of pin V6VI.

The output is protected against overload (e.g short to GND) and overtemperature. In case of an overcurrent, the output current is limited and the diagnosis bit is set. The diagnosis bit is cleared with a readout of register DIAGO if no overcurrent is present anymore.

The output is protected against reverse supply to pin V6VI.

The 5 V sensor supply is designed for low battery operation (see **Sensor supply low drop resistance**).

The 5 V sensor supply can be deactivated through SPI configuration of bit COM5VEN in the CONFIG register.

A capacitor at the pin T5V is recommended for stable operation and ripple reduction.

### **Small engine management IC**

Power supply and voltage monitoring function

### 5.1.5 5 V Communication supply

The output COM5V of the 5 V communication supply follows the voltage level at pin V5VI. The communication supply is supplied out of pin V6VI.

The output is protected against overload (e.g short to GND) and overtemperature. In case of an overcurrent, the output current is limited and the diagnosis bit is set. The diagnosis bit is cleared with a readout of register DIAGO if no overcurrent is present anymore.

The 5 V communication supply is designed for low battery operation (see **Communication supply low drop resistance**).

The 5 V communication supply can be deactivated through SPI configuration of bit T5VEN in the CONFIG register.

A capacitor, at the pin COM5V is recommended for stable operation and ripple reduction.

### 5.2 Voltage monitoring

The TLE8082ES implements an undervoltage detection and overvoltage detection at pins V5VI, T5V and COM5V. All undervoltage and overvoltage diagnosis bits are located in the register DIAG0.

The V5VI undervoltage detection monitors the pin V5VI. Two thresholds are implemented, one for rising voltages and one for falling voltages. For falling voltages the diagnosis bit is set if the voltage level is below the **V5VI Undervoltage detection threshold 2**. If the voltage level is above **V5VI Undervoltage detection threshold 1**, the diagnosis bit is reset after an SPI read out. An **Undervoltage detection filter time** is implemented. In case of an undervoltage, the V5VI undervoltage reset is triggered (see **Chapter 4.2**).

The V5VI overvoltage detection monitors the pin V5VI. For voltage levels above **V5VI Overvoltage detection threshold**, the diagnosis bit is set. If the voltage level is below the threshold, the diagnosis bit is reset after an SPI read out. An **Overvoltage detection hysteresis** and an **Overvoltage detection filter time** are implemented.

The T5V undervoltage detection monitors the pin T5V. For voltage levels below the **T5V Undervoltage detection threshold**, the diagnosis bit is set. If the voltage level is above the threshold, the diagnosis bit is reset after an SPI read out. An **Undervoltage detection hysteresis** and an **Undervoltage detection filter time** are implemented.

The T5V overvoltage detection monitors the pin T5V. For voltage levels above the **T5V Overvoltage detection threshold**, the diagnosis bit is set. If the voltage level is below the threshold, the diagnosis bit is reset after an SPI read out. An **Overvoltage detection hysteresis** and an **Overvoltage detection filter time** are implemented.

The COM5V undervoltage detection monitors the pin COM5V. For voltage levels below the **COM5V Undervoltage detection threshold** the diagnosis bit is set. If the voltage level is above the threshold, the diagnosis bit is reset after an SPI read out. An **Undervoltage detection hysteresis** and an **Undervoltage detection filter time** are implemented.

The COM5V overvoltage detection monitors the pin COM5V. For voltage levels above the **COM5V Overvoltage detection threshold** the diagnosis bit is set. If the voltage level is below the threshold, the diagnosis bit is reset after an SPI read out. An **Overvoltage detection hysteresis** and an **Overvoltage detection filter time** are implemented.

### **Small engine management IC**

Power supply and voltage monitoring function

### 5.3 Overtemperature protection

### 5.3.1 T5V Overtemperature monitoring

The T5V overtemperature monitoring protects the sensor supply T5V against high temperatures. For temperatures above the **T5V Overtemperature detection threshold**, the diagnosis bit T5VOT in register DIAG0 is set. If the temperature level is below the threshold, the diagnosis bit is reset after an SPI read out.

An Overtemperature detection hysteresis and an Overtemperature filter time are implemented.

### 5.3.2 COM5V Overtemperature monitoring

The COM5V overtemperature monitoring protects the communication supply COM5V against high temperatures. For temperatures above the **COM5V Overtemperature detection threshold**, the diagnosis bit COM5VOT in register DIAG0 is set. If the temperature level is below the threshold, the diagnosis bit is reset after an SPI read out.

An **Overtemperature detection hysteresis** and an **Overtemperature filter time** are implemented.

### 5.4 Electrical characteristics power supplies

### Table 19 Electrical characteristics power supplies

$T_J = -40$ °C to 150°C;  $V_{VS} = 10 - 18$  V;  $V_{V5VI} = 5$  V; all voltages with respect to AGND = PGND, positive current flowing into pin (unless otherwise specified).

| Parameter                                                          | Symbol             | l Values |      |      | Unit | Note or condition                                                                                                                                                           | P-Number |

|--------------------------------------------------------------------|--------------------|----------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                    |                    | Min.     | Тур. | Max. |      |                                                                                                                                                                             |          |

| Pre-regulator output voltage                                       | V <sub>V6VI</sub>  | 6        | 6.5  | 7    | V    |                                                                                                                                                                             | DS-155   |

| Pre-regulator<br>voltage drop<br>VS to VG -<br>normal<br>operation | V <sub>VS-VG</sub> | -        | -    | 2    | V    | $V_{VS} \ge 12 \text{ V}; V_{V6VI} < 6 \text{ V}$ $V_{VS-VG} = V_{VS} - V_{VG}$ capacitive load at pin VG                                                                   | DS-281   |

| Pre-regulator<br>delta voltage<br>VG to VS - low<br>battery        |                    | 3.5      | -    | -    | V    | $4.5 \text{ V} \le V_{\text{VS}} \le 12 \text{ V}; V_{\text{V6VI}} < 6 \text{ V}$<br>$\Delta V_{\text{VG-VS}} = V_{\text{VG}} - V_{\text{VS}}$<br>capacitive load at pin VG | DS-280   |

| Capacitor at pin VG                                                | C <sub>VG</sub>    | -        | 4.7  | -    | nF   | connect to AGND                                                                                                                                                             | DS-158   |

| Capacitor at pin V6VI                                              | C <sub>V6VI</sub>  | -        | 20   | -    | μF   | I <sub>COM5V</sub> ≥ 35 mA; connect to AGND                                                                                                                                 | DS-159   |

| Capacitor at pin CP                                                | C <sub>CP</sub>    | -        | 4.7  | -    | nF   | connect to AGND; no static load                                                                                                                                             | DS-160   |

| V5VI current consumption                                           | I <sub>V5VI</sub>  | -        | _    | 1.5  | mA   | no SPI communication, power stages disabled                                                                                                                                 | DS-293   |

### **Small engine management IC**

Power supply and voltage monitoring function

### Table 19 Electrical characteristics power supplies (continued)

$T_J$  = -40°C to 150°C;  $V_{VS}$  = 10 - 18 V;  $V_{VSVI}$  = 5 V; all voltages with respect to AGND = PGND, positive current flowing into pin (unless otherwise specified).

| Parameter                                          | Symbol                   | Values |      |      | Unit | Note or condition                                                                                       | P-Number |

|----------------------------------------------------|--------------------------|--------|------|------|------|---------------------------------------------------------------------------------------------------------|----------|

|                                                    |                          | Min.   | Тур. | Мах. |      |                                                                                                         |          |

| Sensor<br>supply<br>tracking<br>accuracy           | ΔV <sub>T5V,acc</sub>    | -10    | _    | 10   | mV   | $\Delta V_{T5V} = V_{T5V} - V_{V5VI}$<br>2.9 V \le V_{V5VI} \le 5.1 V                                   | DS-161   |

| Sensor<br>supply<br>operation<br>current           | I <sub>T5V,op</sub>      | -      | -    | 150  | mA   |                                                                                                         | DS-162   |

| Sensor<br>supply<br>current<br>limitation          | I <sub>T5V,lim</sub>     | 150    | _    | _    | mA   |                                                                                                         | DS-163   |

| Sensor<br>supply sleep<br>current                  | I <sub>T5V,sleep</sub>   | -      | -    | 0.5  | μΑ   | V <sub>T5V</sub> = 0 V                                                                                  | DS-291   |

| Sensor<br>supply low<br>drop<br>resistance         | R <sub>T5V,low</sub>     | -      | _    | 3.3  | Ω    | $V_{V6VI} = V_{VS} = V_{V5VI} = 4.5 \text{ V}$                                                          | DS-164   |

| Capacitor at pin T5V                               | C <sub>T5V</sub>         | -      | 10   | -    | nF   | connect to AGND                                                                                         | DS-165   |

| Communicati<br>on supply<br>tracking<br>accuracy   | ΔV <sub>COM5V,acc</sub>  | -35    | -    | 35   | mV   | $\Delta V_{\text{COM5V}} = V_{\text{COM5V}} - V_{\text{V5VI}}$<br>2.9 V \leq V_{\text{V5VI}} \leq 5.1 V | DS-166   |

| Communicati<br>on supply<br>operation<br>current   | I <sub>COM5V,op</sub>    | -      | _    | 200  | mA   |                                                                                                         | DS-167   |

| Communicati<br>on supply<br>current<br>limitation  | I <sub>COM5V,lim</sub>   | 200    | -    | _    | mA   |                                                                                                         | DS-168   |

| Communicati<br>on supply<br>sleep current          | I <sub>COM5V,sleep</sub> | -      | -    | 0.5  | μΑ   | V <sub>COM5V</sub> = 0 V                                                                                | DS-294   |

| Communicati<br>on supply<br>low drop<br>resistance | R <sub>COM5V,low</sub>   | _      | -    | 2    | Ω    | $V_{V6VI} = V_{VS} = V_{V5VI} = 4.5 \text{ V}$                                                          | DS-169   |

### **Small engine management IC**

Power supply and voltage monitoring function

### Table 19 Electrical characteristics power supplies (continued)

$T_J$  = -40°C to 150°C;  $V_{VS}$  = 10 - 18 V;  $V_{V5VI}$  = 5 V; all voltages with respect to AGND = PGND, positive current flowing into pin (unless otherwise specified).

| Parameter                                        | Symbol                   | Values |      |      | Unit | Note or condition                          | P-Number |

|--------------------------------------------------|--------------------------|--------|------|------|------|--------------------------------------------|----------|

|                                                  |                          | Min.   | Тур. | Max. |      |                                            |          |

| Capacitor at pin COM5V                           | C <sub>COM5V</sub>       | _      | 10   | -    | μF   | I <sub>COM5V</sub> ≥ 7 mA; connect to AGND | DS-170   |

| V5VI<br>Undervoltage<br>detection<br>threshold 1 | V <sub>V5VI,UV,th1</sub> | 4.1    | -    | 4.8  | V    |                                            | DS-171   |

| V5VI<br>Undervoltage<br>detection<br>threshold 2 | V <sub>V5VI,UV,th2</sub> | 2.8    | -    | 3.2  | V    |                                            | DS-172   |

| T5V<br>Undervoltage<br>detection<br>threshold    | V <sub>T5V,UV,th</sub>   | 4.25   | _    | 4.85 | V    |                                            | DS-173   |

| COM5V<br>Undervoltage<br>detection<br>threshold  | V <sub>COM5V,UV,th</sub> | 4.25   | _    | 4.85 | V    |                                            | DS-174   |

| V5VI<br>Overvoltage<br>detection<br>threshold    | V <sub>V5VI,OV,th</sub>  | 5.1    | _    | 5.85 | V    |                                            | DS-175   |

| T5V<br>Overvoltage<br>detection<br>threshold     | V <sub>T5V,OV,th</sub>   | 5.1    | -    | 5.8  | V    |                                            | DS-176   |

| COM5V<br>Overvoltage<br>detection<br>threshold   | V <sub>COM5V,OV,th</sub> | 5.1    | _    | 5.8  | V    |                                            | DS-177   |

| Undervoltage detection hysteresis                | V <sub>UV,hys</sub>      | 10     | _    | 100  | mV   |                                            | DS-178   |

| Overvoltage detection hysteresis                 | V <sub>OV,hys</sub>      | 10     | -    | 130  | mV   |                                            | DS-179   |

| Undervoltage detection filter time               | t <sub>UV,fil</sub>      | 5      | _    | 15   | μs   |                                            | DS-180   |

27

### **Small engine management IC**

Power supply and voltage monitoring function

### Table 19 Electrical characteristics power supplies (continued)

$T_J$  = -40°C to 150°C;  $V_{VS}$  = 10 - 18 V;  $V_{VSVI}$  = 5 V; all voltages with respect to AGND = PGND, positive current flowing into pin (unless otherwise specified).

| Parameter                                              | Symbol                | Values |      |      | Unit | Note or condition | P-Number |

|--------------------------------------------------------|-----------------------|--------|------|------|------|-------------------|----------|

|                                                        |                       | Min.   | Тур. | Max. |      |                   |          |

| Overvoltage detection filter time                      | $t_{ m OV,fil}$       | 5      | _    | 15   | μs   |                   | DS-181   |

| T5V<br>Overtempera<br>ture<br>detection<br>threshold   | T <sub>T5V,ot</sub>   | 150    | -    | 200  | °C   |                   | DS-182   |

| COM5V<br>Overtempera<br>ture<br>detection<br>threshold | T <sub>COM5V,ot</sub> | 150    | -    | 200  | °C   |                   | DS-183   |

| Overtempera<br>ture<br>detection<br>hysteresis         | $T_{hys}$             | -      | 20   | _    | °C   |                   | DS-184   |

| Overtempera<br>ture filter<br>time                     | $t_{\rm ot}$          | 10     | _    | 20   | μs   |                   | DS-185   |

# **(infineon**

Watchdog

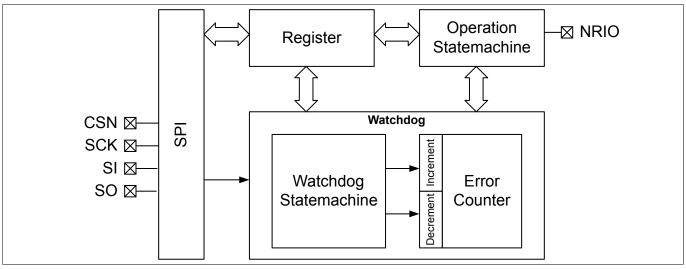

# 6 Watchdog

The device implementes a window watchdog with a closed and an open time window serviced by a watchdog command via SPI.

The watchdog consists of:

- · a watchdog state machine and

- an error counter

Figure 5 Watchdog function diagram

### 6.1 Watchdog period

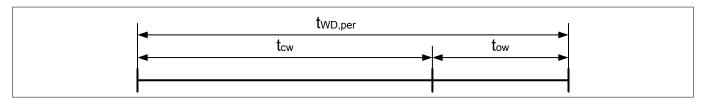

The watchdog period  $t_{WD,per}$  consists of a closed window  $t_{cw}$  and an open window  $t_{ow}$ .

Figure 6 Watchdog period

The watchdog period time  $t_{\rm WD,per}$  can be configured to 4 different values by setting the bit WDP in the WD register. The open window can be configured to a short and a long value for each watchdog period value with the bit WDOW in the WD register. The configuration of the watchdog period can be changed together with the watchdog command.

Table 20 Watchdog period configuration (all values are typical values)

| Watchdog period t <sub>WD,per</sub>  | Open window setting | Open window time tow              | Closed window time t <sub>cw</sub> |

|--------------------------------------|---------------------|-----------------------------------|------------------------------------|

| $t_{\text{WD,per1}} = 32 \text{ ms}$ | short               | $t_{\text{ow1,s}} = 4 \text{ ms}$ | 28 ms                              |

| $t_{\text{WD,per1}} = 32 \text{ ms}$ | long                | t <sub>ow1,l</sub> = 8 ms         | 24 ms                              |

| $t_{\text{WD,per2}} = 48 \text{ ms}$ | short               | t <sub>ow2,s</sub> = 8 ms         | 40 ms                              |

| $t_{\text{WD,per2}} = 48 \text{ ms}$ | long                | t <sub>ow2,l</sub> = 12 ms        | 36 ms                              |

### **Small engine management IC**

Watchdog

Table 20 Watchdog period configuration (all values are typical values) (continued)

| Watchdog period t <sub>WD,per</sub>  | Open window setting | Open window time tow        | Closed window time t <sub>cw</sub> |

|--------------------------------------|---------------------|-----------------------------|------------------------------------|

| $t_{\text{WD,per3}} = 64 \text{ ms}$ | short               | t <sub>ow3,s</sub> = 8 ms   | 56 ms                              |

| $t_{\rm WD,per3}$ = 64 ms            | long                | $t_{ow3,l} = 16 \text{ ms}$ | 48 ms                              |

| $t_{\rm WD,per4}$ = 128 ms           | short               | t <sub>ow4,s</sub> = 16 ms  | 112 ms                             |

| t <sub>WD,per4</sub> = 128 ms        | long                | $t_{ow4,l} = 30 \text{ ms}$ | 98 ms                              |

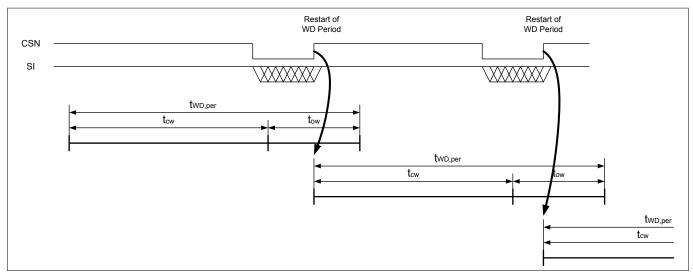

### 6.2 Trigger of the watchdog - watchdog (WD) command

The watchdog trigger event is a rising edge at the pin CSN of an SPI communication frame with write access to register WD. The trigger event is called watchdog command.

Note: All other SPI communications are not triggering the watchdog.

Figure 7 Watchdog trigger

# 6.3 Watchdog operation and error definition

The watchdog provides two functions to check the microcontroller:

- 1. timing check and

- 2. controlling of the functional check inside the microcontroller

A correct trigger of the watchdog is confirmed if the timing check and the control of the functional check inside the microcontroller are passed. This leads to a decrement of the error counter. All other situations are considered as watchdog errors and lead to an increment of the error counter. The watchdog status is indicated by the bits EC, WDTO, WDCE and WDERR in the register WD.

### **Timing check:**

The watchdog expects a watchdog command via SPI inside the open window. If the timing of the microcontroller is too fast, the watchdog detects a watchdog command inside the closed window. In this case, the watchdog command too early bit WDCE in register WD is set to 1. If the microcontroller timing is too slow, the watchdog period is expired and the watchdog time out bit WDTO in register WD is set to 1.

### Controlling of the internal functional check of the microcontroller:

The microcontroller transmits the status of the internal functional check by setting the watchdog check command bit WDC in register WD. If the internal functional check of the microcontroller is not ok, the watchdog error bit WDERR in register WD is set to 1.

### **Small engine management IC**

Watchdog

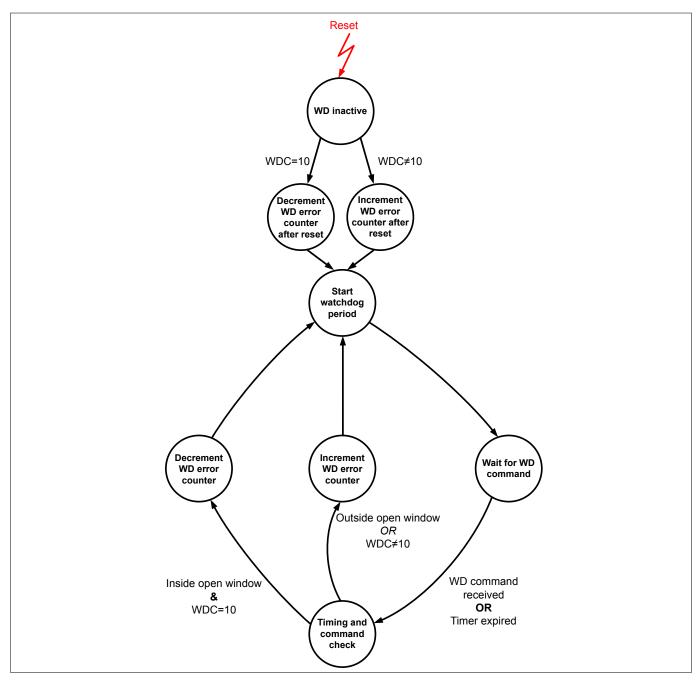

### 6.4 Watchdog state machine

After a reset condition the watchdog state machine is set to the state "WD inactive". The watchdog states are described in *Table 21*. The transitions of the state machine are described in *Table 22*.

#### Definitions: